12-Bit, 20 MSPS/40 MSPS/65 MSPS/80 MSPS,

1.8 V Analog-to-Digital Converter

AD9629 Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, M A 02062-9106, U.S.A. Tel: 781.329.4700 https://www.doczj.com/doc/809064336.html, Fax: 781.461.3113 ?2009 Analog Devices, Inc. All rights reserved.

FEATURES

1.8 V analog supply operation

1.8 V to 3.3 V output supply

SNR

71.3 dBFS at 9.7 MHz input

69.0 dBFS at 200 MHz input

SFDR

95 dBc at 9.7 MHz input

83 dBc at 200 MHz input

Low power

45 mW at 20 MSPS

85 mW at 80 MSPS

Differential input with 700 MHz bandwidth

On-chip voltage reference and sample-and-hold circuit

2 V p-p differential analog input

DNL = ±0.16 LSB

Serial port control options

Offset binary, gray code, or twos complement data format Integer 1, 2, or 4 input clock divider

Built-in selectable digital test pattern generation

Energy-saving power-down modes

Data clock out with programmable clock and data alignment APPLICATIONS

Communications

Diversity radio systems

Multimode digital receivers

GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX, TD-SCDMA Smart antenna systems

Battery-powered instruments

Hand held scope meters

Portable medical imaging

Ultrasound

Radar/LIDAR

PET/SPECT imaging

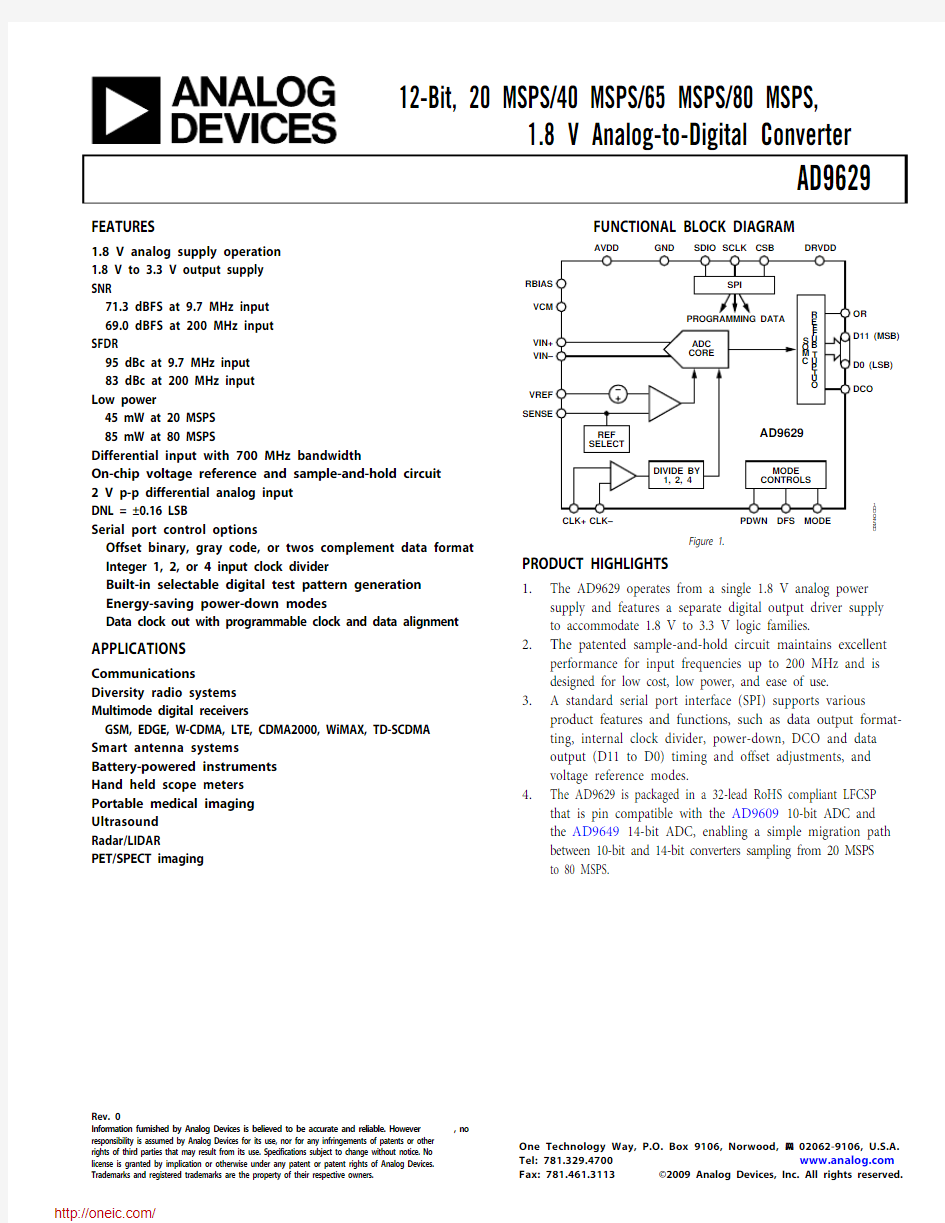

FUNCTIONAL BLOCK DIAGRAM

8

5

4

-

1

Figure 1.

PRODUCT HIGHLIGHTS

1.The AD9629 operates from a single 1.8 V analog power

supply and features a separate digital output driver supply to accommodate 1.8 V to 3.3 V logic families.

2.The patented sample-and-hold circuit maintains excellent

performance for input frequencies up to 200 MHz and is

designed for low cost, low power, and ease of use.

3. A standard serial port interface (SPI) supports various

product features and functions, such as data output format-ting, internal clock divider, power-down, DCO and data

output (D11 to D0) timing and offset adjustments, and

voltage reference modes.

4.The AD9629 is packaged in a 32-lead RoHS compliant LFCSP

that is pin compatible with the AD9609 10-bit ADC and

the AD9649 14-bit ADC, enabling a simple migration path between 10-bit and 14-bit converters sampling from 20 MSPS to 80 MSPS.

AD9629

Rev. 0 | Page 2 of 32

TABLE OF CONTENTS

Features .............................................................................................. 1 Applications ....................................................................................... 1 Functional Block Diagram .............................................................. 1 Product Highlights ........................................................................... 1 Revision History ............................................................................... 2 General Description ......................................................................... 3 Specifications ..................................................................................... 4 DC Specifications ......................................................................... 4 AC Specifications .......................................................................... 5 Digital Specifications ................................................................... 6 Switching Specifications .............................................................. 7 Timing Specifications .................................................................. 8 Absolute Maximum Ratings ............................................................ 9 Thermal Characteristics .............................................................. 9 ESD Caution .................................................................................. 9 Pin Configuration and Function Descriptions ........................... 10 Typical Performance Characteristics ........................................... 11 AD9629-80 .................................................................................. 11 AD9629-65 .................................................................................. 13 AD9629-40 .................................................................................. 14 AD9629-20 .................................................................................. 15 Equivalent Circuits ......................................................................... 16 Theory of Operation ...................................................................... 17 Analog Input Considerations .................................................... 17 Voltage Reference ....................................................................... 19 Clock Input Considerations ...................................................... 20 Power Dissipation and Standby Mode .................................... 21 Digital Outputs ........................................................................... 22 Timing ......................................................................................... 22 Built-In Self-Test (BIST) and Output Test .................................. 23 Built-In Self-Test (BIST) ............................................................ 23 Output Test Modes ..................................................................... 23 Serial Port Interface (SPI) .............................................................. 24 Configuration Using the SPI ..................................................... 24 Hardware Interface ..................................................................... 25 Configuration Without the SPI ................................................ 25 SPI Accessible Features .............................................................. 25 Memory Map .................................................................................. 26 Reading the Memory Map Register Table ............................... 26 Open Locations .......................................................................... 26 Default Values ............................................................................. 26 Memory Map Register Table ..................................................... 27 Memory Map Register Descriptions ........................................ 29 Applications Information .............................................................. 30 Design Guidelines ...................................................................... 30 Outline Dimensions ....................................................................... 31 Ordering Guide .. (31)

REVISION HISTORY

10/09—Revision 0: Initial Version

AD9629

Rev. 0 | Page 3 of 32

GENERAL DESCRIPTION

The AD9629 is a monolithic, single channel 1.8 V supply, 12-bit, 20 MSPS/40 MSPS/65 MSPS/80 MSPS analog-to-digital conver-ter (ADC). It features a high performance sample-and-hold circuit and on-chip voltage reference.

The product uses multistage differential pipeline architecture with output error correction logic to provide 12-bit accuracy at 80 MSPS data rates and to guarantee no missing codes over the full operating temperature range.

The ADC contains several features designed to maximize flexibility and minimize system cost, such as programmable clock and data alignment and programmable digital test pattern generation. The available digital test patterns include built-in deterministic and pseudorandom patterns, along with custom user-defined test patterns entered via the serial port interface (SPI). A differential clock input with optional 1, 2, or 4 divide ratios controls all internal conversion cycles.

The digital output data is presented in offset binary, gray code, or twos complement format. A data output clock (DCO) is

provided to ensure proper latch timing with receiving logic. Both 1.8 V and 3.3 V CMOS levels are supported.

The AD9629 is available in a 32-lead RoHS compliant LFCSP and is specified over the industrial temperature range (?40°C to +85°C).

AD9629

Rev. 0 | Page 4 of 32

SPECIFICATIONS

DC SPECIFICATIONS

AVDD = 1.8 V; DRVDD = 1.8 V , maximum sample rate, 2 V p-p differential input, 1.0 V internal reference; AIN = ?1.0 dBFS, 50% duty cycle clock, unless otherwise noted. Table 1.

Parameter Temp AD9629-20/AD9629-40 AD9629-65 AD9629-80

Unit M in Typ M ax M in Typ M ax M in Typ M ax RESOLUTION Full 12 12 12 Bits ACCURACY No Missing Codes Full Guaranteed G uaranteed G uaranteed Offset Error Full ?0.40 +0.05 +0.50 ?0.40 +0.05 +0.50 ?0.40 +0.05 +0.50 % FSR

Gain Error 1

Full ?1.5 ?1.5 ?1.5 % FSR Differential Nonlinearity (DNL)2 Full ±0.25 ±0.25 ±0.30 LSB 25°C ±0.11 ±0.11 ±0.16 LSB Integral Nonlinearity (INL)2 Full ±0.40 ±0.30 ±0.35 LSB 25°C ±0.11 ±0.13 ±0.16 LSB TEMPERATURE DRIFT Offset Error Full ±2 ±2 ±2 ppm/°C INTERNAL VOLTA G E REFERENCE Output Voltage (1 V Mode) Full 0.984 0.996 1.008 0.984 0.996 1.008 0.984 0.996 1.008 V Load Regulation Error at 1.0 mA Full 2 2 2 mV INPUT-REFERRED NOISE VREF = 1.0 V 25°C 0.25 0.25 0.25 LSB rms ANALO G INPUT Input Span, VREF = 1.0 V Full 2 2 2 V p-p Input Capacitance 3 Full 6 6 6 pF Input Common-Mode Voltage Full 0.9 0.9 0.9 V Input Common-Mode Range Full 0.5 1.3 0.5 1.3 0.5 1.3 V REFERENCE INPUT RESISTANCE Full 7.5 7.5 7.5 kΩ POWER SUPPLIES Supply Voltage AVDD Full 1.7 1.8 1.9 1.7 1.8 1.9 1.7 1.8 1.9 V DRVDD Full 1.7 3.6 1.7 3.6 1.7 3.6 V Supply Current

IAVDD 2

Full 24.9/31.1 26.7/33.2 41.2 46.0 46.8 50.0 mA IDRVDD 2 (1.8 V) Full 1.5/2.5 4.2 5.0 mA IDRVDD 2 (3.3 V) Full 2.7/4.7 7.5 9.0 mA POWER CONSUMPTION DC Input Full 45.0/56.7 75 85.2 mW

Sine Wave Input 2

(DRVDD = 1.8 V) Full 47.5/60.5 50.7/65.0 81.7 86.0 93 100 mW

Sine Wave Input 2

(DRVDD = 3.3 V) Full 53.7/71.7 98.9 114 mW Standby Power 4 Full 34 34 34 mW Power-Down Power Full 0.5 0.5 0.5 mW

1 Measured with 1.0 V external reference.

2

Measured with a 10 MHz input frequency at rated sample rate, full-scale sine wave, with approximately 5 pF loading on each output bit. 3

Input capacitance refers to the effective capacitance between one differential input pin and AGND. 4

Standby power is measured with a dc input and the clock active.

AD9629

Rev. 0 | Page 5 of 32

AC SPECIFICATIONS

AVDD = 1.8 V; DRVDD = 1.8 V , maximum sample rate, 2 V p-p differential input, 1.0 V internal reference; AIN = ?1.0 dBFS, 50% duty cycle clock, unless otherwise noted. Table 2.

Parameter 1 Temp AD9629-20/AD9629-40 AD9629-65 AD9629-80

Unit M in Typ M ax M in Typ M ax M in Typ M ax SIGNAL-TO-NOISE RATIO (SNR) f IN = 9.7 MHz 25°C 71.4 71.3 71.3 dBFS f IN = 30.5 MHz 25°C 71.2 71.2 71.2 dBFS Full 70.5/70.7 70.6 dBFS f IN = 70 MHz 25°C 70.5/71.0 71.0 70.9 dBFS Full 70.3 dBFS f IN = 200 MHz 25°C 69.0 69.0 dBFS SI G NAL-TO-NOISE-AND-DISTORTION (SINAD)

f IN = 9.7 MHz 25°C 71.4 71.3 71.2 dBFS f IN = 30.5 MHz 25°C 71.2 71.2 71.1 dBFS Full 70.5/70.6 70.5 dBFS f IN = 70 MHz 25°C 70.4/70.9 70.9 70.8 dBFS Full 70.2 dBFS f IN = 200 MHz 25°C 68 68 68 dBFS EFFECTIVE NUMBER OF BITS (ENOB) f IN = 9.7 MHz 25°C 11.4/11.6 11.6 11.5 Bits f IN = 30.5 MHz 25°C 11.4/11.5 11.5 11.5 Bits f IN = 70 MHz 25°C 11.4/11.5 11.5 11.5 Bits f IN = 200 MHz 25°C 11.0 11.0 11.0 Bits WORST SECOND OR THIRD HARMONIC f IN = 9.7 MHz 25°C ?97 ?97 ?95 dBc f IN = 30.5 MHz 25°C ?95 ?95 ?94 dBc Full ?83 ?83 dBc f IN = 70 MHz 25°C ?96/?94 ?95 ?95 dBc Full ?81 dBc f IN = 200 MHz 25°C ?83 ?83 ?83 dBc SPURIOUS-FREE DYNAMIC RANGE (SFDR) f IN = 9.7 MHz 25°C 97 97 95 dBc f IN = 30.5 MHz 25°C 96/95 95 93 dBc Full 83 83 dBc f IN = 70 MHz 25°C 96/94 95 95 dBc Full 81 dBc f IN = 200 MHz 25°C 83 83 83 dBc WORST OTHER (HARMONIC OR SPUR) f IN = 9.7 MHz 25°C ?100 ?100 ?100 dBc f IN = 30.5 MHz 25°C ?100 ?100 ?100 dBc Full ?92/?91 ?93 dBc f IN = 70 MHz 25°C ?97/?100 ?100 ?100 dBc Full ?89 dBc f IN = 200 MHz 25°C ?92 ?92 ?92 dBc TWO-TONE SFDR f IN = 30.5 MHz (?7 dBFS), 32.5 MHz (?7 dBFS) 25°C 90 90 90 dBc ANALOG INPUT BANDWIDTH 25°C 700 700 700 MHz

1

See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation , for a complete set of definitions.

AD9629

Rev. 0 | Page 6 of 32

DIGITAL SPECIFICATIONS

AVDD = 1.8 V; DRVDD = 1.8 V , maximum sample rate, 2 V p-p differential input, 1.0 V internal reference; AIN = ?1.0 dBFS, 50% duty cycle clock, unless otherwise noted. Table 3.

Parameter Temp AD9629-20/AD9629-40/AD9629-65/AD9629-80

Unit

M in Typ M ax DIFFERENTIAL CLOCK INPUTS (CLK+, CLK?) Logic Compliance CMOS/LVDS/LVPECL Internal Common-Mode Bias Full 0.9 V Differential Input Voltage Full 0.2 3.6 V p-p Input Voltage Range Full GND ? 0.3 AVDD + 0.2 V High Level Input Current Full ?10 +10 μA Low Level Input Current Full ?10 +10 μA Input Resistance Full 8 10 12 kΩ Input Capacitance Full 4

pF LOGIC INPUTS (SCLK/DFS, MODE, SDIO/PDWN)1

High Level Input Voltage Full 1.2 DRVDD + 0.3 V Low Level Input Voltage Full 0 0.8 V High Level Input Current Full ?50 ?75 μA Low Level Input Current Full ?10 +10 μA Input Resistance Full 30 kΩ Input Capacitance Full 2

pF LOGIC INPUTS (CSB)2

High Level Input Voltage Full 1.2 DRVDD + 0.3 V Low Level Input Voltage Full 0 0.8 V High Level Input Current Full ?10 +10 μA Low Level Input Current Full 40 135 μA Input Resistance Full 26 kΩ Input Capacitance Full 2 pF DIGITAL OUTPUTS DRVDD = 3.3 V High Level Output Voltage, I OH = 50 μA Full 3.29 V High Level Output Voltage, I OH = 0.5 mA Full 3.25 V Low Level Output Voltage, I OL = 1.6 mA Full 0.2 V Low Level Output Voltage, I OL = 50 μA Full 0.05 V DRVDD = 1.8 V High Level Output Voltage, I OH = 50 μA Full 1.79 V High Level Output Voltage, I OH = 0.5 mA Full 1.75 V Low Level Output Voltage, I OL = 1.6 mA Full 0.2 V Low Level Output Voltage, I OL = 50 μA Full 0.05

V

1 Internal 30 kΩ pull-down. 2

Internal 30 kΩ pull-up.

AD9629

Rev. 0 | Page 7 of 32

SWITCHING SPECIFICATIONS

AVDD = 1.8 V; DRVDD = 1.8 V , maximum sample rate, 2 V p-p differential input, 1.0 V internal reference; AIN = ?1.0 dBFS, 50% duty cycle clock, unless otherwise noted. Table 4.

Parameter Temp AD9629-20/AD9629-40 AD9629-65 AD9629-80

Unit M in Typ M ax M in Typ M ax M in Typ M ax CLOCK INPUT PARAMETERS Input Clock Rate 1 Full 80/160 260 320 MHz

Conversion Rate 2

Full 3 20/40 3 65 3 80 MSPS

CLK Period, Divide-by-1 Mode (t CLK ) Full 50/25 15.38 12.5 ns

CLK Pulse Width High (t

CH ) 25.0/12.5 7.69 6.25 ns Aperture Delay (t A ) Full 1.0 1.0 1.0 ns Aperture Uncertainty (Jitter, t J ) Full 0.1 0.1 0.1 ps rms DATA OUTPUT PARAMETERS

Data Propagation Delay (t PD ) Full 3 3 3 ns DCO Propagation Delay (t DCO ) Full 3 3 3 ns DCO to Data Skew (t SKEW ) Full 0.1 0.1 0.1 ns

Pipeline Delay (Latency) Full 8 8 8 Cycles

Wake-Up Time 3

Full 350 350 350 μs Standby Full 600/400 300 260 ns OUT-OF-RAN G E RECOVERY TIME Full 2 2 2 Cycles

1 Input clock rate is the clock rate before the internal CLK divider. 2

Conversion rate is the clock rate after the CLK divider. 3

Wake-up time is dependent on the value of the decoupling capacitors.

VIN

CLK+CLK–

DATA DCO

Figure 2. CMOS Output Data Timing

AD9629

Rev. 0 | Page 8 of 32

TIMING SPECIFICATIONS

Table 5.

Parameter

Conditions Min Typ Max Unit SPI TIMING REQUIREMENTS

t DS Setup time between the data and the rising edge of SCLK 2 ns t DH Hold time between the data and the rising edge of SCLK 2 ns t CLK Period of the SCLK

40 ns t S Setup time between CSB and SCLK 2 ns t H Hold time between CSB and SCLK 2 ns t HIGH SCLK pulse width high 10 ns t LOW SCLK pulse width low

10 ns t EN_SDIO Time required for the SDIO pin to switch from an input to an output relative to the SCLK falling edge

10 ns t DIS_SDIO

Time required for the SDIO pin to switch from an output to an input relative to the SCLK rising edge

10

ns

AD9629

Rev. 0 | Page 9 of 32

ABSOLUTE MAXIMUM RATINGS

Table 6.

Parameter Rating AVDD to AGND ?0.3 V to +2.0 V DRVDD to AGND ?0.3 V to +3.9 V VIN+, VIN? to AGND ?0.3 V to AVDD + 0.2 V CLK+, CLK? to AGND ?0.3 V to AVDD + 0.2 V VREF to AGND ?0.3 V to AVDD + 0.2 V

SENSE to AGND ?0.3 V to AVDD + 0.2 V

VCM to AGND ?0.3 V to AVDD + 0.2 V

RBIAS to AGND ?0.3 V to AVDD + 0.2 V

CSB to AGND ?0.3 V to DRVDD + 0.3 V

SCLK/DFS to AGND ?0.3 V to DRVDD + 0.3 V

SDIO/PDWN to AGND ?0.3 V to DRVDD + 0.3 V

MODE/OR to AGND ?0.3 V to DRVDD + 0.3 V D0 through D11 to AGND ?0.3 V to DRVDD + 0.3 V

DCO to AGND ?0.3 V to DRVDD + 0.3 V

Operating Temperature Range (Ambient) ?40°C to +85°C Maximum Junction Temperature Under Bias 150°C Storage Temperature Range (Ambient) ?65°C to +150°C

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

THERMAL CHARACTERISTICS

The exposed paddle is the only ground connection for the chip. The exposed paddle must be soldered to the AGND plane of the user’s circuit board. Soldering the exposed paddle to the user’s board also increases the reliability of the solder joints and maximizes the thermal capability of the package. Table 7. Thermal Resistance Package Type Airflow Velocity (m/sec) θJA 1, 2

θJC 1, 3 θJB 1, 4 ΨJT 1, 2 Unit 32-Lead LFCSP 5 mm × 5 mm 0 37.1 3.1 20.7 0.3 °C/W 1.0 32.4 0.5 °C/W 2.5 29.1 0.8 °C/W 1

Per JEDEC 51-7, plus JEDEC 51-5 2S2P test board. 2

Per JEDEC JESD51-2 (still air) or JEDEC JESD51-6 (moving air).

3

Per MIL-Std 883, Method 1012.1. 4 Per JEDEC JESD51-8 (still air).

Typical θJA is specified for a 4-layer PCB with a solid ground plane. As shown in Table 7, airflow improves heat dissipation, which reduces θJA . In addition, metal in direct contact with the package leads from metal traces, through holes, ground, and power planes, reduces the θJA .

ESD CAUTION

AD9629

Rev. 0 | Page 10 of 32

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1CLK+2CLK–3AVDD 4CSB 5SCLK/DFS 6SDIO/PDWN

7NC 8

NC 24AVDD

23MODE/OR 22DCO

21D11 (MSB)20D1019D918D817D7

9(L S B ) D 010D 111D 212D 313D R V D D 14D 415D 516

D 632A V D D 31V I N +30V I N –29A V D D 28R B I A S 27V C M 26S

E N S E 25

V R E F 08540-003

NOTES

1. NC = NO CONNECT.

2. THE EXPOSED PADDLE MUST BE SOLDERED TO

THE PCB GROUND TO ENSURE PROPER HEAT DISSIPATION, NOISE, AND MECHANICAL STRENGTH BENEFITS.

Figure 3. Pin Configuration

Table 8. Pin Function Description

Pin No.

Mnemonic

Description

0 (EPAD)

GND

Exposed Paddle. The exposed paddle is the only ground connection. It must be soldered to the analog ground of the customer’s PCB to ensure proper functionality and maximize heat dissipation, noise, and mechanical strength benefits.

1, 2 CLK+, CLK? Differential Encode Clock. PECL, LVDS, or 1.8 V CMOS inputs. 3, 24, 29, 32 AVDD 1.8 V Supply Pin for ADC Core Domain. 4 CSB SPI Chip Select. Active low enable. 30 kΩ internal pull-up. 5 SCLK/DFS SPI Clock Input in SPI Mode (SCLK). 30 kΩ internal pull-down.

Data Format Select in Non-SPI Mode (DFS). Static control of data output format. 30 kΩ internal pull-down. DFS high = twos complement output; DFS low = offset binary output.

6 SDIO/PDWN SPI Data Input/Output (SDIO). Bidirectional SPI data I/O in SPI mode. 30 kΩ internal pull-down.

Non-SPI Mode Power-Down (PDWN). Static control of power-down with 30 kΩ internal pull-down. See Table 14 for details.

7, 8 NC Do Not Connect. 9 to 12, 14 to 21 D0 (LSB) to D11 (MSB)

ADC Digital Outputs.

13 DRVDD 1.8 V to 3.3 V Supply Pin for Output Driver Domain. 22 DCO Data Clock Digital Output. 23 MODE/OR Chip Mode Select Input or Out-of-Range (OR) Digital Output in SPI Mode.

Default = out-of-range (OR) digital output (SPI Register 0x2A[0] = 1). Option = chip mode select input (SPI Register 0x2A[0] = 0). Chip power down (SPI Register 0x08[7:5] = 100b). Chip standby (SPI Register 0x08[7:5] = 101b).

Normal operation, output disabled (SPI Register 0x08[7:5] = 110b). Normal operation, output enabled (SPI Register 0x08[7:5] = 111b). Out-of-Range (OR) digital output only in non-SPI mode.

25 VREF 1.0 V Voltage Reference Input/Output. See Table 10. 26 SENSE Reference Mode Selection. See Table 10. 27 VCM Analog Output Voltage at Mid AVDD Supply. Sets common mode of the analog inputs. 28 RBIAS Sets Analog Current Bias. Connect to 10 kΩ (1% tolerance) resistor to ground. 30, 31 VIN?, VIN+ ADC Analog Inputs.

分销商库存信息:

ANALOG-DEVICES

AD9629BCPZRL7-20AD9629BCPZRL7-40AD9629BCPZ-20 AD9629BCPZ-40AD9629BCPZRL7-65AD9629BCPZRL7-80 AD9629BCPZ-65AD9629BCPZ-80AD9629-80EBZ

AD9629-65EBZ AD9629-20EBZ AD9629-40EBZ

产业处于不同时期的会展营销策略分析 针对行业发展不同周期的会展营销策略分析之朝阳产业 展览会的成功举办必须三个基本前提,产业基础、政府支持、优势场馆,三个条件是前提,有了这个前提才能考虑其他方面。 朝阳产业,顾名思义,就是产业发展处于生长期,处于被客户认知与接受之间的产业,产品逐渐为客户所认可,并有着纵深发展潜力的产业周期,当然,产业周期的判定需要很 复杂的论证,这需要一定的眼光以及对政策调整的准确认知。有些论证结果可能是错误的,而如果是正确的则前途不可限量。而行业展览会的发展便是一个论证的过程。 首先,需要确定该行业有广阔的发展前景,在未来一段时间内会发展成为成熟产业,同时,很多相关企业在往这方面努力,共同促进产业升级,在未来一段时间内会有一定的产业集群出现,这样,大力促进该行业发展的企业则成为行业的领军者,享受产业升级所带来的巨额利润,这也是很多企业热衷于投资的主要原因,当然这种投资也可能变为投入, 投资与投入是截然不同的概念,投资是有回报的,而投入则是没有回报的,二者的意义有云泥之差。 展览会的举办,简单来说就是打造一个平台,让供需双方在一个平台上有效的沟通,达到行业内信息的共享,同时促进行业的发展,对于产业处于朝阳期的行业展览会来说,由 于对未来产业发展形势的不明朗,需要动用各种营销策略来吸引买家和卖家共同支持展览会这个平台。 展览会的组织风险也很大,因为很多都是前期投资,最后只有得到供需双方的认可后,展览会才有可能收回成本,于是,组织方判断进入哪个产业需要很深的判断力,一旦确定 了进入,则需要采用各种营销策略方式来促成供需双方的共享平台,于是,营销策略显得尤为重要。 首先,动用政府的力量,政府相关部门的产业倾斜是产业发展的前提条件,有了政府的支持,产业发展才有可能,所以展会初期要取得政府部门的支持,通过政府的力量影响相 关企业的参展倾向,从另外一个角度上来说,政府的倾向决定着这个展览会是否有进行下去的必要。 其次,重点客户公关,重点客户是行业内的意见领袖,他们的决策更有前瞻性、更有说服力,也是行业发展的领军企业,他们的决定将影响着行业内中小企业的动向,而这些大

变电所母线桥的动稳定校验 随着用电负荷的快速增长,许多变电所都对主变进行了增容,并对相关设备进行了调换和校验,但往往会忽视主变母线桥的动稳定校验,事实上此项工作非常重要。当主变增容后,由于阻抗发生了变化,短路电流将会增大许多,一旦发生短路,产生的电动力有可能会对母线桥产生破坏。特别是户内母线桥由于安装时受地理位置的限制,绝缘子间的跨距较长,受到破坏的可能性更大,所以应加强此项工作。 下面以我局35kV/10kv胡店变电所#2主变增容为例来谈谈如何进行主变母线桥的动稳定校验和校验中应注意的问题。 1短路电流计算 图1为胡店变电所的系统主接线图。(略) 已知#1主变容量为10000kVA,短路电压为7.42%,#2主变容量为12500kVA,短路电压为7.48%(增容前短路电压为7.73%)。 取系统基准容量为100MVA,则#1主变短路电压标么值 X1=7.42/100×100×1000/10000=0.742, #2主变短路电压标么值 X2=7.48/100×100×1000/12500=0.5984 胡店变电所最大运行方式系统到35kV母线上的电抗标么值为0.2778。 ∴#1主变与#2主变的并联电抗为: X12=X1×X2/(X1+X2)=0.33125; 最大运行方式下系统到10kV母线上的组合电抗为: X=0.2778+0.33125=0.60875

∴10kV母线上的三相短路电流为:Id=100000/0.60875*√3*10.5,冲击电流:I sh=2.55I =23032.875A。 d 2动稳定校验 (1)10kV母线桥的动稳定校验: 进行母线桥动稳定校验应注意以下两点: ①电动力的计算,经过对外边相所受的力,中间相所受的力以及三相和二相电动力进行比较,三相短路时中间相所受的力最大,所以计算时必须以此为依据。 ②母线及其支架都具有弹性和质量,组成一弹性系统,所以应计算应力系数,计及共振的影响。根据以上两点,校验过程如下: 已知母线桥为8×80mm2的铝排,相间中心线间距离为210mm,先计算应力系数: ∵频率系数N f=3.56,弹性模量E=7×10.7 Pa,单位长度铝排质量M=1.568kg/m,绝缘子间跨距2m,则一阶固有频率: f’=(N f/L2)*√(EI/M)=110Hz 查表可得动态应力系数β=1.3。 ∴单位长度铝排所受的电动力为: f ph=1.73×10-7I sh2/a×β=568.1N/m ∵三相铝排水平布置,∴截面系数W=bh2/6=85333mm3,根据铝排的最大应力可确定绝缘子间允许的最大跨距为: L MAX=√10*σal*W/ f ph=3.24m ∵胡店变主变母线桥绝缘子间最大跨距为2m,小于绝缘子间的最大允许跨距。

毕业论文 论文题目:国内会展营销现状及营销策略分析 班级 专业 学生姓名 学生学号 指导教师 日期 _____年月____日 目录 摘要 (1) 一、会展业简况 (1) (一)会展业概念 (1) (二)会展业在国民经济中地地位 (1) 二.会展营销简况 (1) (一)国内会展市场状况 (1) (二)会展营销现状 (2) (三)会展营销对营销学地创新之处 ............................................. 2个人收集整理勿做商业用途三、会展营销中地营销策略分析 . (3) (一)市场定位策略与促销策略 (3) (二)服务策略 (3) (三)品牌策略 (4) (四)经营创新策略 (4) 四、会展营销现状存在地问题分析 (4) (一)缺乏整体地营销协调 (4) (二)会展营销理念落后 (5) (三)城市会展定位混乱 (5) (四)客户关系管理不到位,服务营销做得差 ............................. 5个人收集整理勿做商业用途五、关于会展营销发展地建议.. (5) (一)加速会展业地市场化 (5) (二)着力打造会展品牌 (5)

(三)注重服务营销 (6) (四)努力拓展营销渠道................................................................. 6个人收集整理勿做商业用途(五)加速会展营销地网络化 . (6) 结束语 (6) 参考文献 (6) 国内会展营销现状及营销策略分析 摘要: 会展自诞生起就具有营销地性质,目前会展营销是许多企业全新而有效地市场营销组合策略之一,对会展营销最具有主导作用地主体是展览公司.本文从展览公司地角度出发研究会展营销地状况,并对会展营销地发展提出相关地建议. 个人收集整理勿做商业用途 关键字:会展营销营销学营销策略 一、会展业简况 (一)会展业概念 会展业是会议业和展览业地总称,是一个新兴地服务行业,影响面广,关联度高.会展业为参展商和观众提供了一个理想地沟通和交流地一个平台.通过这个平台,观众能在短时间接触到大量地提供统一产品地参展商,接触到不同地展品,比较充分地了解到同类产品地最新信息;而参展商也能在较短地时间内接触到大量地观众.通过参展,参展商将企业形象、产品等信息传达给观众;观众也可以找到合适地产品、合适地参展商,从而更好地合作和交流,或从中找寻新地商机.所以说,会展地本质是信息传播地一个平台,可以说展会时一个浓缩无限商机得打舞台.作为联系参展商和观众地桥梁和纽带,参展是一个重要地营销方式之一,也是观众获取信息地重要渠道.个人收集整理勿做商业用途 (二)会展业在国民经济中地地位 21世纪地今天,国际间地政治、经济、文化交流异常频繁,会展业作为第三产业发展日趋成熟后出现地一种新型经济形态,已成为世界上许多发达国家国民经济新地经济增长点.作为一个前景广阔地产业,会展业素有“城市地面包”和“触摸世界地窗口”之称,它不仅可以为会展举办城市带来巨大地直接和间接经济效益,而且能加强城市与外界地商贸、文化交流,推进城市基础设施建设,提高城市地知名度以及优化地区经济结构,因而受到了世界各国地广泛重视.个人收集整理勿做商业用途 二、会展营销概述 (一)国内会展市场状况 随着全球经济一体化进程地加快,会展经济在我国得到了快速发展,并成为国民经济运行中地新亮点和助推器.会展市场作为专门举办会议和展览地场所,是会展经济发展地重要载体.目前,在发达国家,会展市场已发展到相当高地水平.例如德国地汉诺威、慕尼黑、杜塞尔多夫、法兰克福,英国地伦敦,美国地芝加哥,法国地巴黎,意大利地M兰,以及新加坡等都是著

母线电动力及动热稳定性计算 1 目的和范围 本文档为电气产品的母线电动力、动稳定、热稳定计算指导文件,作为产品结构设计安全指导文件的方案设计阶段指导文件,用于母线电动力、动稳定性、热稳定性计算的选型指导。 2 参加文件 表1 3 术语和缩略语 表2 4 母线电动力、动稳定、热稳定计算 4.1 载流导体的电动力计算 4.1.1 同一平面内圆细导体上的电动力计算

? 当同一平面内导体1l 和2l 分别流过1I 和2I 电流时(见图1),导体1l 上的电动力计 算 h F K I I 4210 π μ= 式中 F ——导体1l 上的电动力(N ) 0μ——真空磁导率,m H 60104.0-?=πμ; 1I 、2I ——流过导体1l 和2l 的电流(A ); h K ——回路系数,见表1。 图1 圆细导体上的电动力 表1 回路系数h K 表 两导体相互位置及示意图 h K 平 行 21l l = ∞=1l 时,a l K h 2= ∞≠1l 时,?? ? ???-+=l a l a a l K h 2)(12 21l l ≠ 22 2) ()(1l a m l a l a K h ++-+= 22)()1(l a m +-- l a m =

? 当导体1l 和2l 分别流过1I 和2I 电流时,沿1l 导体任意单位长度上各点的电动力计 算 f 124K f I I d μ= π 式中 f ——1l 导体任意单位长度上的电动力(m N ); f K ——与同一平面内两导体的长度和相互位置有关的系数,见表2。 表2 f K 系数表

4.1.2 两平行矩形截面导体上的电动力计算 两矩形导体(母线)在b <<a ,且b >>h 的情况下,其单位长度上的电动力F 的 计算见表3。 当矩形导体的b 与a 和h 的尺寸相比不可忽略时,可按下式计算 712 210x L F I I K a -=? 式中 F -两导体相互作用的电动力,N ; L -母线支承点间的距离,m ; a -导体间距,m ; 1I 、2I -流过两个矩形母线的电流,A ; x K -导体截面形状系数; 表3 两矩形导体单位长度上的电动力 4.1.3 三相母线短路时的电动力计算

会展营销策划书范文 第一篇:会展营销第二篇:如何做好会展营销第三篇:会展策划书第四篇:会展策划书第五篇:会展策划书更多相关范文第一章会展营销概述 一、会展活动的内涵: 1、会议:会议是一种聚众议事的社会活动。在现实生活中,凡是在一定的时间和空间内,为了达到一定目的或者解决某个问题而进行的有组织、有领导、有共同议题的议事活动均可称之会议。 2、展览会:展览会是会展活动中最普遍、最活跃并且最具有典型性的部分。从展览会产生的历史以及在社会经济生活中发挥的主要作用看,展览会是为参展商和专业买家提供交易机会的贸易平台,是一个与贸易紧密相关的概念。 3、特殊活动:“特殊活动”是指人们为了纪念某个特殊的事件或者为了满足某种社会群体的特殊需求而精心计划和举办的文体比赛、庆祝仪式、特技表演以及节庆活动等。 二、会展活动的共性特征: 1、都是“长期筹备、短期举办”的“点”状活动,而不像行政及企业中那样的“线”状活动 2、都涉及到人员的迁徙和移动,参加者参加必须借助交通工具并在举办地住宿和餐饮 3、能为人们的日常工作和生活平添几分乐趣,能够吸引人们的参与,并能够引起媒体的关注;

4、活动的组织管理都是以独立的“项目”方式进行的,一项活动结束后,需要策划和组织另一项活动,并在项目的不断策划和举办过程中,提高活动的声誉和价值。 三、会展活动的构成及本课程的研究范围: 会展活动:1、会议:(1)公司会议(2)协会会议(3)政府会议 2、展览:(1)商业性展览:机场展览会、化工展览会、服装展览会等 (2)公益性展览会:科普展览会、成就展览会、戒毒展览会等 3、特殊活动:(1)国际性大型活动(2)区域性大型活动(3)地方性节庆 四、会展营销的概念:会展营销是指展览会组织者寻找目标市场、研究目标顾客需求、设计会展产品和服务、制订营销价格、选择营销渠道以及保持良好客户关系等一系列销售活动的总和。 五、以会展项目为中心的会展营销研究对象:1、会展营销理念2、会展产品和服务3、会展顾客采购行为分析4、会展宣传和推广5、会展营销渠道管理6、会展产品和服务定价策 7、会展赞助的策划和营销8、会展客户关系管理9、因特网在会展营销中的应用 六、以营销管理为中心的会展营销研究对象:1、从会展企业管理的视角,研究如何制订营销管理战略、如何制订营销计划、如何协调

会展营销策划方案 篇一:参展商---展会营销策划方案 房地产项目参会营销方案 目录 一、前言 3 一、参展的目的 7 二、展会背景 8 三、营销活动全程时间计划 9 四、办展流程 10 五、展会内容策划 11 六、展会结束后还需要进行的工作 13 七、接待人员展会及其他环节工作职责、要求 14 八、展会费用预算 15 九、附件 16 四、活动参与人员 17 五、活动的主题 17 六、活动内容 17 七、看房车安排方案 20 八、活动准备工作: 21 一、前言 展览会是一种“昂贵”的行为,然而许多企业并没有投入足够的时间和精力对展会进行周密的策划。

一个策划周密、执行良好的展会可能总共需要花费6个月甚至更多的时间,包括事先的准备工作和展会后的后续活动。 第一阶段:确定参加展会的目标: 1、了解展会参观者的大致情况。 2、企业自身能投入多少资源。 3、目标可量化,(用合理的评估机制来监控展会的绩效)。 ——通常企业参加展会的目标: 1. 接触新客户 2. 提升企业形象 3. 与顾客互动 4. 促销现有产品 5. 新品发布 6. 获取竞争对手的情报 7. 赶超竞争对手 8. 提升士气 9. 与分销商互动 10. 常规性的市场研究 11. 获取销售订单 12. 接触新的分销商 第二阶段:确定参加哪个展会

1、可供选择的展会的数量。[某些行业每年仅有一两次比较合适的展会] 2、展会的参观者概况。大多数展会的主办方都会根据上一年的情况提供有关这方面的信息[但主办方不会给你提供消极的数据] 3、展会成本 4、理想场所的理想位置的可获得性 5、展会同公司的运营周期以及其他沟通项目相关的时间选择问题 6、参展企业的大致概况[调查自己的竞争对手] 7、展会的声望水平 第三阶段:展会展台工作人员配置策划: [大多数经理人倾向于把销售人员作为展台的主要工作人员配置,但这种做法的缺点在于他会影响销售人员的正常工作。而且,研究表明,大多数的参观者实际上并不是来展览会买东西的,他们来展会的目的更可能只是搜集购买决策所需的信息,因此,把技术人员或客服人员作为展台的主要人员配置,只留差不多一名销售人员负责应对买家及收集线索,这样做效果可能会更好(除非展会本身就是销售性质的)] 第四阶段:展会支持性促销活动策划: [包括给预期参观者的DM广告、展会前的广告攻势、行业杂志或消费者杂志上的新闻稿以及由销售人员负责的会

二、相关概念 1、营销的直接含义 (1)西方表述(美国市场营销协会委员会):引导商品和劳务从生产者手中到达消费者手中所实行的一种商业活动。 (2)习惯表述:个人或集体通过交易其创造的产品或价值,以获得所需之物,实现双赢或多赢的过程。(3)科学表述:以满足顾客需求为出发点, 从目标市场出发,采取有效的市场营销组合来创造利润,并有意地激发和引导需求,从而进一步使顾客潜在购买力转变为产品或服务的有效需求的管理过程。 2、营销的相关含义 (1)需要、欲望、需求 1)需要:生理或心理的一种匮乏状态。 2)欲望:人们达到某种东西的愿望。 3)需求:有支付能力的购买力欲望。 (2)产品:能引起消费者注意的、通过交换、消费、使用可满足需要的任何事物(包括有形的东西、无形的服务、能满足消费者需求的一切载体)。 1)核心产品:产品的使用价值(产品的用途、真正购买的是什么)。 2)有形产品:产品的外部形态(核心产品借以实现的形式—具有质量水平、特点、风格、品牌名称、包装五个特征)。 3)延伸产品:附加利益和服务。 (3)交换:两方或多方把有价值的东西交给另一方以满足需要的过程。 (4)市场 1)营销含义:有某种特定需要或欲望并有支付能力的全体潜在消费者。 2)一般含义:进行商品交换的场所。 3)经济学含义:生产某种产品的生产者与共同决定该产品价格的消费者的集合。 (5)营销组合 1)基本含义:企业为了满足目标市场的需要,综合考虑各个可控因素后制订的一整套市场营销方案。 2)组成要素:产品、价格、促销、分销。 3、策划含义 (1)策划:与计谋相关的一种行为过程和方法系统。 (2)会展策划:一种对会展项目的进程以及会展项目的总体战略进行前瞻性规划的活动。 4、活动含义 1)基本含义:由共同目的联合起来并完成一定社会职能的动作的总和。 2)结构层次:活动由目的、动机和动作构成,具有完整的结构系统。 3)表现组成:会议、展览、节事、赛事、演艺、旅游等。 4)条件功能:可信度、关联度、传达力、吸引力、执行力 5、策划条件 (1)信息资料(2)精干人才 (3)自身实力(4)客观资源(5)市场机会 三、市场营销理念的演进过程 1、生产观念 (1)形成时间:18世纪60年代 (2)主要表现 1)指导思想:以生产为中心 2)精力重心:大量生产,力求产品标准化,通过降低成本而获利。 2、产品阶段 (1)形成时间:19世纪中后期 (2)主要表现: 1)指导思想:以品质为中心 2)精力重心:产品创新、不断提高产品的质量 3、销售观念 (1)形成时间:20世纪30年代后期

筠连县分水岭煤业有限责任公司 井 下 高 压 电 缆 热 稳 定 性 校 验 计 算 书 巡司二煤矿 编制:机电科 筠连县分水岭煤业有限责任公司

井下高压电缆热稳定校验计算书 一、概述: 根据《煤矿安全规程》第453条及456条之规定,对我矿入井高压电缆进行热稳定校验。 二、确定供电方式 我矿高压供电采用分列运行供电方式,地面变电所、井下变电所均采用单母线分段分列供电方式运行,各种主要负荷分接于不同母线段。 三、井下高压电缆明细: 矿上有两趟主进线,引至巡司变电站不同母线段,一趟931线,另一趟925线。井下中央变电所由地面配电房10KV输入。 入井一回路:MYJV22-8.7/10KV 3*50mm2--800m(10KV) 入井二回路:MYJV22-8.7/10KV 3*50mm2--800m(10KV) 四、校验计算 1、井下入井回路高压电缆热稳定性校验 已知条件:该条高压电缆型号为,MYJV22-8.7/10KV 3*50mm2 ,800m,电缆长度为800m=0.8km。 (1)计算电网阻抗 查附表一,短路电流的周期分量稳定性为 电抗:X=0.072*0.8=0.0576Ω; 电阻:R=0.407*0.8=0.3256 Ω; (2)三相短路电流的计算

A Z I 5.174693305 .0310000 3v 3=?== ∞ (3)电缆热稳定校验 由于断路器的燃弧时间及固有动作时间之和约为t=0.05S; 查附表二得热稳定计算系数取K=142; 故电缆最小热值稳定截面为 23mm 51.2705.0142/5.17469t )/(min ===∞)(K I S Smin<50mm 2 故选用 MYJV 22 -8.7/10KV 3*50 电缆热稳定校验合格,符合要求。 附表一:三相电缆在工作温度时的阻抗值(Ω/Km ) 电缆截面S (mm 2 ) 4 6 10 16 2 5 35 50 70 95 120 150 185 240 交联聚乙烯 R 4.988 3.325 2.035 1.272 0.814 0.581 0.407 0.291 0.214 0.169 0.136 0.11 0.085 X 0.093 0.093 0.087 0.082 0.075 0.072 0.072 0.069 0.069 0.069 0.07 0.07 0.07 附表二 不同绝缘导体的热稳定计算系数 绝缘材料 芯线起始温度(° C ) 芯线最高允许温度(°C ) 系数K 聚氯乙烯 70 160 115(114) 普通橡胶 75 200 131 乙丙橡胶 90 250 143(142) 油浸纸绝缘 80 160 107 交联聚乙烯 90 250 142

天津农学院 会展经济学期末考试论文新加坡会展业的营销策略分析 学生姓名陈瑞 学院人文学院 专业班级2011级旅游管理专业1班 学号 1107074117 指导教师高书军 成绩评定 2014年6月

新加坡会展业的营销策略分析 陈瑞 (天津农学院人文学院 11旅游1班) 摘要:新加坡享有“国际会展之都”的美誉,是亚太地区举办会展和进行商务、休闲旅游的首选地。被国际协会联合会评为世界第五大“会展之都”。本文就新加坡会展业的发展和现状,分析其发展的营销策略,总结可以学习的成功经验、方法。 关键词:会展新加坡营销策略成功经验 1 新加坡会展业发展现状 新加坡是位于东南亚马来半岛南端的一个城市型岛国,地处太平洋与印度洋航运要道马六甲海峡入口、东南亚地区的中心,堪称“亚洲的十字路口”,地理位置十分重要。新加坡会展业发展始于20世纪70年代,政府部门高度重视会展业发展,加上很高的国际开放度、有利的地理区位优势、完善的城市基础设施以及高水平的服务业水准,诸多因素导致新加坡会展旅游蓬勃发展。 新加坡会展国际客源市场主要集中在亚太地区(2001年亚太地区客源市场占总客源比例高达61%%),日本是其最大的客源国,其次是欧洲和美洲。会展旅游直接收入达22亿新元,而带动关联产业发展的间接收入则更是可观。据有关部门测算,新加坡会展业投入产出比例高达1:12。 会展经济强化了新加坡作为亚洲航空和海运中枢、地区政治中心、金融中心、商业和服务业中心的地位。2003年新加坡共举办国际、国内大型会议500多个,会议范围涉及制造、信息技术、能源、家具、食品、医疗、健康、快速消费品、服务等行业。知名展会有亚洲国际通讯和资讯科技展览、亚洲航空展和新加坡国际家具展等。新加坡拥有众多先进完善的会展设施,新加坡博览中心、新达新加坡国际展览与会议中心及莱佛士会议中心是新加坡三大会展中心。 新加坡会展业的快速发展也为其在国际会展市场赢得了众多盛誉:连续19年(1984年至2002年)荣获国际协会联盟颁布的亚洲最佳会议城市;连续3年(2000年至2002年)荣获国际协会联盟颁发的世界最佳会议城市第五名;2003年在全球10个最杰出的国际会议城市中,新加坡赢得全球第三大会议城市的美誉。 2新加坡会展业发展的优势分析 2.1地理环境优越,气候宜人,交通便利 地理位置优越,风景优美,被称为“亚洲的新加坡地处马六甲海峡的入口”,全年

目录 前言 (1) 一、展会时间 (1) 二、展会地址 (1) 三、策划目的 (1) 二、营销环境分析 (2) (一)宏观与微观环境分析 (2) (二)农机展览的SWOT分析 (2) 三、STP战略 (3) (一)市场细分 (3) (二)目标市场能够选择与市场定位 (3) 四、营销组合策略制定 (4) (一)产品营销策略 (4) (二)价格营销策略制定 (4) 1.考虑影响农机价格因素 (4) 2.掌握定价方法 (4) (三)渠道营销策略制定 (5) 1.选择适当的中间商 (5) 2.监控中间商确定生产量 (5) (四)促销策略的制定 (5) 五、宣传与服务 (6) 六、总结 (6)

《黑龙江省农业机械展览会2016年度营销策划方案》 前言 随着会展业的快速发展,众多的中小型企业不断地参加到会展的行列。也有不少企业希望通过参加展会来提高知名度。通过展会来挖掘潜在顾客。为企业宣传造势,是不少企业的做法。黑龙江省农业机械展览会有很大的影响力,各企业正好可以通过这个平台来提升自己的品牌知名度,进而进驻更多,更大的市场。黑龙江农业机械展览会在哈尔滨举办是最正确的选择,黑龙江拥有肥沃的黑土地,有庞大的销售市场,农机的市场潜力是巨大的。我国农业发展势头迅猛,而农业的发展离不开农用机械的发展,农机发展水平的代表着一个国家农业发展态势。农业的发展也需要科技的进步,此次展览会不仅是为了展览和销售,更是为了科技的交流和学习的。 一、展会时间 2016年5月27日至30日 二、展会地址 黑龙江省哈尔滨市会展中心 三、策划目的 2016年中国黑龙江省农业机械展览会于2016年5月27日至30日在哈尔滨会展中心举办。农机领域“三巨头”——中国农机流通协会、中国农机工业协会、中国农机化协会4月23日联合在黑龙江省会哈尔版发布新闻宣布,2016年中国黑龙江省农业机械展览会由黑龙江省人民政府、黑龙江省商务厅主办。本次展会主要目的是进行农业机械的品牌推广和机械的买卖。本次展会要求划分更加专业、布局更加合理。本届展会展区总面积12万平方米,比上届增加了2万平方

井下高压开关、供电电缆动热稳定性校验 一、-350中央变电所开关断路器开断能力及电缆热稳定性校验 1 23 G 35kV 2 Uz%=7.5△P N.T =12kW △P N.T =3.11kW S N.T =8MVA 6kV S1点三相短路电流计算: 35kV 变压器阻抗: 2 22.1. u %7.5 6.30.37()1001008z N T N T U Z S ?===Ω? 35kV 变压器电阻:2 22.1.22. 6.30.0120.007()8 N T N T N T U R P S =?=?=Ω 35kV 变压器电抗:10.37()X = ==Ω 电缆电抗:02(x )0.415000.08780 0.66()1000 1000i L X ??+?== =Ω∑ 电缆电阻:02(x )0.11815000.118780 0.27()1000 1000 i L R ??+?== =Ω∑ 总阻抗: 21.370.66) 1.06( Z ==Ω S1点三相短路电流:(3)1 3.43()d I KA === S2点三相短路电流计算: S2点所用电缆为MY-3×70+1×25,长400米,变压器容量为500KV A ,查表的:(2)2d I =2.5KA

S2点三相短路电流:32 d d =2.88I I KA = 1、架空线路、入井电缆的热稳定性校验。已知供电负荷为3128.02KV A ,电压为6KV ,需用系数0.62,功率因数cos 0.78φ=,架空线路长度1.5km ,电缆长度780m (1)按经济电流密度选择电缆,计算容量为 3128.020.62 2486.37cos 0.78 kp S KVA φ?= ==。 电缆的长时工作电流Ig 为239.25 Ig === A 按长时允许电流校验电缆截面查煤矿供电表5-15得MYJV42-3×185-6/6截面长时允许电流为479A/6kV 、大于239.25A 符合要求。 (2)按电压损失校验,配电线路允许电压损失5%得 60000.1300Uy V ?=?=,线路的实际电压损失 109.1L U COS DS φφ?====,U ?小于300V 电压损失满足要求 (3)热稳定性条件校验,短路电流的周期分量稳定性为 电缆最小允许热稳定截面积: 3 2min d =S I mm 其中:i t ----断路器分断时间,一般取0.25s ; C----电缆热稳定系数,一般取100,环境温度35℃,电缆温升不超过120℃时,铜芯电缆聚乙烯电缆熔化温度为130℃,电

浅谈会展网络营销特点和操作方式 互联网在展会行业来说,早就不再是一个新鲜事物。展会官方信息网站,在当前已然是会展营销的基本配置,也可谓是展会主办机构对互联网的基本理解和应用。 随着互联网在中国这20余年的飞速发展,大数据应用,云计算技术、AR/VR技术的日益完善,甚至AI技术的发展,对会展网络营销的价值也不断发起着挑战和冲击。 会展网络营销是会展企业整体营销战略的一个重要组成部分,是为实现企业总体经营目标所进行的,以互联网信息技术为基础手段进而营造网上经营环境的各种活动。 会展网络营销就是建立在会展企业营销的整合营销组合上,然后利用互联网信息技术去更快速的发布(如快速发布展会资讯,发布招商信息,观众报名通道等),或者利用网络技术实现企业更灵活的营销活动(如积分兑换、推荐有奖、折扣抢占展位等)。 如果我们从网络营销(互联网)思维性上开始改变,大胆的利用和发挥网络的优势和特征,就能真正迅速地建立起有自己特色的会展服务和新竞争力,信息技术的发展正在变革着传统会展业。 【会展网络营销具有哪些特点?】 会展网络营销具有传统会展营销根本不具备的许多独特的、鲜明的特点,具体表现在: 1.地域的全球性。互联网的发展,使得全球网络资源得以共享。它决定了会展网络营销信息的无地域、无时间限制的全球化传播。同时也决定了,会展网络营销效果的全球性,这种市场格局的全球化特点带来的是更大的范围内的潜在客户群体和成交的可能性。在互联网经济时代来临之前,是没有任何一种营销方式能够实现这种跨越时空限制营销的。 2.资源的整合性。在会展网络营销的过程中,可以对多种资源进行整合,可以对多种营销手段和营销方法进行整合,更可以对有形资产和无形资产的交叉运作和交叉延伸进行整合。如:

会展营销策略 1.市场调查和定位策略 对于举办一个成功的会展,市场调查是必不可少的,在确定会展项目以前,必须进行深入的市场调查。调研主要针对有参展需求的参展商,还有要了解这些展会信息的人群,寻求“买与卖”的结合,并着眼于未满足而竞争对手较弱的市场。 市场调查还要掌握地区经济、地理方面的优势,使之充分为会展服务。在掌握了市场信息的基础上,确定会展的定位,是走综合性的会展道路还是走专业性的会展道路。 综合性的会展是指将各个产业、行业与内外贸结合的交易会、博览会或大型国际会议;专业性会展是指以某一个产业或者行业为依托举办的交易会、博览会或大型会议。前者以“广交会”为例,其宣传口号为“来到‘广交会’就可以找到中国大多数的出口商品”,后者以“高交会”和宁波“中国国际男装展”为例,一个是高新技术产品的展会,而另一个的细分更加明确。 2.打造会展品牌 中国会展业缺乏品牌意识,会展企业鱼龙混杂,竞争无序性带来整个行业的效率低下与恶性循环,行业缺乏品牌企业和品牌会展,缺少领头羊。 以上海为例,国际性会展每年高达300多场,曾经出现暑假期间,面向儿童推出三个卡通展的情况,展期接近,题材重复,各展会规模上不去,效益也打了折扣。参展商面对众多的招展函不知所措,不知道该信赖谁家。 而在国外,多年的市场竞争已经实现了优胜劣汰,打造出不少品牌会展,如汉诺威工业博览会,科隆国际博览会,法兰克福国际博览会等等,许多出色的品牌展览公司都有自己独家的领域,例如美国的夏洛特展览公司专门举办针对妇女、家庭用品和草坪、农场用品的展会;Weathersfield展览公司主要从事鲜花、礼品和户外体育活动用品展。 3.注重服务营销 服务是会展业的生命和根本所在,没有一流的服务就不可能有一流的会展,因此,从立项、招展、办展到会展结束,都必须贯穿良好的服务意识。 要做好展前的信息发布,帮助参展商做好展馆展台的布置工作和展场企业的广告宣传,设置展场的各类咨询服务。有的会展中参展商遇到了金融、法律、会计等方面的问题不知该如何解决,影响了参展效果。举办各种洽谈会、主题研讨会,交流信息,创造商机,“广交会”设立跨国定点采购专区的做法很值得借鉴。设立海关、商检的绿色通道,为参展商提供便利;提供运输、保险、翻译等各方面的服务。 最重要的然而也往往容易被忽略的一点是会展结束后的后续服务问题,这需要我们建立参展商、观展商的资料库,保持会后的联络,了解他们的意见和建议,便于日后改进工作,现在要做到这一点对于我国一些会展经营者来说,有一定的难度,但对于有品牌意识和长远发展打算的公司来说是非常重要的。 4.制定网络营销策略 电子商务已经发展到相对成熟的阶段,网上展览也已经为众多的展会所采用。会展本身具有集中性和实物性,但这也决定了其时空的有限性,即它是在某段时间在某地集中举行。但是开辟网上会展则可以突破这些限制,除了在会展举办期间作为主场的有利补充之外,它还可以提供全天候、跨地域、跨国的会展环境,为各国贸易商提供一个丰富、开放、全息的信息交流场所。在网上会展中,只要输入自己想要的产品信息,就会有众多相关供应商的资料提供给你。当然这也需要展会经营者从观念到技术都不断更新,并保证网上会展的时效性。 【拓展知识】 科技人文并进-杭州休博会

第三章会展项目策划 (一)会展项目策划概述 1、识记: (1)项目的含义和特征(73) 1)含义:项目是一项为了创造某种独特的产品或者服务而进行的有时限性的工作。(或者说,是在既定的资源和要求的约束下,为实现某种目的而相互联系的一次性工作任务。) 2)特征: ①项目的唯一性 ②项目的时限性 ③项目的整体性 ④资源成本的约束性 ⑤明确的目的性 ⑥项目的生命周期性 ⑦项目的冲突性 补:项目管理的四个阶段 启动、规划、执行、结束 (2)会展项目管理的程序(77) ①启动程序块:确认一个项目或者一个阶段可以启动,并要求着实实行 ②规划程序块:为实现启动过程提出目标而制定计划,保持一份可操作的进度安排 ③执行程序块:组织、协调人员和其他资源,执行计划 ④控制程序块:监控、测量项目的进程,并在必要的时候采取纠正措施,以确保启动阶段时提出的目标得以实施。 ⑤结束程序块:通过对项目或项目阶段成果的正式认可,以使从启动阶段开始的这一周期有条不紊地结束。 (3)会展项目策划含义(79) 会展项目策划就是为了实现会展项目的具体目标,以客观的市场调查和市场定位为基础,以独特的题材和主题概念设计为核心,综合运用各种策划手段,按一定的成效,对项目进行创造性的规划,并以具有可操作性的策划文本作为结果的活动,提出创造性的思维对策,并制定出具体的实施计划。它包括:选题策划、主题策划、营销策划、运行管理策划、后期策划等。 2、领会: (1)会展项目策划的特点(79) 1)系统性 2)社会性 3)创造性 4)超前性 5)服务性 6)高风险 (2)会展项目策划内容(81)

市场调研、项目市场细分、题材的选择、项目策划的创意、项目的可行性研究、立项策划书的撰写。 3、应用 (1)举例分析会展项目策划流程(81) 项目调研——项目识别(项目题材的选择)——项目可行性研究——立项策划书的撰写——项目实施方案的策划——项目策划结果的验证 (二)市场细分和项目识别 1、识记 (1)市场分析和市场细分的含义(82) 1)市场分析,是指对影响市场运行的各种因素,运用一定的方法进行综合分析,旨在通过市场分析,为企业增强竞争能力,获取生存和发展技能服务。 2)市场细分,一个市场的顾客是有差异的,他们有不同的需要,寻求不同的利益,企业应该对市场加以区分。 (2)会展题材的调整的意义(85) 会展题材要根据产业和产品的生命周期适时进行选择和调整,实时跟踪展会所属行业的最新动态,适时通过新立、分裂、拓展和合并等方式调整展会题材,才能使展会失重保持强大的生命力。会展的调整体现出企业本身的产品创新、管理创新和营销创新能力,创新的目的在于让会展企业获得竞争优势从而令展会项目在此走向成长之路。 2、领会: (1)展览题材的选定(84) 1)新立题材。指办展机构从来没有涉及的产业作为举办新展览会的展览题材。 2)分列题材。就是说办展机构将已有的展览会的展览题材再做进一步的细分,从原有的大题材中分列更小的题材,并将这些小题材办成独立的展览会的一种选择展览题材的方式。3)拓展题材。就是将现有展览会所没有包含的,但与现有展览会的展览题材有密切关联的题材,或者是将现有展览会展览题材中暂时还未包含的某一分题材列入现有展览会展览题材的一种方法。 4)合并题材。就是将两个或两个以上彼此相同或有一定关联的展览题材的现有展览会合并为一个展览会,或是将两个或两个以上的展览会中彼此相通或有一定关联的展览题材剔除出去,放在另一个展览会里统一展出。 (2)会议的主题的选择范围 3、应用 (1)说明会展项目市场细分的程序(83) 1)划定细分范围 2)确认细分依据 3)权衡细分变量,变量可分为:地理区域细分、人口统计细分、心理细分、行为细分 4)实施市场调查 5)评估细分市场,可以根据以下四方面评估:细分市场的规模和发展潜力、细分市场的赢利能力、细分市场的结构吸引力、会展举办机构自身的目标和资源

*作品编号:DG13485201600078972981* 创作者:玫霸* 筠连县分水岭煤业有限责任公司 井 下 高 压 电 缆 热 稳 定 性 校 验 计 算 书 巡司二煤矿

编制:机电科 筠连县分水岭煤业有限责任公司 井下高压电缆热稳定校验计算书 一、概述: 根据《煤矿安全规程》第453条及456条之规定,对我矿入井高压电缆进行热稳定校验。 二、确定供电方式 我矿高压供电采用分列运行供电方式,地面变电所、井下变电所均采用单母线分段分列供电方式运行,各种主要负荷分接于不同母线段。 三、井下高压电缆明细: 矿上有两趟主进线,引至巡司变电站不同母线段,一趟931线,另一趟925线。井下中央变电所由地面配电房10KV输入。 入井一回路:MYJV22-8.7/10KV 3*50mm2--800m(10KV) 入井二回路:MYJV22-8.7/10KV 3*50mm2--800m(10KV) 四、校验计算 1、井下入井回路高压电缆热稳定性校验 已知条件:该条高压电缆型号为,MYJV22-8.7/10KV 3*50mm2 ,800m,电缆长度为800m=0.8km。 (1)计算电网阻抗 查附表一,短路电流的周期分量稳定性为

电抗:X=0.072*0.8=0.0576Ω; 电阻:R=0.407*0.8=0.3256 Ω; (2)三相短路电流的计算 (3)电缆热稳定校验 由于断路器的燃弧时间及固有动作时间之和约为t=0.05S; 查附表二得热稳定计算系数取K=142; 故电缆最小热值稳定截面为 Smin<50mm2故选用 MYJV22 -8.7/10KV 3*50 电缆热稳定校验合格,符合要求。 附表一:三相电缆在工作温度时的阻抗值(Ω/Km)

XX展会的品牌化营销策略分析 中国会展业发展迅速,各地不断推出的各式各样的展会,从宏观来说,为提升我国制造业水平、为打造城市靓丽名片、为加强我国工商界人士的国际交流和拓展国际空间提供了非常有效的平台;但由于展会运营机构办展水平参差不齐,其中的一些展会未能获得好的经济效益和社会效益。究其原因,可发现在展会组织和安排中蕴含着非常多的问题。而此时,品牌展会的提出对于会展业指明了一个很好的发展方向。本文的重点旨在以XX展览股份有限公司为平台,通过对其所操办的展会现状分析,以知名展会品牌为标准,找到其展会品牌化发展过程中存在问题,最后重点提出切实可行的品牌化展会发展策略。 1.品牌展会的概念与评价标准 品牌展会是指那些形象鲜明,服务优质,知名度和美誉度高的展会。品牌展会的实质是展会项目的差异化,这种差异化,是建立在满足参展客商需要,定位清晰,形象鲜明,卓有成效的基础上。 对于一个展会而言,品牌创立从成长到成熟,是一个长期的品牌战略管理过程,其中凝聚了展会主办方大量的心血,智慧和个创新。一个品牌展会的打造,需要有明确的品牌战略,以及相应的实施策略,包括品牌定位,品牌形象树立,品牌经营和品牌文化形成等。 用什么标准评价一个展会是否是品牌展会?迄今为止,国际国内没有统一的标准。综合业内人士的看法,结合我国的实际,满足以下五个条件的展会可称为品牌展会。 第一,良好的展会举办地及场馆。展会举办地城市的环境美化、交通运输、酒店服务、消费娱乐等是否良好,展馆是否能够提供舒适的展示空间、优质的设施服务等是吸引客商参展的重要因素。 第二,形成规模效应。品牌展会必须是在同类型或同行业展会中规模大的展会,在展览期间,整个行业众多有实力的卖家、买家和中介齐聚一堂。有规模效应的展会,意味着大批的产品供应商和采购商参展,且能提供几乎涵盖整个专业市场的所有信息,以及由此降低的组展商单位成本,和其他各方投入产出比率的增加。 第三,一流的展会服务。展会服务贯穿于组展商的整个运营过程,从市场调研、主题立项、寻求合作、广告宣传、招展手段、观众组织、活动安排、现场气氛营造、展后服务,甚至包括所有对外文件和信函的格式化、标准化等,都须具备高的专业水准和从业人员的严谨处事态度,服务过程体现高效和细致。 第四,媒体的强力合作。有影响力媒体的强力合作是展会影响力的重要保障。一个展会要成功举办,并发展成为品牌展会,媒体宣传报道充分与否至关重要;展会品牌的形成需要媒体的大量的正面报道;媒体的权威性和可信度,亦有助于提升展会的知名度和美誉度。反过来,品牌展会也会在一定程度上吸引众多媒体的关注。 第五,得到政府的大力支持。在我国目前的体制现状下,能得到政府支持的展会,往往能获得良好的综合效益,包括经济和社会效益。这样的展会,展会运营机构在政府的支持和帮助下,能整合更多的资源,从而能为参展客商提供更多的实惠和便利,办展质量往往较高,展会的品牌影响力更容易扩张。 2.品牌展会营销现状 中国展览业现状具有五大特点:展览项目持续增长,数量扩张明显;展馆建设方兴未艾,成为城市必要设施;展览主办多元发展,政府主导色彩浓烈;展览地区集中程度高,经济发达地区领先;展览直接收入增长缓慢,社会经济效益驱动。 XX展览股份有限公司是本地最早从事会展服务的公司,其所操办的XX订货会已成 功连办了十七届。该项展会为全国建筑行业的新产品和新技术在河北乃至华北地区的推广

《会展营销策划与管理》试题集 第一章会展营销概述 一、单选 1.会展营销是以( A )的需求为中心的服务营销活动。 A.参展商与观众 B.组展商与参展商 C.组展商与观众D.赞助商与观众 2.( B )是成功举办一个会展项目的核心环节。 A.宣传工作 B.营销工作 C.赞助工作D.定价工作 3.( D )是会展营销的起点,也是提高营销针对性的重要手段。 A.树立会展营销理念 B.研究会展产品 C.确定会展营销工具 D.研究会展目标客户的决策行为 4.会展行业营销人员的基本功是( C )。 A.如何推销展位 B.如何组织观众 C.如何处理客户关系 D.如何对产品宣传和定价

5.( D )是指展览会的核心功能通过哪些具体形式表现出来并传达给目标顾客。 A.基本要素 B.核心要素 C.附加要素 D.形式要素 6.以下说法不正确的是( B )。 A.会展项目宣传推广包括选择宣传推广目标对象、选择合适的宣传手段、准备宣传资料和展览会的联合推广与促销等环节 B.会展项目的宣传推广只需针对参展商 C.参展的厂商数量一般应该与会展的计划规模相适应 D.组展者要结合财务预算确定宣传的范围和力度 7.会展行业使用最广泛的宣传方式是( A )。 A.直邮 B.广告宣传 C.人员推广 D.新闻报道 8.会议、表演、评奖等属于( C )宣传方式。 A.广告宣传 B.新闻报道 C.公关活动 D.路演 9.国际大会和会议协会(ICCA)属于( B )。 A.政府有关部门 B.行业协会、学会等有关组织 C.驻外使领馆 D.专业化商业中介组织 10.展览会的定价方法主要是指( D )。 A.门票的定价方法 B.赞助费的定价方法 C.广告的定价方法 D.展位的定价方法 11.绝大多数会展企业展览会的价格都是以( B )为基础测算出来的。A.组展企业运行成本 B.展会项目成本 C.行业平均成本 D.展位租赁成本 12.( A )是一种按照会展项目所花费成本的高低来决定展位价格的方法。