基于ARM+μC/OS-II的嵌入式数据采集系统设计

宋苗,王博,黄秋燕

中国矿业大学信电学院,江苏徐州(221008)

E-mail:miao.315@https://www.doczj.com/doc/838854645.html,

摘 要:比较了常见的几种数据采集系统方案,说明了基于ARM的嵌入式系统方案的优势。通过移植μC/OS-II操作系统到硬件平台上,将Samsung S3C44B0X和μC/OS-II操作系统设计相结合设计成了一个集多通道数据采集、LCD波形数据显示、UART通信、人机界面控制的嵌入式实时数据采集系统。

关键字:μC/OS-II;ARM;数据采集;嵌入式系统

1. 引言

嵌入式系统是以应用为中心,以计算机技术为基础、软件硬件可裁剪,运用于应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。用以实现对其它设备的控制、监视和管理等功能。嵌入式系统所用的计算机是嵌入到被控中心的专用微处理器,这与通用的计算机不同,它必须适合被嵌入对象的工作环境,如以上提到的:体积、功耗、成本和稳定性等参数;嵌入式系统可以根据实际需要剪裁所用的软硬件[3]。

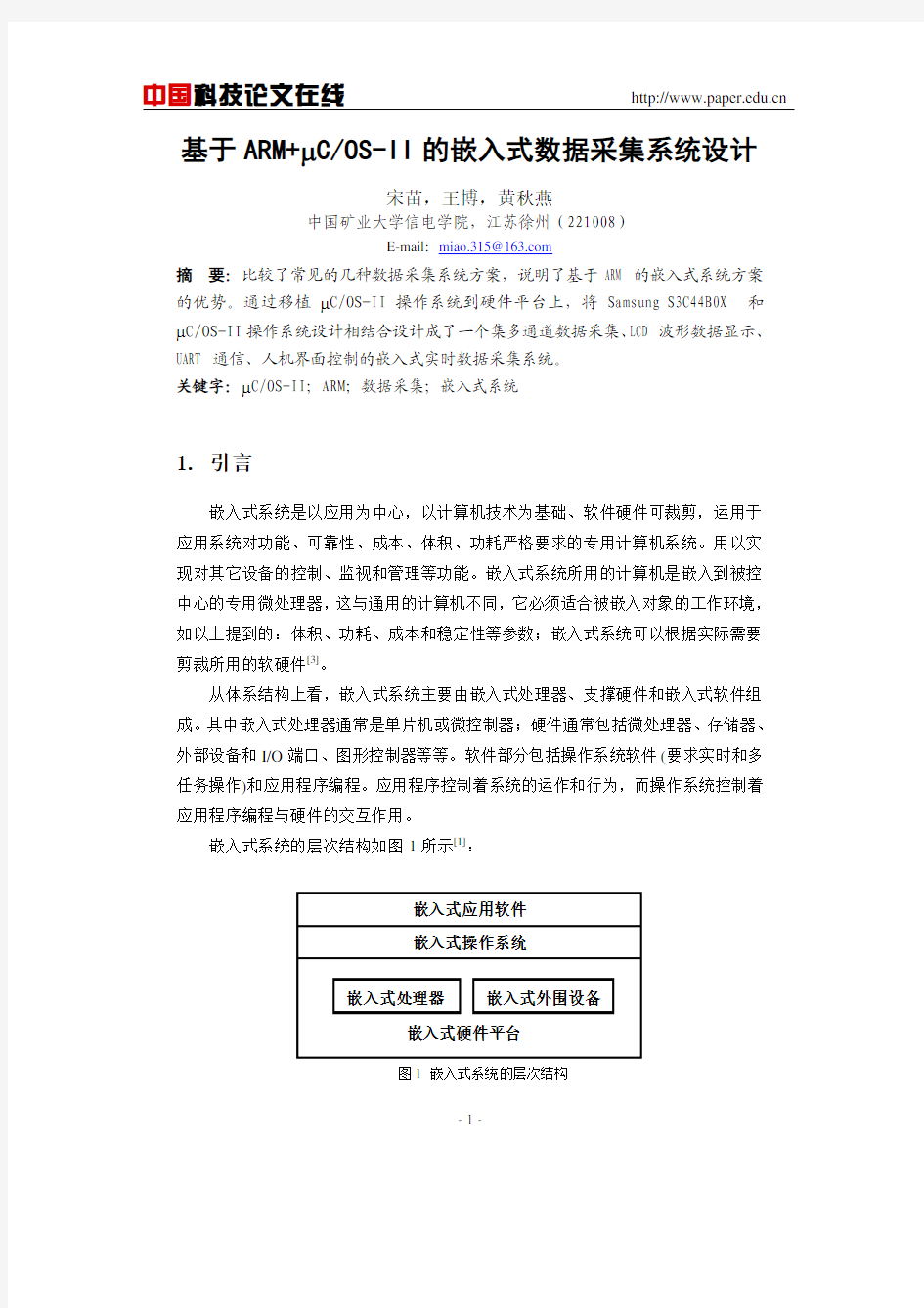

从体系结构上看,嵌入式系统主要由嵌入式处理器、支撑硬件和嵌入式软件组成。其中嵌入式处理器通常是单片机或微控制器;硬件通常包括微处理器、存储器、外部设备和I/O端口、图形控制器等等。软件部分包括操作系统软件(要求实时和多任务操作)和应用程序编程。应用程序控制着系统的运作和行为,而操作系统控制着应用程序编程与硬件的交互作用。

嵌入式系统的层次结构如图1所示[1]:

图1 嵌入式系统的层次结构

- 1 -

本文设计的通过在Samsung S3C44B0X上移植μC/OS-II操作系统,从而实现基于ARM和μ C/OS-II操作系统的优点的数据采集系统,通过对操作系统的任务和优先级的划分定义实现多通道数据采集、LCD波形数据显示、UART通信、人机界面控制。

2. 数据采集系统方案设计

基于嵌入式系统的数据采集在目前常用的有

1、基于MCU的数据采集系统方案

2、基于数据采集卡技术方案

3、基于PLC的技术方案

4、基于嵌入式ARM微处理器的技术方案

对上述四种方案进行了一番比较和分析:第一种基于MCU的数据采集系统方案,虽然成本低,技术成熟,但是一般采用装置大多采用8位或16位单片机,位数小、时钟频率低、指令执行时间长、内存小,不能运行实时操作系统,因此不能胜任数据采集的实时性以及各种附加功能要求。

第二种基于数据采集卡和工控机的方案,虽然具有速度快、开发周期短等优点,但由于硬盘和操作系统的使用,存在可靠性和稳定性较差的问题,另外成本较高;

第三种基于 PLC的方案,可以采用多个数据采集模块以实现多功能的采集,并且开发方便,但PLC与上位机的数据传输速度受限制,通常是采用串口的接口形式,采样速度也不能达到要求,同时价格也比较昂贵。

第四种基于嵌入式ARM微处理器的方案,可以针对特定的应用,开发专用的系统,ARM核微处理器的主频可以达到l00MHz以上,可以满足高速数据采集的要求,通过以太网接口可以实现与上位机的高速数据传输,成本较低。

经过以上的比较和权衡之后,放弃了前三种方案,最终采用第四种基于嵌入式ARM微处理器的技术方案。

3. 硬件部分

数据采集系统的硬件构成:核心部分为Samsung的S3C44B0X微处理器是是三星公司专为手持设备和一般应用提供的高性价比和高性能的微控制器解决方案。并在ARM7TDMI核基本功能的基础集成了丰富的外围功能模块,便于低成本设计嵌

- 2 -

入式应用系统。

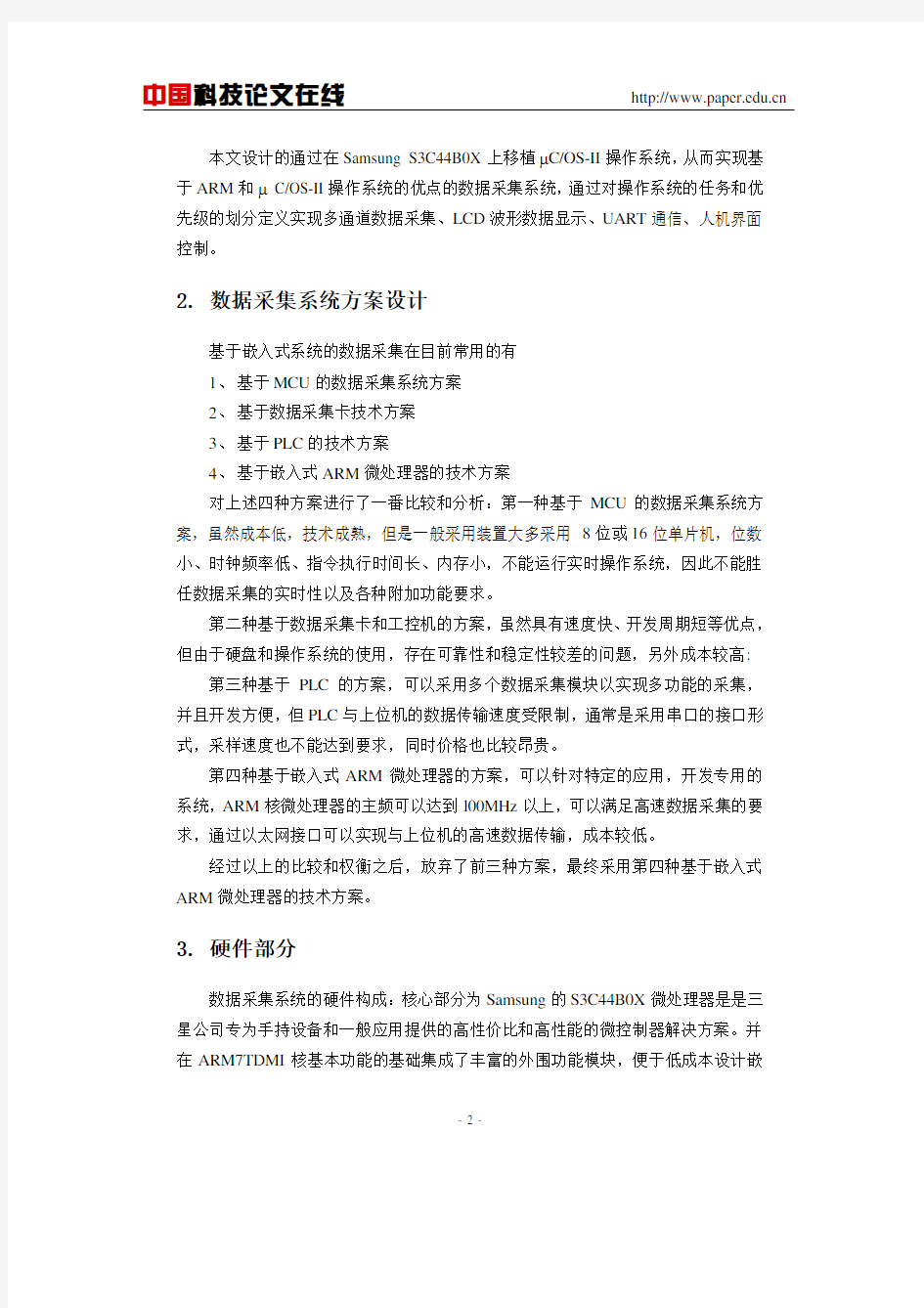

在实验中涉及到硬件平台的模块为:串口(UART)模块、LCD显示模块、A/D 数据采集模块、键盘扫描模块、JTAG接口电路模块。模块功能图如图2所示

图2 系统模块功能图

3.1 串口(UART)模块

S3C44B0X的UART(Universal Asynchronous Receiver and Transmitter),通用异步收发器)单元提供两个独立的异步串行I/O(SIO)口,都可以运行于中断模式或DMA模式。每个UART有7种状态:溢出错误,校验错误,帧错误,暂停态,接收缓冲区准备好,发送缓冲区空,发送移位缓冲器空,这些状态可以由相应的UTRSTA Tn/UERSTA Tn表示,并且与发送接收缓冲区相对应的有错误缓冲区。波特率的可以通过控制波特率寄存器(UBRDIVn)控制本开发平台提供两个串口UART0和UART1,最高传输速率为115200 bit/s。

3.2 LCD显示模块

S3C44B0X中具有内置的LCD控制器,它具有将显示缓存中的LCD图像数据传输到外部LCD驱动电路的逻辑功能。

S3C44B0X中内置的LCD控制器用于传输显示数据并产生必要的控制信号。除了控制信号,还有显示数据的数据端口VD[7:0]。LCDCDMA为专用DMA,它可以自动地将显示数据从帧内存中传送到LCD驱动器中。通过专用DMA,可以实现在不需要CPU介入的情况下显示数据。VIDPRCS从LCDCDMA接收数据,变换为合适的数据格式后通过VD[7:0]发送到LCD驱动器。TIMEGEN包含可编程的逻辑,以支持常见LCD驱动器所需要的不同的接口时间、速率要求。TIMEGEN部分产生

- 3 -

VFRAME, VLINE, VCLK, VM等信号。

3.3 A/D数据采集模块

ARM S3C440BX芯片自带一个8路10位A/D转换器,它是一个逐次逼近型的ADC,内部结构中包括模拟输入多路复用器,自动调零比较器,时钟产生器,10位逐次逼近寄存器。这个ADC还提供可编程选择的睡眠模式,以节省功耗。在电路中,对44B0X的AFEFT、AREFB、AVCOM引脚需要按照图3加上电容。

图3外部引脚配制

图4为S3C44B0X内部ADC的功能结构图

图4 S3C44B0X内部ADC 结构图

3.4 键盘扫描模块

键盘模块可能用来输入数字型数据或者选择控制设备的操作模式。它的实现有两种方案:一是采用现有的一些芯片实现键盘扫描;再就是用软件实现键盘扫描。

每个键被分配一个称为扫描码的唯一标识符。应用程序利用该扫描码,根据按下的键来判定应该采取什么行动。一个瞬时接触开关放置在每一行与一列的交叉点。矩阵所需的键的数目显然根据应用程序而不同。每一行由一个输出端口的一位驱动,而每一列由一个电阻器上拉且供给输入端口一位。在本系统使用ZLG7289A是一片

- 4 -

具有串行接口的,可同时驱动8位共阴式数码管(或64只独立LED)的智能显示驱动芯片,该芯片同时还可连接多达64键的键盘矩阵,单片即可完成LED显示﹑键盘接口的全部功能[7]。

4. 软件部分

4.1 μC/OS-II操作系统的移植

嵌入式操作系统μC/OS-II(microcontroller operating system)是专为微控制器系统和软件开发而设计的公开源代码的抢占式实时多任务操作系统内核,是一段微控制器启动后首先执行的背景程序,作为整个系统的框架贯穿系统运行的始终。μC/OS-II由于它的公开源代码,代码结构清晰,注释详尽,组织有条理,可移植性好,可裁剪,可固化,并且内核属于抢占式,最多可以管理60个任务,是一个经实践证明好用且稳定可靠的内核,对于对实时性和稳定性要求很高的数据采集系统来说,引入μC/OS-II无疑将大大改善其性能[6]。

要将μC/OS-Ⅱ操作系统应用到基于ARM的嵌入式系统上,就要进行移植。移植工作包括以下几个内容:

◇用#define 设置一个常量的值(OS_CPU.H)

◇声明10个数据类型(OS_CPU.H)

◇用#define 声明三个宏(OS_CPU.H)

◇用C 语言编写六个简单的函数(OS_CPU_C.C)

◇编写四个汇编语言函数(OS_CPU_A.ASM)

4.2 Boot Loader的设计

芯片的Boot Loader代码,就是芯片CPU复位后进入操作系统之前执行的一段代码,Boot Loader代码与芯片的内核结构,具体芯片和使用的操作系统等因素有关。其功能有点类似于PC机的BIOS程序,保证操作系统正常运行[4]。

Boot Loader 程序首先获得系统的控制权之后,对关键硬件自检没有发现故障并且控制台没有发出启用Shell Menu检测菜单的情况下,依据文件系统的管理和支持,从电子硬盘即16M NAND FLASH 中读取操作系统或应用程序的代码到SDRAM 的指定位置,然后把程序指针转移到该位置,从而使操作系统获得控制权,完成引导过程。Boot Loader的运行流程如图5所示:

- 5 -

图5 Boot Loader程序的流程图

4.3 建立μC/OS-Ⅱ扩展RTOS的文件系统

将μC/OS-Ⅱ移植到自己的硬件平台以后,接下来就是对操作系统本身的扩充。包括建立文件系统、为外部设备建立驱动程序并规范相应的API函数、创建图形用户接口(GUI)函数、建立其他实用的应用程序接口函数等。

硬件中有一片容量至少16M的NAND FLASH存储芯片作为嵌入式设备的固态数据存储器。该存储器由文件系统管理,在文件系统的功能函数与FLASH芯片之间有相关驱动程序实现高层系统功能和底层具体硬件的数据交换。

使用文件系统之前必须通过initOSFile()函数初始化文件系统,为文件缓冲区分配存储空间。在OSFile.h中定义了文件系统函数。用OpenOSFile()函数以指定模式打开文件;用ReadOSFile()函数读取已打开文件数据到指定缓冲区;用WriteOSFile()函数将指定缓冲区的数据写入到文件;用LineReadOSFile()函数读取文本文件的一行字符;用CloseOSFile()函数关闭文件,释放文件缓冲区;用SeekOSFile()函数定位文件指针;用DeleteOSFile()函数删除指定文件。由于有了文件系统,只须打开并读取指定文件到指定位置即完成了装载,然后把程序指针指向该位置即实现了控制的转移。

- 6 -

4.4 应用程序部分

对于应用软件部分根据整个装置实现的功能和对他的要求进行系统任务分割,并根据实际需要为各个任务分配优先级。系统大致可分为如下几个任务:主任务、显示任务、各通道的数据采集任务以及包含在数据采集任务中的通信任务。对应每个任务,需要编写相应的应用程序。系统的流程图为图6所示。

在本系统中任务划分和设定的优先级

已经定义的OS任务:

TCP监控任务,优先级为11;以太网物理层监控任务,优先级为8;触摸屏任务,优先级为9;键盘任务,优先级为10;LCD刷新任务,优先级为59;系统任务,优先级为1。

根据系统的功能实现,实时性和系统的数据要求我将应用程序的任务划分为6个,在main程序中创建主任务和显示任务;在主任务中创建AD采样通道0、1、2、3,考虑到系统各任务的关系和重要程度将应用程序任务定义为:

主任务,优先级12;显示任务,优先级25;AD采样通道0,优先级19;AD 采样通道1,优先级20;AD采样通道2,优先级21;AD采样通道3,优先级22。

- 7 -

图6 系统流程图

5、结束语

本文完成了基于32位ARM微处理器S3C44B0X和嵌入式实时操作系统μC/OS-Ⅱ的嵌入式数据采集系统的研究和设计。采用S3C44B0X嵌入式微处理器,可以使系统小型化,便于提高性能以及与各种外设连接扩展,同时降低了成本。μC/OS-II作为一个源代码公开的操作系统,在具体应用中稳定可靠。通过将嵌入式

- 8 -

实时操作系统μC/OS-Ⅱ和文件系统移植到ARM7微处理器上,并对其进行软件功能的扩充和硬件扩展,实现了一个集多通道数据采集、LCD波形数据显示、UART通信、人机界面控制的嵌入式实时数据采集系统的完整的嵌入式实时操作系统。

参考文献

[1]王田苗.嵌入式系统设计与实例开发-基于ARM微处理器与μC/OS-Ⅱ实时操作系统.北京:清华大学出版社,2003.10

[2]罗浩,谢华成. 一种新的基于ARM的数据采集系统设计. 信阳师范学院学报(自然科学版).2006,(4):203-205

[3]谭勋琼.基于ARM7+μC/OS-II的数据采集系统设计.《现代电子技术》,2005,(5):32-35

[4]周航慈,吴光文.基于嵌入式实时操作系统的程序设计技术.北京:北京航空航天大学出版社,2006.11

[5]李学桥,陈晓雷,郭功兵,李淑君.基于ARM的远程数据采集系统的设计与实现. 《仪表技术与传感器》,2004,(1):32-34

[6](美)Jean J. Labrosse;邵贝贝译.μC/OS-Ⅱ:原码公开的实时嵌入式操作系统.北京:中国电力出版社,2001.8

[7]Samsung Electronics. S3C44B0X RISC MICROPROCESSOR Data Sheet

Design of Embedded Data Acquisition System Based on

ARM and μC/OS-II

Song Miao, Wang Bo, Huang Qiuyan

School of Information Electrical Engineering, CUMT, Xuzhou, (221008, China)

Abstract

This paper explains the advantage of the ARM-based embedded systems by analyzing some common data collection system scheme, combined the μC/OS-II operating system with Samsung S3C44B0X by transplanted the μC/OS-II operating system to hardware development platform. This paper also designed a system which integrates the embedded system with data collection, waveform data displaying on LCD, UART communications, human-computer interface control.

Key words:μC/OS-II; ARM; Data Acquisition; Embedded system

作者简介:

宋苗,女,1985年生,硕士研究生,主要研究方向:嵌入式系统、电网谐波。

王博,女,1985年生,硕士研究生,主要研究方向:嵌入式系统研究、电网谐波

黄秋燕,女,1986年生,硕士研究生,主要研究方向:检测技术及自动化装置

- 9 -

简易数据采集系统设计 题目:二选一 1. 设计一个单片机控制的数据采集系统,要求A/D 精度12位,采样频率最高100KHz,输 入8路信号,分时复用A/D 芯片,将采集到的波形进行4K 的SRAM 存储,然后通过串行口发送给计算机 2. 设计一波形发生电路,计算机通过串行口向板卡发送波形电路,波形存储到板卡上的 SRAM 中,然后进行计算机控制的D/A 波形产生,板卡上用单片机进行控制 要求: 1. 选择器件,确定具体型号。 2. 画原理图。 3. 根据器件封装画PCB 图。 4. 写出相应的单片机和微机控制程序。 5. 写出详细的原理分析报告。 器件选择: TI 公司生产的8位逐次逼近式模数转换器ADC0809,8051,MAX232 原理图如下: 原理报告原理报告:: 采集多路模拟信号时,一般用多路模拟开关巡回检测的方式,即一种数据采集的方式。利用多路开关(MUX )让多个被测对象共用同一个采集通道,这就是多通道数据采集系统的实质。当采集高速信号时,A/D 转换器前端还需加采样/保持(S/H)电路。 待测量一般不能直接被转换成数字量,通常要进行放大、特性补偿、滤波等

环节的预处理。被测信号往往因为幅值较小,而且可能还含有多余的高频分量等原因,不能直接送给A/D 转换器,需对其进行必要的处理,即信号调理。如对信号进行放大、衰减、滤波等。 通常希望输入到A/D 转换器的信号能接近A/D 转换器的满量程以保证转换精度,因此在直流电流电源输出端与A/D 转换器之间应接入放大器以满足要求。 本题要求中的被测量为0~5V 直流信号,由于输出电压比较大,满足A/D 转换输入的要求,故可省去放大器,而将电源输出直接连接至A/D 转换器输入端。 关于A/D 转换器的选取: 1.转换时间的选择 转换速度是指完成一次A/D 转换所需时间的倒数,是一个很重要的指标。A/D 转换器型号不同,转换速度差别很大。通常,8位逐次比较式ADC 的转换时间为100us 左右。由于本系统的控制时间允许,可选8位逐次比较式A/D 转换器。 2.ADC 位数的选择 A/D 转换器的位数决定着信号采集的精度和分辨率。 要求精度为0.5%。对于该8个通道的输入信号,8位A/D 转换器,其精度为 8 0.39%2 ?= 输入为0~5V 时,分辨率为 8 50.019611 22Fs N V v ==?? Fs v —A/D 转换器的满量程值 N —ADC 的二进制位数 量化误差为 8 50.0098(1)2 (1)2 22Fs N Q V v = = =?×?× ADC0809是8位逐次逼近式模数转换器,包括一个8位的逼近型的ADC 部分,并提供一个8通道的模拟多路开关和联合寻址逻辑,为模拟通道的设计提供了很大的方便。

高速数据采集系统 设计

基于FPGA和SoC单片机的 高速数据采集系统设计 一.选题背景及意义 随着信息技术的飞速发展,各种数据的实时采集和处理在现代工业控制和科学研究中已成为必不可少的部分。高速数据采集系统在自动测试、生产控制、通信、信号处理等领域占有极其重要的地位。随着SoC单片机的快速发展,现在已经能够将采集多路模拟信号的A/D转换子系统和CPU核集成在一片芯片上,使整个数据采集系统几乎能够单芯片实现,从而使数据采集系统体积小,性价比高。FPGA为实现高速数据采集提供了一种理想的实现途径。利用FPGA高速性能和本身集成的几万个逻辑门和嵌入式存储器块,把数据采集系统中的数据缓存和控制电路全部集成在一片FPGA芯片中,大大减小了系统体积,提高了灵活性。FPGA 还具有系统编程功能以及功能强大的EDA软件支持,使得系统具有升级容易、开发周期短等优点。 二.设计要求 设计一高速数据采集系统,系统框图如图1-1所示。输入模拟信号为频率200KHz、Vpp=0.5V的正弦信号。采样频率设定为25MHz。经过按键启动一次数据采集,每次连续采集128点数据,单片机读取128点数据后在LCD模块上回放显示信号波形。

图1-1 高速数据采集原理框图 三.整体方案设计 高速数据采集系统采用如图3-1的设计方案。高速数据采集系统由单片机最小系统、FPGA最小系统和模拟量输入通道三部分组成。输入正弦信号经过调理电路后送高速A/D转换器,高速A/D 转换器以25MHz的频率采样模拟信号,输出的数字量依次存入FPGA内部的FIFO存储器中,并将128字节数据在LCD模块回放显示。 图3-1 高速数据采集系统设计方案 四.硬件电路设计 1.模拟量输入通道的设计 模拟量输入通道由高速A/D转换器和信号调理电路组成。信号调理电路将模拟信号放大、滤波、直流电平位移,以满足A/D转换器对模拟输入信号的要求。

嵌入式系统设计与应用第五章程序设计与分析(1) 西安交通大学电信学院 任鹏举

本章主要内容 Software Design Cycle ●嵌入式软件中的组件(状态机 、循环缓存器、队列) ●编程模型,如数据流和控制图●编译方法介绍 ●根据性能、大小和功耗来分析 和优化程序 ●如何测试程序以验证其正确性

1 嵌入式程序组件 ●状态机(State machine) 用变量来表示内部的状态,根据输入完成状态的转移交通灯控制、CPU design controller ●循环缓冲区(Circular buffer) I/O input buffer ●队列(Queue)

状态机(1) ● 反应系统(reactive system ):响应外部事件的系统。 ●外部输入是间歇到达● 适合使用状态机描述 ● 有限状态机是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型。 ●Moore 机:● Mealy 机:输出只由当前状态确定 输出依赖于当前状态和输入

状态机(2) 例子:一个简单的座位安全带控制器 idle buzzer seated belted 未入座/-入座/定时器启动 未系安全带且定时器未超时/- 未系安全带/定时器启动系好安全带/-系好安全带/蜂鸣器关闭 定时器超时/蜂鸣器启动 未入座/-未入座/蜂鸣器关闭输入/输出-= 无动作

状态机(3) #define IDLE 0#define SEATED 1#define BELTED 2#define BUZZER 3switch (state) { case IDLE: if (seat) { state = SEATED; timer_on = TRUE; } break; case SEATED: if (belt) state = BELTED; else if (timer) state = BUZZER; break; case BELTED: if (!seat) state = IDLE; else if (!belt) state = SEATED; break; case BUZZER: if (belt) state = BELTED; else if (!seat) state = IDLE; break; } Inputs :seat, belt, timer Outputs: buzzer

嵌入式软件开发流程 一、嵌入式软件开发流程 1.1 嵌入式系统开发概述 由嵌入式系统本身的特性所影响,嵌入式系统开发与通用系统的开发有很大的区别。嵌入式系统的开发主要分为系统总体开发、嵌入式硬件开发和嵌入式软件开发3大部分,其总体流程图如图1.1所示。 图1.1 嵌入式系统开发流程图 在系统总体开发中,由于嵌入式系统与硬件依赖非常紧密,往往某些需求只能通过特定的硬件才能实现,因此需要进行处理器选型,以更好地满足产品的需求。另外,对于有些硬件和软件都可以实现的功能,就需要在成本和性能上做出抉择。往往通过硬件实现会增加产品的成本,但能大大提高产品的性能和可靠性。 再次,开发环境的选择对于嵌入式系统的开发也有很大的影响。这里的开发环境包括嵌入式操作系统的选择以及开发工具的选择等。比如,对开发成本和进度限制较大的产品可以选择嵌入式Linux,对实时性要求非常高的产品可以选择Vxworks等。

1.2 嵌入式软件开发概述 嵌入式软件开发总体流程为图4.15中“软件设计实现”部分所示,它同通用计算机软件开发一样,分为需求分析、软件概要设计、软件详细设计、软件实现和软件测试。其中嵌入式软件需求分析与硬件的需求分析合二为一,故没有分开画出。 由于在嵌入式软件开发的工具非常多,为了更好地帮助读者选择开发工具,下面首先对嵌入式软件开发过程中所使用的工具做一简单归纳。 嵌入式软件的开发工具根据不同的开发过程而划分,比如在需求分析阶段,可以选择IBM的Rational Rose等软件,而在程序开发阶段可以采用CodeWarrior(下面要介绍的ADS 的一个工具)等,在调试阶段所用的Multi-ICE等。同时,不同的嵌入式操作系统往往会有配套的开发工具,比如Vxworks有集成开发环境Tornado,WindowsCE的集成开发环境WindowsCE Platform等。此外,不同的处理器可能还有对应的开发工具,比如ARM的常用集成开发工具ADS、IAR和RealView等。在这里,大多数软件都有比较高的使用费用,但也可以大大加快产品的开发进度,用户可以根据需求自行选择。图4.16是嵌入式开发的不同阶段的常用软件。 图1.2 嵌入式开发不同阶段的常用软件 嵌入式系统的软件开发与通常软件开发的区别主要在于软件实现部分,其中又可以分为编译和调试两部分,下面分别对这两部分进行讲解。 1.交叉编译 嵌入式软件开发所采用的编译为交叉编译。所谓交叉编译就是在一个平台上生成可以在另一个平台上执行的代码。在第3章中已经提到,编译的最主要的工作就在将程序转化成运行该程序的CPU所能识别的机器代码,由于不同的体系结构有不同的指令系统。因此,不同的CPU需要有相应的编译器,而交叉编译就如同翻译一样,把相同的程序代码翻译成不同CPU的对应可执行二进制文件。要注意的是,编译器本身也是程序,也要在与之对应的某一个CPU平台上运行。嵌入式系统交叉编译环境如图4.17所示。

基于TLC549的数据采集系统设计 Time:2009-09-22 11:14:00 Author: Source:电子元器件应用 杨来侠,万建军 (西安科技大学,陕西西安710054) 0 引言 现代自动控制系统中需要测量和控制的参数往往都是连续变化的模拟信号,如温度,压力,流量,速度等。这些物理量和控制参数往往都是连续变化的电压和电流,因此,必须将其变换成数字量(即需经模,数转换),才能被数字计算机所识别。这些数字量在计算机内经过运算处理,可以得到一个数字形式的控制量,将这些控制量经过数/模转换器,变成模拟电压或电流信号,再送到执行机构去驱动相应的设备动作,即可实现对生产过程的自动控制。 1 TLC549的主要特点和工作原理 l.l TLC549的主要特点 TLC549是采用IinCMOSTM技术并以开关电容逐次逼近原理工作的8位串行A/D7芯片,可与通用微处理器、控制器通过I/O CLOCK、CS、DATA OUT三条口线进行串行接口。TLC549具有4MHz的片内系统时钟和软、硬件控制电路,转换时间最长为17μs,允许的最高转换速率为40000次/s。总失调误差最大为±0.5LSB,典型功耗值为6 mW。TLC549采用差分参考电压高阻输入,抗干扰,可按比例量程校准转换范围,由于其VREF-接地时,(VREF+)-(VREF-)≥1 V,故可用于较小信号的采样,此外,该芯片还单电源3~6v的供电范围。总之,TLC549具有控制口线少,时序简单,转换速度快,功耗低,价格便宜等特 点,适用于低功耗袖珍仪器上的单路A/D采样,也可将多个器件并联使用。TLC549的内部结构框图和管脚名称如图1所示。 1.2 TLC549的极限参数,

嵌入式系统设计与应用复习资料 (一)?单项选择题: 1. 下面哪个系统属于嵌入式系统。 ( 八、“天河一号”计算机系统 C 、联想S10±网木 D ) B 、联想T400笔记本计算机 D 、联想OPhone 手机 2. 软硕件协同设计方法与传统设计方法的最大不同Z 处在于(B )。 A 、软硬件分开描述 C 、协同测试 3. 卜?面关于哈佛结构描述正确的是(A A 、程序存储空间与数据存储空间分离 C 、程序存储空间与数据存储空间合并 4. 下面哪一种工作模式不属于ARM 特权模式 A 、用户模式 B 、系统模式 C 、 5. ARM7TDM1的工作状态包括(D )。 A 、测试状态和运行状态 C 、就绪状态和运行状态 6. USB 接口移动硬盘最合适的传输类型为( A 、控制传输 B 、批量传输 C 、 7. 下而哪一种功能单元不属于I/O 接口电路。(D ) A 、USB 控制器 B 、UART 控制器 C 、以太网控制器 &下面哪个操作系统是恢入式操作系统。(B ) As Red-hat Linux B 、 PCLinux C 、 Ubuntu Linux D 、 SUSE Linux 9. 使用Host-Target 联合开发嵌入式应用,(B )不是必须的。 A 、宿主机 B 、银河麒麟操作系统 C 、目标机 D 、交叉编译器 10. 下面哪个系统不属于嵌入式系统(D )。 A 、MP3播放器 B 、GPS 接收机 C 、“银河玉衡”核心路由器 D 、“犬河一号”计算机系统 11. 在嵌入式系统设计中,嵌入式处理器选型是在进行(C )吋完成。 A 、需求分析 B 、系统集成 C 、体系结构设计 D 、软便件设计 12. 下面哪一类嵌入式处理器最适合于用于工业控制(B )。 A 、嵌入式微处理器 B 、微控制器 C 、DSP D 、以上都不合适 13. 关于ARM 了程序和Thumb 了程序互相调用描述正确的是(B )。 A 、 系统初始化Z 后,ARM 处理器只能工作在一种状态,不存在互相调用。 B 、 只要遵循一定调用的规则,Thumb 子程序和ARM 子程序就可以互相调用。 C 、 只要遵循一定调用的规则,仅能Thumb 子程序调用ARM 子程序。 D 、 只耍遵循一定调用的规则,仅能ARM 子程序调用Thumb 子程序。 14. 关于ARM 处理器的异常的描述不正确的是(C )。 A 、复位属于异常 B 、除数为零会引起异常 B 、软硬件统一描述 D 、协同验证 B 、存储空间与10空间分离 D 、存储空间与10空间合并 (A )0 软中断模式 D 、FTQ 模式 B 、挂起状态和就绪状态 D 、ARM 状态和Thumb 状态 B )0 中断传输 D 、等时传输 D 、LED

从软件工程的角度来说,嵌入式应用软件也有一定的生命周期,如要进行需求分析、系统设计、代码编写、调试和维护等工作,软件工程的许多理论对它也是适用的。 但和其他通用软件相比,它的开发有许多独特之处: ·在需求分析时,必须考虑硬件性能的影响,具体功能必须考虑由何种硬件实现。 ·在系统设计阶段,重点考虑的是任务的划分及其接口,而不是模块的划分。模块划分则放在了任务的设计阶段。 ·在调试时采用交叉调试方式。 ·软件调试完毕固化到嵌入式系统中后,它的后期维护工作较少。 下面主要介绍分析和设计阶段的步骤与原则: 1、需求分析 对需求加以分析产生需求说明,需求说明过程给出系统功能需求,它包括:·系统所有实现的功能 ·系统的输入、输出 ·系统的外部接口需求(如用户界面) ·它的性能以及诸如文件/数据库安全等其他要求 在实时系统中,常用状态变迁图来描述系统。在设计状态图时,应对系统运行过程进行详细考虑,尽量在状态图中列出所有系统状态,包括许多用户无需知道的内部状态,对许多异常也应有相应处理。 此外,应清楚地说明人机接口,即操作员与系统间地相互作用。对于比较复杂地系统,形成一本操作手册是必要的,为用户提供使用该系统的操作步骤。为使系统说明更清楚,可以将状态变迁图与操作手册脚本结合起来。

在对需求进行分析,了解系统所要实现的功能的基础上,系统开发选用何种硬件、软件平台就可以确定了。 对于硬件平台,要考虑的是微处理器的处理速度、内存空间的大小、外部扩展设备是否满足功能要求等。如微处理器对外部事件的响应速度是否满足系统的实时性要求,它的稳定性如何,内存空间是否满足操作系统及应用软件的运行要求,对于要求网络功能的系统,是否扩展有以太网接口等。 对于软件平台而言,操作系统是否支持实时性及支持的程度、对多任务的管理能力是否支持前面选中的微处理器、网络功能是否满足系统要求以及开发环境是否完善等都是必须考虑的。 当然,不管选用何种软硬件平台,成本因素都是要考虑的,嵌入式Linux 正是在这方面具有突出的优势。 2、任务和模块划分 在进行需求分析和明确系统功能后,就可以对系统进行任务划分。任务是代码运行的一个映象,是无限循环的一段代码。从系统的角度来看,任务是嵌入式系统中竞争系统资源的最小运行单元,任务可以使用或等待CPU、I/O设备和内存空间等系统资源。 在设计一个较为复杂的多任务应用系统时,进行合理的任务划分对系统的运行效率、实时性和吞吐量影响都极大。任务分解过细会不断地在各任务之间切换,而任务之间的通信量也会很大,这样将会大大地增加系统的开销,影响系统的效率。而任务分解过粗、不够彻底又会造成原本可以并行的操作只能按顺序串行执行,从而影响系统的吞吐量。为了达到系统效率和吞吐量之间的平衡折中,在划分任务时应在数据流图的基础上,遵循下列步骤和原则:

等间距采样的高速数据采集系统设计 郝亮,孟立凡,刘灿,高建中 (中北大学仪器科学与动态测试教育部重点实验室,太原030051) 摘要:简单介绍通过对窄脉冲等间距采样来测试电缆故障的基本原理,分析其脉冲的特点和处理要求;采用F PGA和MSP430F149作为主控芯片,设计了单路多次低速数据采集系统;利用Quartus II软件编写主控程序,并在Modelsim下进行仿真验证。实验结果表明,该系统方案切实可行,可有效解决电缆故障测距过程中的高精度数据采集问题。 关键词:等间距采样;数据采集;MSP430F149;F PGA 中图分类号:TN98文献标识码:B H igh2spe ed Data Acquisition System Based on Equidistance Sampling Hao Liang,Meng Lifan,Liu Can,Gao Jianzhong (Inst ruments Science and Dynamic Measurement Ministry of Education Key Laboratory, North University of China,T aiyuan030051,China) A bstract:T he basic principle of testing cable faults wit h narrow2pulse equidistance sampling is described.Pulse characteristics and pro2 cessing requirements are analyzed.The single2line repeated low2speed dat a acquisition system is designed with FPGA and MSP430F149 as main control chips.Main control procedures are programmed in Quartus II and simulated in Modelsim.Experimental result shows that t he system is practical,and the problem of high2precision data acquisition in the process of cable fault location is resolved effectively. K ey words:equidist ance sampling;data acquisit ion;MSP430F149;FPGA 引言 电缆故障是通信行业中的常见故障,而电缆测距是排除故障的前提条件。准确的电缆测距可以缩短发现故障点的时间,利于快速排除故障,减少损失。窄脉冲时域反射仪利用时域反射技术来测定电缆断点位置,可以同时检测出同轴传输系统中多个不连续点的位置、性质和大小。窄脉冲信号持续的时间非常短暂,为了能够有效地捕捉到窄脉冲信号,对A/D采样率和处理器速率提出了较高的要求,传统的数据采集已经不能满足系统设计需求。本文介绍的单路多次低速数据采集方案硬件结构简单,成本低,能够满足系统设计要求。 1系统设计理论依据 根据电磁波理论,电缆即传输线。假若在电缆的一端发送一探测脉冲,它就会沿着电缆进行传输,当电缆线路发生障碍时会造成阻抗不匹配,电磁波会在障碍点产生反射。在发射端,由测量仪器将发送脉冲和反射脉冲波形记录下来。实际测试中,具体障碍的波形有所差异:断线(开路)障碍时,反射脉冲与发射脉冲极性相同;而短路、混线障碍时,反射脉冲与发射脉冲极性相反。波形如图1所示。 图1发射脉冲与反射脉冲波形 设从发射窄脉冲开始到接收到反射脉冲波的时间为$t,则: l=v#$t 2 其中,v为脉冲波在电缆中的传输速度;l为电缆故障点与脉冲波送入端的距离。 由以上分析可知,在同一个固定障碍的线路上多次送入同一脉冲电压,其反射脉冲将同样地在同一位置多次出现。 要实现对反射窄脉冲的捕获和1m的测距分辨率(在波速为200m/L s的情况下),则$t= 2l v =2@1 200 =0.01L s =10ns。即要求抽样的时间分辨率为10ns,对应的数据采集系统频率高达100MHz。同时,最大测量范围是2km 时,要求发射脉冲的重复周期T= 2l v =2@2000 200 =20L s。

多路数据采集系统设计毕业论文 第1章绪论 1.1 多路数据采集系统介绍 随着工、农业的发展,多路数据采集势必将得到越来越多的应用,为适应这一趋势,作这方面的研究就显得十分重要。在科学研究中,运用数据采集系统可获得大量的动态信息,也是获取科学数据和生成知识的重要手段之一。总之,不论在哪个应用领域中,数据采集与处理将直接影响工作效率和所取得的经济效益。 此外,计算机的发展对通信起了巨大的推动作用。算机和通信紧密结合构成了灵活多样的通信控制系统,也可以构成强有力的信息处理系统,这样对社会的发展产生了深远的影响。数据通信是计算机广泛应用的必然产物[2]。 数据采集系统,从严格的意义上来说,应该是用计算机控制的多路数据自动检测或巡回检测,并且能够对数据实行存储、处理、分析计算以及从检测的数据中提取可用的信息,供显示、记录、打印或描绘的系统。 数据采集系统一般由数据输入通道,数据存储与管理,数据处理,数据输出及显示这五个部分组成。输入通道要实现对被测对象的检测,采样和信号转换等

工作。数据存储与管理要用存储器把采集到的数据存储起来,建立相应的数据库,并进行管理和调用。数据处理就是从采集到的原始数据中,删除有关干扰噪声,无关信息和必要的信息,提取出反映被测对象特征的重要信息。另外,就是对数据进行统计分析,以便于检索;或者把数据恢复成原来物理量的形式,以可输出的形态在输出设备上输出,例如打印,显示,绘图等。数据输出及显示就是把数据以适当的形式进行输出和显示。 由于RS-232在微机通信接口中广泛采用,技术已相当成熟。在近端与远端通信过程中,采用串行RS-232标准,实现PC机与单片机间的数据传输。在本毕业设计中对多路数据采集系统作了初步的研究。本系统主要解决的是怎样进行数据采集以及怎样进行多路的数据采集,并将数据上传至计算机[2]。 1.2 设计思路 多路数据采集系统采用ADC0809模数转换器作为数据采集单元和AT89C51单片机来对它们进行控制,不仅具有控制方便、简单和灵活性大等优点,而且可以大幅度提高采集数据的灵敏度及指标。通过MAX232电平转换芯片实现单片机与PC 机的异步串行通信,设计中的HD7279实现了键盘控制与LED显示显示功能。本文设计了一种以AT89C51和ADC0809及RS232为核心的多路数据采集系统。 多路数据采集系统就是通过键盘控制选择通路,将采集到的电压模拟两转换成数字量实时的送到单片机里处理从而显示出采集电压和地址值,最终控制执行单片机与PC机的异步串行通信。 连接好硬件后,给ADC0809的三条输入通路通入直流电压。4-F键为功能键,4-E键为复位键,F键为确认键。1-3键为通道选择键,分别采集三个通道的数据值并实时显示出数值和地址值。结合单片机RS232串口功能还实现了与PC机的异

1 引言 1.1 数据采集系统的意义 数据采集系统是结合基于计算机的测量软硬件产品来实现灵活的、用户自定义的测量系统。数据采集是指从传感器和其它待测设备等模拟和数字被测单元中自动采集信息的过程。本设计采用A/D转换器和51单片机组成数据采集系统,该设计具有结构简单、操作方便、高性价比、具有显示、记录存储功能,能够适应油田野外恶劣环境,具有性能稳定、可靠性高、响应速度快操作简单、费用低廉、回放过程的信号可以直观的观察。它与有线数传相比主要有布线成本低、安装简便、便于移动等性能。 经调查,目前数据采集器的市场需求量大,以数据采集器为核心构成的小系统应用广泛,因此开发高性能的数据采集器具有良好的市场前景。随着计算机技术的飞速发展和普及,数据采集系统在多个领域有着广泛的应用。数据采集是工、农业控制系统中至关重要的一环,在医药、化工、食品、等领域的生产过程中,往往需要随时检测各生产环节的温度、湿度、流量及压力等参数。同时,还要对某一检测点任意参数能够进行随机查寻,将其在某一时间段内检测得到的数据经过转换提取出来,以便进行比较,做出决策,调整控制方案,提高产品的合格率,产生良好的经济效益。随着工、农业的发展,多路数据采集势必将得到越来越多的应用,为适应这一趋势,作这方面的研究就显得十分重要。在科学研究中,运用数据采集系统可获得大量的动态信息,也是获取科学数据和生成知识的重要手段之一。单片机构成的数据采集处理系统适用于各种现场自动化监测及控制,能够适应油田野外恶劣环境,具有性能稳定、可靠性高、响应速度快操作简单、费用低廉、等优点。1.2 数据采集系统的主要功能 数据采集是指从传感器和其它待测设备等模拟和数字被测单元中自动采集信息的过程。数据采集系统是结合基于计算机的测量软硬件产品来实现灵活的、用户自定义的测量系统。比如条码机、扫描仪等都是数据采集工具。 数据处理系统是指运用计算机处理信息而构成的系统。其主要功能是将输入的数据信息进行加工、整理,计算各种分析指标,变为易于被人们所接受的信息形式,并将处理后的信息进行有序贮存,随时通过外部设备输给信息使用者。

5 Gsps 高速数据采集系统的设计与实现 摘要:以某高速实时频谱仪为应用背景,论述了5 Gsps 采样率的高速数据采集系统的构成和设计要点,着重分析了采集系统的关键部分高速ADC(analog to digital,模数转换器)的设计、系统采样时钟设计、模数混合信号完整性设计、电磁兼容性设计和基于总线和接口标准(PCI Express)的数据传输和处理软件设计。在实现了系统硬件的基础上,采用Xilinx 公司ISE 软件的在线逻辑分析仪(ChipScope Pro)测试了ADC 和采样时钟的性能,实测表明整体指标达到设计要求。给出上位机对采集数据进行处理的结果,表明系统实现了数据的实时采集 存储功能。关键词:高速数据采集;高速ADC;FPGA;PCI Express 高速实时频谱仪是对实时采集的数据进行频谱分析,要达到这样的目的,对数据采集系 统的采样精度、采样率和存储量等指标提出了更高的要求。而在高速数据采集 系统中,ADC 在很大程度上决定了系统的整体性能,而它们的性能又受到时钟质量的影响。为满足系统对高速ADC 采样精度、采样率的要求,本设计中提 出一种新的解决方案,采用型号为EV8AQ160 的高速ADC 对数据进行采样;考虑到ADC 对高质量、低抖动、低相位噪声的采样时钟的要求,采用AD9520 为5 Gsps 数据采集系统提供采样时钟。为保证系统的稳定性,对模数混合信号完整性和电磁兼容性进行了分析。对ADC 和时钟性能进行测试,并给出上位 机数据显示结果,实测表明该系统实现了数据的高速采集、存储和实时后处理。 1 系统的构成高速数据采集系统主要包括模拟信号调理电路、高速ADC、高速时钟电路、大容量数据缓存、系统时序及控制逻辑电路和计算机接口电路等。图1 所示为5 Gsps 高速数据采集系统的原理框图。所用ADC 型号为EV8AQ160,8 bit 采样精度,内部集成4 路ADC,最高采样率达5 Gsps,可以工作在多种模式下。通过对ADC 工作模式进行配置,ADC 既可以工作在采样

嵌入式系统设计与应用 本文由kenneth67贡献 ppt文档可能在W AP端浏览体验不佳。建议您优先选择TXT,或下载源文件到本机查看。 课程名称:课程名称:嵌入式系统设计与应用 总学时:其中讲课36学时,上机实践环节12 36学时12学时总学时:其中讲课36学时,上机实践环节12学时教材:嵌入式系统设计教程》教材:《嵌入式系统设计教程》电子工业出版社马洪连参考书:参考书:1、《嵌入式系统开发与应用》北航出版社、田泽编著. 嵌入式系统开发与应用》北航出版社、田泽编著. 2、《ARM体系结构与编程》清华大学出版社杜春雷编著ARM体系结构与编程体系结构与编程》嵌入式系统设计与实例开发—ARM ARM与C/OS3、《嵌入式系统设计与实例开发ARM与μC/OS-Ⅱ》清华大学出版社王田苗、魏洪兴编著清华大学出版社王田苗、ARM嵌入式微处理器体系结构嵌入式微处理器体系结构》4、《ARM嵌入式微处理器体系结构》北航出版社、马忠梅等著. 北航出版社、马忠梅等著. 张石.ARM嵌入式系统教程嵌入式系统教程》5、张石.《ARM嵌入式系统教程》.机械工业出版2008年社.2008年9月 1 课程内容 绪论:绪论: 1)学习嵌入式系统的意义2)高校人才嵌入式培养情况嵌入式系统设计(实验课)3)嵌入式系统设计(实验课)内容安排 第1章嵌入式系统概况 1.1 嵌入式系统的定义1.2 嵌入式系统的应用领域及发展趋势1.3 嵌入式系统组成简介 第2章嵌入式系统的基本知识 2.1 2.2 2.3 嵌入式系统的硬件基础嵌入式系统的软件基础ARM微处理器的指令系统和程序设计ARM微处理器的指令系统和程序设计 2 第3章 3.1 3.2 3.3 基于ARM架构的嵌入式微处理器基于ARM架构的嵌入式微处理器ARM 概述嵌入式微处理器的组成常用的三种ARM ARM微处理器介绍常用的三种ARM 微处理器介绍 第4章 4.1 4.2 4.3 4.4 4.5 4.6 嵌入式系统设计 概述嵌入式系统的硬件设计嵌入式系统接口设计嵌入式系统人机交互设备接口嵌入式系统的总线接口和网络接口设计嵌入式系统中常用的无线通信技术 3 第5章嵌入式系统开发环境与相关开发技术 5.1 5.2 5.3 5.4 5.5 6.1 6.2 6.3 6.4 概述嵌入式系统的开发工具嵌入式系统调试技术嵌入式系统开发经验嵌入式系统的Bootloader Bootloader技术嵌入式系统的Bootloader技术μC/OS-II操作系统概述C/OS-II操作系统概述ADS开发环境ARM ADS开发环境C/OS-II操作系统在ARM系统中的移植操作系统在ARM μC/OS-II操作系统在ARM系统

?应用技术研究? 一种新的基于AR M 的数据采集系统设计 罗 浩 1a,2 ,谢华成 1b (1.信阳师范学院a .物理电子工程学院; b.网络信息与计算中心,河南信阳464000; 2.华中科技大学电子系,湖北武汉430074) 摘 要:给出了一种新的基于AR M 的数据采集系统硬件和软件设计方案1硬件主要由微处理器芯片 S3C44BOX 、US B 接口芯片I SP1362、AD 转换芯片AD7829等构成1系统能实现8路同时采集,单路采集速率100ks p s,且通过设置Device 和Host 两种模式,可在无PC 机的情况下进行数据采样与存储,从而实现了脱机式 应用1 关键词:数据采集;US B;S3C44B0X;AD7829;I SP1362 中图分类号:TP273 文献标识码:A 文章编号:100320972(2006)022******* 0 引言 数据采集是测控系统中的核心单元之一,目前常用的 数据采集方式是A /D 卡和422、485等总线板卡[1],这类方 式的数据采集过程必须依赖PC 机完成,不便野外应用;故研制能够实现脱离PC 机进行数据采集的数据采集卡具有实际意义1 本文提出的基于AR M 的数据采集系统设计方案,以 S3C44B0X 为主控制器,控制AD7829进行数据采集,并控 制US B 接口芯片(I SP1362)进行数据传输1本设计综合利用了S3C44B0X 的高性能、低成本和能耗省的特点,设计了 US B 数据通信的Device 模式和Host 模式,在没有PC 机的 情况下,工作在Host 模式,可以直接与外存储器相连进行脱机式数据采集,实现了脱机式应用1 1 硬件设计 1.1 方案选择 目前,对于US B Host 的开发方式主要有两种选择:一种是选用集成了US B 接口的单片机,比如Cyp ress 公司生产的EZ -US B 系列,I ntel 的8X930AX 系列等1此种开发工具虽然编程简单,但需要购置专门的开发系统,投资较大;另一种是选择普通的单片机或嵌入式微处理器,加专用的US B 接口芯片进行开发1后者不需要购买新的开发系统,节省投资1因此我们采用了第二种方案进行开发1 为了便于开发和扩展Device 、Host 模式,选择了较新且易于开发的US B 接口芯片I SP1362;且为了满足8路采集, AD 转换芯片选择了AD7829;适于I SP1362的开发,其主控 器芯片选择了高性能、低功耗的AR M 芯片S3C44BOX 1三星的S3C44B0X 是为手持设备和通用设备而设计的一款16/32位R I SC 结构的低成本高性能的单片机1为了降低产品的总体成本,S3C44B0X 还提供了如下的配置: 8K B 高速缓存(cache )、可配置的片内SRAM 、LC D 控制器、 两路带握手功能的UART (通用串行口)、4路DMA 控制器、系统管理功能(片选逻辑,FP /E DO /S DRAM 控制器)、5路带P WM 的定时计数器、I/O 接口,RTC (时钟)、8路10位ADC 、II C 总线、II S 总线、同步SI O 接口和为系统提供时钟而设的P LL 倍频电路[2]1 系统分为四大部分:8路AD 转换,US B 接口,AR M 主控器以及S DRAM (2M )、Flash (2M )1AD7829构成的模数转换(8路模拟输入、8位数字输出),在S3C44B0X 控制下完成数据采集,再通过US B 接口传输到外存储器1如图11 图1 系统结构框图 F i g .1The syste m structure d i a gram S3C44B0X 自身虽集成有8路10位ADC,但没有采样 保持电路,其内部集成的A /D 转换只能输入0~100Hz 的模拟信号,因此我们需要对其进行扩展1AD7829作为A /D 转换,S3C44B0X 作为控制器,利用S3C44B0X 的P D 口为双向口来进行扩展,以S3C44B0X 的P D 口发出脉冲作为 AD7829的CONVEST 的负脉冲,进行模数转换,同时能够 收稿日期:2005211230 基金项目:湖北省重大科技攻关项目(2002AA101C39 ) 作者简介:罗 浩(19702),男,河南信阳人,讲师,在读硕士研究生,主要从事电子技术方向研究1 3 02信阳师范学院学报(自然科学版)Journal of Xinyang Nor mal University 第19卷 第2期 2006年4月 (Natural Science Editi on )Vol .19No .2Ap r .2006

嵌入式系统设计与应用第六章进程和操作系统(3)西安交通大学电信学院孙宏滨 i n S u n i 'a n J i a o t o n g U i v e r s i t y I n t e r n a l T e a c h i n g U s e O n l y

● 我们该如何评估调度策略?● 能满足所有截止时限 ● CPU 利用率---CPU 执行有用工作所占的时间比例● 调度开销---做调度决策所需的时间 i n S u n i 'a n J i a o t o n g U i v e r s i t y I n t e r n a l T e a c h i n g U s e O n l y

● 分配优先级主要有两种方法:● 静态优先级:在整个执行过程中优先级始终不变● 动态优先级:在执行过程中优先级发生变化 i n S u n i 'a n J i a o t o n g U i v e r s i t y I n t e r n a l T e a c h i n g U s e O n l y

● 单调速率调度(Rate-Monotonic Scheduling, RMS ):首先为实时操作系统开发的调度策略之一,直至现在仍然被广泛使用。● RMS 属于静态调度策略。事实证明,固定优 先级的做法在许多情况下都足以有效地调度进程。● RMS 的理论基础是单调速率分析(Rate Monotonic Analysis, RMA )。i n S u n i 'a n J i a o t o n g U i v e r s i t y I n t e r n a l T e a c h i n g U s e O n l y

湖南工业大学科技学院 毕业设计(论文)开题报告 (2012届) 教学部:机电信息工程教学部 专业:电子信息工程 学生姓名:肖红杰 班级: 0801 学号 0812140106 指导教师姓名:杨韬仪职称讲师 2011年12 月10 日

题目:基于单片机的数据采集系统的控制器设计 1.结合课题任务情况,查阅文献资料,撰写1500~2000字左右的文献综述。 近年来,数据采集及其应用技术受到人们越来越广泛的关注,数据采集系统在各行各业也迅速的得到应用。如在冶金、化工、医学、和电器性能测试等许多场合需要同时对多通道的模拟信号进行采集、预处理、暂存和向上位机传送、再由上位机进行数据分析和处理,信号波形显示、自动报表生成等处理,这些都需要数据采集系统来完成。但很多数据采集系统存在功能单一、采集通道少、采集速率低、操作复杂、并且对操作环境要求高等问题。人们需要一种应用范围广、性价比高的数据采集系统,基于单片机的数据采集系统具有实现处理功能强大、处理速度快、显示直观,性价比高、应用广泛等特点,可广泛应用于工业控制、仪器、仪表、机电一体化,智能家居等诸多领域。总之,无论在那个应用领域中,数据采集与处理越及时,工作效率就超高,取得的经济效益就越大。 数据采集系统的任务,就是采集传感器输出的模拟信号转换成计算机能识别的信号,并送入计算机,然后将计算得到的数据进行显示或打印,以便实现对某些物理量的监测,其中一些数据还将被生产过程中的计算机控制系统用来控制某些物理量。 数据采集系统的市场需求量大,特别是随着技术的发展,可用数据器为核心构成一个小系统,而目前国内生产的主要是数据采集卡,存在无显示功能、无记忆存储功能等问题,其应用有很大的局限性,所以开发高性能的,具有存储功能的数据采集产品具有很大的市场前景。 随着电子技术的迅速发展,,一些高性能的电子芯片不断推出,为我们进行电子系统设计提供的更多的选择和更多的方便,单片机具有体积小、低功耗、使用方便、处理精度高、性价比高等优点,这些都使得越来越广泛的选用单片机作为数据采集系统的核心处理器。一些高性能的A/D转换芯片的出现也为数据采集系统的设计提供了更多的方便,无论是采集精度还是采样速度都比以前有了较大的提高。其中一些知名的大公司如MAXIM公司、TI公司、ADI公司都有推出性能比效突出的 A/D转换芯片,这些芯片普通具有低功耗、小尺寸的特点,有些芯片还具有多通道的同步转换功能。这些芯片的出现,不仅因为芯片价格便宜,能够降低系统设计的成本,而且可以取代以前繁琐的设计方法,提高系统的集成度。 数据采集器是目前工业控制中应用较多的一类产品,数据采集器的研制已经相当成熟,而且数据采集器的各类不断增多,性能越来越好,功能也越来越强大。 在国外,数据采集器已发展的相当成熟,无论是在工业领域,还是在生活中的应用,比如美国FLUKE公司的262XA系列数据采集器是一种小型、便携、操作简单、使用灵活的数据采集器,它既可单独使用又可和计算机连接使用,它具有多种测量

基于8051单片机的数据采集系统设计 一.设计任务 设计一个数据采集系统,要求: 1.有一组开关量和1路模拟量,采样开关量控制一组发光二极管,定时采样模拟量并显示出来。 2.定时采样ADC0809某通道模拟信号,每隔2秒在显示器或数码管上显示出来。 3.定时的实现。 二.设计思路 数据采集是指从传感器和其他待测设备中自动采集模拟或数字信号电量或非电量信号送入控制器中进行分析和数据处理。 本设计采用单路模拟信号的数据采集。设计思路为:通过传感器采集待测的信号,将其转换为相应的电压信号,经运算放大器放大后送入模数转换器ADC0809在单片机的控制下进行模数转换。每次转换结束后,单片机在控制电路的作用下将数据读走存入片内存储器。而单片机则需要将收到的数据送入PC机中进行相应处理。单片机与PC 间的数据通信方式为串口通信协议RS 232,通过芯片MAX232进行电气匹配。 目录

一.系统总统设计方案 二.系统的硬件设计 2.1信号调理电路 2.2数据采集电路 2.3 80C51芯片内部功能与引脚介绍 三.系统的软件设计 3.1主程序 3.2 A/D转换 3.3数据采集中断程序 四.设计总结 五.参考文献 六.附录—数据采集系统原理图一.系统总统设计方案

根据系统基本要求,将本设计系统划分为信号调理电路、8路模拟信号的产生与A/D 转换器、发送端的数据采集与传输控制器、人机通道的接口电路、数据传输接口电路几个部分。 数据采集与传输系统一般由信号调理电路,多路开关,采样保持电路,A/D,单片机,电平转换接口,接收端(单片机、PC或其它设备)组成。系统框图如下图1所示。 图1 一般系统框图 二.系统的硬件设计 2.1信号调理电路 信号调理能够将被测对象的输出信号变换成计算机要求的输入信号。如图2所示,为 避免小信号通过模拟开关造成较大的附加误差,在传感器输出信号过小时,每个通道应 设前置放大环节。 图2 信号调理过程 2.2 数据采集电路 把连续变化量变成离散量的过程称为量化,也可理解为信号的采样。 把以一定时间间隔T逐点采集连续的模拟信号,并保持一个时间t,使被采集的信号变成时间上离散、幅值等于采样时刻该信号瞬时值的一组方波序列信号,即采样信号。