嵌入式操作系统ucosII的中断处理过程(上篇)

发表于2009/1/4 21:27:24

嵌入式操作系统ucosII的中断处理过程(上篇)转

一. UCOSII的中断过程简介

系统接收到中断请求后,如果CPU处于开中断状态,系统就会中止正在运行的当前任务,而按中断向量的指向去运行中断服务子程序,当中断服务子程序运行完成后,系统会根据具体情况返回到被中止的任务继续运行,或转向另一个中断优先级别更高的就绪任务。

由于UCOS II是可剥夺型的内核,所以中断服务程序结束后,系统会根据实际情况进行一次任务调度,如果有优先级更高的任务,就去执行优先级更高的任务,而不一定要返回被中断了的任务。

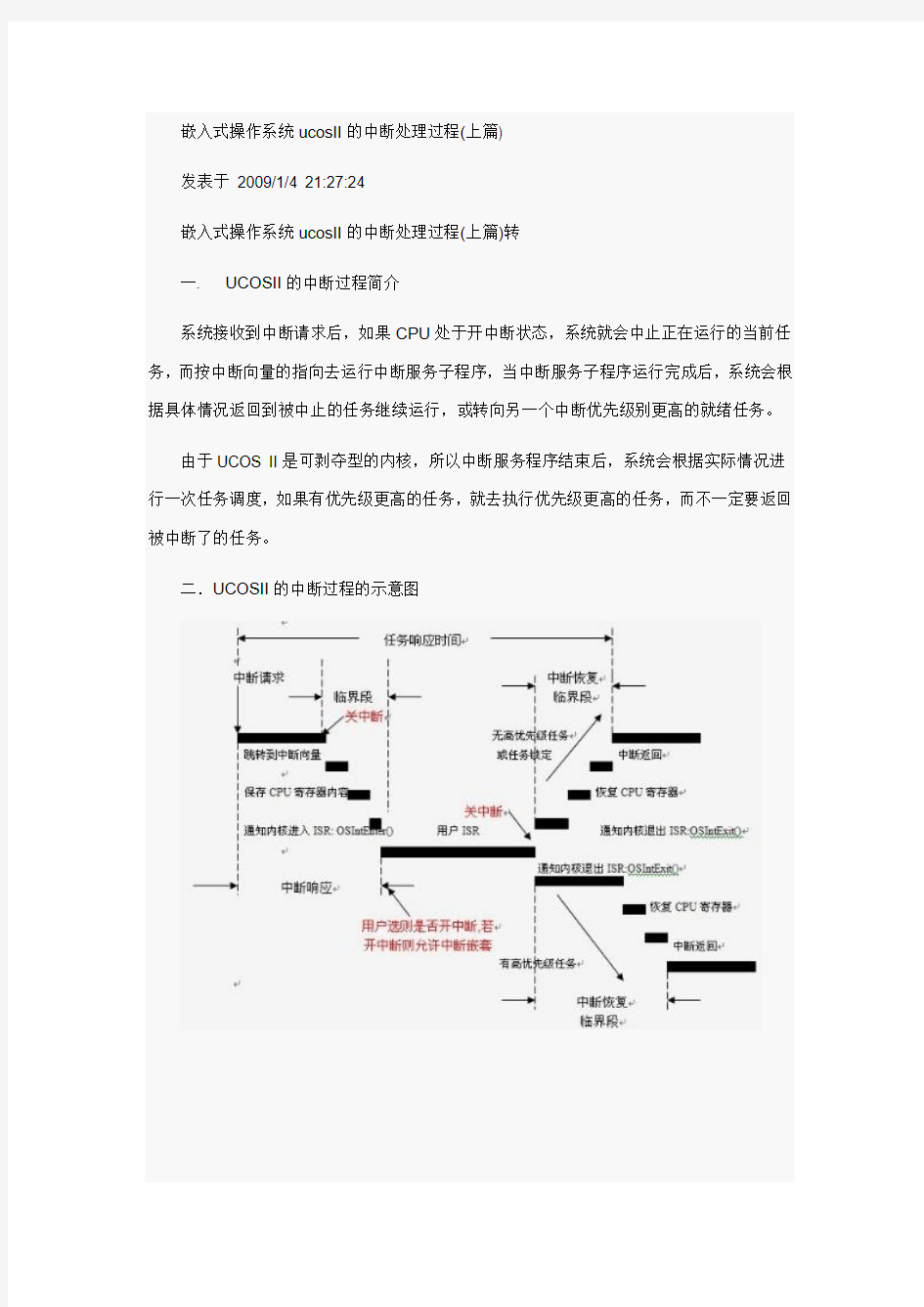

二.UCOSII的中断过程的示意图

三.具体中断过程

1.中断到来,如果被CPU识别,CPU将查中断向量表,根据中断向量表,获得中断服务子程序的入口地址。

2.将CPU寄存器的内容压入当前任务的任务堆栈中(依处理器的而定,也可能压入被压入被中断了的任务堆栈中。

3.通知操作系统将进入中断服务子程序。即:调用OSIntEnter()或OSIntNesting直接加1。

4.If(OSIntNesting==1){OSTCBCur->OSTCBStrPtr=SP;} //如果是第一层中断,则将堆栈指针保存到被中断任务的任务控制块中

5.清中断源,否则在开中断后,这类中断将反复的打入,导致系统崩贵

6.执行用户ISR

7.中断服务完成后,调用OSIntExit().如果没有高优先级的任务被中断服务子程序激活而进入就绪态,那么就执行被中断了的任务,且只占用很短的时间.

8.恢复所有CPU寄存器的值.

9.执行中断返回指令.

四.相关代码

与编译器相关的数据类型:

typedef unsigned char BOOLEAN;

typedef unsigned char INT8U;

typedef unsigned int OS_STK; //堆栈入口宽度为16 位(一) void OSIntEnter (void)的理解

uCOS_II.H中定义:

#ifdef OS_GLOBALS

#define OS_EXT

#define OS_EXT extern

#endif //定义全局宏OS_EXT

#ifndef TRUE

#define TRUE 1

#endif

OS_EXT BOOLEAN OSRunning; //定义外部BOOLEAN类型全局变量,用来指示//核是否在运行

OS_EXT INT8U OSIntNesting;//定义外部8位无符号整型数全局变量,用来表

//示中断嵌套层数

OS_CORE.C中的OSIntEnter()函数原型:

void OSIntEnter (void)

{

if (OSRunning == TRUE) //如果内核正在运行则进入if

{

if (OSIntNesting < 255) //如果嵌套层数小于255,则可以继续

{

OSIntNesting++; //嵌套层数加1

}

}

}

(二)在中断服务子程序中加if ( OSIntNesting == 1){…}的原因

uCOS_II.H中定义:

typedef struct os_tcb {

OS_STK *OSTCBStkPtr;//声明指向任务堆栈栈顶的16位指针………………

} OS_TCB;//定义名为OS_TCB的结构体数据类型,即任务控制块的数据结构

OS_EXT OS_TCB *OSTCBCur;//声明一个指向任务控制块的全局指针变量

//用于指向当前任务的任务控制块

中断服务程序中添加的代码:

if ( OSIntNesting == 1)

{

OSTCBCur->OSTCBStkPtr = SP; // 如果是第一层中断,则将被中断任务

//的堆栈指针保存在被中断任务的任务

//任务控制块中

}

关于uCOS-II的中断服务程序(ISR)中必须加“OSIntNesting == 1”的原因==避免调整堆栈指针.

出现这个问题的根源是当低优先级的任务被中断,当中断完成后由于有高优先级的任务就绪,则必须调度高优先级的任务,原来的低优先级任务继续被中断着,但是此时的低优先级任务的堆栈已经被破坏,已不能被调度程序直接调度了,要想被调度而必须调整堆栈指针。如下图所示的场景:

问题分析:

要想理解加上上面两句的原因,不妨假设有下面场景出现:

void MyTask(void)

{

...

}

该任务在执行过程中被中断打断,下面是它的服务子程序

void MyISR(void)

{

保存现场(PUSHA)

OSIntEnter();

// 此时的堆栈指针是正确的,再往下就不对了,应该在此处保存用户任务堆栈

指针

OSIntExit();

恢复现场(POPA)

中断返回

}

OSIntExit(),大体如下:

OSIntExit()

{

OS_ENTER_CRITICAL();

if( OSIntNesting==0 && OSLockNesting == 0 ) {

找到目前系统中就绪表中优先级最的任务

如果不是当前任务,则调度它执行

OSIntCtxSw();

}

OS_EXIT_CRITICAL();

}

综上所述,任务调用链如下:

MyTask --> MyISR -->

①OSIntExit -->

②OS_ENTER_CRITICAL(); ③

OSIntCtxSw(); ④

然而在实际的移植过程中,需要调整的指针偏移量是与编译器相关的,如果想要避免调整,显然一个简单的方法就是在调用OSIntExit之前先把堆栈指针保存下来,以后调度该用户任务时,直接从此恢复堆栈指针,而不再管实际的堆栈内容了(因为下面的内容相对于调度程序来说已经没有用处了)

(三) void OSIntExit (void)的理解

OS_CPU.H中的宏定义:

typedef unsigned short OS_CPU_SR; //定义OS_CPU_SR为16位的CPU 状态寄存器

#if OS_CRITICAL_METHOD == 1

#define OS_ENTER_CRITICAL() asm CLI // OS_ENTER_CRITICAL()即为将处理器标志

//寄存器的中断标志为清0,不允许中断#define OS_EXIT_CRITICAL() asm STI // OS_ENTER_CRITICAL()即为将处理器标志

//寄存器的中断标志为置1,允许中断#endif //此一整段代码定义为开关中断的方式一

#if OS_CRITICAL_METHOD == 2

#define OS_ENTER_CRITICAL() asm {PUSHF; CLI} //将当前任务的CPU的标志寄存器入

//然后再将中断标志位清0

#define OS_EXIT_CRITICAL() asm POPF //将先前压栈的标志寄存器的值出栈,恢复

//到先前的状态,如果先前允许中断则现在

//仍允许,先前不允许现在仍不允许

#endif //此一整段代码定义为开关中断的方式二

#if OS_CRITICAL_METHOD == 3

#define OS_ENTER_CRITICAL() (cpu_sr = OSCPUSaveSR()) //保存CPU的状态寄存器到

//变量cpu_sr

中,cpu_sr

//为OS_CPU_SR型变量

#define OS_EXIT_CRITICAL() (OSCPURestoreSR(cpu_sr))// 从cpu_sr中恢复状态寄存

//器

#endif //此一整段代码定义为开关中断的方式三,

//此段代码只是示意代

码,OSCPUSaveSR()及

//OSCPURestoreSR(cpu_sr)具体什么函数由

//用户编译器所提供的函数决定.

//以上宏定义非常重要,在使用不同处理器时要使用相应处理器的开关中断指令,在代码移//植时很有用

uCOS_II.H中定义:

OS_EXT INT8U OSLockNesting; //8位无符号全局整数,表示锁定嵌套计数器

void OSIntExit (void)

{

#if OS_CRITICAL_METHOD == 3

OS_CPU_SR cpu_sr;

#endif //采用开关中断方式三

if (OSRunning == TRUE) //如果内核正在运行,则进入if {

OS_ENTER_CRITICAL();//进入临界段,关中断

if (OSIntNesting > 0) //判断最外层中断任务是否已完成{

OSIntNesting--;//由于此层中断任务已完成,中断嵌套计数器减//一

}

if ((OSIntNesting == 0) && (OSLockNesting == 0))

// OSIntNesting==0表示程序的最外层中断任务以完成, OSLockNesting == 0

//表示是否存在任务锁定,整句代码的意思是如果全部中断处理完了且没有其他

//任务锁定任务调度则执行下列任务调度代码

{

OSIntExitY = OSUnMapTbl[OSRdyGrp];

//1

OSPrioHighRdy = (INT8U)((OSIntExitY << 3) + OSUnMapTbl[OSRdyTbl[OSIntExitY]]); //2

if (OSPrioHighRdy != OSPrioCur)

//3

{

OSTCBHighRdy =

OSTCBPrioTbl[OSPrioHighRdy];

OSCtxSwCtr++;

OSIntCtxSw();

}

}

OS_EXIT_CRITICAL();//开中断

}

}

要理解1,2,3处的代码含义.首先要理解任务是如何调度的,所以先讲一下任务调度的核心算法:

a.数据结构:

1.就绪表:就绪表包含两个变量,他们分别是OSRdyGrp(在uCOS_II.H中为OS_EXT INT8U OSRdyGrp;即8位无符号整型的全局变量)和OSRdyTb1[](在uCOS_II.H中为

OS_EXT INT8U OSRdyTbl[OS_RDY_TBL_SIZE];)

先分析OS_EXT INT8U OSRdyTbl[OS_RDY_TBL_SIZE];是怎么回事

#define OS_LOWEST_PRIO 12 //在OS_CFG.H中

这个宏定义了任务所能具有的最低优先级,那么此处共有从0到12共13个优先级,用户在代码移植时可以修改它,自定义所需要的优先级个数,但max(OS_LOWEST_PRIO)==63

#define OS_RDY_TBL_SIZE ((OS_LOWEST_PRIO) / 8 + 1) //在uCOS_II.中OS_RDY_TBL_SIZE用于确定数组OSRdyTbl[]的大小,如果

OS_LOWEST_PRIO==63,则上述宏实际上为#define OS_RDY_TBL_SIZE 8,由于每个数组元素为8位,如果每一位表示一个优先级,则共有8*8=64个优先级现在回到就绪表,操作系统将优先级分为8组,优先级从0到7分为第一组,对应于OSRdyGrp的第0位,从8到15分为第二组,对应于OSRdyGrp的第1位,以此类推,64个优先级就有下面的对应关系(OSRdyTb1[]每组元素的每一位代表一个优先级):

OSRdyTb1[0]--------------优先级从0到7--------------OSRdyGrp第0位

OSRdyTb1[1]--------------优先级从8到15-------------OSRdyGrp第1位

OSRdyTb1[2]--------------优先级从16到23-------------OSRdyGrp第2位

OSRdyTb1[3]--------------优先级从24到31-------------OSRdyGrp第3位

OSRdyTb1[4]--------------优先级从32到39-------------OSRdyGrp第4位

OSRdyTb1[5]--------------优先级从40到47-------------OSRdyGrp第5位

OSRdyTb1[6]--------------优先级从48到55-------------OSRdyGrp第6位

OSRdyTb1[7]--------------优先级从55到63-------------OSRdyGrp第7位

现在再做如下对应:

当OSRdyTbl[0]中的任何一位是1时,OSRdyGrp的第0位置1,

当OSRdyTbl[1]中的任何一位是1时,OSRdyGrp的第1位置1,

当OSRdyTbl[2]中的任何一位是1时,OSRdyGrp的第2位置1,

当OSRdyTbl[3]中的任何一位是1时,OSRdyGrp的第3位置1,

当OSRdyTbl[4]中的任何一位是1时,OSRdyGrp的第4位置1,

当OSRdyTbl[5]中的任何一位是1时,OSRdyGrp的第5位置1,

当OSRdyTbl[6]中的任何一位是1时,OSRdyGrp的第6位置1,

当OSRdyTbl[7]中的任何一位是1时,OSRdyGrp的第7位置1,

如果置1表示有任务进入就绪态,那么上面的表可以理解为:OSRdyGrp的第N位

(0<=N<=7)为1,那么在OSRdyTb1[N]中至少有一位是1,也就是说在OSRdyTb1[N]对应的任务中至少有一个任务处于就绪态

该表在OS_CORE.C中定义如下:

INT8U const OSMapTbl[]={0x01, 0x02, 0x04, 0x08, 0x10, 0x20, 0x40, 0x80};

//8位无符号整型常量数组

3.表(数组)OSUnMapTb1[]:用于求出一个8位整型数最低位为1的位置

该数组在OS_CORE.C中定义如下:

INT8U const OSUnMapTbl[] = {

0, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0, /* 0x00 to 0x0F */

4, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0, /* 0x10 to 0x1F */

5, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0, /* 0x20 to 0x2F */

4, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0, /* 0x30 to 0x3F */

6, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0, /* 0x40 to 0x4F */

4, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0, /* 0x50 to 0x5F */

5, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0, /* 0x60 to 0x6F */

4, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0, /* 0x70 to 0x7F */

7, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0, /* 0x80 to 0x8F */

4, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0, /* 0x90 to 0x9F */

5, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0, /* 0xA0 to 0xAF */

4, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0, /* 0xB0 to 0xBF */

6, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0, /* 0xC0 to 0xCF */

4, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0, /* 0xD0 to 0xDF */

5, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0, /* 0xE0 to 0xEF */

4, 0, 1, 0, 2, 0, 1, 0, 3, 0, 1, 0, 2, 0, 1, 0 /* 0xF0 to 0xFF */ };

理解: 我把问题转化为:

“一个无符号的8位整数,如何确定最低位为1的位的位置?”

即对于任意一个8位整型数,比如4,考虑它的二进制位中所有为1的位,确定最低位为1的位置(相对第0位的偏移),一般来讲首先想到的方法是移位的方法.如: pos=0;//pos用于统计相对于第0位的偏移

while( !(num & 0x01) )//与00000001按位于,如果最低位为1,退出循环,即找到最低位//为1的位

{

num=num>>1;//将二进制数右移一位

pos++;//进行一次移位,则pos加一

}

最后得到的pos就是所有位中为1的最低位的偏移量,但这样计算需要时间,尽管最多右移7次。为了节省时间,使用的方法是“空间换时间”的办法,即把8位无符号数,所有可能的情况的都列了出来,共有256个数字,把每个数字的最低为1位的位置都预先计算好。比如4对应二进制数为100,最低为1位相对第0位偏移量为2,则查表时,以4为索引,马上就得到2这个数字。(即:OSUnMapTb1[4]==2)

b.构建OSRdyGrp和OSRdyTb1[]算法:

代码原型在OS_CORE.C中,实际代码大致如下:(prio为任务优先级)

INT8U OS_TCBInit (INT8U prio, OS_STK *ptos, OS_STK *pbos, INT16U id, INT32U stk_size, void *pext, INT16U opt)

{

…………

ptcb->OSTCBY = prio >> 3;

ptcb->OSTCBBitY = OSMapTbl[ptcb->OSTCBY];

ptcb->OSTCBX = prio & 0x07;

ptcb->OSTCBBitX = OSMapTbl[ptcb->OSTCBX];

…………..

OSRdyGrp |= ptcb->OSTCBBitY;

OSRdyTbl[ptcb->OSTCBY] |= ptcb->OSTCBBitX;

…………..

}//此函数在创建任务时被调用,即OSTaskCreate(..)中,用于初始化任务控制块以上代码可以等效于:

OSRdyGrp |= OSMapTbl[prio>>3];

OSRdyTb1[prio>>3] |= OSMapTbl[prio&0x07];

此处prio >> 3 是右移3位,就相当于连续除以3个2,因此相当于:prio / 8 ;

prio & 0x07 是求低3位的值,而由高5位构成的值正好是8的整数倍,因此是取余运算,即:prio % 8

因此又可将算法等效为:

OSRdyGrp |= OSMapTbl[prio / 8];

OSRdyTb1[prio / 8] |= OSMapTbl[prio % 8];

算法的作用相当于如下流程:(假定prio=28)

就这样把任务的优先级放入了就绪表.在此我产生一个疑问,”prio>>3与

prio&0x07并不直观,为什么不用prio/8与prio%8呢?”我做如下解释:

处理器一般具有如下结构

累加器是具有移位功能的,prio>>3可以在累加器中完成而不必进入ALU,而prio/8则不同,要进入ALU,ALU处理速度不如累加器,如果采用prio/8将降低操作系统的实时性,同样prio&0x07只是一个间单的位与操作,而prio%8则还要经过ALU,如采用prio%8也将降低实时性.

现在回到OSIntExit()处,看1,2,3处的代码:

OSIntExitY = OSUnMapTbl[OSRdyGrp]; //1

OSPrioHighRdy = (INT8U)((OSIntExitY << 3) + OSUnMapTbl[OSRdyTbl[OSIntExitY]]);//2

if (OSPrioHighRdy != OSPrioCur)

//3

{

OSTCBHighRdy =

OSTCBPrioTbl[OSPrioHighRdy];

OSCtxSwCtr++;

OSIntCtxSw();

}

在uCOS_II.H中有如下定义:

OS_EXT INT8U OSIntExitY;//8位无符号全局整型变量,用于存放就绪表中就绪的任务组

OS_EXT INT8U OSPrioHighRdy;// 8位无符号全局整型变量,用于存放具有最高优先级任务的优先级

OSUnMapTbl[]:用于计算偏移量,偏移量即为优先级最高的就绪任务组在OSRdyGrp中的位置

以及优先级最高的任务在最高优先级任务组OSRdyTbl[N](N表示最高优先级任务组,0<=N<=7)中的位置.

OSIntExitY = OSUnMapTbl[OSRdyGrp];//表示获得具有最高优先级的组

例如OSRdyGrp值为01101000(0x68),则第3,5,6组中有任务就绪,查表OSUnMapTbl[0x68]==3,即优先级最高任务组为第3组.

OSUnMapTbl[OSRdyTbl[OSIntExitY]] //表示获得最高优先级任务组中的优先级最高的任务

例如OSRdyTbl[3]的值为01110000(0x70),则第4,5,6位中有任务

绪,OSUnMapTbl[0x70]==4,即优先级最高的任务在组中位于第4位.

OSPrioHighRdy = (INT8U)((OSIntExitY << 3) +

OSUnMapTbl[OSRdyTbl[OSIntExitY]]);

//就是3*8+4==28,再经强制类型转换成INT8U型,赋给OSPrioHighRdy

这样OSPrioHighRdy就获得了就绪表中优先级最高的任务

嵌入式操作系统ucosII的中断处理过程(下篇)

再看3处代码:

在uCOS_II.H中有如下定义:

OS_EXT OS_TCB *OSTCBPrioTbl[OS_LOWEST_PRIO + 1];//定义指向任务控制块的指针数//组,且每个优先级在同一时刻只对应一个任务

OS_EXT INT8U OSPrioCur;//用于保存目前任务的优先级

OS_EXT INT32U OSCtxSwCtr;//32位无符号全局整型变量,作为任务切换计数器

OS_EXT OS_TCB *OSTCBHighRdy;//指向最高优先级任务任务控制块的指针

if (OSPrioHighRdy != OSPrioCur)

//就绪态任务中的最高优先级已不是目前任务的优先级,则进行中断级的任务//切换{

OSTCBHighRdy = OSTCBPrioTbl[OSPrioHighRdy];

//将最高优先级任务控制块指针指向当前优先级最高的任务的任务控制块

OSCtxSwCtr++;//任务切换计数器加1

OSIntCtxSw();//调用中断级任务切换函数

}

此段代码体现出了可剥夺型实时操作系统内核的特点.

OSIntCtxSw()在80x86上的移植代码,此代码在OS_CPU_A.ASM中,代码如下:

。 目录 1引言 1.1编写目的 1.2背景 1.3参考资料 1.4术语定义及说明 2设计概述 2.1任务和目标 2.1.1需求概述 2.1.2运行环境概述 2.1.3条件与限制 2.1.4详细设计方法和工具 3系统详细需求分析 3.1详细需求分析 3.2详细系统运行环境及限制条件分析接口需求分析4总体方案确认 4.1系统总体结构确认 4.2系统详细界面划分 4.2.1应用系统与支撑系统的详细界面划分 4.2.2系统内部详细界面划分 5系统详细设计 5.1系统结构设计及子系统划分

。 5.2系统功能模块详细设计 5.3系统界面详细设计 5.3.1外部界面设计 5.3.2内部界面设计 5.3.3用户界面设计 6数据库系统设计 6.1设计要求 6.2信息模型设计 6.3数据库设计 6.3.1设计依据 6.3.2数据库选型 6.3.3数据库种类及特点 6.3.4数据库逻辑结构 6.3.5物理结构设计 6.3.6数据库安全 6.3.7数据字典 7网络通信系统设计 7.1设计要求 7.2网络结构确认 7.3网络布局设计 7.4网络接口设计 8信息编码设计

。 8.1代码结构设计 8.2代码编制 9维护设计 9.1系统的可靠性和安全性 9.2系统及用户维护设计 9.3系统扩充 9.4错误处理 9.4.1出错类别 9.4.2出错处理 9.4.3系统调整及再次开发问题 10系统配置 10.1配置原则 10.2硬件配置 10.3软件配置 11关键技术 11.1关键技术的提出 11.2关键技术的一般说明 11.3关键技术的实现方案 12组织机构及人员配置 13投资预算概算及资金规划 14实施计划 14.1限制

实习一中断处理 一、实习内容 模拟中断事件的处理。 二、实习目的 现代计算机系统的硬件部分都设有中断机构,它是实现多道程序设计的基础。中断机 构能发现中断事件,且当发现中断事件后迫使正在处理器上执行的进程暂时停止执行,而让操作系统的中断处理程序占有处理器去处理出现的中断事件。对不同的中断事件,由于它们的性质不同,所以操作系统应采用不同的处理。通过实习了解中断及中断处理程序的作用。本实习模拟“时钟中断事件”的处理,对其它中断事件的模拟处理,可根据各中断事件的性质确定处理原则,制定算法,然后依照本实习,自行设计。 三、实习题目 模拟时钟中断的产生及设计一个对时钟中断事件进行处理的模拟程序。 [提示]: (1) 计算机系统工作过程中,若出现中断事件,硬件就把它记录在中断寄存器中。中 断寄存器的每一位可与一个中断事件对应,当出现某中断事件后,对应的中断寄存器的某一位就被置成―1‖。 处理器每执行一条指令后,必须查中断寄存器,当中断寄存器内容不为―0‖时,说明有中断事件发生。硬件把中断寄存器内容以及现行程序的断点存在主存的固定单元,且让操作系统的中断处理程序占用处理器来处理出现的中断事件。操作系统分析保存在主存固定单元中的中断寄存器内容就可知道出现的中断事件的性质,从而作出相应的处理。 本实习中,用从键盘读入信息来模拟中断寄存器的作用,用计数器加1 来模拟处理器 执行了一条指令。每模拟一条指令执行后,从键盘读入信息且分析,当读入信息=0 时,表示无中断事件发生,继续执行指令;当读入信息=1 时,表示发生了时钟中断事件,转时钟中断处理程序。 (2)假定计算机系统有一时钟,它按电源频率(50Hz)产生中断请求信号,即每隔20 毫秒产生一次中断请求信号,称时钟中断信号,时钟中断的间隔时间(20 毫秒)称时钟单

任务3制定计划与实行目标管理(参考答案) 一、单项选择题 1.A2.A3.B4.A5.A 6.B7.D8.C9.C10.C 二、判断题 1.错2.错3.错4.对5.对 6.错7.对8.对9.对l0.对 三、简答题 1.什么是计划?计划工作的特征有哪些? 计划,通常是指人们行动之前预先拟定的行动内容、具体目标、采用方法和实施步骤。 计划的特征可以概括为五个方面,即目的性、首位性、普遍性、效率性和创造性。 2.简述计划编制的程序。 计划工作的程序一般包括:机会分析、确定目标、编制计划的前提、制定可供选择的方案、评价各种方案、选择方案、编制派生计划、用预算形式使计划数字化等。 (1)机会分析 机会分析的主要内容是根据市场、竞争、顾客的需求,组织的长处和短处,对未来可能出现的机会进行初步分析,了解利用这些机会的能力,弄清组织面临的主要不确定因素,分析其发生的可能性和影响程度,并展望组织可能取得的成果。 (2)确定目标

计划工作的第一步是在机会分析的基础上为组织及其所属的下级单位确定计划工作的目标,即组织在一定时期内所要达到的效果。恰当地确定哪些成果应首先取得,即哪些是优先目标,这是目标选择过程中的重要工作。 (3)编制计划的前提 计划工作的前提就是计划实施时的预期环境,即组织将在什么样的环境下执行计划。确定前提条件,就是要对组织未来的内外部环境和所具备的条件进行分析和预测,弄清计划执行过程中可能存在的有利条件和不利条件。 (4)制定可供选择的方案 (5)评价各种方案 在评价时要从各个方面的客观性、合理性、有效性、经济性和可操作性等方面来衡量。 (6)选择方案 选择方案是计划工作最关键的一步,也是抉择的实质性阶段。在选择最佳方案时,要注意两个方面:一是应选出可行性、满意性和可能带来的结果三者结合最好的方案;二是方案的投入产出比率,应选出投入产出比率尽可能大的方案。 (7)编制派生计划 派生计划就是总计划下的分计划。在完成方案的选择之后,计划工作并没有结束,还必须帮助涉及计划内容的各个下属部门制订支持总计划的派生计划。 (8)用预算形式使计划数字化 预算实质上是资源的分配计划,即根据选择的方案,对组织可利用的资源进行分配,涉及到计划需要那些资源,各需要多少,何时投入以及投入多少等问题。 3.简述计划编制常用的方法。

时钟中断处理 1.VS2010中如何用C进行时钟中断处理? 如何获取时钟中断并进行中断处理(简洁的说一下怎么写整个中断处理过程)?应该用到哪个头文件中的什么函数? 代码: UINT SetTimer( HWND hWnd, // handle of window for timer messages UINT nIDEvent, // timer identifier UINT uElapse, // time-out value TIMERPROC lpTimerFunc // address of timer procedure ); winuser.h.//头文件 每隔uElapse毫秒的时间,就会发送一个WM_TIMER消息。 2.VS2010 C++中让结果窗口暂停 一是:使用std::cin.get()可以让窗口保持等待状态。 二是:#include

软件系统设计设计概要 目录 1 引言 1.1 编写目的 1.2 背景 1.3 参考资料 1.4 术语定义及说明 2 设计概述 2.1 任务和目标 2.1.1 需求概述 2.1.2 运行环境概述 2.1.3 条件与限制 2.1.4 详细设计方法和工具 3 系统详细需求分析 3.1 详细需求分析 3.2 详细系统运行环境及限制条件分析接口需求分析 4 总体方案确认 4.1 系统总体结构确认 4.2 系统详细界面划分 4.2.1 应用系统与支撑系统的详细界面划分 4.2.2 系统内部详细界面划分 5 系统详细设计 5.1 系统结构设计及子系统划分 5.2 系统功能模块详细设计 5.3 系统界面详细设计 5.3.1 外部界面设计 5.3.2 内部界面设计

5.3.3 用户界面设计 6 数据库系统设计 6.1 设计要求 6.2 信息模型设计 6.3 数据库设计 6.3.1 设计依据 6.3.2 数据库选型 6.3.3 数据库种类及特点 6.3.4 数据库逻辑结构 6.3.5 物理结构设计 6.3.6 数据库安全 6.3.7 数据字典 7 网络通信系统设计 7.1 设计要求 7.2 网络结构确认 7.3 网络布局设计 7.4 网络接口设计 8 信息编码设计 8.1 代码结构设计 8.2 代码编制 9 维护设计 9.1 系统的可靠性和安全性9.2 系统及用户维护设计 9.3 系统扩充 9.4 错误处理 9.4.1 出错类别 9.4.2 出错处理 9.4.3 系统调整及再次开发问题 10 系统配置 10.1 配置原则 10.2 硬件配置 10.3 软件配置 11 关键技术 11.1 关键技术的提出 11.2 关键技术的一般说明

多功能数字钟(A) 一、任务 设计制作一个24小时制多功能数字钟。示意图如下(仅供参考): 二、要求 (1)具有时间设置(小时和分钟)、闹钟时间设置、闹钟开、闹钟关功能。 (2)数字显示小时、分钟,有AM、PM指示器,闹钟就绪灯,蜂鸣器。 (3)220V供电。 #include

void delay(uint t) //延时代码 { uint x,y; for(x=t;x>0;x--) for(y=120;y>0;y--); } void initial() //初始化 { TMOD=0x01; //T0方式1计时0.05S TH0=(65536-50000)/256;//定时器T0的高四位赋值 TL0=(65536-50000)%256;//定时器T0的低四位赋值 EA=1; //中断允许 ET0=1; //允许计数器T0中断 TR0=1; //开中断,启动定时器 } void timer0() interrupt 1 //定时器启动1模式 { TH0=(65536-50000)/256; TL0=(65536-50000)%256; i++; if(i==18) { i=0; miao++; //根据振荡频率计算时间增加秒 if(miao==60) //如果秒=60了归为零且分钟增加一分钟 { miao=0; clock[0]=clock[0]+1; if(clock[0]==60) //如果分钟为60,小时增加1 { clock[0]=0; clock[1]=clock[1]+1; if(clock[1]==24) //小时为24小时制,如果24即为0 { clock[1]=0; } } } } }

典型的新产品开发流程 综合Stage-Gate以及PACE的新产品开发流程来看,发现它们基本上是一致的。本文转自项目管理者联盟 项目管理者联盟文章,深入探讨。 下面是对每个阶段的描述: Discovery阶段项目管理者联盟文章,深入探讨。 这个阶段主要是寻求产品构思,并不是每个企业都把这个阶段作为流程的正式阶段,但是,它却是产品创新过程的一个必经的阶段,因为,任何一个可产品化的构思都是从无数多个构思中筛选而来的,这个阶段的过程管理往往是非常开放的,它们可以来自于客户/合作伙伴/售后/市场/制造以及研发内部,这些来自各个渠道的信息就构成了产品的最原始概念。本文转自项目管理者联盟 这个阶段的焦点应放在分析市场机会和战略可行性上,主要通过快速收集一些市场和技术信息,使用较低的成本和较短的时间对技术/市场/财务/制造/知识产权等方面的可行性进行分析,并且评估市场的规模、市场的潜力、和可能的市场接受度,并开始塑造产品概念。这个阶段一般只有少数几个人参与项目,通常包括一个项目发

起人和其他几个助手,正常情况下,这个阶段在4-8周的时间内完成。 这个阶段是产品开发工作的基础阶段,它的主要目的是新产品定义,包括目标市场的定义、产品构思的定义、产品定位战略以及竞争优势的说明,需要明确产品的功能规格以及产品价值的描述等方面内容,决定产品的开发可行性,对Scoping阶段的估计进行严格的调研,并完成后续阶段的计划制定,当然,这个阶段并不需要详细的产品设计,一旦这个阶段结束,需要对这一产品的资源、时间表和资金作出估算。这一阶段涉及的活动比前一阶段要多很多,并且要求多方面的资源和信息投入,这一阶段最好是由一个跨职能的团队来处理,也就是最终项目团队的核心成员。 Development阶段

Linux内核的时钟中断机制 opyright © 2003 by 詹荣开 E-mail:zhanrk@https://www.doczj.com/doc/6012815458.html, Linux-2.4.0 Version 1.0.0,2003-2-14 摘要:本文主要从内核实现的角度分析了Linux 2.4.0内核的时钟中断、内核对时间的表示等。本文是为那些想要了解Linux I/O子系统的读者和Linux驱动程序开发人员而写的。 关键词:Linux、时钟、定时器 申明:这份文档是按照自由软件开放源代码的精神发布的,任何人可以免费获得、使用和重新发布,但是你没有限制别人重新发布你发布内容的权利。发布本文的目的是希望它能对读者有用,但没有任何担保,甚至没有适合特定目的的隐含的担保。更详细的情况请参阅GNU 通用公共许可证(GPL),以及GNU自由文档协议(GFDL)。 你应该已经和文档一起收到一份GNU通用公共许可证(GPL)的副本。如果还没有,写信给:The Free Software Foundation, Inc., 675 Mass Ave, Cambridge,MA02139, USA 欢迎各位指出文档中的错误与疑问。 前言 时间在一个操作系统内核中占据着重要的地位,它是驱动一个OS内核运行的“起博器”。一般说来,内核主要需要两种类型的时间: (1)、在内核运行期间持续记录当前的时间与日期,以便内核对某些对象和事件作时间标记(timestamp,也称为“时间戳”),或供用户通过时间syscall进行检索。 (2)、维持一个固定周期的定时器,以提醒内核或用户一段时间已经过去了。 PC机中的时间是有三种时钟硬件提供的,而这些时钟硬件又都基于固定频率的晶体振荡

目录 桥梁工程课程式设计任务书 (1) 第1章设计资料与结构布置 (3) 1.1 设计资料 (3) 1.2 结构布置 (3) 1.3 设计概述 (6) 第2章主梁内力计算 (7) 2.1 恒载内力计算 (7) 2.2 汽车、人群荷载产生内力计算 (9) 2.3 主梁内力组合 (9) 第3章主梁配筋设计 (21) 3.1 跨中正截面强度计算 (21) 3.2 斜截面承载力剪力筋设计 (23) 3.3 全梁承载力校核 (26) 3.4 裂缝验算 (29) 3.5变形验算 (29) 桥梁工程课程设计任务书 一、课程设计题目 钢筋混凝土简支T梁桥主梁设计 二、课程设计目的 桥梁工程课程设计是桥梁设计的入门,通过设计进一步巩固钢筋混凝土基本原理的主要理论知识,是学生掌握桥梁的设计原理和各种体系桥梁的受力特点,同时重点掌握结构计算基本理论。结合课程设计与习题加深对桥梁工程课堂理论教学内容的理解。培养学生的动手能力。 三、基本要求

1掌握钢筋混凝土桥梁结构的设计原理、步骤,结构构造和设计计算方法。 2熟悉并掌握桥梁工程现行规范运用。 3通过本课程的学习,具有设计一般桥梁结构的能力。 四、基本资料 标准跨径、桥面净宽、荷载等级、主梁及横隔梁数目(按照自己的数据填写) 五、基本内容 1、提供钢筋混凝土简支T形梁桥设计计算书一份,基本内容如下: (1)拟定桥面铺装、主梁截面尺寸及各部分尺寸 (2)主梁内力计算 (3)配筋设计与各种验算 2、完成下列图纸绘制 (1)桥梁一般布置图 (2)主梁一般构造图 (3)主梁钢筋布置图 六、课程设计依据 1《铁路桥涵设计通用规范》(JTG D60—2004) 2《铁路钢筋混凝土及预应力混凝土桥涵设计规范》(JTG D62—2004) 3《铁路砖石及混凝土桥涵设计规范》 4《铁路桥梁荷载横向分布计算》 七、要求 1.熟读规范、标准,理论联系实际; 2.手工与计算机绘图相结合,至少一张手工图,均采用3号图纸;说明书用A4纸,打印。 3.独立完成设计。 桥梁工程课程设计文件撰写要求 一、顺序要求(按照模板) 封面 目录 任务书 正文 二、字体及字号要求 正文用五号宋体; 行距为1.2倍

单片机编程技巧----功能强大的时钟中断 在单片机程序设计中,设置一个好的时钟中断,将能使一个CPU发挥两个CPU的功效,大大方便和简化程序的编制,提高系统的效率与可操作性。我们可以把一些例行的及需要定时执行的程序放在时钟中断中,还可以利用时钟中断协助主程序完成定时、延时等操作。 下面以6MHz时钟的AT89C51系统为例,说明时钟中断的应用。 定时器初值与中断周期时钟中断无需过于频繁,一般取20mS(50Hz)即可。如需要百分之一秒的时基信号,可取10mS(100Hz)。这里取20mS,用定时器T0工作于16位定时器方式(方式1)。T0的工作方式为:每过一个机器周期自动加1,当计满0FFFFh,要溢出时,便会产生中断,并由硬件设置相应的标志位供软件查询。即中断时比启动时经过了N+1个机器周期。所以,我们只要在T0中预先存入一个比满值0FFFFh小N的数,然后启动定时器,便会在N个机器周期后产生中断。这个值便是所谓的“初值”。下面计算我们需要的初值:时钟为6MHz,12个时钟周期为一 个机器周期,20mS中有10000个机器周期。(10000)10=(2710)16,则0FFFFh-2710h+1=0D8F0h。由于响应中断、保护现场及重装初值还需要 7~8个机器周期,把这个值再加上7,即T0应装入的初值是0D8F7h。每次中断进入后,先把A及PSW的值压入堆栈,然后即把0D8F7h装入T0。 设置一个单元,每次中断加1我们可以取内部RAM中一个单元,取名为INCPI(Increase Per Interrupt),在中断中,装完T0初值后,用INC INCPI指令将其加一。从这个单元中,无论中断程序还是主程序,都可以从中获得20mS的1~256之间任意整数倍的信号。例如:有一段向数码管送显的程序,需要每0.5秒执行一次以便刷新显示器,便可以设一单元(称为等待单元)W_DISP,用 MOV A,INCPI ADD A,#25 MOV W_DISP,A 语句让其比当前的INCPI值大25,然后在每次中断中检查是否于INCPI值相等。若相等,说明已过了25个中断周期,便执行送显程序,并且让W_DISP再加上25,等待下个0.5秒。我们可以设置多个等待单元,以便取出多个不同的时基信号。让中断程序在每次中断时依次查询各个等待单元是否与INCPI相等,若相等,则执行相应的处理,并重新设置该等待单元的值,否则跳过。例如:用0.5秒信号刷新或闪烁显示器,用1秒信号产生实时时钟,或输出一定频率的方波,以一定间隔查询输入设备等。 在中断中读键,通常,我们在主程序中读键盘,步骤为:扫描键盘,若有键按下,则延时几十毫秒去抖动,再次确认此键确实按下,然后处理该键对应的工作,完成后再次重上述步骤。但这有两点不足: 1.处理相应工作时无法锁存按键的输入,即可能漏键。 2.延时去抖时CPU无法做其它事情,效率不高。 如果把读键放入时钟中断中,则可避免上述不足。方法为:如果两次相邻的中断中都读到同一个键按下,则这个键是有效的(达到了去抖目的),并将其锁存到先入先出(队列)的键盘缓冲区,等主程序来处理。这样,主程序处理按键的同时,仍可响应键盘的输入。缓冲区深度通常可设为8级,若锁存的键数多于8个,则忽略新的按键,并报警提示用户新的按键将无效。若键盘缓冲队列停滞的时间大大长于主程序处理按键所需要的最大时间,说明主程序已出错或跑飞,可以在中断用指令将系统复位,起到了看门狗的目的。 主程序中的延时,由于有常开的时钟中断,所以当主程序中有需要时间较短、精度较高的延时时,应暂时把时钟中断关闭。而程序中需要时间较长、精度不高的延时时,便可仿照下需的写法,避免多层嵌套的循环延时。 例:在P1.1输出1秒的高电平脉冲 MOV A,INCPI INC A CJNE A,INCPI$ ;等待一次中断处理完成 SETB P1.1 ;设P1.1为H,脉冲开始 ADD A,#50 ;50个20mS为1秒 CJNE A,INCPI,$ ;等中断将INCPI加一50次 CLR P1.1 ;设P1.1为L,脉冲结束 结束语:从上看出,要灵活地应用时钟中断,将任务合理分配给中断和主程序,并且二者要分工明确,接口简单。这其中的技巧还需要大家在实践中多多摸索与体会。另外要注意:应尽量缩短中断处理程序的执行时间,更不要长于20mS。

新产品开发流程简介 LRBU 2011-8-5

Guiding Principle Time t o M arket: 并行开发,缩短开发时程,加速新产品 导入时间 (Schedule) Time t o V olume:在新产品设计开发时,即能充分考虑成 本 (Cost)、品质(Quality)、易制造 (Manufacturing) 等因素 Time t o M oney:把握DFx之精神,使新产品能在具竞争性 的成本下競爭,快速爬坡大量生产,为公 司带来利润

Terms Definition PM: P roduct M anagement 产品管理 ID: I ndustrial D esign 工业设计 F/W: F irmware 韧体设计 DQA: D esign Q uality A ssurance 设计品质保证 ETP: E ngineering T echnology P latform 工程技术平台 EMC/Safety: E lectric M agnetic C ompatibility 电磁相容/安规 PE: P roduct E ngineering 产品工程 CS: C ustomer S ervice 客户服务 BM: B usiness M anagement 经营管理 IP: I ntellectual P roperty 智慧财产(智权) MRD: M arketing R equirement D ocument 市场需求评估报告 FMEA: F ailure M ode & E ffect A nalysis 失效模式与效应分析 E-BOM: E ngineering B ill O f M aterial 工程材料列表 P-BOM: P roduction B ill O f M aterial 生产材料列表

C51单片机时钟中断及主要问题 一. 中断一般概念 51单片机一共设有5个中断源. 引起CPU中断根源, 成为中断源. 中断嵌套, 也即单片机在处理一个中断时又发生了一个中断, 单片机中断当前中断程序, 转而去处理新的中断程序. 中断优先级, 通过中断优先级寄存器设置. 1. 中断源及其默认优先级 52单片机共有6个中断源, 如下: 符号名称产生条件 INT0 外部中断0 由P3.2端口线引入, 低电平或下降沿引起 INT1 外部中断1 由P3.3端口线引入, 低电平或下降沿引起 T0 定时器/计数器0 由T0计数器计满回零引起 T1 定时器/计数器1 由T1计数器计满回零引起 T2 定时器/计数器2 由T2计数器计满回零引起 TI/RI 串行口中断串行端口完成一帧字符发送/接受后引起 其中, T2是52单片机独有的. 其默认中断优先级别如下: 中断源默认优先级别序号(C语言用) 入口地址(汇编) INT0 最高0 0003H T0 第2 1 000BH INT1 第3 2 0013H T1 第4 3 001BH TI/RI 第5 4 0023H T2 最低 5 002BH 2.中断控制中的特殊功能寄存器SFR (1). 中断允许寄存器IE(Interrupt Enable) 位序号位符号位地址说明 D7(高位) EA 0xAF 全局中断允许位 D6 -- -- 无效位 D5 ET2 0xAD Timer2中断允许位

D4 ES 0xAC 串行口中断允许位 D3 ET1 0xAB Timer1中断允许位 D2 EX1 0xAA 外部中断1中断允许位 D1 ET0 0xA9 Timer0中断允许位 D0(低位) EX0 0xA8 外部中断0中断允许位 备注对于上述所有中断允许位: 1: 打开该中断 0: 关闭该中断 (2). 中断优先级寄存器IP(Interrupt Priority) 位序号位符号位地址说明 D7(高位) -- -- 无效位 D6 -- -- 无效位 D5 -- -- 无效位 D4 PS 0xBC 串行口中断优先级控制位 D3 PT1 0xBB Timer1中断优先级控制位 D2 PX1 0xBA 外部中断1中断优先级控制位 D1 PT0 0xB9 Timer0中断优先级控制位 D0(低位) PX0 0xB8 外部中断0中断优先级控制位 备注对于上述所有中断优先级控制位: 1: 设置对应的中断为高优先级 0: 设置对应的中断为低优先级 二. 单片机的定时器中断 定时器/计数器实质是一个16位的加1计数器, 由高8位(THx)和低8位(TLx)两个寄存器组成. TMOD是定时器/计数器的工作方式寄存器, 确定工作方式和功能; TCON是控制寄存器, 控制T0, T1的启动和停止及设置溢出标志. 1. 定时器/计数器工作方式寄存器TMOD 定时器/计数器工作方式寄存器在特殊功能寄存器中, 字节地址为0x89, 不能位寻址, TMOD 用来确定定时器的工作方式及功能选择. 单片机复位时TMOD全部被清0. 各位的含义如下: 位序号控制位符号说明 D7(高位) Timer1 GA TE 门控制位. 0表示Timer启动与停止仅受TCON寄存 器TRx(x=0, 1)控制

详细设计及实现 一、总体方案 本系统采用Microsoft Visual Studio6.0多层结构开发,以Oracle为后台数据库,系统架构为C/S模型。系统根据职业资格考试的特点,能够完成职业资格考试的全部任务,整个系统包括基本设置、报名、考试编排、成绩管理等模块。 (1)基础设置模块主要是对整个系统进行数据的初始化,按照需要分为基础设置、考工工种设置、考工级别设置、考工考试设置四个功能。 (2)考试报名模块主要实现了考生报名、考生信息查询、考生照片查询三个功能。 (3)考务编排模块主要包括准考证号规则设置,编排考生准考证号,编排考场、考务、监考人员,打印考务材料四个功能。 (4)成绩处理模块包括成绩归档、成绩上报、证书编号回登三个功能。 系统的总体流程图如图1所示。 图1 系统总体流程图

二、界面设计 本系统采用基于任务驱动的功能模块设计,系统采用数据任务模型进行信息处理,终端用户和其它应用通过互联网协议如HTTP/HTTPS、TCP/SSL协议和XML 数据格式申请任务执行请求、提供执行任务参数并指定任务返回数据和格式。任务服务器接受到任务请求后,根据用户提供的参数执行用户指定的数据处理任务,并使用相应的HTML网页、XML数据、WORD文档、MAIL邮件或其它格式将任务处理结果数据返回。 1、登录的实现 系统的登录基于角色来控制,不同的角色登录时对应着不同的口令。 基于角色管理的访问控制由于实现了用户与访问权限的逻辑分离,此策略极大的方便了权限管理。例如,如果一个用户的职位发生变化,只要将用户当前的角色去掉,加入代表新职务或新任务的角色即可。研究表明,角色/权限之间的变化比角色/用户关系之间的变化相对要慢得多,并且委派用户到角色不需要很多技术,可以由行政管理人员来执行,而配置权限到角色的工作比较复杂,需要一定的技术,可以由专门的技术人员来承担,但是不给他们委派用户的权限,这与现实中情况正好一致。除了方便权限管理之外,基于角色的访问控制方法还可以很好的地描述角色层次关系,实现最少权限原则和职责分离的原则。 系统登录窗口采用人性化布局设计,集成了系统初始化完整性校验、已开设考试鉴定工种列表和登录账号、密码和修改密码快捷键F1,账号主要分成三个角色:教务管理员、成绩管理员、各院系,账号的总体控制由教务管理员来操作。如图2所示。 登录账号修改登录密码集成在登录窗口中,在用户选择登录账号后,按F1键弹出修改登录密码窗口,如图3所示。 图2 系统登录窗口

新产品开发控制程序 1、目的 通过对新产品开发活动进行有效策划和控制,确保新开发的产品能满足顾客的质量、成本和交货期的要求。 2、适用范围 适用于本公司之以下类型的新产品开发过程的控制: A类-全新设计开发的新产品; B类-按客户提供样品之参考设计 C类-老产品局部结构改型; D类-老产品之性能改进或增加 3、职责 3.1 新产品开发项目组长:一般由市场部项目主管担当,项目组长按项目开发要求编 制《新产品开发项目进度计划》、协调各部门按进度计划推进新产品开发活动,对对新产品开发项目全过程工作负责; 3.2 新产品开发项目小组负责在策划和设计开发阶段以同步工程的方式开展新产品开 发工作。 3.3相关部门根据《新产品开发项目进度计划》之各部门职能分工,按项目流程计划 节点要求分别承担各自专项工作。 4、工作内容 4.1 新产品项目立项 4.1.1 市场部根据顾客的要求、市场调研及预测的信息提出项目背景资料,填写《产 品开发立项确认书》,并组织由各部门经理参加的项目确认评审会,评审内容主要包括: 产品价格(估价); 市场或客户对新产品的关注点; 新产品与现有技术平台的差异; 开发成本; 产品过程能力的预估分析和投资估算; 顾客的各种要求及时间期限; 可能涉及到的法律、法规(安全性、环保和用后处置)的问题。 4.1.2 经评审通过的项目由评审人员在《产品开发立项确认书》上签字,报总经理批

准立项。 4.1.3 如果此新产品为公司需要全新设计的项目或现有技术平台较差的项目,则需 由开发部组织各部门采用《新产品可行性分析报告》详细分析检讨。 4.2 成立新产品开发项目小组CFT 4.2.1 新产品开发项目经总经理批准后,成立开发项目小组,项目组长由总经理批 准任命,成员将由市场部、开发部、工程部、财务部、品管部、生产部、采 购部等部门项目分管人员组成,必要时将邀请主要供应商担当加入。 4.2.2 项目小组组长组织小组成员进行项目管理,协调与顾客、小组成员间以及各部 门之间的工作,各项目成员之主要职责将由项目组长形成《多功能小组名单和 职责表》来规定。 4.3 建立新产品开发项目管理计划 4.3.1 项目小组组长组织小组成员消化技术资料,根据顾客的要求和希望,结合公 司的技术水平和生产状况,提出产品和过程开发的主要框架,确定所要求的资源情况和管理者的支持。 4.3.2 项目小组长根据顾客要求编制《新产品开发项目进度计划》,明确开发产品的 具体工作内容与完成时间,小组成员会签后报主管副总批准后实施。 《新产品开发项目进度计划》策划时,要做到: 4.3.2.1项目进度计划要依据同步工程明确全过程中相关部门的工作任务,规定起 始和完成时间和检查评审点,落实责任者。 4.3.2.2 项目小组长对项目全过程的进展情况进行跟踪,项目任务若无法如期完成, 相关部门/人员应主动提前告知项目组长,说明未完成原因及打算采取的措 施,已便项目小组对整体计划进行协调更新。 4.3.2.3各相关部门应根据《新产品开发项目进度计划》编制具体的实施计划,其 内容和时间应保持与项目进度计划一致。如果项目不复杂,任务要求可在 项目进度计划中明确,不要求部门再制定分计划。 4.3.2.4项目组长按顾客要求的时间确定各阶段的工作任务和完成各项工作所要求 的重要输出并找出全过程的关键路径。 4.3.2.5《新产品开发项目进度计划》将随客户的新产品开发计划变化而变化,如果 客户或公司内部没有变化,CFT组长均每15天更新一次。更新后的计划以 邮件的形式发送至各小组成员。 4.4 产品设计开发阶段

20.数字钟﹝★﹞1.实验任务 (1.开机时,显示12:00:00的时间开始计时; (2.P0.0/AD0控制“秒”的调整,每按一次加1秒;(3.P0.1/AD1控制“分”的调整,每按一次加1分;(4.P0.2/AD2控制“时”的调整,每按一次加1个小时;2.电路原理图 图4.20.1

3.系统板上硬件连线 (1.把“单片机系统”区域中的P1.0-P1.7端口用8芯排线连接到“动态数码显示” 区域中的A-H端口上; (2.把“单片机系统:区域中的P3.0-P3.7端口用8芯排线连接到“动态数码显示” 区域中的S1-S8端口上; (3.把“单片机系统”区域中的P0.0/AD0、P0.1/AD1、P0.2/AD2端口分别用导线连接到“独立式键盘”区域中的SP3、SP2、SP1端口上; 4.相关基本知识 (1.动态数码显示的方法 (2.独立式按键识别过程 (3.“时”,“分”,“秒”数据送出显示处理方法 5.程序框图

6.汇编源程序 SECOND EQU 30H MINITE EQU 31H HOUR EQU 32H HOURK BIT P0.0 MINITEK BIT P0.1 SECONDK BIT P0.2 DISPBUF EQU 40H DISPBIT EQU 48H T2SCNTA EQU 49H T2SCNTB EQU 4AH TEMP EQU 4BH ORG 00H LJMP START ORG 0BH LJMP INT_T0 START: MOV SECOND,#00H MOV MINITE,#00H MOV HOUR,#12 MOV DISPBIT,#00H MOV T2SCNTA,#00H MOV T2SCNTB,#00H MOV TEMP,#0FEH LCALL DISP MOV TMOD,#01H MOV TH0,#(65536-2000) / 256 MOV TL0,#(65536-2000) MOD 256 SETB TR0 SETB ET0 SETB EA WT: JB SECONDK,NK1 LCALL DELY10MS JB SECONDK,NK1 INC SECOND MOV A,SECOND CJNE A,#60,NS60 MOV SECOND,#00H NS60: LCALL DISP JNB SECONDK,$ NK1: JB MINITEK,NK2 LCALL DELY10MS JB MINITEK,NK2 INC MINITE MOV A,MINITE CJNE A,#60,NM60 MOV MINITE,#00H NM60: LCALL DISP JNB MINITEK,$ NK2: JB HOURK,NK3 LCALL DELY10MS JB HOURK,NK3 INC HOUR

《时钟中断实验》实验报告 姓名: 赵广元 学号: 1428403058 学院: 电子信息学院 班级: 电子信息工程

时钟中断实验 一实验目的 1.熟悉定时器初始化的步骤 2.熟悉定时器控制寄存器(TCR)的含义和使用 3.熟悉定时器中断的原理和使用 二实验设备 本实验设备包括:PC机、CCS2.1和5416DSK开发板 三实验内容 本实验要求编一个简单的定时器中断程序,设置一定的周期控制XF引脚输出电平周期性变化。当定时器中断产生时可以观察到XF引脚输出电平周期性变化。 四实验原理 中断处理: 接受中断请求→应答中断→执行中断服务程序ISR 定时器中断:19号中断 当发生时钟中断时,PC值将指向时钟中断的中断向量地址 中断向量地址的计算方法: (1)取PMST寄存器的IPTR的值(中断向量指针,9位); (2)查DSP的中断表得到时钟中断向量序号19; (3)将中断向量序号19左移2位 (4)将IPTR值左移7位(占高9位)与(3)相加,得到中断向量地址。 中断向量表程序设计: (1)TI54系列DSP最大支持序号0~31的32个中断(存在复用) (2)根据中断向量表地址计算方法,每四个中断向量占四个字(序号左移两位),整个中断向量表共占128个字 (3)硬件复位后,其中断向量表首地址为0xFF80(0号中断地址) (4)软件设置IPTR后,其中断向量表地址发生变化,为使高速响应中断,应在片内RAM中运行定时器: C54X系列的DSP都具有一个或者两个预定标的片内定时器,这种定时器是一个倒数定时器,它可以被特殊的状态位实现停止,重启动,重设置或者静止。定时器在复位后就处于运行状态,为了降低功耗可以禁止定时器工作。应用中可以用定时器来产生周期性的CPU中断或者脉冲输出。定时器的功能方框图如5.1所示,其中有一个主计数器(TIM)和一个预定标计数器(PSC)。TIM用于重装载周期寄存器(PRD)的值,PSC用来重装载周期寄存器(TDDR)的值。

文档编号: 版本号: 密级: XXX详细设计方案(模板) 项目名称:(此处填入项目中文名称) (此处填入项目英文名称) 项目负责人:(此处填入项目负责人) 拟制:年月日审核:年月日批准:年月日

文件控制变更记录 审阅 分发

目录 1引言 5 1.1 编写目的 5 1.2背景 5 1.3 参考资料 5 1.4术语定义及说明 5 22设计概述 5 2.1任务和目标 5 2.1.1需求概述 5 2.1.2运行环境概述 6 2.1.3条件与限制 6 2.1.4详细设计方法和工具 6 3系统详细需求分析 6 3.1详细需求分析 6 3.2接口需求分析 6 4总体方案确认7 4.1系统总体结构确认7 4.2 系统详细界面划分7 4.2.1应用系统与支撑系统的详细界面划分7 4.2.2系统内部详细界面划分7 5系统详细设计7 5.1系统结构设计及子系统划分7 5.2系统功能模块详细设计8 5.3系统界面详细设计8 5.3.1外部界面设计8 5.3.2内部界面设计9 5.3.3用户界面设计9 6数据库系统设计9 6.1设计要求9 6.2信息模型设计9 6.3数据库设计9 6.3.1设计依据9 6.3.2数据库选型9 6.3.3数据库种类及特点9 6.3.4数据库逻辑结构9 6.3.5物理结构设计10 6.3.6数据库安全10 6.3.7数据字典10 7网络通信系统设计10

7.1设计要求10 7.2网络结构确认10 7.3网络布局设计10 7.4网络接口设计11 88信息编码设计11 8.1代码结构设计11 8.2代码编制11 99维护设计11 9.1系统的可靠性和安全性11 9.2系统及用户维护设计11 9.3系统扩充11 9.4错误处理11 9.4.1出错类别11 9.4.2 出错处理11 9.5 系统调整及再次开发问题12 10系统配置12 10.1配置原则12 10.2硬件配置12 10.3软件配置12 1111关键技术12 11.1关键技术的提出12 11.2关键技术的一般说明12 11.3关键技术的实现方案13 12组织机构及人员配置13 13投资预算概算及资金规划13 14实施计划13 14.1限制13 14.2实施内容和进度安排13 14.3实施条件和措施13 14.4系统测试计划13 14.4.1测试策略14 14.4.2测试方案14 14.4.3预期的测试结果14 14.4.4测试进度计划14 14.5验收标准14

478

其中:引脚X1、X2接外部晶振输入端,可直接以32. 768kHz的晶体源驱动;Vbat接后备电源/电容,该引脚不用时接地;SDA为串行数据输入输出端;SCL为串行时钟输入端;IRQ/Fout为中断/频率输出端,可用作中断/频率输出;Vdd和GND为电源和接地端。 3. ISL1208内部结构及其工作原理 ISL1208内部结构框图如图2。由图可知,ISL1208主要包括:I2C接口控制单元、实时时钟控制逻辑、时钟分频器、电源管理单元和寄存器单元。其中寄存器单元被分成四段:实时时钟、控制与状态、报警寄存器和用户SRAM;这四段寄存器各自含有不同的功能:实时时钟和报警寄存器用于写入/读出时间值和报警值,其写入形式为BCD码;控制与状态寄存器可完成对其他寄存器读写控制、报警与频率输出控制、模拟与数字微调控制等功能,其存储映射图如表1。 控制与状态寄存器(Control and Status) 控制与状态寄存器包括状态寄存器、中断与报警寄存器、模拟微调与数字微调寄存器。

状态寄存器(SR):用来控制RTC失效、电池模式、报警触发、时钟计数器写保护、晶体振荡器使能以及状态位的自动复位或者提供相应的状态信息。在时钟上电时,需将写RTC使能位WRTC置“1”,以便 启动时钟计数。 中断控制寄存器(INT):主要用于控制时钟的周期性和单事件报警。其中频率输出控制位FO3-FO0使能/禁止频率输出功能,并选择IRQ/FOUT引脚的输出频率(2-5Hz-215Hz)。在频率模式被激活时它将覆盖IRQ/FOUT引脚上的报警模式。报警使能位ALME使能/禁止报警功能,中断/报警模式位IM使能单 周期定时事件(IM=0)/周期定时事件(IM=1)。 模拟微调寄存器(ATR):ATR0至ATR5为六位模拟微调位,可调整片内负载电容(CX1、CX2)的值,这一电容值用于RTC的频率补偿,其每一位都有不同的电容调节比重。有效的片内串联负载电容CLOA D 的范围从4.5pF至20.25pF,中间值为12.5pF(默认)。CLOAD可通过X1/X2引脚之间两个数字控制 电容器CX1和CX2调节。 数字微调寄存器(DTR):数字微调位DTR0、DTR1和DTR2用来调整每秒钟的平均计数值和平均误差以获取更好的精度。其中DTR2为符号位(DTR2=0频率补偿>0,DTR2=1频率补偿<0),DTR1和DTR 0为刻度位:DTR1提供40ppm调整,DTR0提供20ppm调整。用以上三位可以表示-60ppm至+60ppm 的补偿范围。 4. 应用举例 4.1 硬件结构 ISL1208具有I2C接口,使其便于与各类处理器连接且硬件结构十分简单,传输速率最高可达400Hz。硬件结构如图3。其中时钟输入口SCL、数据输入输出口SDA分别与AT89C51的P1.6、P1.7腿相连,中断输出口IRQ/Fout接外部中断INT0。AT89C51通过RS232口与计算机相连,通过计算机对实时时钟产生 控制。Vbat引脚接后备电容器。