Level Shifters for High-Speed1-V to3.3-V Interfaces

in a 0.13-μm Cu-Interconnection/Low-k CMOS Technology Wen-Tai Wang, Ming-Dou Ker, Mi-Chang Chiang*, and Chung-Hui Chen*

Integrated Circuits & Systems Laboratory National Chiao-Tung University

Hsinchu, Taiwan

*Design Service Devision

Taiwan Semiconductor Manufacturing Company, Ltd.

Hsinchu, Taiwan

A BSTRACT

Level shifters for 1.0-V to 3.3-V high-speed interfaces are proposed. Level-up shifter uses zero-Vt 3.3-V NMOSs as voltage clamps to protect 1.0-V NMOS switches from high voltage stress across the gate oxide. Level-down shifter uses 3.3-V NMOSs as both pull-up and pull-down devices with supply voltage of 1.0-V and gate voltage swing from 0-V to 3.3-V. The zero-Vt NMOS is a standard MOSFET device in a 0.13-μm CMOS process without adding extra mask or process step to realize it. Level-up transition from 0.9-V to 3.6-V takes only 1 ns in time, and the level-down transition has no minimum core voltage limitation. These circuits do not consume static DC power, therefore they are very suitable for low-power and high-speed interfaces in the deep sub-quarter-micron CMOS technologies.

I NTRODUCTION

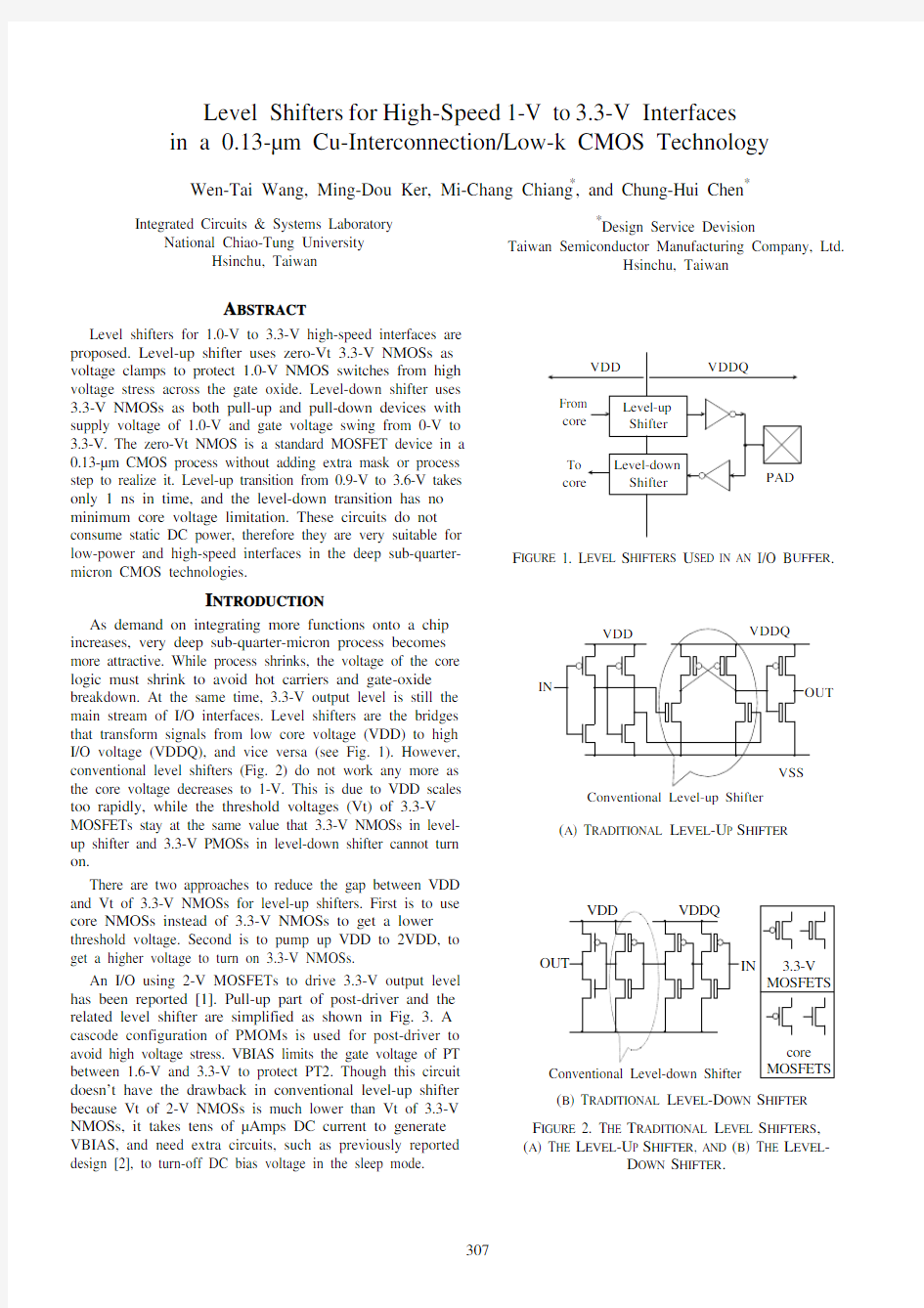

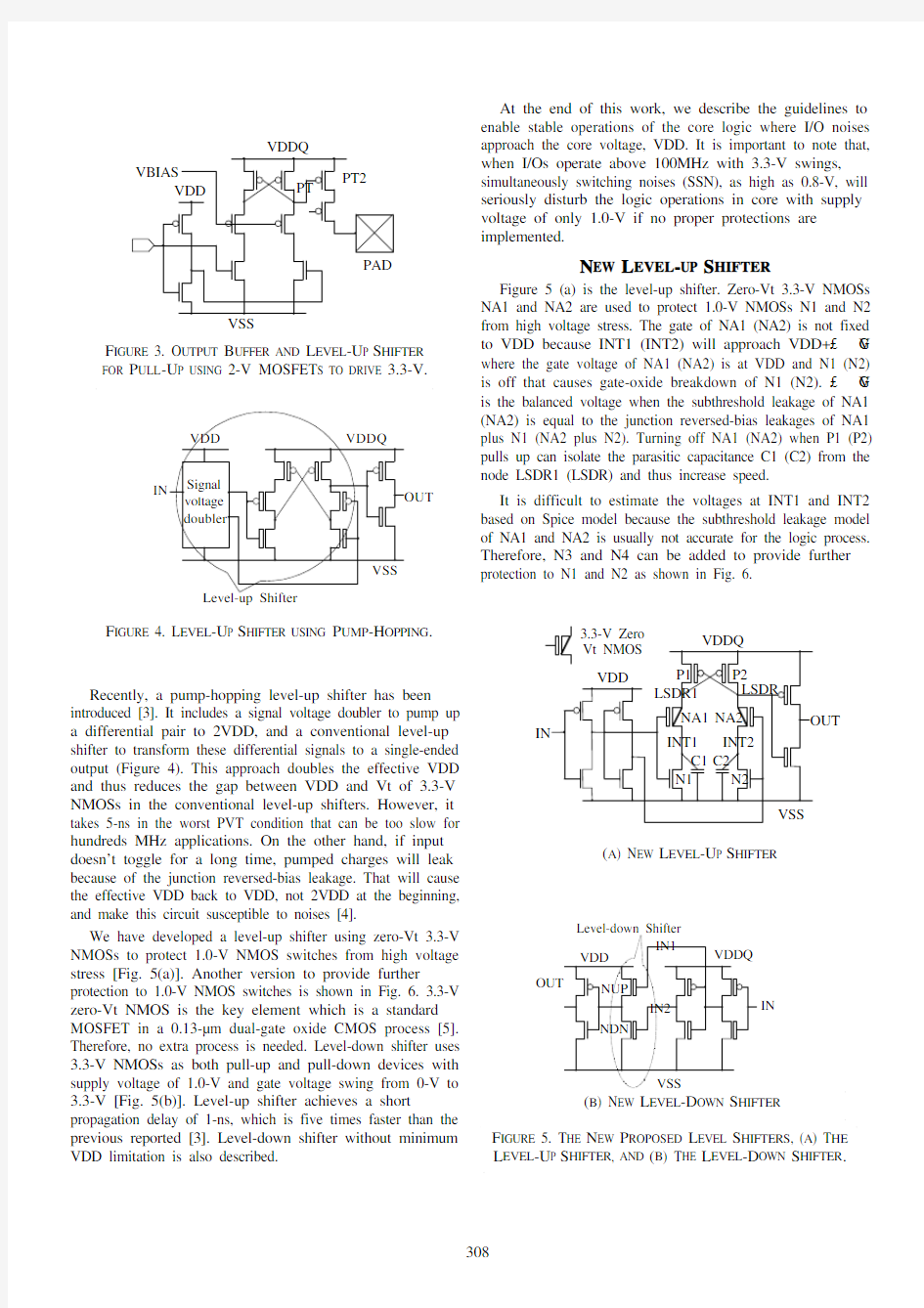

As demand on integrating more functions onto a chip increases, very deep sub-quarter-micron process becomes more attractive. While process shrinks, the voltage of the core logic must shrink to avoid hot carriers and gate-oxide breakdown. At the same time, 3.3-V output level is still the main stream of I/O interfaces. Level shifters are the bridges that transform signals from low core voltage (VDD) to high I/O voltage (VDDQ), and vice versa (see Fig. 1). However, conventional level shifters (Fig. 2) do not work any more as the core voltage decreases to 1-V. This is due to VDD scales too rapidly, while the threshold voltages (Vt) of 3.3-V MOSFETs stay at the same value that 3.3-V NMOSs in level-up shifter and 3.3-V PMOSs in level-down shifter cannot turn on.

There are two approaches to reduce the gap between VDD and Vt of 3.3-V NMOSs for level-up shifters. First is to use core NMOSs instead of 3.3-V NMOSs to get a lower threshold voltage. Second is to pump up VDD to 2VDD, to get a higher voltage to turn on 3.3-V NMOSs.

An I/O using 2-V MOSFETs to drive 3.3-V output level has been reported [1]. Pull-up part of post-driver and the related level shifter are simplified as shown in Fig. 3. A cascode configuration of PMOMs is used for post-driver to avoid high voltage stress. VBIAS limits the gate voltage of PT between 1.6-V and 3.3-V to protect PT2. Though this circuit doesn’t have the drawback in conventional level-up shifter because Vt of 2-V NMOSs is much lower than Vt of 3.3-V NMOSs, it takes tens of μAmps DC current to generate VBIAS, and need extra circuits, such as previously reported design [2], to turn-off DC bias voltage in the sleep mode.

Recently, a pump-hopping level-up shifter has been introduced [3]. It includes a signal voltage doubler to pump up a differential pair to 2VDD, and a conventional level-up shifter to transform these differential signals to a single-ended output (Figure 4). This approach doubles the effective VDD and thus reduces the gap between VDD and Vt of 3.3-V NMOSs in the conventional level-up shifters. However, it takes 5-ns in the worst PVT condition that can be too slow for hundreds MHz applications. On the other hand, if input doesn’t toggle for a long time, pumped charges will leak because of the junction reversed-bias leakage. That will cause the effective VDD back to VDD, not 2VDD at the beginning,and make this circuit susceptible to noises [4].

We have developed a level-up shifter using zero-Vt 3.3-V NMOSs to protect 1.0-V NMOS switches from high voltage stress [Fig. 5(a)]. Another version to provide further protection to 1.0-V NMOS switches is shown in Fig. 6. 3.3-V zero-Vt NMOS is the key element which is a standard MOSFET in a 0.13-μm dual-gate oxide CMOS process [5].Therefore, no extra process is needed. Level-down shifter uses 3.3-V NMOSs as both pull-up and pull-down devices with supply voltage of 1.0-V and gate voltage swing from 0-V to 3.3-V [Fig. 5(b)]. Level-up shifter achieves a short propagation delay of 1-ns, which is five times faster than the previous reported [3]. Level-down shifter without minimum VDD limitation is also described.

At the end of this work, we describe the guidelines to enable stable operations of the core logic where I/O noises approach the core voltage, VDD. It is important to note that,when I/Os operate above 100MHz with 3.3-V swings,simultaneously switching noises (SSN), as high as 0.8-V, will seriously disturb the logic operations in core with supply voltage of only 1.0-V if no proper protections are implemented.

N EW L EVEL -UP S HIFTER

Figure 5 (a) is the level-up shifter. Zero-Vt 3.3-V NMOSs NA1 and NA2 are used to protect 1.0-V NMOSs N1 and N2from high voltage stress. The gate of NA1 (NA2) is not fixed to VDD because INT1 (INT2) will approach VDD+£G V where the gate voltage of NA1 (NA2) is at VDD and N1 (N2)is off that causes gate-oxide breakdown of N1 (N2). £G V is the balanced voltage when the subthreshold leakage of NA1(NA2) is equal to the junction reversed-bias leakages of NA1plus N1 (NA2 plus N2). Turning off NA1 (NA2) when P1 (P2)pulls up can isolate the parasitic capacitance C1 (C2) from the node LSDR1 (LSDR) and thus increase speed.

It is difficult to estimate the voltages at INT1 and INT2based on Spice model because the subthreshold leakage model of NA1 and NA2 is usually not accurate for the logic process.Therefore, N3 and N4 can be added to provide further protection to N1 and N2 as shown in Fig. 6.

Transfer characteristics of proposed and conventional level-up shifters are simulated based on Figure 7 and the results are illustrated in Figure 8. One input pin of each level-up shifter is fixed to VDD and another input pin, IN, is swept from 0-V to VDD. If the level-up shifter can toggle, V(OUT)needs, at least, a voltage drop of Vt below VDDQ to turn on PMOSs at the opposite side. The hardest toggling condition is found at SF process, 0o C, VDDQ = 3.6-V, and VDD = 0.9-V.All MOSFET sizes are listed in Table 1. As shown in Figure 8,even with pull-down NMOSs to pull-up PMOSs ratio as high as 60:1, conventional level-up shifter cannot toggle because V(OUT) only drops to (VDDQ - 0.4-V) as V(IN) = VDD.

Conventional

Proposed

V(IN)

V(OUT)

T ABLE 1. MOSFET S IZES IN F IGURE 7.

P3P4N5N6

1/0.31/0.360/0.3560/0.35

P1P2NA1NA2N1N2N3

N4

1/0.31/0.320/1.220/1.215/0.1315/0.1315/0.1315/0.13

Unit: μm

Fig. 9 shows the simulated waveforms in typical PVT condition (Typical process, 25o C, VDDQ = 3.3-V, and VDD = 1.0-V) using the level-up shifter circuitry shown in Figure 6.Simulations for other PVT conditions show that the maximum propagation delay from IN to OUT is 1-ns at FS process,125o C, VDDQ = 3.0-V, and VDD = 0.9-V.

Optimized sizes of NA1 and NA2 for both speed and noise margin are 10-μm /1.2-μm, half of the current sizes. The reason to chose NA1 and NA2 twice of the optimized size is to reserve guard band before real silicon out. Figure 10 shows if NA1 and NA2 are taken as 10-μm /1.2-μm or 15-μm /1.2-μm, other than 20-μm /1.2-μm, the propagation delays will reduce to 0.75-ns and 0.9-ns, respectively, which is 25% and 10% faster.

Because NMOS switches are composed of core devices,the Vt of core devices will shrink proportionally to supply voltage, VDD. Therefore, by adjusting P1 and P2, this level-IN

OUT LSDR

N EW L EVEL -D OWN S HIFTER

Figure 5 (b) is the level-down shifter. IN1 and IN2 are 3.3-V signals, and VDD is at 1-V that makes pull-up and pull-down devices, NUP and NDN, to have large gate-to-source voltages and thus low resistance. Because NUP and NDN always work in linear region, this circuit can work without any minimum limitation of the core voltage.

F IGURE 8. T RANSFER C HARACTERISTICS OF P ROPOSED

F IGURE 9. S IMULATED W AVEFORMS OF THE

NUP and NDN are optimized with sizes 3-μm /0.35-μm and 3-μm /0.35-μm, respectively. Conventional level-down shifter in Figure 2 has pull-up PMOS size of 30-μm /0.3-μm and pull-down NMOS size of 3-μm /0.35-μm. The worst PVT condition for the conventional one is at SS process, 0o C, and VDD = 0.9-V; VDDQ is not a key factor here. This is because (|Vgs| - |Vt|) of pull-up 3.3-V PMOS dominates the propagation delays. |Vt| increases at low temperature and |Vgs|decreases as VDD goes down to 0.9-V. Simulated waveforms of the worst PVT condition are shown in Figure 11. The conventional one has a propagation delay of 2.5-ns.Meanwhile, the proposed one has a propagation delay of 0.5-ns, which is five times faster.

IN

New Out

Conventional

Out N OISE C ONSIDERATIONS

As I/O frequency above 100MHz and output swing as high as 3.3-V, simultaneously switching noises (SSN) induced by current spike can be as high as 0.8-V which is almost the same amplitude as VDD of 1-V. Therefore, we have the following

guidelines to help stable operations of the pre-driver and the core logic:

a) All NMOSs in Figure 5 (a) use the same ground, VSS,

and layout closely;

b) All NMOSs in Figure 5 (b) use the same ground, VSS,

and layout closely;

c) Use double guard rings to isolate I/O noises from the

pre-driver and the core (Fig 12).

d) Put decoupling capacitors between VDD and VSS;

Decoupling capacitors can be either PMOSs or NMOSs or other active or passive devices.

e) Put as many pick-ups as possible in the core.

Decoupling capacitors are normally used to share the noises at VDD and VSS to a half. Here they are used to make VDD and VSS to follow each other that keeps the voltage difference between VDD and VSS to a constant. Numerous pick-ups are used to help the substrate to follow the VSS C ONCLUSION

Level shifters for 1.0-V to 3.3-V interfaces are developed in a 0.13-μm CMOS process. Level-up shifter uses zero-Vt 3.3-V NMOSs to protect 1.0-V NMOS switches and level-down shifter uses 3.3-V NMOSs as both pull-up and pull-down devices. No extra process step, no DC power and high-speed make these level shifters suitable for low power and high-speed applications. These techniques work even at VDD below 1.0-V in the future.

A CKNOWLEDGEMENTS

We would like to thank CS Chen for useful discussions,and Cindy Lu for layout assistance.

R EFERENCES

[1] L. T. Clark, “A high-voltage output buffer fabricated on a 2V

CMOS technology,” in Proc. of Symp. on VLSI Circuits , June 1999, pp. 61-62.

[2] H. Sanchez, et al., “A versatile 3.3/2.5/1.8-V CMOS I/O driver

built in a 0.2-μm, 3.5-nm Tox, 1.8-V CMOS technology,” IEEE J. Solid-State Circuits , vol. 34, pp. 1501-1511, Nov. 1999.

[3] Y. Kanno, et al., “Level converters with high immunity to

power-supply bouncing for high-speed sub-1-V LSIs,” in Proc.of Symp. on VLSI Circuits , June 2000, pp. 202-203.

[4] E. Seevinck, et al., “Static-noise margin analysis of MOS

SRAM cells,” IEEE J. Solid-State Circuits , vol. 22, pp. 748-754,Oct. 1987.

[5] K.-K. Young, et al ., “A 0.13μm CMOS technology with 193nm

lithography and Cu/low-k for high performance applications,”in Tech. Dig. of IEDM , Dec., 2000.

F IGURE 11. S IMULATED W AVEFORMS OF L EVEL -D OWN S HIFTER .

Cambridge International AS & A Level DC (JC/CT) 182587/3? UCLES 2020 [Turn over This document has 12 pages. Blank pages are indicated. *5745011940* PHYSICS 9702/33 Paper 3 Advanced Practical Skills 1 February/March 2020 2 hours You must answer on the question paper. You will need: The materials and apparatus listed in the confidential instructions INSTRUCTIONS ●Answer all questions. ●Use a black or dark blue pen. You may use an HB pencil for any diagrams or graphs. ●Write your name, centre number and candidate number in the boxes at the top of the page. ●Write your answer to each question in the space provided. ●Do not use an erasable pen or correction fluid. ●Do not write on any bar codes. ●You will be allowed to work with the apparatus for a maximum of 1 hour for each question. ●You should record all your observations in the spaces provided in the question paper as soon as these observations are made. ●You may use a calculator. ●You should show all your working and use appropriate units. INFORMATION ●The total mark for this paper is 40. ●The number of marks for each question or part question is shown in brackets [ ]. For Examiner’s Use 12Total

Section 6: Oscillations Revision spread1 : Simple harmonic motion Checkpoints : (1)recall that the condition for simple harmonic motion is F=-kx Identify situations in which simple harmonic motion will occur. (2) recognize and use the expressions a=-ω2x, a=-Aω2xcosωt, v=-Aωsinωt,x=A cosωt,and T=1/f=2π/ωas applied to a simple harmonic oscillator. (3) obtain a displacement-time graph for an oscillating object and recognize that the gradient at a point gives the velocity at that point. (201306-1)A mass is bouncing on the end of a vertical spring. Its motion will be simple harmonic if the spring A .can store energy. B .has elasticity. C .is hung vertically. D .obeys Hooke’s law. (201206-4)Which of the following is not an example of simple harmonic motion? A A car bouncing on its suspension system. B A child jumping on a trampoline. C A person bouncing on the end of a bungee cord. D A swinging pendulum in a grandfather clock. 201301

一般词汇 数学mathematics, maths(BrE), math(AmE) 公理axiom 定理theorem 计算calculation 运算operation 证明prove 假设hypothesis, hypotheses(pl.) 命题proposition 算术arithmetic 加plus(prep.), add(v.), addition(n.) 被加数augend, summand 加数addend 和sum 减minus(prep.), subtract(v.), subtraction(n.) 被减数minuend

减数subtrahend 差remainder 乘times(prep.), multiply(v.), multiplication(n.) 被乘数multiplicand, faciend 乘数multiplicator 积product 除divided by(prep.), divide(v.), division(n.) 被除数dividend 除数divisor 商quotient 等于equals, is equal to, is equivalent to 大于is greater than 小于is lesser than 大于等于is equal or greater than 小于等于is equal or lesser than 运算符operator 数字digit 数number

自然数natural number 整数integer 小数decimal 小数点decimal point 分数fraction 分子numerator 分母denominator 比ratio 正positive 负negative 零null, zero, nought, nil 十进制decimal system 二进制binary system 十六进制hexadecimal system 权weight, significance 进位carry 截尾truncation 四舍五入round

英国高中Alevel课程介绍 一、课程体系 英国高中课程(General Certificate of Education Advanced Level)简称A-Level课程,于1951年在英国正式启用。它是英国的全民课程体系,也是英国学生的大学入学考试课程,A-Level课程证书被几乎所有英语授课的大学作为招收新生的入学标准。因此,A-Level课程被国际教育界誉为“金牌”教育方式(British Golden Education System)。英国学生一般在16岁或稍大一些开始学习这种课程,圆满修完这种课程即可进入大学就读。这种课程可以简单理解为中国的高中。能否上英国大学特别是好的名牌大学,A Level成绩是关键。 二、课程的权威性 该课程体系的教学大纲、课程设置及其考试分别由英国四个主要考试 局Cambridge International Examinations,简称 CIE, Oxford Cambridge and RSA Examinations 简称 OCR, Assessment and Qualifications Alliance 简称AQA 和EDEXEL设计并组织,其权威性得到了国际上的广泛认可。迄今为止,全球已有5000多个教育机构开设了英国高中课程,每年有数百万学生参加由这些考试局组织的统一考试。由于该课程的科学性和权威性,新加坡甚至直接将该课程考试作为大学入学的全国统一考试。 三、教学质量控制 英国国家考试局对每一个开设A-Level的高级附属中心都进行严格的教学质量控制措施。每一位教授A-Level课程的老师都经过严格的筛选和测评。同时,老师们也可以通过多种渠道得到英国国家考试局的协助和培训。为了监控分布在世界上150多个国家教育中心的教学质量,这些考试局已经在全球各地建立了完善的组织网络;通过其批准的高级附属中心,不定期地对教学质量进行检查和评定。从而保证每一个就读A-Level课程的学生能接受到高质量的教育。 四、A-Level课程的优点 除大学预科课程之外,A-Level课程是中国学生入读英国大学的最佳途径。这是因为A-Level课程要大大优于大学基础课程,其优点有以下三方面: 第一、中国学生在国内的高一或高二的在校学生可以赴英国学习A-Level课程。这样,他们再经过两年的学习就可以进入英国大学就读,而不是像在中国那样,高中毕业然后还要学习一年的大学预科课程,才能入读英国大学。 第二、这种课程是为中国学生进入英国大学做准备的理想课程。无论是在学业方面还是在语言方面都会高于大学基础课程可达到的程度。中国学生要用英语学习各门课程,亲自体验新的教学方法,其英语也会达到相当熟练的程度。 第三、牛津、剑桥、帝国理工和伦敦大学学院这样的名牌英国大学几乎是从不录取大学预科的学生,而只录取A-Level毕业证书或同等学历的学生。同样,如果没有A-Level毕业证书或同等学历,要想就读像医科或医疗卫生领域的某些课程

而选择IB课程,学生必须在第二语言、社会科学、英语、实验科学和数学这几门课程中修满并至少拿到3门的高分数。此外还需要选择一个选修课,2个学期的Theory of Knowledge,2年内150小时的社会实践活动以及写一篇4000字的论文。 学生必须在课程开始之前制定出选课方案,具体时间可以在10年级结束或者11年级的开始。 IB课程学科设置及考试 参与IB文凭项目的学生要获得文凭,在两年里要从6个学术领域的学科板块中选择6门课程进行学习,并通过考核,还要完成3项必选拓展课程。由于课程的深度与广度的关系,课程分为高级(High Level,简称HL)与标准(Standard Level,简称SL)两个层次。

课程板块 第一板块:语言A1与世界文学 第二板块:语言B(母语以外的现代语) 第三板块:个人与社会学(历史、地理、经济学、哲学、心理学等) 第四板块:实验科学(物理、化学、生物、设计、环境系统等) 第五板块:数学(数学高等级、高等数学标准等级、数学研究、数学法) 第六板块:艺术与选修(美术设计、音乐、戏剧艺术等,或第三种现代语,或从第三组、第四组中再选一科,或高等数学标准等级) 每个学生要从六大基础学科组的每一组中选出一科学习。每个科目分两个层次:标准课程与高级课程。每科标准课程的教学时数是150学时,高级课程教学时数是不少于240学时。 在学生选择的ib预科课程的六门科目中,最少三门最多四门是高级课程,其他是标准课程,这样即保证了学科基础的宽度,又具有足够学术深度。

学生自学超过六门(或高级课程超过四门)当然没有限制。各个学科组的课程都始终在不断地检验与更新之中,以适应该学科领域的最新发展。 学通国际课程培训中心自2008年起一直致力于ALEVEL、IGCSE、IB、AP、SAT2等主流国际课程中30多门科目的提分与培优,经11年深耕教学,目前已拥有教师团队80余人,其中20%为博士,80%为名校海归硕士,平均国际课程教龄8年以上,每年为学生提供50000小时以上的高品质课程。除常规国际课程培训外,我们还提供“G5全程护航计划”——全天候全脱产式学习,“全球TOP10大学冲击计划”——高考留学两不误双轨制ALEVEL课程,国际学校备考与衔接课程,英国G5名校STEP、MAT、PAT、TSA、牛剑面试等附加考试辅导,海外学校iTEP、Ukiset、AEAS、AEIS、维立克面试等入学考试辅导课程;同时还提供个性化的学术背景提升项目。

ALevel课程被很多家长成为“洋高考”,它已经变得不再陌生,在北上广深等城市已发展得如火如荼,完成Alevel课程可以帮助学生申请欧美大学,而得到优异的分数更是成为学生们可以进入英国殿堂级的高校敲门砖。 但是很多家长和学生并不了解,ALevel课程体系的教学大纲、课程设置及其考试在英国本土分别有英国三个主要考试局,其中Alevel在中国设有考试中心,所以也是学生报名学习较多的一个考试局。 下面我们一起来了解一下Alevel的物理考试大纲吧: 该表格向我们展示了教学大纲中包含的Alevel重点知识内容,下面我们一起来看一下

ALEVEL物理学的内容包括:普通物理、牛顿力学、物质、振动及波、电学与磁学、现代物理等板块。整个学习的内容跟国内的教材基本相同,但是ALEVEL课程的重点放在物理现象的理解和描述,而国内的课程更偏向于计算。学生学习的过程中会发现,计算的内容并

不难。难点是考试中如何通过计算出来的结果,分析和准确的描述和解释问题中所问的物理现象。这类题目呢,叫做陈述题,ALEVEL考试中大约30%-40%的的分数是这类题目,学生往往会在这上面丢掉不少分数。 整个Alevel物理学部分有5张,我们可以把他分为paper 1到paper 5,AS阶段需要完成选择题、简答计算题、实验操作题,而在A2阶段需要完成的是简答计算题含应用物理以及实验设计题。 学通国际课程培训中心自2008年起一直致力于ALEVEL、IGCSE、IB、AP、SAT2等主流国际课程中30多门科目的提分与培优,经11年深耕教学,目前已拥有教师团队80余人,其中20%为博士,80%为名校海归硕士,平均国际课程教龄8年以上,每年为学生提供50000小时以上的高品质课程。除常规国际课程培训外,我们还提供“G5全程护航计划”——全天候全脱产式学习,“全球TOP10大学冲击计划”——高考留学两不误双轨制ALEVEL课程,国际学校备考与衔接课程,英国G5名校STEP、MAT、PAT、TSA、牛剑面试等附加考试辅导,海外学校iTEP、Ukiset、AEAS、AEIS、维立克面试等入学考试辅导课程;同时还提供个性化的学术背景提升项目。

10月的Alevel已经结束一段时间了,而明年的Alevel还会远?每年都有新的考生参加其中,想必给位都在努力学习吧。那么今年数学考试有哪些变化呢,下面就为大家介绍一下。 Edexcel去年第一次开始考新版大纲,也就是这里看到的P打头的科目,Pure纯数部分,以前是C打头的叫做Core。 国际版新版大纲中只有P1-P4和D1(Decision1,决策数学,跟计算机有点关系,一般会放在高数里面学)的大纲变了,其他的都没有变。今年10月的考试还是新旧版考试都存在的过渡阶段。 一、参加10月份考试的大致分两类人: 1、补考; 2、基础好的或者暑期预学了提早参加考试。 对于补考的学生来说,大部分是选其中一门进行补考,只需要冲刺这门就可以,一般来说都是补考C34。因为数学A*的标准要求C34达90%,总分达80%。C34重点内容也有很多。 比如三角函数(trigonometry),比如微分(differentiation),比如积分(integration),甚至重点内容还会交叉,顺带考一些小的知识点,比如可以用一个parametricequation的题把上述三个重点全串在一起。但如果说重中之重,那一定是integration。Integration里面的内容过于繁杂,列表如下。

6.1-6.4和6.6是积分的计算,是提醒大家有几个不常见的公式在公式表上都有给出,6.5和6.7是积分的应用,包括C12中的求面积和体积。最重要的还是微分的计算,这块是基础,所以要求学生能够熟练做出以下的积分是很有必要的: 6.2部分 6.3部分

6.4部分 这些做好了,微积分就不用再害怕了,才能披荆斩棘继续进行下一步积分的应用。至于其他的知识点,比如经常会出现错误的微分chain rule,这里就不一一说明。大家在刷题过程中要了解自己在哪里容易错,然后对这些点进行挨个击破。 学通国际课程培训中心自2008年起一直致力于ALEVEL、IGCSE、IB、AP、SAT2等主流国际课程中30多门科目的提分与培优,经11年深耕教学,目前已拥有教师团队80余人,其中20%为博士,80%为名校海归硕士,平均国际课程教龄8年以上,每年

Newton's Laws Name: Newton's Second Law Problem-Solving Study from Lessons 3 of the Newton's Laws chapter at The Physics Classroom: https://www.doczj.com/doc/677840148.html,/Class/newtlaws/u2l3c.html https://www.doczj.com/doc/677840148.html,/Class/newtlaws/u2l3d.html For the following problems, construct a free-body diagram and show your work clearly. 1. A rightward force of 302 N is applied to a 28.6-kg crate to accelerate it across the floor. The coefficient of friction between the crate and the floor is 0.750. Determine the acceleration of the crate. 2. During a football workout, two linemen are pushing the coach on the sled. The combined mass of the sled and the coach is 300. kg. The coefficient of friction between the sled and the grass is 0.800. The sled accelerates at a rate of 0.580 m/s/s. Determine the force applied to the sled by the lineman. 3. A 405-N rightward force is use to drag a large box across the floor with a constant velocity of 0.678 m/s. The coefficient of friction between the box and the floor is 0.795. Determine the mass of the box. 4. A 6.58 x 103 N upward tension force is exerted on a 521-kg downward-moving freight elevator. Determine the acceleration of the elevator.

数学mathematics, maths(BrE), math(AmE) 公理axiom 定理theorem 计算calculation 运算operation 证明prove 假设hypothesis, hypotheses(pl.) - 命题proposition 算术arithmetic 加plus(prep.), add(v.), addition(n.) 被加数augend, summand 加数addend 和sum 减minus(prep.), subtract(v.), subtraction(n.) 被减数minuend ~ 减数subtrahend 差remainder 乘times(prep.), multiply(v.), multiplication(n.) 被乘数multiplicand, faciend 乘数multiplicator 积product 除divided by(prep.), divide(v.), division(n.) 被除数dividend # 除数divisor 商quotient 等于equals, is equal to, is equivalent to 大于is greater than 小于is lesser than 大于等于is equal or greater than 小于等于is equal or lesser than 运算符operator - 数字digit 数number 自然数natural number 整数integer 小数decimal 小数点decimal point } 分数fraction 分子numerator 分母denominator 比ratio 正positive 负negative 零null, zero, nought, nil 十进制decimal system > 二进制binary system 十六进制hexadecimal system 权weight, significance 进位carry 截尾truncation 四舍五入round 下舍入round down 上舍入round up — 有效数字significant digit 无效数字insignificant digit 代数algebra 公式formula, formulae(pl.) 单项式monomial 多项式polynomial, multinomial 系数coefficient 未知数unknown, x-factor, y-factor, z-factor : 等式,方程式equation 一次方程simple equation 二次方程quadratic equation 三次方程cubic equation 四次方程quartic equation 不等式inequation 阶乘factorial

Mark scheme (Results) Summer 2016 Pearson Edexcel GCE AS Level in Economics A (8EC0) Paper 01 Introduction to markets and market failure

Edexcel and BTEC Qualifications Edexcel and BTEC qualifications are awarded by Pearson, the UK’s largest awarding body. We provide a wide range of qualifications including academic, vocational, occupational and specific programmes for employers. For further information visit our qualifications websites at https://www.doczj.com/doc/677840148.html, or https://www.doczj.com/doc/677840148.html,. Alternatively, you can get in touch with us using the details on our contact us page at https://www.doczj.com/doc/677840148.html,/contactus. Pearson: helping people progress, everywhere Pearson aspires to be the world’s leading learning company. Our aim is to help everyone progress in their lives through education. We believe in every kind of learning, for all kinds of people, wherever they are in the world. We’ve been involved in education for over 150 years, and by working across 70 countries, in 100 languages, we have built an international reputation for our commitment to high standards and raising achievement through innovation in education. Find out more about how we can help you and your students at: https://www.doczj.com/doc/677840148.html,/uk Summer 2016 Publications Code 8EC0_01_1606_MS All the material in this publication is copyright ? Pearson Education Ltd 2016

alevel数学试卷答案 一、填空题 1.一元二次方程的一般形式是__________. 2将方程-5x2+1=6x化为一般形式为__________. 3.将方程(x+1)2=2x化成一般形式为__________. 4.方程2x2=-8化成一般形式后,一次项系数为__________,常数项为 __________. 5.方程5(x2-x+1)=-3x+2的一般形式是__________,其二次项是 __________,一次项是__________,常数项是__________. 6.若ab≠0,则x2+x=0的常数项是__________. 7.如果方程ax2+5=(x+2)(x-1)是关于x的一元二次方程,则a__________. 8.关于x的方程(m-4)x2+(m+4)x+2m+3=0,当m__________时,是一元二次方程,当m__________时,是一元一次方程. 二、选择题 1.下列方程中,不是一元二次方程的是( ) A.2x2+7=0 B.2x2+2x+1=0 C.5x2++4=0 D.3x2+(1+x) +1=0 2.方程x2-2(3x-2)+(x+1)=0的一般形式是( ) A.x2-5x+5=0 B.x2+5x+5=0 C.x2+5x-5=0 D.x2+5=0 3.一元二次方程7x2-2x=0的二次项、一次项、常数项依次是( ) A.7x2,2x,0 B.7x2,-2x,无常数项 C.7x2,0,2x D.7x2,-2x,0 4.方程x2-=(-)x化为一般形式,它的各项系数之和可能是( ) A. B.-C. D. 5.关于x的方程(ax+b)(d-cx)=m(ac≠0)的二次项系数是ac,则常数项为( ) A.m B.-bd C.bd-m D.-(bd-m) 6.若关于x的方程a(x-1)2=2x2-2是一元二次方程,则a的值是( ) A.2 B.-2 C.0 D.不等于2 7.若x=1是方程ax2+bx+c=0的解,则( ) A.a+b+c=1 B.a-b+c=0 C.a+b+c=0 D.a-b-c=0 8.关于x2=-2的说法,正确的是( ) A.由于x2≥0,故x2不可能等于-2,因此这不是一个方程 B.x2=-2是一个方程,但它没有一次项,因此不是一元二次方程

Core Mathematics1(AS/A2)——核心数学1 1.Algebra and functions——代数和函数 2.Quadratic functions——二次函数 3.Equations and inequalities——等式和不等式 4.Sketching curves——画图(草图) 5.Coordinate geometry in the (x,y)plane——平面坐标系中的坐标几何 6.Sequences and series——数列 7.Differentiation——微分 8.Integration——积分 Core Mathematics2(AS/A2)——核心数学2 1.Algebra and functions——代数和函数 2.The sine and cosine rule——正弦和余弦定理 3.Exponentials and logarithm——指数和对数 4.Coordinate geometry in the (x,y)plane——平面坐标系中的坐标几何 5.The binomial expansion——二项展开式 6.Radian measure and its application——弧度制及其应用 7.Geometric sequences and series——等比数列 8.Graphs of trigonometric functions——三角函数的图形 9.Differentiation——微分 10.Trigonometric identities and simple equations——三角恒等式和简单的三角等式 11.Integration——积分 Core Mathematics3(AS/A2)——核心数学3 1.Algebra fractions——分式代数 2.Functions——函数 3.The exponential and log functions——指数函数和对数函数 4.Numerical method——数值法 5.Transforming graph of functions——函数的图形变换 6.Trigonometry——三角 7.Further trigonometric and their applications——高级三角恒等式及其应用 8.Differentiation——微分 Core Mathematics4(AS/A2)——核心数学4 1.Partial fractions——部分分式 2.Coordinate geometry in the (x,y)plane——平面坐标系中的坐标几何 3.The binomial expansion——二项展开式 4.Differentiation——微分 5.Vectors——向量 6.Integration——积分

Alevel选课和大学专业到底有什么关系 PART1哪些大学和专业对AL科目有要求 1、有些大学课程会招收特定A-Level课程的学生 有些英国大学课程会要求申请者学习某些特定的A-Level课程,并取得相应的成绩,如果学生未达到要求,学生是没有资格申请的。 比如:药剂学专业要求申请者A-Level课程必修化学,且至少选修生物、数学、物理中的任一科。(医学专业需要加考其他考试如UKCAT和MAT) 英语专业通常要求申请者A-Level课程必修英国文学,有时也可能是英语语言文学或英语语言学。 地质学/地学专业要求申请者A-Level课程必修数学、物理、化学以及生物学中的任两科。 2、选择大学各专业入学要求中频繁出现的课程,会给你大学专业更多的选择 选择A-Level课程前你还不确定自己大学想学什么专业?别担心,这样的学生可不止你一个。 也许你很清楚心仪的大学是哪一所,却并不知道想学什么专业。这时,不妨选择一些较为广泛地符合大学入学要求的Alevel科目,做一个“聪明的搭配”,以确保未来的专业选择更加多样化。例如: Biology Chemistry English Geography History Maths Modern and Classical Languages Physics 选择得越多,可以选择的课程就越多。此外,如果你有艺术、设计或者音乐方面的天分,并可能将其作为未来事业追求的方向,那么就选一些与此相关的Alevel 科目吧。 有些大学公开反对学生的某些特定的学科组合,尤其是非常类似的几门课,比如business studies(商业研究)和economics(经济学),所以在选课时,尤其要避免选择这样的课程组合。 3、A-Level课程要比GCSE难学得多

Alevel物理干货:Doppler Effect 多普勒效应(Doppler Effect)这个名字也许唬住了很多学生,其实这是一个在我们日常生活中经常会见到的现象。当一个声源面向我们靠近的时候,我们听到的声音越来越高;反之,当声源渐渐远离我们,我们听到的声音就会越来越低。回想一下,一辆救护车或者警车不断尖叫着向你驶来的场景,应该会很容易理解这个现象。但就是这么一个简单的事情,引起了物理学家多普勒的兴趣,他对此研究发展出了自己的一套理论。另外,体检过的学生一定都对彩超机器不陌生,实际上,彩超所应用的原理也是多普勒效应。所以说,多普勒效应与我们的生活息息相关。 我们的生活中充满了这样那样的原理,虽然我们并不掌握这些原理,但并不影响我们的正常活动。举个简单的例子,每个人都有手机,手机上下载了各种各样的APP,没有几个人真正了解APP应用的原理,但这并不妨碍我们使用手机。因此人们觉得对这些原理了解与否,并没有什么实质性的改变。其实不然,当你对一个原理了解越多的时候,你就会“活得明白”,而且还能增加一些小小的乐趣。 要了解多普勒效应,首先需要知道多普勒是谁? 多普勒全名克里斯琴·约翰·多普勒,1803年出生于奥地利的萨尔茨堡。克里斯琴·多普勒家族并非科学世家,他们家族经营石匠生意,而按照家族的传统多普勒则理所当然成了生意的接班人。但是多普勒从小体弱多病,这使得他免于承担生意生的重任。试想一下,如果多普勒当时继承家族生意,那么世界上就会多一个毫不显眼的石匠商人,而少了一颗璀璨的科学明珠。 多普勒肖像图 多普勒并非一开始就从事物理学研究,1829年他毕业于维也纳大学,被任命为高等数学和力学教授的助理,在这段时间他发表了几篇论文。但四年之后,他不知想起什么又跑到一家工厂当会计,之后又来到布拉克一所技术中学担任老师,同时还在布拉格理工学院任着兼职讲师。1841年,教学出色的多普勒得到扶正,成为了理工学院的数学教授。

精编l e v e l数学简介 TPMK standardization office【 TPMK5AB- TPMK08- TPMK2C- TPMK18】

第三节英国A-level数学课程 一.A-level课程优势及其介绍 英国高中课程(General Certificate of Education Advanced Level )简称A-Level课程,它是英国的普通中等教育证书考试高级水平课程,是英国的全民课程体系,也是英国学生的大学入学考试课程,就像我国的高考一样,A-Level课程证书被几乎所有英语授课的大学作为招收新生的入学标准。在中国开设A-Level课程旨在为中国学生提供进入国外大学的有效途径,具体目标为:培养在国内初高中成绩优秀的学生进入世界顶尖大学;培养在国内初高中成绩中等的学生进入世界一流大学;培养在国内初高中成绩一般的学生考取适合自己的大学。 这种课程要求学生学习三门或四门主科课程并参加毕业考试,考试合格者即可进入大学就读。学生的考试成绩及其所选修的A-Level课程在很大程度上决定着能否进入理想的大学和学习所选择的学位课程。英国的大多数中学开设的A-Level课程科目相当广泛,有文科、商科、经济、语言、数学、理科、计算、法律、媒体、音乐等。 该课程体系的教学大纲、课程设置及其考试分别由英国四个主要考试局 Cambridge International Examinations, 简称CIE, Oxford Cambridge and RSA Examinations 简称OCR, Assessment and Qualifications Alliance 简称AQA 和EDEXCEL等设计并组织,其权威性得到了国际上的广泛认可。迄今为止,全球已有5000多个教育机构开设了英国高中课程,每年有数百万学生参加由这些考试局组

2010美国大学中国录取名单信息数据 选取部分 (一)综合大学 综合大学 Harvard College(哈佛大学,综合排名1) RD: 2 from NFLS (1 SAT 2400; 1 SAT 2230; both full aid) Princeton University(普林斯顿大学,综合排名1) RD: 1 from FDFZ Yale College(耶鲁大学,综合排名3) REA(共6人): 1 from FDFZ (S2330, ACT35, T120, AP, exchange, full FA); 1 from NFLS (S2330, S2 2400, T113, full FA); 1 from 新加坡高中(原北京, S2360, T116, no FA) RD: 1 from NFLS(SAT2310,曾在新西兰生活) 1 from NFLS(SAT2300+, exchange) California Institute of Technology (加州理工学院,综合排名4) EA: 1 from 上海(国际科技节金奖) RD: 1 from 宁波镇海中学(S2310, T110, FA 48k+); 1 from 长沙一中(S2280, T103); 1 from RJC (S2230, 7AP, 5Alevel, 新加坡数学奥赛金牌);1 from HFLS(SAT 2250 T117,全国物理一等,走进西澳第一名)! Stanford University(斯坦福大学,综合排名4) REA: 1 from 美国高中Deerfield (原SFLS); 1 from 江阴一中(S2230, T108, no FA) University of Pennsylvania,(宾夕法尼亚大学,综合排名4) --Fisher/Huntsman/Vagelos/Wharton ED: 1 from SZMS(Huntsman); 1 from HFLS; 1from NSFZ(S2300 sat2 2300+, green card, IB, 美国初中, ABC, Wharton); 1 from NEYC; 1 from VJC (S2200+,ALEVEL,Wharton); 1 from 英国高中(S2300, T117, ALEVEL, Huntsman); 1 from RDFZ (S2100+, ALEVEL) Columbia College (Columbia University) 哥伦比亚学院(哥伦比亚大学,综合排名8) ED:1 from 上海平和学校(T101, IB) RD: 1 from 上海(international school); 1 from 成都七中(FA 27k) Columbia College (Columbia University) ED: 1 from HFLS (S2190, T108, no FA) 1 from 清华附中1 from 山东 Columbia Engineering (Columbia University) ED: 1 from 北京十一学校(S2200 T104) 7 _+ @) h2 University of Chicago(芝加哥大学,综合排名8) EA: 1 from 美国高中(S2120, T106, 原深圳)

Edexcel GCE in Mathematics Mathematical Formulae and Statistical Tables For use in Edexcel Advanced Subsidiary GCE and Advanced GCE examinations Core Mathematics C1 – C4 Further Pure Mathematics FP1 – FP3 Mechanics M1 – M5 Statistics S1 – S4 For use from January 2008 UA018598

TABLE OF CONTENTS Page 4 Core Mathematics C1 4 Mensuration 4 Arithmetic series 5 Core Mathematics C2 5 Cosine rule 5 Binomial series 5 Logarithms and exponentials 5 Geometric series 5 Numerical integration 6 Core Mathematics C3 6 Logarithms and exponentials 6 Trigonometric identities 6 Differentiation 7 Core Mathematics C4 7 Integration 8 Further Pure Mathematics FP1 8 Summations 8 Numerical solution of equations 8 Coordinate geometry 8 Conics 8 Matrix transformations 9 Further Pure Mathematics FP2 9 Area of sector 9 Maclaurin’s and Taylor’s Seri es 10 Taylor polynomials 11 Further Pure Mathematics FP3 11 Vectors 13 Hyperbolics 14 Integration 14 Arc length 15 Surface area of revolution UA018598 – Edexcel AS/A level Mathematics Formulae List: C1 – C4, FP1 – FP3 – Contents Page – Issue 1 – September 2007 1