D Wake-Up From Standby Mode in Less Than 6 μs

D 16-Bit RISC Architecture,

125-ns Instruction Cycle Time D 12-Bit A/D Converter With Internal Reference, Sample-and-Hold and Autoscan Feature

D 16-Bit Timer_B With Three ? or Seven ?

Capture/Compare-With-Shadow Registers D 16-Bit Timer_A With Three Capture/Compare Registers D On-Chip Comparator

D

Serial Communication Interface (USART),Select Asynchronous UART or Synchronous SPI by Software:

? Two USARTs (USART0, USART1) —MSP430x44x Devices ? One USART (USART0) — MSP430x43x(1) Devices D Brownout Detector

D

Supply Voltage Supervisor/Monitor With Programmable Level Detection

D Bootstrap Loader

D

Family Members Include:

? MSP430F435, MSP430F4351§:

16KB+256B Flash Memory,512B RAM

? MSP430F436, MSP430F4361§:

24KB+256B Flash Memory,1KB RAM

? MSP430F437, MSP430F4371§:

32KB+256B Flash Memory,1KB RAM

? MSP430F447:

32KB+256B Flash Memory,1KB RAM

? MSP430F448:

48KB+256B Flash Memory,2KB RAM

? MSP430F449:

60KB+256B Flash Memory,2KB RAM

D

For Complete Module Descriptions, See The MSP430x4xx Family User’s Guide ,Literature Number SLAU056

?

’F435, ’F436, and ’F437 devices

? ’F447, ’F448, and ’F449 devices

§ The MSP430F43x1 devices are identical to the MSP430F43x

devices with the exception that the ADC12 module is not implemented.

description

The T exas Instruments MSP430 family of ultralow power microcontrollers consists of several devices featuring different sets of peripherals targeted for various applications. The architecture, combined with five low-power modes, is optimized to achieve extended battery life in portable measurement applications. The device features a powerful 16-bit RISC CPU, 16-bit registers, and constant generators that contribute to maximum code efficiency. The digitally controlled oscillator (DCO) allows wake-up from low-power modes to active mode in less than 6 μs.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications. These devices have limited built-in ESD protection.

PRODUCTION DATA nformat on s current as of publ cat on date.Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright ? 2002?2007, Texas Instruments Incorporated

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

description (continued)

The MSP430x43x(1) and the MSP430x44x series are microcontroller configurations with two built-in 16-bit timers, a fast 12-bit A/D converter (not implemented on the MSP430F43x1 devices), one or two universal serial synchronous/asynchronous communication interfaces (USART), 48 I/O pins, and a liquid crystal driver (LCD) with up to 160 segments.

Typical applications include sensor systems that capture analog signals, convert them to digital values, and process and transmit the data to a host system, or process this data and display it on a LCD panel. The timers make the configurations ideal for industrial control applications such as ripple counters, digital motor control, EE-meters, hand-held meters, etc. The hardware multiplier enhances the performance and offers a broad code and hardware-compatible family solution.

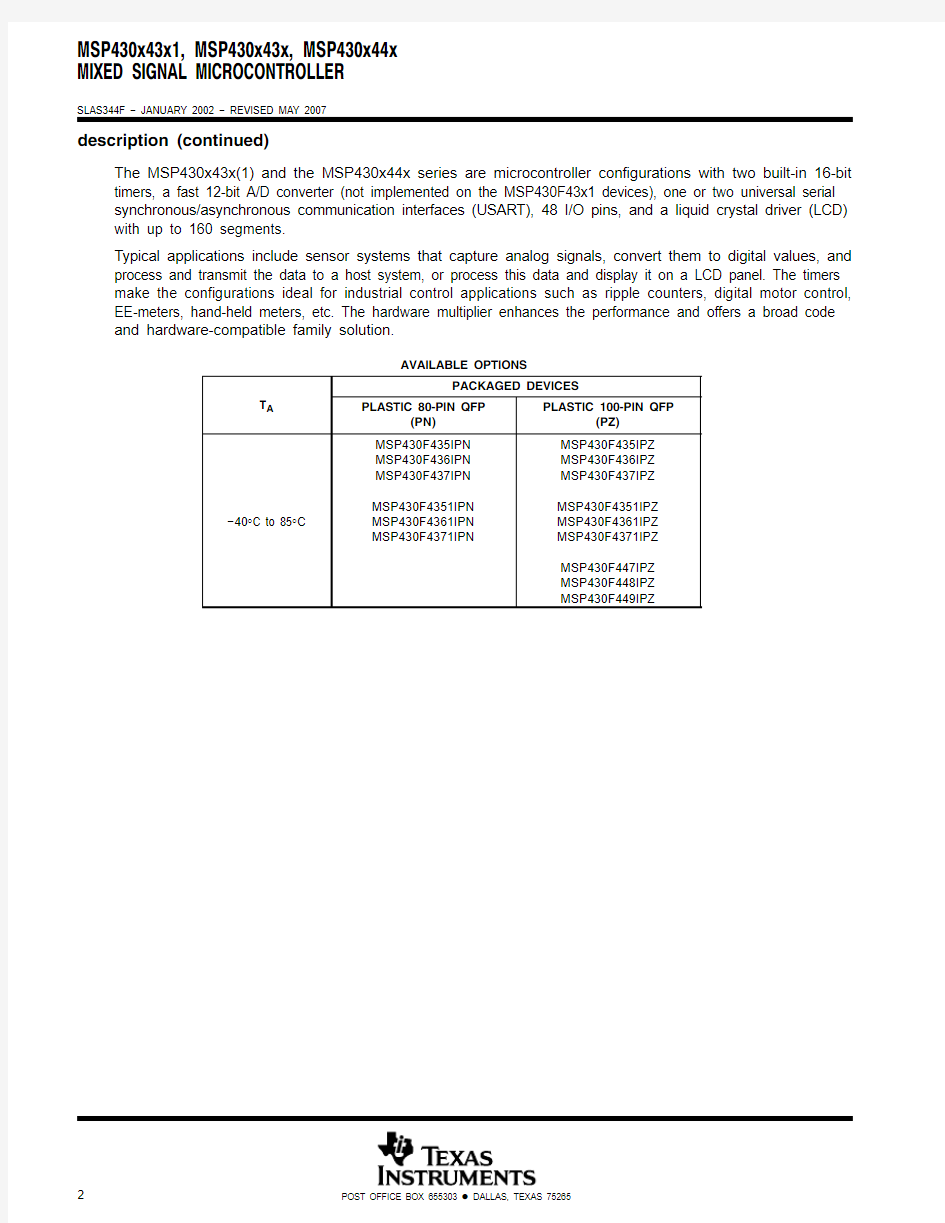

AVAILABLE OPTIONS

PACKAGED DEVICES

T A PLASTIC 80-PIN QFP

(PN)PLASTIC 100-PIN QFP

(PZ)

?40°C to 85°C

MSP430F435IPN

MSP430F436IPN

MSP430F437IPN

MSP430F4351IPN

MSP430F4361IPN

MSP430F4371IPN

MSP430F435IPZ

MSP430F436IPZ

MSP430F437IPZ

MSP430F4351IPZ

MSP430F4361IPZ

MSP430F4371IPZ

MSP430F447IPZ

MSP430F448IPZ

MSP430F449IPZ

pin designation, MSP430x4351IPN, MSP430x4361IPN, MSP430x4371IPN

P1.7/CA1P2.0/TA2P2.1/TB0P2.2/TB1P2.3/TB2P2.4/UTXD0P2.5/URXD0DV SS2DV CC2P5.7/R33P5.6/R23P5.5/R13R03

P5.4/COM3P5.3/COM2P5.2/COM1COM0

P3.0/STE0/S31P3.1/SIMO0/S30P3.2/SOMI0/S29

DV CC1P6.3P6.4P6.5P6.6

P6.7/SVSIN Reserved

XIN XOUT DV SS DV SS P5.1/S0P5.0/S1P4.7/S2P4.6/S3P4.5/S4P4.4/S5P4.3/S6P4.2/S7P4.1/S8

PN PACKAGE (TOP VIEW)

T D O /T D I P 6.1P 6.0R S T /N M I T C K T M S P 2.6/C A O U T /S 19S 21S 15S 16S 17P 4.0/S 9X T 2O U T S 22S 23P 3.7/S 24P 3.6/S 25P 1.0/T A 0P 1.1/T A 0/M C L K P 1.2/T A 1P 1.3/T B O U T H /S V S O U T

P 3.5/S 26P 3.4/S 27P 1.4/T B C L K /S M C L K P 1.5/T A C L K /A C L K T D I /T C L K X T 2I N P 1.6/C A 0

S 10S 20P 3.3/U C L K 0/S 28

S 11S 12S 13S 14P 2.7/S 18P 6.2S S 1D V C C A V S S

A V

pin designation, MSP430x4351IPZ, MSP430x4361IPZ, MSP430x4371IPZ

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25

7

6

7

7

7

8

7

9

8

8

1

8

2

8

3

8

4

8

5

8

6

8

7

8

8

8

9

9

9

1

9

2

9

3

9

4

9

5

9

6

9

7

9

8

9

9

1

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

5

4

9

4

8

4

7

4

6

4

5

4

4

4

3

4

2

4

1

4

3

9

3

8

3

7

3

6

3

5

3

4

3

3

3

2

3

1

3

2

9

2

8

2

7

2

6

P

1

.

7

/

C

A

1

P

6

.

1

P

6

.

R

S

T

/

N

M

I

X

T

2

I

N

X

T

2

O

U

T

P

1

.

3

/

T

B

O

U

T

H

/

S

V

S

O

U

T

P

1

.

4

/

T

B

C

L

K

/

S

M

C

L

K

P

1

.

5

/

T

A

C

L

K

/

A

C

L

K

P

1

.

6

/

C

A

P

2

.

3

/

T

B

2

S

1

4

S

1

5

S

1

6

S

1

7

S

1

8

S

2

S

2

5

S

2

6

S

2

7

S

2

8

S

2

9

S

3

1

P

4

.

7

/

S

3

4

S

3

PZ PACKAGE

(TOP VIEW)

P

1

.

/

T

A

T

D

I

/

T

C

L

K

T

D

O

/

T

D

I

S

2

1

S

S

1

D

V

P

6

.

2

P

1

.

2

/

T

A

1

S

2

4

P

4

.

6

/

S

3

5

DV CC1

P6.3

P6.4

P6.5

P6.6 P6.7/SVSIN Reserved

XIN

XOUT

DV SS

DV SS

P5.1/S0

P5.0/S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

S11

S12

S13

P2.4/UTXD0

P2.5/URXD0

P2.6/CAOUT

P2.7

P3.0/STE0

P3.1/SIMO0

P3.2/SOMI0

P3.3/UCLK0

P3.4

P3.5

P3.6

P3.7

P4.0

P4.1

DV SS2

DV CC2

P5.7/R33

P5.6/R23

P5.5/R13

R03

P5.4/COM3

P5.3/COM2

P5.2/COM1

COM0

P4.2/S39 S

1

9

S

2

2

S

2

3

S

3

3

S

3

2

P

4

.

5

/

S

3

6

P

4

.

4

/

S

3

7

P

4

.

3

/

S

3

8

C

C

A

V

S

S

A

V

T

C

K

T

M

S

P

1

.

1

/

T

A

/

M

C

L

K

P

2

.

/

T

A

2

P

2

.

1

/

T

B

P

2

.

2

/

T

B

1

MSP430F4351IPZ

MSP430F4361IPZ

MSP430F4371IPZ

pin designation, MSP430x435IPN, MSP430x436IPN, MSP430x437IPN

P1.7/CA1P2.0/TA2P2.1/TB0P2.2/TB1P2.3/TB2P2.4/UTXD0P2.5/URXD0DV SS2DV CC2P5.7/R33P5.6/R23P5.5/R13R03

P5.4/COM3P5.3/COM2P5.2/COM1COM0

P3.0/STE0/S31P3.1/SIMO0/S30P3.2/SOMI0/S29

DV CC1P6.3/A3P6.4/A4P6.5/A5P6.6/A6

P6.7/A7/SVSIN

VREF+

XIN XOUT VeREF+

VREF?/VeREF?

P5.1/S0P5.0/S1P4.7/S2P4.6/S3P4.5/S4P4.4/S5P4.3/S6P4.2/S7P4.1/S8

PN PACKAGE (TOP VIEW)

T D O /T D I P 6.1/A 1P 6.0/A 0R S T /N M I T C K T M S P 2.6/C A O U T /S 19S 21S 15S 16S 17P 4.0/S 9X T 2O U T S 22S 23P 3.7/S 24P 3.6/S 25P 1.0/T A 0P 1.1/T A 0/M C L K P 1.2/T A 1P 1.3/T B O U T H /S V S O U T

P 3.5/S 26P 3.4/S 27P 1.4/T B C L K /S M C L K P 1.5/T A C L K /A C L K T D I /T C L K X T 2I N P 1.6/C A 0

S 10S 20P 3.3/U C L K 0/S 28

S 11S 12S 13S 14P 2.7/A D C 12C L K /S 18P 6.2/A 2S S 1D V C C A V S S

A V

pin designation, MSP430x435IPZ, MSP430x436IPZ, MSP430x437IPZ

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25

7

6

7

7

7

8

7

9

8

8

1

8

2

8

3

8

4

8

5

8

6

8

7

8

8

8

9

9

9

1

9

2

9

3

9

4

9

5

9

6

9

7

9

8

9

9

1

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

5

4

9

4

8

4

7

4

6

4

5

4

4

4

3

4

2

4

1

4

3

9

3

8

3

7

3

6

3

5

3

4

3

3

3

2

3

1

3

2

9

2

8

2

7

2

6

P

1

.

7

/

C

A

1

P

6

.

1

/

A

1

P

6

.

/

A

R

S

T

/

N

M

I

X

T

2

I

N

X

T

2

O

U

T

P

1

.

3

/

T

B

O

U

T

H

/

S

V

S

O

U

T

P

1

.

4

/

T

B

C

L

K

/

S

M

C

L

K

P

1

.

5

/

T

A

C

L

K

/

A

C

L

K

P

1

.

6

/

C

A

P

2

.

3

/

T

B

2

S

1

4

S

1

5

S

1

6

S

1

7

S

1

8

S

2

S

2

5

S

2

6

S

2

7

S

2

8

S

2

9

S

3

1

P

4

.

7

/

S

3

4

S

3

PZ PACKAGE

(TOP VIEW)

P

1

.

/

T

A

T

D

I

/

T

C

L

K

T

D

O

/

T

D

I

S

2

1

S

S

1

D

V

P

6

.

2

/

A

2

P

1

.

2

/

T

A

1

S

2

4

P

4

.

6

/

S

3

5

DV CC1

P6.3/A3

P6.4/A4

P6.5/A5

P6.6/A6 P6.7/A7/SVSIN

VREF+

XIN

XOUT

VeREF+ VREF?/VeREF?

P5.1/S0

P5.0/S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

S11

S12

S13

P2.4/UTXD0

P2.5/URXD0

P2.6/CAOUT

P2.7/ADC12CLK

P3.0/STE0

P3.1/SIMO0

P3.2/SOMI0

P3.3/UCLK0

P3.4

P3.5

P3.6

P3.7

P4.0

P4.1

DV SS2

DV CC2

P5.7/R33

P5.6/R23

P5.5/R13

R03

P5.4/COM3

P5.3/COM2

P5.2/COM1

COM0

P4.2/S39 S

1

9

S

2

2

S

2

3

S

3

3

S

3

2

P

4

.

5

/

S

3

6

P

4

.

4

/

S

3

7

P

4

.

3

/

S

3

8

C

C

A

V

S

S

A

V

T

C

K

T

M

S

P

1

.

1

/

T

A

/

M

C

L

K

P

2

.

/

T

A

2

P

2

.

1

/

T

B

P

2

.

2

/

T

B

1

MSP430F435IPZ

MSP430F436IPZ

MSP430F437IPZ

pin designation, MSP430x447IPZ, MSP430x448IPZ, MSP430x449IPZ

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25

7

6

7

7

7

8

7

9

8

8

1

8

2

8

3

8

4

8

5

8

6

8

7

8

8

8

9

9

9

1

9

2

9

3

9

4

9

5

9

6

9

7

9

8

9

9

1

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

5

4

9

4

8

4

7

4

6

4

5

4

4

4

3

4

2

4

1

4

3

9

3

8

3

7

3

6

3

5

3

4

3

3

3

2

3

1

3

2

9

2

8

2

7

2

6

P

1

.

7

/

C

A

1

P

6

.

1

/

A

1

P

6

.

/

A

R

S

T

/

N

M

I

X

T

2

I

N

X

T

2

O

U

T

P

1

.

3

/

T

B

O

U

T

H

/

S

V

S

O

U

T

P

1

.

4

/

T

B

C

L

K

/

S

M

C

L

K

P

1

.

5

/

T

A

C

L

K

/

A

C

L

K

P

1

.

6

/

C

A

P

2

.

3

/

T

B

2

S

1

4

S

1

5

S

1

6

S

1

7

S

1

8

S

2

S

2

5

S

2

6

S

2

7

S

2

8

S

2

9

S

3

1

P

4

.

7

/

S

3

4

S

3

PZ PACKAGE

(TOP VIEW)

P

1

.

/

T

A

T

D

I

/

T

C

L

K

T

D

O

/

T

D

I

S

2

1

S

S

1

D

V

P

6

.

2

/

A

2

P

1

.

2

/

T

A

1

S

2

4

P

4

.

6

/

S

3

5

DV CC1

P6.3/A3

P6.4/A4

P6.5/A5

P6.6/A6 P6.7/A7/SVSIN

VREF+

XIN

XOUT

VeREF+ VREF?/VeREF?

P5.1/S0

P5.0/S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

S11

S12

S13

P2.4/UTXD0

P2.5/URXD0

P2.6/CAOUT

P2.7/ADC12CLK

P3.0/STE0

P3.1/SIMO0

P3.2/SOMI0

P3.3/UCLK0

P3.4/TB3

P3.5/TB4

P3.6/TB5

P3.7/TB6

P4.0/UTXD1

P4.1/URXD1

DV SS2

DV CC2

P5.7/R33

P5.6/R23

P5.5/R13

R03

P5.4/COM3

P5.3/COM2

P5.2/COM1

COM0

P4.2/STE1/S39 S

1

9

S

2

2

S

2

3

S

3

3

S

3

2

P

4

.

5

/

U

C

L

K

1

/

S

3

6

P

4

.

4

/

S

O

M

I

1

/

S

3

7

4

.

3

/

S

I

M

O

1

/

S

3

8

C

C

A

V

S

S

A

V

T

C

K

T

M

S

P

1

.

1

/

T

A

/

M

C

L

K

P

2

.

/

T

A

2

P

2

.

1

/

T

B

P

2

.

2

/

T

B

1

MSP430F447IPZ

MSP430F448IPZ

MSP430F449IPZ

MSP430x43x1 functional block diagram

DV DV AV AV XT2IN XT2OUT

MSP430x43x functional block diagram

DV DV AV AV XT2IN XT2OUT

MSP430x44x functional block diagram

DV DV AV AV

MSP430x43x1 Terminal Functions

TERMINAL

PN PZ I/O

NAME NO.I/O

NAME NO.DESCRIPTION

DV CC11DV CC11Digital supply voltage, positive terminal.P6.32I/O P6.32I/O General-purpose digital I/O P6.43I/O P6.43I/O General-purpose digital I/O P6.54I/O P6.54I/O General-purpose digital I/O P6.65I/O P6.65I/O General-purpose digital I/O

P6.7/SVSIN 6I/O P6.7/SVSIN 6I/O General-purpose digital I/O / input to brownout, supply voltage supervisor

Reserved 7Reserved 7Reserved, do not connect externally

XIN 8I XIN 8I Input port for crystal oscillator XT1. Standard or watch crystals can be connected.

XOUT 9O XOUT 9O Output terminal of crystal oscillator XT1DV SS 10I DV SS 10I Connect to DV SS DV SS 11I DV SS 11I Connect to DV SS

P5.1/S012I/O P5.1/S012I/O General-purpose digital I/O / LCD segment output 0P5.0/S113I/O P5.0/S113I/O General-purpose digital I/O / LCD segment output 1P4.7/S214I/O S214O General-purpose digital I/O / LCD segment output 2P4.6/S315I/O S315O General-purpose digital I/O / LCD segment output 3P4.5/S416I/O S416O General-purpose digital I/O / LCD segment output 4P4.4/S517I/O S517O General-purpose digital I/O / LCD segment output 5P4.3/S618I/O S618O General-purpose digital I/O / LCD segment output 6P4.2/S719I/O S719O General-purpose digital I/O / LCD segment output 7P4.1/S820I/O S820O General-purpose digital I/O / LCD segment output 8P4.0/S921I/O S921O General-purpose digital I/O / LCD segment output 9S1022O S1022O LCD segment output 10S1123O S1123O LCD segment output 11S1224O S1224O LCD segment output 12S1325O S1325O LCD segment output 13S1426O S1426O LCD segment output 14S1527O S1527O LCD segment output 15S1628O S1628O LCD segment output 16S1729O S1729O LCD segment output 17

P2.7/S1830I/O S1830O General-purpose digital I/O / LCD segment output 18

P2.6/CAOUT/S1931I/O S1931O General-purpose digital I/O / Comparator_A output / LCD segment output 19

S2032O S2032O LCD segment output 20S2133O S2133O LCD segment output 21S2234O S2234O LCD segment output 22S2335O S2335O LCD segment output 23

P3.7/S2436I/O S2436O General-purpose digital I/O / LCD segment output 24P3.6/S2537I/O S2537O General-purpose digital I/O / LCD segment output 25P3.5/S2638I/O S2638O General-purpose digital I/O / LCD segment output 26P3.4/S27

39

I/O S27

39

O General-purpose digital I/O / LCD segment output 27

MSP430x43x1 Terminal Functions (Continued)

TERMINAL

PN PZ NAME NO.I/O NAME

NO.I/O DESCRIPTION

P3.3/UCLK0/S2840I/O S2840O General-purpose digital I/O / ext. clock i/p—USART0/UART or SPI mode, clock o/p—USART0/SPI mode / LCD segment output 28P3.2/SOMI0/S2941I/O S2941O General-purpose digital I/O / slave out/master in of USART0/SPI mode / LCD segment output 29

P3.1/SIMO0/S3042I/O S3042O General-purpose digital I/O / slave out/master out of USART0/SPI mode / LCD segment output 30

P3.0/STE0/S31

43

I/O

S3143O General-purpose digital I/O / slave transmit enable-USART0/SPI mode / LCD segment output 31S3244O LCD segment output 32S3345O LCD segment output 33

P4.7/S3446I/O General-purpose digital I/O / LCD segment output 34P4.6/S3547I/O General-purpose digital I/O / LCD segment output 35P4.5/S3648I/O General-purpose digital I/O / LCD segment output 36P4.4/S3749I/O General-purpose digital I/O / LCD segment output 37P4.3/S3850I/O General-purpose digital I/O / LCD segment output 38P4.2/S39

51I/O General-purpose digital I/O / LCD segment output 39COM044O COM052O COM0?3 are used for LCD backplanes.

P5.2/COM145I/O P5.2/COM153I/O General-purpose digital I/O / common output, COM0?3 are used for LCD backplanes.

P5.3/COM246I/O P5.3/COM254I/O General-purpose digital I/O / common output, COM0?3 are used for LCD backplanes.

P5.4/COM347I/O P5.4/COM355I/O General-purpose digital I/O / common output, COM0?3 are used for LCD backplanes.

R0348I R0356I Input port of fourth positive (lowest) analog LCD level (V5)

P5.5/R1349I/O P5.5/R1357I/O General-purpose digital I/O / input port of third most positive analog LCD level (V4 or V3)

P5.6/R2350I/O P5.6/R2358I/O General-purpose digital I/O / input port of second most positive analog LCD level (V2)

P5.7/R3351I/O

P5.7/R3359I/O

General-purpose digital I/O / output port of most positive analog LCD level (V1)

DV CC252DV CC260Digital supply voltage, positive terminal.DV SS2

53

DV SS261Digital supply voltage, negative terminal.P4.162I/O General-purpose digital I/O P4.063I/O General-purpose digital I/O P3.764I/O General-purpose digital I/O P3.665I/O General-purpose digital I/O P3.566I/O General-purpose digital I/O P3.467I/O General-purpose digital I/O

P3.3/UCLK068I/O General-purpose digital I/O / external clock input—USART0/UART or SPI mode, clock output—USART0/SPI mode

P3.2/SOMI069I/O General-purpose digital I/O / slave out/master in of USART0/SPI mode P3.1/SIMO070I/O General-purpose digital I/O / slave in/master out of USART0/SPI mode P3.0/STE071I/O General-purpose digital I/O / slave transmit enable USART0/SPI mode P2.772I/O General-purpose digital I/O

P2.6/CAOUT

73I/O General-purpose digital I/O / Comparator_A output

P2.5/URXD0

54

I/O

P2.5/URXD0

74

I/O General-purpose digital I/O / receive data in—USART0/UART mode

MSP430x43x1 Terminal Functions (Continued)

TERMINAL

PN PZ NAME NO.I/O NAME NO.I/O DESCRIPTION

P2.4/UTXD055I/O P2.4/UTXD075I/O General-purpose digital I/O / transmit data out—USART0/UART mode P2.3/TB256I/O P2.3/TB276I/O General-purpose digital I/O / Timer_B3 CCR2.

Capture: CCI2A/CCI2B input, compare: Out2 output P2.2/TB157I/O P2.2/TB177I/O General-purpose digital I/O / Timer_B3 CCR1.

Capture: CCI1A/CCI1B input, compare: Out1 output P2.1/TB058I/O P2.1/TB078I/O General-purpose digital I/O / Timer_B3 CCR0.

Capture: CCI0A/CCI0B input, compare: Out0 output P2.0/TA259I/O P2.0/TA279I/O General-purpose digital I/O / Timer_A

Capture: CCI2A input, compare: Out2 output P1.7/CA160I/O P1.7/CA180I/O General-purpose digital I/O / Comparator_A input P1.6/CA061I/O P1.6/CA081I/O General-purpose digital I/O / Comparator_A input

P1.5/TACLK/ACLK 62I/O P1.5/TACLK/ACLK 82I/O General-purpose digital I/O / Timer_A, clock signal TACLK input / ACLK output (divided by 1, 2, 4, or 8)

P1.4/TBCLK/SMCLK 63I/O P1.4/TBCLK/SMCLK 83I/O General-purpose digital I/O / input clock TBCLK—Timer_B3 / submain system clock SMCLK output

P1.3/TBOUTH/SVSOUT 64I/O P1.3/TBOUTH/SVSOUT 84I/O General-purpose digital I/O / switch all PWM digital output ports to high impedance—Timer_B3 TB0 to TB2 / SVS: output of SVS comparator P1.2/TA165I/O P1.2/TA185I/O General-purpose digital I/O / Timer_A, Capture: CCI1A input,compare: Out1 output

P1.1/TA0/MCLK 66I/O P1.1/TA0/MCLK 86I/O General-purpose digital I/O / Timer_A. Capture: CCI0B input / MCLK output. Note: TA0 is only an input on this pin / BSL receive

P1.0/TA067I/O P1.0/TA087I/O General-purpose digital I/O / Timer_A. Capture: CCI0A input,compare: Out0 output / BSL transmit XT2OUT 68O XT2OUT 88O Output terminal of crystal oscillator XT2

XT2IN 69I XT2IN 89I Input port for crystal oscillator XT2. Only standard crystals can be connected.

TDO/TDI 70I/O TDO/TDI 90I/O Test data output port. TDO/TDI data output or programming data input terminal

TDI/TCLK 71I TDI/TCLK 91I Test data input or test clock input. The device protection fuse is connected to TDI/TCLK.

TMS 72I TMS 92I Test mode select. TMS is used as an input port for device programming and test.

TCK 73I TCK 93I Test clock. TCK is the clock input port for device programming and test.RST/NMI 74I RST/NMI 94I General-purpose digital I/O / reset input or nonmaskable interrupt input port

P6.075I/O P6.095I/O General-purpose digital I/O P6.176I/O P6.196I/O General-purpose digital I/O P6.277I/O

P6.297I/O

General-purpose digital I/O

AV SS 78AV SS 98Analog supply voltage, negative terminal. Supplies SVS, brownout,oscillator, comparator_A, port 1, and LCD resistive divider circuitry.DV SS179DV SS199Digital supply voltage, negative terminal.

AV CC

80

AV CC

100

Analog supply voltage, positive terminal. Supplies SVS, brownout,oscillator, comparator_A, port 1, and LCD resistive divider circuitry;must not power up prior to DV CC1/DV CC2.

MSP430x43x Terminal Functions

TERMINAL

PN PZ I/O

NAME NO.I/O

NAME NO.DESCRIPTION

DV CC11DV CC11Digital supply voltage, positive terminal.

P6.3/A32I/O P6.3/A32I/O General-purpose digital I/O / analog input a3—12-bit ADC P6.4/A43I/O P6.4/A43I/O General-purpose digital I/O / analog input a4—12-bit ADC P6.5/A54I/O P6.5/A54I/O General-purpose digital I/O / analog input a5—12-bit ADC P6.6/A65I/O P6.6/A65I/O General-purpose digital I/O / analog input a6—12-bit ADC

P6.7/A7/SVSIN 6I/O P6.7/A7/SVSIN 6I/O General-purpose digital I/O / analog input a7—12-bit ADC, analog /input to brownout, supply voltage supervisor

V REF+7O V REF+7O Output of positive terminal of the reference voltage in the ADC XIN 8I XIN 8I Input port for crystal oscillator XT1. Standard or watch crystals can be connected.

XOUT 9O XOUT 9O Output terminal of crystal oscillator XT1

Ve REF+10I Ve REF+10I Input for an external reference voltage to the ADC

V REF?/Ve REF?11I V REF?/Ve REF?11I Negative terminal for the ADC’s reference voltage for both sources, the internal reference voltage, or an external applied reference voltage.P5.1/S012I/O P5.1/S012I/O General-purpose digital I/O / LCD segment output 0P5.0/S113I/O P5.0/S113I/O General-purpose digital I/O / LCD segment output 1P4.7/S214I/O S214O General-purpose digital I/O / LCD segment output 2P4.6/S315I/O S315O General-purpose digital I/O / LCD segment output 3P4.5/S416I/O S416O General-purpose digital I/O / LCD segment output 4P4.4/S517I/O S517O General-purpose digital I/O / LCD segment output 5P4.3/S618I/O S618O General-purpose digital I/O / LCD segment output 6P4.2/S719I/O S719O General-purpose digital I/O / LCD segment output 7P4.1/S820I/O S820O General-purpose digital I/O / LCD segment output 8P4.0/S921I/O S921O General-purpose digital I/O / LCD segment output 9S1022O S1022O LCD segment output 10S1123O S1123O LCD segment output 11S1224O S1224O LCD segment output 12S1325O S1325O LCD segment output 13S1426O S1426O LCD segment output 14S1527O S1527O LCD segment output 15S1628O S1628O LCD segment output 16S17

29O S1729O LCD segment output 17

P2.7/ADC12CLK/S18

30

I/O S18

30

O General-purpose digital I/O / conversion clock—12-bit ADC / LCD segment output 18

P2.6/CAOUT/S1931I/O S1931O General-purpose digital I/O / Comparator_A output / LCD segment output 19

S2032O S2032O LCD segment output 20S2133O S2133O LCD segment output 21S2234O S2234O LCD segment output 22S2335O S2335O LCD segment output 23

P3.7/S2436I/O S2436O General-purpose digital I/O / LCD segment output 24P3.6/S2537I/O S2537O General-purpose digital I/O / LCD segment output 25P3.5/S2638I/O S2638O General-purpose digital I/O / LCD segment output 26P3.4/S27

39

I/O

S27

39

O

General-purpose digital I/O / LCD segment output 27

MSP430x43x Terminal Functions (Continued)

TERMINAL

PN PZ NAME NO.I/O NAME

NO.I/O DESCRIPTION

P3.3/UCLK0/S2840I/O S2840O General-purpose digital I/O / ext. clock i/p—USART0/UART or SPI mode, clock o/p—USART0/SPI mode / LCD segment output 28P3.2/SOMI0/S2941I/O S2941O General-purpose digital I/O / slave out/master in of USART0/SPI mode / LCD segment output 29

P3.1/SIMO0/S3042I/O S3042O General-purpose digital I/O / slave out/master out of USART0/SPI mode / LCD segment output 30

P3.0/STE0/S31

43

I/O

S3143O General-purpose digital I/O / slave transmit enable-USART0/SPI mode / LCD segment output 31S3244O LCD segment output 32S3345O LCD segment output 33

P4.7/S3446I/O General-purpose digital I/O / LCD segment output 34P4.6/S3547I/O General-purpose digital I/O / LCD segment output 35P4.5/S3648I/O General-purpose digital I/O / LCD segment output 36P4.4/S3749I/O General-purpose digital I/O / LCD segment output 37P4.3/S3850I/O General-purpose digital I/O / LCD segment output 38P4.2/S39

51I/O General-purpose digital I/O / LCD segment output 39COM044O COM052O COM0?3 are used for LCD backplanes.

P5.2/COM145I/O P5.2/COM153I/O General-purpose digital I/O / common output, COM0?3 are used for LCD backplanes.

P5.3/COM246I/O P5.3/COM254I/O General-purpose digital I/O / common output, COM0?3 are used for LCD backplanes.

P5.4/COM347I/O P5.4/COM355I/O General-purpose digital I/O / common output, COM0?3 are used for LCD backplanes.

R0348I R0356I Input port of fourth positive (lowest) analog LCD level (V5)

P5.5/R1349I/O P5.5/R1357I/O General-purpose digital I/O / input port of third most positive analog LCD level (V4 or V3)

P5.6/R2350I/O P5.6/R2358I/O General-purpose digital I/O / input port of second most positive analog LCD level (V2)

P5.7/R3351I/O

P5.7/R3359I/O

General-purpose digital I/O / output port of most positive analog LCD level (V1)

DV CC252DV CC260Digital supply voltage, positive terminal.DV SS2

53

DV SS261Digital supply voltage, negative terminal.P4.162I/O General-purpose digital I/O P4.063I/O General-purpose digital I/O P3.764I/O General-purpose digital I/O P3.665I/O General-purpose digital I/O P3.566I/O General-purpose digital I/O P3.467I/O General-purpose digital I/O

P3.3/UCLK068I/O General-purpose digital I/O / external clock input—USART0/UART or SPI mode, clock output—USART0/SPI mode

P3.2/SOMI069I/O General-purpose digital I/O / slave out/master in of USART0/SPI mode P3.1/SIMO070I/O General-purpose digital I/O / slave in/master out of USART0/SPI mode P3.0/STE071I/O General-purpose digital I/O / slave transmit enable USART0/SPI mode P2.7/ADC12CLK 72I/O General-purpose digital I/O / conversion clock—12-bit ADC P2.6/CAOUT

73I/O General-purpose digital I/O / Comparator_A output

P2.5/URXD0

54

I/O

P2.5/URXD0

74

I/O General-purpose digital I/O / receive data in—USART0/UART mode

MSP430x43x Terminal Functions (Continued)

TERMINAL

PN PZ NAME NO.I/O NAME NO.I/O DESCRIPTION

P2.4/UTXD055I/O P2.4/UTXD075I/O General-purpose digital I/O / transmit data out—USART0/UART mode P2.3/TB256I/O P2.3/TB276I/O General-purpose digital I/O / Timer_B3 CCR2.

Capture: CCI2A/CCI2B input, compare: Out2 output P2.2/TB157I/O P2.2/TB177I/O General-purpose digital I/O / Timer_B3 CCR1.

Capture: CCI1A/CCI1B input, compare: Out1 output P2.1/TB058I/O P2.1/TB078I/O General-purpose digital I/O / Timer_B3 CCR0.

Capture: CCI0A/CCI0B input, compare: Out0 output P2.0/TA259I/O P2.0/TA279I/O General-purpose digital I/O / Timer_A

Capture: CCI2A input, compare: Out2 output P1.7/CA160I/O P1.7/CA180I/O General-purpose digital I/O / Comparator_A input P1.6/CA061I/O P1.6/CA081I/O General-purpose digital I/O / Comparator_A input

P1.5/TACLK/ACLK 62I/O P1.5/TACLK/ACLK 82I/O General-purpose digital I/O / Timer_A, clock signal TACLK input / ACLK output (divided by 1, 2, 4, or 8)

P1.4/TBCLK/SMCLK 63I/O P1.4/TBCLK/SMCLK 83I/O General-purpose digital I/O / input clock TBCLK—Timer_B3 / submain system clock SMCLK output

P1.3/TBOUTH/SVSOUT 64I/O P1.3/TBOUTH/SVSOUT 84I/O General-purpose digital I/O / switch all PWM digital output ports to high impedance—Timer_B3 TB0 to TB2 / SVS: output of SVS comparator P1.2/TA165I/O P1.2/TA185I/O General-purpose digital I/O / Timer_A, Capture: CCI1A input,compare: Out1 output

P1.1/TA0/MCLK 66I/O P1.1/TA0/MCLK 86I/O General-purpose digital I/O / Timer_A. Capture: CCI0B input / MCLK output. Note: TA0 is only an input on this pin / BSL receive

P1.0/TA067I/O P1.0/TA087I/O General-purpose digital I/O / Timer_A. Capture: CCI0A input,compare: Out0 output / BSL transmit XT2OUT 68O XT2OUT 88O Output terminal of crystal oscillator XT2

XT2IN 69I XT2IN 89I Input port for crystal oscillator XT2. Only standard crystals can be connected.

TDO/TDI 70I/O TDO/TDI 90I/O Test data output port. TDO/TDI data output or programming data input terminal

TDI/TCLK 71I TDI/TCLK 91I Test data input or test clock input. The device protection fuse is connected to TDI/TCLK.

TMS 72I TMS 92I Test mode select. TMS is used as an input port for device programming and test.

TCK 73I TCK 93I Test clock. TCK is the clock input port for device programming and test.RST/NMI 74I RST/NMI 94I General-purpose digital I/O / reset input or nonmaskable interrupt input port

P6.0/A075I/O P6.0/A095I/O General-purpose digital I/O / analog input a0 ? 12-bit ADC P6.1/A176I/O P6.1/A196I/O General-purpose digital I/O / analog input a1 ? 12-bit ADC P6.2/A277I/O

P6.2/A297I/O

General-purpose digital I/O / analog input a2 ? 12-bit ADC

AV SS 78AV SS 98Analog supply voltage, negative terminal. Supplies SVS, brownout,oscillator, comparator_A, ADC12, port 1, and LCD resistive divider circuitry.

DV SS179DV SS199Digital supply voltage, negative terminal.

AV CC

80

AV CC

100

Analog supply voltage, positive terminal. Supplies SVS, brownout,oscillator, comparator_A, ADC12, port 1, and LCD resistive divider circuitry; must not power up prior to DV CC1/DV CC2.

MSP430x44x Terminal Functions

TERMINAL

NAME NO.

I/O DESCRIPTION DV CC11Digital supply voltage, positive terminal.

P6.3/A32I/O General-purpose digital I/O / analog input a3—12-bit ADC P6.4/A43I/O General-purpose digital I/O / analog input a4—12-bit ADC P6.5/A54I/O General-purpose digital I/O / analog input a5—12-bit ADC P6.6/A65I/O General-purpose digital I/O / analog input a6—12-bit ADC

P6.7/A7/SVSIN6I/O General-purpose digital I/O / analog input a7—12-bit ADC / analog input to brownout, supply voltage supervisor

V REF+7O Output of positive terminal of the reference voltage in the ADC

XIN8I Input port for crystal oscillator XT1. Standard or watch crystals can be connected. XOUT9O Output terminal of crystal oscillator XT1

Ve REF+10I Input for an external reference voltage to the ADC

V REF?/Ve REF?11I Negative terminal for the ADC’s reference voltage for both sources, the internal reference voltage, or an external applied reference voltage

P5.1/S012I/O General-purpose digital I/O / LCD segment output 0 P5.0/S113I/O General-purpose digital I/O / LCD segment output 1 S214O LCD segment output 2

S315O LCD segment output 3

S416O LCD segment output 4

S517O LCD segment output 5

S618O LCD segment output 6

S719O LCD segment output 7

S820O LCD segment output 8

S921O LCD segment output 9

S1022O LCD segment output 10

S1123O LCD segment output 11

S1224O LCD segment output 12

S1325O LCD segment output 13

S1426O LCD segment output 14

S1527O LCD segment output 15

S1628O LCD segment output 16

S1729O LCD segment output 17

S1830O LCD segment output 18

S1931O LCD segment output 19

S2032O LCD segment output 20

S2133O LCD segment output 21

S2234O LCD segment output 22

S2335O LCD segment output 23

S2436O LCD segment output 24

S2537O LCD segment output 25

S2638O LCD segment output 26

S2739O LCD segment output 27

S2840O LCD segment output 28

MSP430x44x Terminal Functions (Continued) TERMINAL

PN I/O DESCRIPTION NAME NO.

S2941O LCD segment output 29

S3042O LCD segment output 30

S3143O LCD segment output 31

S3244O LCD segment output 32

S3345O LCD segment output 33

P4.7/S3446I/O General-purpose digital I/O / LCD segment output 34

P4.6/S3547I/O General-purpose digital I/O / LCD segment output 35

P4.5/UCLK1/S3648I/O General-purpose digital I/O / external clock input—USART1/UART or SPI mode, clock output—USART1/SPI MODE / LCD segment output 36

P4.4/SOMI1/S3749I/O General-purpose digital I/O / slave out/master in of USART1/SPI mode / LCD segment output 37

P4.3/SIMO1/S3850I/O General-purpose digital I/O / slave in/master out of USART1/SPI mode / LCD segment output 38

P4.2/STE1/S3951I/O General-purpose digital I/O / slave transmit enable—USART1/SPI mode / LCD segment output 39 COM052O COM0?3 are used for LCD backplanes.

P5.2/COM153I/O General-purpose digital I/O / common output, COM0?3 are used for LCD backplanes.

P5.3/COM254I/O General-purpose digital I/O / common output, COM0?3 are used for LCD backplanes.

P5.4/COM355I/O General-purpose digital I/O / common output, COM0?3 are used for LCD backplanes.

R0356I Input port of fourth positive (lowest) analog LCD level (V5)

P5.5/R1357I/O General-purpose digital I/O / Input port of third most positive analog LCD level (V4 or V3)

P5.6/R2358I/O General-purpose digital I/O / Input port of second most positive analog LCD level (V2)

P5.7/R3359I/O General-purpose digital I/O / Output port of most positive analog LCD level (V1)

DV CC260Digital supply voltage, positive terminal.

DV SS261Digital supply voltage, negative terminal.

P4.1/URXD162I/O General-purpose digital I/O / receive data in—USART1/UART mode

P4.0/UTXD163I/O General-purpose digital I/O / transmit data out—USART1/UART mode

P3.7/TB664I/O General-purpose digital I/O / Timer_B7 CCR6 / Capture: CCI6A/CCI6B input, compare: Out6 output P3.6/TB565I/O General-purpose digital I/O / Timer_B7 CCR5 / Capture: CCI5A/CCI5B input, compare: Out5 output P3.5/TB466I/O General-purpose digital I/O / Timer_B7 CCR4 / Capture: CCI4A/CCI4B input, compare: Out4 output P3.4/TB367I/O General-purpose digital I/O / Timer_B7 CCR3 / Capture: CCI3A/CCI3B input, compare: Out3 output

P3.3/UCLK068I/O General-purpose digital I/O / external clock input—USART0/UART or SPI mode, clock output—USART0/SPI mode

P3.2/SOMI069I/O General-purpose digital I/O / slave out/master in of USART0/SPI mode

P3.1/SIMO070I/O General-purpose digital I/O / slave in/master out of USART0/SPI mode

P3.0/STE071I/O General-purpose digital I/O / slave transmit enable—USART0/SPI mode

P2.7/ADC12CLK72I/O General-purpose digital I/O / conversion clock—12-bit ADC

P2.6/CAOUT73I/O General-purpose digital I/O / Comparator_A output

P2.5/URXD074I/O General-purpose digital I/O / receive data in—USART0/UART mode

P2.4/UTXD075I/O General-purpose digital I/O / transmit data out—USART0/UART mode

P2.3/TB276I/O General-purpose digital I/O / Timer_B7 CCR2. Capture: CCI2A/CCI2B input, compare: Out2 output P2.2/TB177I/O General-purpose digital I/O / Timer_B7 CCR1. Capture: CCI1A/CCI1B input, compare: Out1 output P2.1/TB078I/O General-purpose digital I/O / Timer_B7 CCR0. Capture: CCI0A/CCI0B input, compare: Out0 output P2.0/TA279I/O General-purpose digital I/O / Timer_A Capture: CCI2A input, compare: Out2 output

P1.7/CA180I/O General-purpose digital I/O / Comparator_A input

MSP430x44x Terminal Functions (Continued)

TERMINAL

PN I/O DESCRIPTION

NAME NO.

P1.6/CA081I/O General-purpose digital I/O / Comparator_A input

P1.5/TACLK/

ACLK

82I/O General-purpose digital I/O / Timer_A, clock signal TACLK input / ACLK output (divided by 1, 2, 4, or 8) P1.4/TBCLK/

SMCLK

83I/O General-purpose digital I/O / input clock TBCLK—Timer_B7 / submain system clock SMCLK output

P1.3/TBOUTH/ SVSOUT 84I/O

General-purpose digital I/O / switch all PWM digital output ports to high impedance—Timer_B7 TB0 to TB6

/ SVS: output of SVS comparator

P1.2/TA185I/O General-purpose digital I/O / Timer_A, Capture: CCI1A input, compare: Out1 output

P1.1/TA0/MCLK86I/O General-purpose digital I/O / Timer_A. Capture: CCI0B input / MCLK output. Note: TA0 is only an input on this pin / BSL receive

P1.0/TA087I/O General-purpose digital I/O / Timer_A. Capture: CCI0A input, compare: Out0 output / BSL transmit XT2OUT88O Output terminal of crystal oscillator XT2

XT2IN89I Input port for crystal oscillator XT2. Only standard crystals can be connected.

TDO/TDI90I/O Test data output port. TDO/TDI data output or programming data input terminal

TDI/TCLK91I Test data input or test clock input. The device protection fuse is connected to TDI/TCLK.

TMS92I Test mode select. TMS is used as an input port for device programming and test.

TCK93I Test clock. TCK is the clock input port for device programming and test.

RST/NMI94I Reset input or nonmaskable interrupt input port

P6.0/A095I/O General-purpose digital I/O, analog input a0—12-bit ADC

P6.1/A196I/O General-purpose digital I/O, analog input a1—12-bit ADC

P6.2/A297I/O General-purpose digital I/O, analog input a2—12-bit ADC

AV SS98Analog supply voltage, negative terminal. Supplies SVS, brownout, oscillator, comparator_A, ADC12, port 1, and LCD resistive divider circuitry.

DV SS199Digital supply voltage, negative terminal.

AV CC100Analog supply voltage, positive terminal. Supplies SVS, brownout, oscillator, comparator_A, ADC12, port 1, and LCD resistive divider circuitry; must not power up prior to DV CC1/DV CC2.

General-Purpose Register Program Counter Stack Pointer Status Register Constant Generator General-Purpose Register General-Purpose Register General-Purpose Register PC/R0SP/R1SR/CG1/R2CG2/R3R4R5R12R13General-Purpose Register General-Purpose Register R6R7General-Purpose Register General-Purpose Register R8R9General-Purpose Register General-Purpose Register R10R11General-Purpose Register General-Purpose Register

R14R15

short-form description

CPU

The MSP430 CPU has a 16-bit RISC architecture that is highly transparent to the application. All operations, other than program-flow instructions,are performed as register operations in conjunction with seven addressing modes for source operand and four addressing modes for destination operand.

The CPU is integrated with 16 registers that provide reduced instruction execution time. The register-to-register operation execution time is one cycle of the CPU clock.

Four of the registers, R0 to R3, are dedicated as program counter, stack pointer, status register,and constant generator respectively. The remaining registers are general-purpose registers.

Peripherals are connected to the CPU using data,address, and control buses, and can be handled with all instructions.instruction set

The instruction set consists of 51 instructions with three formats and seven address modes. Each instruction can operate on word and byte data.Table 1 shows examples of the three types of instruction formats; the address modes are listed in Table 2.

Table 1. Instruction Word Formats

Dual operands, source-destination e.g. ADD R4,R5R4 + R5 ???> R5Single operands, destination only e.g. CALL R8PC ??>(TOS), R8??> PC Relative jump, un/conditional

e.g. JNE

Jump-on-equal bit = 0

Table 2. Address Mode Descriptions

ADDRESS MODE

S D

SYNTAX EXAMPLE OPERATION Register D D MOV Rs,Rd MOV R10,R11R10 ??> R11Indexed

D D MOV X(Rn),Y(Rm)MOV 2(R5),6(R6)

M(2+R5)??> M(6+R6)Symbolic (PC relative)

D D MOV EDE,TONI M(EDE) ??> M(TONI)Absolute D D

MOV &MEM,&TCDAT M(MEM) ??> M(TCDAT)Indirect D MOV @Rn,Y(Rm)MOV @R10,Tab(R6)M(R10) ??> M(Tab+R6)

Indirect autoincrement D MOV @Rn+,Rm MOV @R10+,R11M(R10) ??> R11R10 + 2??> R10Immediate

D

MOV #X,TONI

MOV #45,TONI #45 ??> M(TONI)

NOTE:S = source D = destination

operating modes

The MSP430 has one active mode and five software selectable low-power modes of operation. An interrupt event can wake up the device from any of the five low-power modes, service the request and restore back to the low-power mode on return from the interrupt program.

The following six operating modes can be configured by software:

D Active mode (AM)

?All clocks are active

D Low-power mode 0 (LPM0)

?CPU is disabled

ACLK and SMCLK remain active. MCLK is disabled

FLL+ loop control remains active

D Low-power mode 1 (LPM1)

?CPU is disabled

FLL+ loop control is disabled

ACLK and SMCLK remain active. MCLK is disabled

D Low-power mode 2 (LPM2)

?CPU is disabled

MCLK, FLL+ loop control, and DCOCLK are disabled

DCO’s dc-generator remains enabled

ACLK remains active

D Low-power mode 3 (LPM3)

?CPU is disabled

MCLK, FLL+ loop control, and DCOCLK are disabled

DCO’s dc-generator is disabled

ACLK remains active

D Low-power mode 4 (LPM4)

?CPU is disabled

ACLK is disabled

MCLK, FLL+ loop control, and DCOCLK are disabled

DCO’s dc-generator is disabled

Crystal oscillator is stopped

12864液晶屏手册 一、液晶显示模块概述 12864A-1汉字图形点阵液晶显示模块,可显示汉字及图形,内置8192个中文汉字(16X16点阵,16*8=128,16*4=64,一行只能写8个汉字,4行;)、128个字符(8X16点阵)及64X256点阵显示RAM(GDRAM)。 主要技术参数和显示特性: 电源:VDD ~+5V(内置升压电路,无需负压); 显示内容:128列×64行(128表示点数) 显示颜色:黄绿 显示角度:6:00钟直视 LCD类型:STN 与MCU接口:8位或4位并行/3位串行 配置LED背光 多种软件功能:光标显示、画面移位、自定义字符、睡眠模式等 二、外形尺寸 1.外形尺寸图 2.主要外形尺寸 项目标准尺寸单位 模块体积××mm

二、模块引脚说明 逻辑工作电压(VDD):~ 电源地(GND):0V 工作温度(Ta):0~60℃(常温) / -20~75℃(宽温) 三、接口时序 模块有并行和串行两种连接方法(时序如下): 8位并行连接时序图 MPU写资料到模块

MPU从模块读出资料 2、串行连接时序图

串行数据传送共分三个字节完成: 第一字节:串口控制—格式11111ABC A为数据传送方向控制:H表示数据从LCD到MCU,L表示数据从MCU到LCD B为数据类型选择:H表示数据是显示数据,L表示数据是控制指令 C固定为0 第二字节:(并行)8位数据的高4位—格式DDDD0000 第三字节:(并行)8位数据的低4位—格式0000DDDD 串行接口时序参数:(测试条件:T=25℃VDD=

备注: 1、当模块在接受指令前,微处理顺必须先确认模块内部处于非忙碌状态,即读取BF标志时BF需为0,方可接受新的指令;如果在送出一个指令前并不检查BF标志,(一般在输入每天指令前加个delay)那么在前一个指令和这个指令中间必须延迟一段较长的时间,即是等待前一个指令确实执行完成,指令执行的时间请参考指令表中的个别指令说明。 2、“RE”为基本指令集与扩充指令集的选择控制位元,当变更“RE”位元后,往后的指令集将维持在最后的状态,除非再次变更“RE”位元,否则使用相同指令集时,不需每次重设“RE”位元。 具体指令介绍: 1、清除显示

D Wake-Up From Standby Mode in Less Than 6 μs D 16-Bit RISC Architecture, 125-ns Instruction Cycle Time D 12-Bit A/D Converter With Internal Reference, Sample-and-Hold and Autoscan Feature D 16-Bit Timer_B With Three ? or Seven ? Capture/Compare-With-Shadow Registers D 16-Bit Timer_A With Three Capture/Compare Registers D On-Chip Comparator D Serial Communication Interface (USART),Select Asynchronous UART or Synchronous SPI by Software: ? Two USARTs (USART0, USART1) —MSP430x44x Devices ? One USART (USART0) — MSP430x43x(1) Devices D Brownout Detector D Supply Voltage Supervisor/Monitor With Programmable Level Detection D Bootstrap Loader D Family Members Include: ? MSP430F435, MSP430F4351§: 16KB+256B Flash Memory,512B RAM ? MSP430F436, MSP430F4361§: 24KB+256B Flash Memory,1KB RAM ? MSP430F437, MSP430F4371§: 32KB+256B Flash Memory,1KB RAM ? MSP430F447: 32KB+256B Flash Memory,1KB RAM ? MSP430F448: 48KB+256B Flash Memory,2KB RAM ? MSP430F449: 60KB+256B Flash Memory,2KB RAM D For Complete Module Descriptions, See The MSP430x4xx Family User’s Guide ,Literature Number SLAU056 ? ’F435, ’F436, and ’F437 devices ? ’F447, ’F448, and ’F449 devices § The MSP430F43x1 devices are identical to the MSP430F43x devices with the exception that the AD C12 module is not implemented. description The T exas Instruments MSP430 family of ultralow power microcontrollers consists of several devices featuring different sets of peripherals targeted for various applications. The architecture, combined with five low-power modes, is optimized to achieve extended battery life in portable measurement applications. The device features a powerful 16-bit RISC CPU, 16-bit registers, and constant generators that contribute to maximum code efficiency. The digitally controlled oscillator (DCO) allows wake-up from low-power modes to active mode in less than 6 μs. This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications. These devices have limited built-in ESD protection. PRODUCTION DATA nformat on s current as of publ cat on date.Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters. Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

112233445566778 8 D D C C B B A A 12 3 45 6789 1011 1213 1415 1617 1819 2021 2223 2425 26 P1 Header 13X21 234567891011121314151617181920212223242526 P2 Header 13X212345678910111213141516171819202122232425 26 P3 Header 13X212345678910111213141516171819202122232425 26 P4 Header 13X2 DVcc1P631234567891011 1213141516171819202122232425262728293031323334353637383940414243444546474849 50P5Header 25X2123 45678910111213141516171819202122232425262728293031323334353637383940414243444546474849 50P6Header 25X2 1 23 45 678910111213141516171819202122232425262728293031323334353637383940414243444546474849 50P7Header 25X212345678910111213141516171819202122232425262728293031323334353637383940414243444546474849 50P8Header 25X2 11221112221122311224 11225 11226 11227 11228 11229 11220112 2#1122* e 1d 2d p 3 c 4g 54 6 b 73829f 10a 11112seg4 D1D2 D3D4D5D6D7D8VCC 11 2 2 A 11 2 2 B 11 2 2 C 11 2 2 D 12345 678 5110 Header 8 GND VCC Vin 3G N D 1 Vout 2U2 AS117-3.3 12 3 4567891110J1 D Connector 912345678910111213 14JTAG GND T D O T D I T M S T C K R S T 1 23 4 2 Header 3 VCC P64P65P66P67VREF+XIN XOUT VeREF+V_P50P51S2S3S4S5S6S7S8S9S10S11S12 S13S14S15S16S17S18S19S20S21S22S23S24S25S26S27S28S29S30S31S32S33P43 P44 P45P46P47P42COM0 P52P53P54P55P56P57R03DVcc2DVss2P40P41P24P25 P26P27P30P31P32P33P34P35P36P37VCC GND DVss1 P60P61P62RST TCK TMS TDO TDI X2IN X2OUT P10P11P12P13P14P15P16P17P20P21P22P23P64 P66 XOUT V_P50 S3 S5 S7 S9 S11S13 VREF+ P63 P65 P67 XIN VeREF+P51 S2 S4 S6 S8 S10 S12 DVcc1 S14 S15 S16 S17 S18 S19 S20 S21 S22S23S24S25 S26 S27 S28 S29 S30 S31 S32 S33 P43 P44 P45P46 P47 P42P52 P54 P55 P57 DVss2P40 P24 P26 P30P32P34P36 COM0P53 P56 R03 DVcc2 P41 P25 P27 P31P33P35 P37 VCC GND P61RST TMS TDO X2OUT P11 P13 P15 P17 P21 P23DVss1 P60P62 TCK TDI X2IN P10 P12 P14 P16 P20 P22VCC 1 23456 5V Header 6 1 23456 3V Header 6 1 23456 GND Header 6 1 23456 GND Header 6 V D D V C C G N D G N D DS LED0 O E 1 Q 02D 03D 14Q 15Q 26D 27D 38Q 39G N D 10 L E 11 Q 412D 413D 514Q 515Q 616D 617D 718Q 719V C C 2074HC373_174HC373O E 1Q 02D 03D 14Q 15Q 26D 27D 38Q 39G N D 10 L E 11 Q 412D 413D 514Q 515Q 616D 617D 718Q 719V C C 2074HC373_274HC373 V 1D-2D+3G 45 5 USB TXD 1DTR_N 2RTS_N 3VDD_2324RXD 5RL_N 6GND 7VDD 8DSR_N 9DCD_N 10DCD_N 11SHTD_N 12EE_CLK 13EE_DATA 14DP 15DM 16VDD_3V3 17GND_3V318RESET 19VDD 20GND 21TRI_STATE 22LD_MODE 23VDD_PLL 24GND_PLL 25PLL_TEST 26OSC127OSC228U1 R1 200R2 200R3200R4200 R5 10k R6 10k R72k R830R930 TXD DTR RTS RXD VCC C10.1u GND VCC VDD GND C20.1u D+ D+D-D-1 2 Y1 12M C3 22p C422p C5100u C6100u C70.1u C80.1u VDD R101K COMMON1 1NC12NO13 COMMON2 5 NC24 NO26 S1SW DPDT VIN VIN GND VCC RST TMS TDO TCK TDI 1310118129147C1+1 C2+4GND 15 C1-3VCC 16C2- 5V- 6 V+ 2U3MAX3232ESE C9 0.1u C100.1u C110.1u C120.1u C13 0.1u TXD1 RXO0 RXD1 TXO0 GND VCC GND GND RXO0TXO0R11 1K R12 1K R131K R14 1K R151K R16 1K R17 1K R181K R19 100R20 100R21 100R22 100 R29100K C140.1u GND R23 10k R24 10k R25 10k R26 10k R27 10k R28 10k R30 1k P_61 P_62 P_60 VCC VCC GND GND GND GND P_63P_64P_65P_20P_21 P_22P_23P_24P_25P_26 P_27P_63P_64P_65P_60 P_61 P_62 P_10P_11P_12P_13P_14 P_15 P_16 P_17 P_20 P_21 P_22 P_23P_24 P_25 P_26 P_27 P_30 P_31 P_32P_33 P_34P_35P_36P_37TXD1RXD1P_42P_43VCC GND TXD RXD DTR RTS P24 P2511 22res SW-PB GND RST 1 23TXD Header 3 123 RXD Header 31 2 3 RTS Header 3 1 23 DTR Header 3 GND GND P_30 P_31P_32P_33P_34 P_35 P_36 P_37P_10 P_11P_12P_13P_14P_15P_16P_17 P_66P_67P_66P_67RST TCK P10 P11

LED显示屏模组使用材料说明 1、LED灯:LED红灯(晶元),亮度1000-1100mcd,中心波长623-627nm LED绿灯(士蓝),亮度1900-2200mcd,中心波长520-525nm LED蓝灯(士蓝),亮度365-385mcd,中心波长470-475nm 发光二极管简称为LED。主要由支架、晶片、银胶、金线、环氧树脂五种物料所组成。由镓(Ga)与砷(AS)、磷(P)的化合物制成的二极管,当电子与空穴复合时能辐射出可见光,因而可以用来制成发光二极管。在电路及仪器中作为指示灯,或者组成文字或数字显示。发光材料用透明环氧树脂封装。封装树脂包括:A胶(主剂)、B胶(硬化剂)、DP(扩散剂)、CP(着色剂)四部份组成。其主要成分为环氧树脂(Epoxy Resin)、酸酐类(酸无水物Anhydride)、高光扩散性填料(Light diffusion)及热安定性染料(dye) 2、LED驱动IC:HB5024 HB5024是一款用于大屏幕LED的低压差、高精度16位恒流驱动芯片。它是内建的16位移位寄存器与栓锁功能,可以将串行的输入数据转换成并行输出数据格式。HB5024的输入电压范围值为3.3V至5V,提供16个电流源,可以在每个输出级提供3mA - 45 mA恒定电流以驱动LED。并且单颗IC 内输出通道的电流差异小于±2%;多颗IC间的输出电流差异小于±3%;恒定输出电流随着输出端耐受电压(VDS)变化,被控制在每伏特0.1%;且电流受供给电压(VDD)、环境温度的变化也被控制在1%。HB5024可以选用不同阻值的外接电阻来调整其输出级的电流大小,藉此机制,使用者可精确地控制LED的发光亮度。HB5024的设计保证其输出级可耐压17V,因此可以在每个输出端串接多个LED。此外,HB5024亦提供30MHz的高时钟频率以满足系统对大量数据传输上的需求。 3、其他LED配件: ①、电源座(加强型):电源座是承接电源线与PCB板连接的主要器件,

液晶显示模块技术手册 HJ1602A 一、概述 HJ1602A是一种工业字符型液晶,能够同时显示16x02即32个字符。(16列2行)二.模块尺寸(如图) 三.引脚接口说明表 第1脚:VSS为地电源。 第2脚:VDD接5V正电源。 第3脚:VL为液晶显示器对比度调整端,接正电源时对比度最弱,接地时对比度最高,对比度过高时会产生“鬼影”,使用时可以通过一个10K的电位器调整对比度。 第4脚:RS为寄存器选择,高电平时选择数据寄存器、低电平时选择指令寄存器。 第5脚:R/W为读写信号线,高电平时进行读操作,低电平时进行写操作。当RS和R/W共同为低电平时可以写入指令或者显示地址,当RS为低电平R/W为高电平时可以读忙信号,当RS 为高电平R/W为低电平时可以写入数据。 第6脚:E端为使能端,当E端由高电平跳变成低电平时,液晶模块执行命令。

第7~14脚:D0~D7为8位双向数据线。 第15脚:背光源正极。 第16脚:背光源负极。 四.1602LCD的指令说明及时序 14:控制命令表 1602液晶模块的读写操作、屏幕和光标的操作都是通过指令编程来实现的。(说明:1为高电平、0为低电平) 指令1:清显示,指令码01H,光标复位到地址00H位置。 指令2:光标复位,光标返回到地址00H。 指令3:光标和显示模式设置I/D:光标移动方向,高电平右移,低电平左移S:屏幕上所有文字是否左移或者右移。高电平表示有效,低电平则无效。 指令4:显示开关控制。D:控制整体显示的开与关,高电平表示开显示,低电平表示关显示C:控制光标的开与关,高电平表示有光标,低电平表示无光标B:控制光标是否闪烁,高电平闪烁,低电平不闪烁。 指令5:光标或显示移位S/C:高电平时移动显示的文字,低电平时移动光标。 指令6:功能设置命令DL:高电平时为4位总线,低电平时为8位总线N:低电平时为单行显示,高电平时双行显示F: 低电平时显示5x7的点阵字符,高电平时显示5x10的点阵字符。指令7:字符发生器RAM地址设置。 指令8:DDRAM地址设置。 指令9:读忙信号和光标地址BF:为忙标志位,高电平表示忙,此时模块不能接收命令或者数据,如果为低电平表示不忙。 指令10:写数据。 指令11:读数据。

MSP430F449在超低功耗高精度雷达液位仪中的应用 摘要: MSP430系列是TI公司的超低功耗低功耗单片机系列产品。这个系列的MCU具有极低的功耗,丰富的片内外设,强大的处理能力,稳定的工作状态,非常适用于要求低功耗、高性能的嵌入式智能系统中。介绍了MSP430F449在低功耗、高精度智能雷达液位液位仪中的应用,保证了系统达到较高的性能指标。关键词: MSP430F449 雷达液位仪直接数字频率合成 HART协议 单片机技术已经渗透到人类生活的各个方面,广泛应用于家用电器、通信、工业控制等领域。随着电子技术的发展,单片机也呈现出高集成度、低功耗、基于闪存的可编程技术和将复杂模块集成到内部等发展趋势。TI公司的MSP430系列单片机就顺应了这些发展趋势。它的低功耗特点使之特别适用于电池供电设备或手持设备中。该系列单片机还将大量的外围模块整合到片内,所以也适合构成较完整的片上系统。其丰富的型号给设计者选择带来了很大的灵活性。MSP430系列采用16位精简指令架构,有大量工作寄存器和数据存储器(MSP430F449含有最多的2KB的RAM),可以说,MSP430系列单片机凭借这些杰出的性能特点,已成为众多单片机中耀眼的新星。雷达液位仪是雷达技术应用于民用领域的典型例子,它用于石油工业等行业里高压储罐的液位测量中。国外公司开发的产品价格昂贵,而国内的相关研究结果还不能令人满意。所以研制高性能、智能化的雷达液位仪,对我国石油工业液位测量仪器的更新具有重要意义。为达到本质安全的工业标准,研制的雷达液位仪对系统提出了极为严格的要求,其功耗必须低于70mW,同时精度要达到±5mm。这给MSP430系列单片机提供了发挥特长的机会。通过选用这个系列产品中最高端的MSP430F449,充分利用其低功耗、高性能、丰富的片上外设等特点搭建系统平台,再加上采用特殊的系统控制和信号处理信号处理机制,非常好地实现了系统指标要求。1 MSP430F449简介MSP430F449是MSP430系列产品中最高档的型号。它采用16位RISC结构,具有丰富的片内外设和大容量的片内工作寄存器和存储器,性能价格比很高。它的特点有:·超低的功耗:能够在1.8V~3.6V的电压下工作;具有工作模式(AM)和五种低功耗模式(LPM)。在3V、1MHz时钟驱动下,各个工作模式下的供电电流典型值如表1所示。 可见工作模式供电电流典型值低达420μA,低功耗模式电流更是显著降低,最低为0.1μA。在低功耗模式下,CPU可以被中断唤醒,响应时间小于6μs。·较强的运算能力:16位的RISC结构,丰富的寻址方式;具有16个中断源,并且可以任意嵌套;在8MHz 时钟驱动下指令周期可达125ns;内部包含硬件乘法器和大量寄存器以及多达64K Byte的FLASH程序空间和2K Byte的RAM空间,为存储数据和进行运算提供了保证。这些特点使MSP430F449具有很强的数字信号处理能力,可以开发出高效率的源程序。·丰富的片上外设:包括看门狗定时器,基本定时器,比较器,16Bit定时器(TA、TB),串口0、1,液晶显示驱动器,六个8bit的I/O端口,12位ADC(最高采样率200kHz)等。丰富的片上外设使设计者可以很方便地构建一个较为完整的系统。另外,充分利用计数器的多路任意波形产生功能和中断控制功能,保证了一些复杂的时序控制任务的完成。·方便高效的开发环境:MSP430F449是FLASH型器件,片内有JTAG调试接口和电可擦写的FLASH存储器,所以可以先下载程序到FLASH内,再在器件内通过软件控制程序的运行,由JTAG接口读取片内信息供设计者调试。这种方式不需要仿真器和编程器,调试十分方便。2 雷达液位仪实现方案2.1 雷达液位仪系统结构低功耗、高精度智能雷达液位仪的系统结构。 系统硬件分为三部分:测量模块、HART通信模块通信模块和测量线。测量模块电路板包括MSP430F449控制器、直接数字频率合成器(DDS)控制的窄脉冲产生电路、脉冲收发与处理电路、A/D采样、结果显示等。这个模块完成距离的精确测量,并实时地通过HART板同上位机进行数据通信。HART板完成MSP430F449控制器与上位机的通信、4~20mA电流的产生、电

液晶显示模块使用手册 版本:V2.0 型号:240128K 系列 选 配 件 说 明 □常温(0~50℃) □宽温(-20~+60℃) 液晶片 □超宽温(-30~+70℃) □黄绿膜 □蓝膜 □灰膜 □黑白膜 LED背光 □白光 □翡绿光 □黄绿光 □蓝光 背 光 EL背光 □白光 □蓝光 □CCFL背光 负压电路 □板载负压 □不带负压 EL逆变器 □配备 □板载 □不配备 CCFL逆变器 □配备 □不配备

一. 概述 240128K是一种图形点阵液晶显示模组。它用T6963C作为控制器,KS0086作为驱动的240(列)X128(行)的全点阵液晶显示。具有与INTER8080时序相适配的MPU接口功能,并有专门的指令集,可完成文本显示和图形显示的功能设置。 二. 特性 1.工作电压为+5V±10% 2.显示内容:240×128点,可显示15个(/行)X8共120个(16×16点阵)的中文字符 3.内部有固定字模库共128种(8X8)字符和2K字节的自定义字模容量。 4. 共有13条操作指令 三. 外形尺寸 . 项目标 准 尺 寸 单 位 模 块 体 积 120×86×12.5mm 定 位 尺 寸110×76mm 视 域93×48.1mm 行 列 点 阵 数 240×128dots 点 距 离 0.03×0.03 mm 点 大 小0.3×0.3 mm

四.硬件说明 1,带控制器引脚特性 电平 功能描述 序号 J1 1 FG - 结构地 2 GND - 逻辑电源负(0V) 3 VCC - 逻辑电源正 (5V) 4 VO - 液晶显示电压输人(调节显示对比度) 5 /WR H/L 写信号口 6 /RD H/L 读信号口 7 /CE H/L 片选信号 8 C/D H/L H:指令通道;L:数据通道 9 RES H/L 复位信号 10 DB0 H/L 数据位0 11 DB1 H/L 数据位1 12 DB2 H/L 数据位2 13 DB3 H/L 数据位3 14 DB4 H/L 数据位4 15 DB5 H/L 数据位5 16 DB6 H/L 数据位6 17 DB7 H/L 数据位7 18 FS H/L 液晶显示字体选择(H:6X8 ,L: 8X8) 19 BLA - 背光正 20 BLK - 背光负 21 VOUT 液晶显示电压输出

UOC3+GM5221液晶电视原理及维修简要说明—— LCD2003EU/TLM1588/TLM2077 一、方案概述 本机采用LG-PHILIPS公司的20.1英寸高亮度、高对比度、宽视角电视专用液晶屏。图像处理部分由GENESIS公司的嵌入式芯片GM5221(其中包括CPU、A/D转换、SCALER、DEINTERLACE部分),PHILIPS的模拟解码,图文,丽音处理芯片UOC3,成都旭光的频率合成式高频头TDQ-6FT/W124H等组成。 二、原理说明(参照电路图) (一)、电源部分 本机工作时有12V、5V、3.3V、1.8V、33V等多组电压。 (1) 12 V部分 由内置电源直接供给直流12V,由于内置电源是作为一个部件采购,这里就不在详细描述其工作原理。本机需要12V供电的部分有:伴音功放N601 (解码板TDA1517P)、耳机功放N600(解码板TDA2822M)、逆变器(INVERTER)、 升压模块N401(解码板BA6161N)。 ⑵5V部分 本机由集成电路U9(主板LM2576-5.0)及其外围电路构成了一个降压型开关电源。通过这个开关电源,将12V直流电压变为5V直流电压为整机供电。在这个电路中,U9相当于一个起开关作用的功率晶体管,L10(100yH)为储能电感,D3 11N5822)为续流二极管,由于工作于开关方式,使其输出负载电流大(3.0A),电源转换效率高(77%)发热量小,可以采用铜箔散热的方式。同时,本电路还具有输出限流,及在故障状况下提供完全保护的热关断功能。 (3)3.3V 部分 本机3.3V是通过两个低压差线性电压稳压器U11(主板LM1117-3.3)、N400 (解码板LM1117-3.3)、对5V直流电压进行稳压来得到。此外该芯片还具有内部限流和热关断的功能,LM1117-3.3的最大输出电流为800毫安。 ⑷1.8V部分 本机1.8V是通过两个低压差线性电压稳压器U13(主板LM1117-1.8) 对5V直流电压进行稳压来得到。此外该芯片还具有内部限流和热关断的功倉泛。 (5)33V部分

//***************************************************************************** * // MSP430-TEST44X Demo - FLL+ clock, Runs internal DCO at 2.45Mhz // // // // MSP430F449 // ----------------- // /|\| XIN|- // | | | 32khz xtal // --|RST XOUT|- // | | // | P1.1|--> MCLK = 2.4576Mhz // | | // | P1.5|--> ACLK = 32khz // | | // // // 程序功能:该程序是通过设置不同的时钟源输出模式,具体是P1.5=ACLK=32.768Khz;P1.1=MCLK=4.9Mhz, // 通过本实验了解MSP430内部的时钟来源和不同频率的设置。 // 硬件连接:在必须连接P1.1、P1.5短接器, // MSP430F449复位后,MCLK和SMCLK的驱动源为DCO,SMCLK=MCLK=32*ACLK=32*32768=1048576Hz。 //////fDCOCLK = D x (N + 1) x fACLK。 //////N的设置为SCFQCTL = N(N取值1~127); /////D的设置为SCFI0 = D(D取值FLLD_1,FLLD_2,FLLD_4,FLLD_8,即D=1,2,4,8),默认值D 取2; /////还要设置FLL_CTL0 |= DCOPLUS,D才会生效 //***************************************************************************** * #include "msp430x44x.h" void main(void) { WDTCTL = WDTPW + WDTHOLD; // Stop watchdog timer SCFI0 |= 2; // 可取1.2.4.8 FLL_CTL0 = XCAP18PF+DCOPLUS; // set load capacitance for xtal SCFQCTL = 74; // (可取1~127) (74+1) x 32768*2 = 4.9Mhz P1DIR = 0x22; // P1.1 & P1.5 to output direction P1SEL = 0x22; // P1.1 & P1.5 to output MCLK & ACLK while(1); // loop in place }

随着生活水平的不断提高以及城市老龄化比例的提高,医疗电子设备的家庭化逐渐成为了趋势。其中家用电子血压计就是典型的家庭医疗检测设备之一。目前血压计大致上可分为两种:一是水银式血压计,其优点为数值稳定,其缺点为无法一个人自行操作,必须专业医护人员操作,且肉眼观察误差极大,主观性强,体积较大不易携带。二是电子式血压计,其优点为:使用简易,可一人独自操作;测量值便于记录,体积轻巧便于携带。电子式血压计具备了诸多优点,越来越受到普通家庭的欢迎。本文介绍了以MSP430F449为控制核心,辅以BP01型压力传感器与MCU之间模拟信号处理电路以及LCD显示、语音提示,实现家用电子血压计的设计。 血压测量原理 血压的概念就是血液流经血管壁时的压力。由心脏出来的血液,需要有推力,才能绕行身体一周,心脏就是借着不停的收缩、放松,将血液推送前进。血压有两种,一是收缩压:是当心脏收缩将血液打到血管所测得的血压,另一是舒张压:是心脏在不收缩所测得的压力。当袖带的压力等于血压时,血液开始可以流通而产生所谓的袖带声,这时候表现为收缩压,从这一刻开始做记录,直到最后袖带声音消失的时候,记录此点即为舒张压。 电子血压计工作原理 系统框图如图1所示。系统由恒流源、压力传感器、放大电路、带通滤波、二次放大、血压脉冲触发、液晶驱动器、键盘语音电路和单片机组成。 图1电子血压计原理图 单片机主要原理为:PWM输出控制气泵充气漏气调整袖带内气压;一路ADC采样袖带内气压直流分量以便取得收缩压和舒张压;一路ADC采样袖带内气压交流分量经分析计算后确定收缩压和舒张压的瞬态时间位置;接收血压脉冲信号触发ADC工作;将计算出的收缩压和舒张压结果输出至LCD显示并进行数值的语音提示。

LED显示屏使用说明书 为保证我们的产品可以在合理条件下正常使用,得到您对产品的认可,我们将简述产品的使用流程以及注意事项,请认真阅读后,再进行LED显示屏的安装和调试工作。 ☆使用硬件设备清单 LED显示屏信号连接线电源连接线系统控制卡(装载在电脑内)系统接收卡(装载在LED显示屏内)台式电脑(含DVI视频输出及串口)显示屏以及相关附属配件 ☆使用流程 硬件安装 安装步骤如下: 1、把DVI显示卡插于主板的AGP插槽,安装好该卡的驱动程序; 2、将数据采集卡插于空的PCI插槽(如果有使用); 3、用DVI电缆线把数据采集卡与显示卡连接在一起; 4、把控制线与串口(Rs232)相连(可选,灵星雨系统需要); 5、用网线与接收卡相连;(具体条数根据工程图纸) 6、检查连接无误即可进行设置或上电调试。 软件安装 安装步骤如下: 1、显卡驱动安装 将显卡驱动程序光盘插入光驱,即可自动进入安装状态,请按提示操作即可。 首先安装DirectX8.1;然后再安装驱动程序;最后安装控制面板。 2、播放软件 安装大屏幕专用播放与设置软件LED演播室,或其他控制软件 将随屏所附应用软件光碟插入光驱,复制或安装所有的程序到计算机上。 ☆电子屏操作步骤(重要) 1、开屏:请先打开计算机,再打开电子屏。 为各设备通入电源(确保输入电压符合产品要求) 打开LED屏体(屏体通电瞬间会有区域性的闪烁,表明屏体通电),打开计算机,务必确保显卡设置正确(不正确会没有显示画面,即黑屏),打开控制软件,进行基本的像素尺寸和显示区域设置(此设置并不影响LED显示屏画面的显示) 2、关屏:首先关掉LED屏体电源,关掉控制软件,再正确的关闭计算机。 ☆发现问题 1 检查各接线方式是否正确,包括,强电部分的连接(弱电部分已经在生产企业测试完成),信号连接是否正确,主要为系统接收卡输入与输出方向是否正确,接收卡上有方向示意。系统连接是否正确(请翻阅系统连接说明) 计算机软件部分是否完成安装,包括显卡的设置(请翻阅显卡设置说明)和控制软件安装。☆注意事项 1、遵守《用户使用手册》中的操作步骤; 2、防潮,湿度要求为:最高工作温度时,LED显示屏应小于相对湿度为92% 3、温度适当,温度要求为:工作环境温度-20°C≤t≤80°C 贮存环境温度-40°C≤t≤60°C 4、供电电源要符合要求 LED显示屏的供电电源电压:220V±10% 频率:50HZ±5% 安全大地接触可靠,地线与零线隔离可靠,接入电源远离大功率用电设备。 在操作流程中的其他问题,请翻阅相关说明,如再有疑问请联系我们。

高清液晶监视器 说明书 (32″)V2.0版 使用操作本产品前,请仔细阅读完本说明书,并保留好以备将来参考

用户服务指南 尊敬的用户: 感谢您选用液晶监视器,为了维护您的利益,及时为您排忧解难,敬请您注意以下事项下事项: 1、我公司产品附有一份《保修卡》,请您在购买产品之后将购机凭证(有效发票)与《保修 卡》妥善保管好,作为今后的保修依据。 2、我公司竭诚为您提供“整机免费保修一年,中心城市24小时内上门服务,边远地区预约 服务”。 3、本机所享受的保修服务只适用于中国大陆使用的用户,不适用其它国家或地区。 装箱清单 液晶监视器…………………………………………1台 说明书………………………………………………1本 合格证………………………………………………1个 保修卡………………………………………………1个 遥控器………………………………………………1个 电源线………………………………………………1条

目录 一、注意事项 (4) 二、警告注意 (5) 三、产品功能特点 (6) 四、基本技术参数 (7) 五、接口说明 (11) 六、遥控器说明 (12) 七、屏幕显示菜单(OSD) (13) 八、简单故障排除 (16)

一、注意事项 使用本产品前,请详细阅读下列注意事项,并请妥善保管以备日后查询。 产品使用本产品时请依照下列规范要求 ◆请不要掩盖或阻塞机体背后散热孔,以免妨碍机体散热。 ◆请不要用锐利物、金属或液体触碰信号接头或进入散热孔内,以免电路短路及产品损坏。 ◆请不要尝试自行分解、拆卸本产品任何部分,这样的行为可能会损坏产品及对人体造成伤害, 并使您所享有的产品保修失效。 ◆请不要用手指直接接触屏幕表面,这样可能会损伤屏幕表面,且皮肤上的油脂若留在屏幕上将很 难清除。 ◆请不要对LCD屏幕施加压力,LCD屏幕是非常精致且脆弱的。 搬运 ◆搬运监视器之前,请断开所有连接的线缆 ◆搬运大型监视器时,需要两人以上。 ◆搬运监视器时,禁止对液晶面板施加压力。 ◆搬运监视器以进行维护或移动时,请使用原有的纸箱和包装材料进行包装。 ◆抬起或移动监视器时,请牢牢扶住后侧和底部。(见下图) 安装 ◆仅可由有资格的服务人员进行监视器安装。 ◆设计安装监视器方案须参照产品外形结构尺寸图(请向经销商索取)。 ◆强烈建议您使用创捷原厂提供的配件(挂架、底座)以保证安装的可靠性和安全性。 ◆监视器安装时,须预留合理的维护操作空间和散热空间 插头在下列情况下,请拔下本产品的电源线 ◆如果您很长一段时间不使用本产品。 ◆如果电源线或电源插座/插头有损坏。 ◆请您依照本使用手册说明进行产品组装货调整,请不要自行以非本手册说明范围内的方式或程序 调整或操作本产品,如果您以非本说明手册的方式或程序调整或操作本产品发生不可预期的状况,请您将电源线拔下并通知本公司相关客服/技术人员为您处理。 ◆如果产品受撞击或摔落,以致外壳破损时。 电源线及信号连接线 ◆请不要让任何物体压迫电源线或信号连接线。 ◆请不要让本产品之电源线或信号连接线经过走道,或人们可能常走动的地方,以避免线体被踩到。 ◆请不要让电源插座或电源线超负荷使用。 ◆请不要让本产品之电源线或信号连接线置于潮湿的地方。

液晶模块说明书SPEC NO YM12864G REV NO 1.0 液晶显示模块 中文说明书 产品类型: 标准产品 产品系列号: YM12864G 产品描述: 128x64图形点阵, 控制器:KS0108,LED背光 编写: Dexun Zou 审核: HCC 批准: Jingxi Yang 发行日期: 2002.1 大连佳显电子有限公司 地址:大连市沙河口区工华街17号 Tel: (0411)84619565 Fax: (0411)84619585 网址: https://www.doczj.com/doc/622727672.html, E-mail:market@https://www.doczj.com/doc/622727672.html,

一.概述 YM12864G是一种图形点阵液晶显示器。它主要采用动态驱动原理由行驱动—控制器和列驱动器两部分组成了128(列)×64(行)的全点阵液晶显示。 此显示器采用了COB的软封装方式,通过导电橡胶和压框连接LCD,使其寿命长,连接可靠。 二.特性 1.工作电压为+5V±10% ,可自带驱动LCD所需的负电压。 2.全屏幕点阵,点阵数为128(列)×64(行),可显示8(/行)×4(行)个(16× 16点阵)汉字,也可完成图形,字符的显示。 3.与CPU接口采用5条位控制总线和8位并行数据总线输入输出,适配M6800系列时序。 4.内部有显示数据锁存器 5.简单的操作指令 显示开关设置,显示起始行设置,地址指针设置和 数据读/写等指令。 三.外形尺寸 1.外形尺寸图

2.主要外形尺寸 项目标 准 尺 寸 单 位 模 块 体 积 118.0×87.0×14.0mm 定 位 尺 寸 110.0×76.5 mm 视 域85.0×55.0 mm 行 列 点 阵 数 128×64dots 点 距 离 0.59×0.75 mm 点 大 小0.63×0.79 mm 四.硬件说明 1.引脚特性 引脚号引脚名称 级 别 引脚功能描述1 VSS0V电源地 2 VDD +5V 电源电压 3 VLCD 0~-10V LCD驱动负电压,要求VDD-VLCD=13V 4 RS H/L 寄存器选择信号 5 R/W H/L 读/写操作选择信号 6 E H/L 使能信号 7 DB0 8 DB1 9 DB2 10 DB3 H/L八位三态并行数据总线 11 DB4 12 DB5 13 DB6 14 DB7 15 CS1 H/L 片选信号,当CS1=H时,液晶左半屏显示 16 CS2 H/L 片选信号,当CS2=H时,液晶右半屏显示 17 /RES H/L 复位信号,低有效 18 VEE -10V 输出-10V的负电压(单电源供电) 19 LED+(EL)+5V 背光电源,Idd≤300mA 20 LED-(EL) 0V