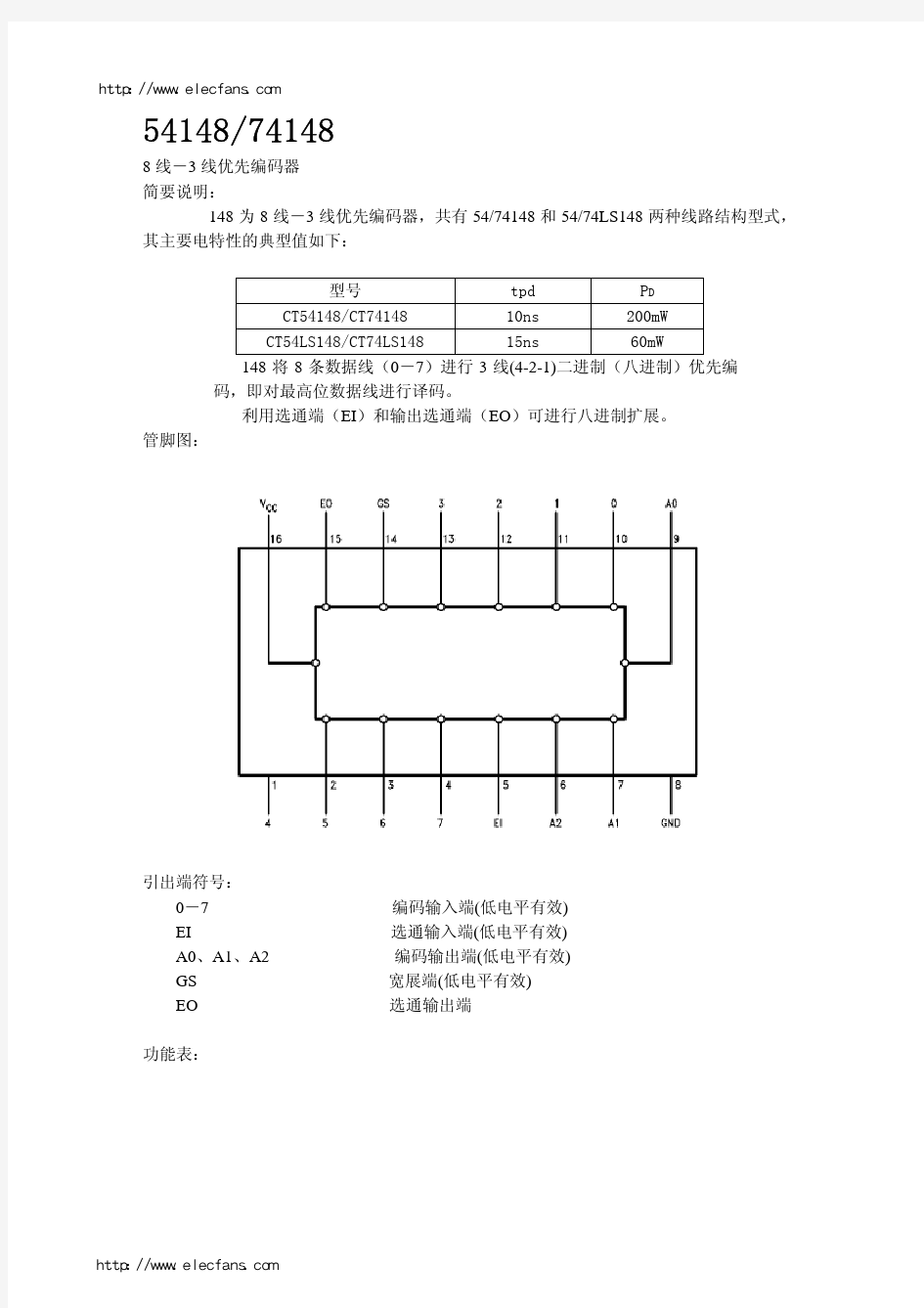

优先编码器74LS148 有些单片机控制系统和数字电路中,无法对几个按钮的同时响应做出反映,如电梯控制系统在这种情况下就出出现错误,这是绝对不允许的于是就出现了74ls148优先编码器,先说一下他的基本原理.他允许同时输入两个以上编码信号。不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。 〈74ls148管脚功能〉〈74ls148引脚图〉 74ls148优先编码器管脚功能介绍:为16脚的集成芯片,电源是VCC(16) GND(8),I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE是使能输出端,GS 为片优先编码输出端。 〈74ls148逻辑图〉〈74ls148逻辑表达式〉 使能端OE(芯片是否启用)的逻辑方程: OE =I0·I1·I2·I3·I4·I5·67·IE 当OE输入IE=1时,禁止编码、输出(反码):A2,A1,A0为全1。 当OE输入IE=0时,允许编码,在I0~I7输入中,输入I7优先级最高,其余依次为:

I6,I5,I4,I3,I2,I0,I0等级排列。 输入输出 EI I0I1I2I3I4I5I6I7A2A1A0GS EO 1 x x x x x x x x 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 0 0 x x x x x x x 0 0 0 0 0 1 0 x x x x x x 0 1 0 0 1 1 0 0 x x x x x 0 1 1 0 1 0 1 0 0 x x x x 0 1 1 1 0 1 1 1 0 0 x x x 0 1 1 1 1 1 0 0 1 0 0 x x 0 1 1 1 1 1 1 0 1 1 0 0 x 0 1 1 1 1 1 1 1 1 0 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 0 <优先编码器74ls148功能表> 从以上的的功能表中可以得出,74ls148输入端优先级别的次序依次为I7,I6,…,I0 。当某一输入端有低电平输入,且比它优先级别高的输入端没有低电平输入时,输出端才输出相应该输入端的代码。例如:I5=0且I6=I7=1(I6、I7优先级别高于I5) 则此时输出代码010 (为(5)10=(101)2的反码)这就是优先编码器的工作原理。

.v .. .. 常用芯片引脚 74LS00数据手册 74LS01数据手册 74LS02数据手册 74LS03数据手册 74LS04数据手册 74LS05数据手册 74LS06数据手册 74LS07数据手册 74LS08数据手册 74LS09数据手册 74LS10数据手册 74LS11数据手册

第2页 共8页 74LS12数据手册 74LS13数据手册 74LS14数据手册 74LS15数据手册 74LS16数据手册 74LS17数据手册 74LS19数据手册 74LS20数据手册 74LS21数据手册 74LS22数据手册 74LS23数据手册 74LS26数据手册 74LS27数据手册 74LS28数据手册

.v .. .. 74LS30数据手册 74LS32数据手册 74LS33数据手册 74LS37数据手册 74LS38数据手册 74LS40数据手册 74LS42数据手册 [1].要求0—15时,灭灯输入(BI )必须开路或保持高电平,如果不要灭十进制数零,则动态灭灯输入(RBI )必须开路或为高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [3].当动态灭灯输入(RBI )和A,B,C,D 输入为低电平而试灯输入为高电平时,所有输出端都为低电平并且动态灭灯输入(RBO )处于第电平(响应条件)。 [4].]当灭灯输入/动态灭灯输出(BI/RBO )开朗路或保持高电平而试 灯输入为低电平时,所有各段输出均为高电平。 表中1=高电平,0=低电平。BI/RBO 是线与逻辑,作灭灯输入(BI )或动态灭灯(RBO )之用,或者兼为二者之用。

一:分类 74ls00 2输入四与非门 74ls01 2输入四与非门 (oc) 74ls02 2输入四或非门 74ls03 2输入四与非门 (oc) 74ls04 六倒相器 74ls05 六倒相器(oc) 74ls06 六高压输出反相缓冲器/驱动器(oc,30v) 74ls07 六高压输出缓冲器/驱动器(oc,30v) 74ls08 2输入四与门 74ls09 2输入四与门(oc) 74ls10 3输入三与非门 74ls11 3输入三与门 74ls12 3输入三与非门 (oc) 74ls13 4输入双与非门 (斯密特触发) 74ls14 六倒相器(斯密特触发) 74ls15 3输入三与门 (oc) 74ls16 六高压输出反相缓冲器/驱动器(oc,15v) 74ls17 六高压输出缓冲器/驱动器(oc,15v) 74ls18 4输入双与非门 (斯密特触发) 74ls19 六倒相器(斯密特触发) 74ls20 4输入双与非门 74ls21 4输入双与门 74ls22 4输入双与非门(oc) 74ls23 双可扩展的输入或非门 74ls24 2输入四与非门(斯密特触发)

74ls25 4输入双或非门(有选通) 74ls26 2输入四高电平接口与非缓冲器(oc,15v) 74ls27 3输入三或非门 74ls28 2输入四或非缓冲器 74ls30 8输入与非门 74ls31 延迟电路 74ls32 2输入四或门 74ls33 2输入四或非缓冲器(集电极开路输出) 74ls34 六缓冲器 74ls35 六缓冲器(oc) 74ls36 2输入四或非门(有选通) 74ls37 2输入四与非缓冲器 74ls38 2输入四或非缓冲器(集电极开路输出74ls39 2输入四或非缓 冲器(集电极开路输出) 7 4ls40 4输入双与非缓冲器 7 4ls41 bcd-十进制计数器 7 4ls42 4线-10线译码器(bcd输入) 7 4ls43 4线-10线译码器(余3码输 入) 7 4ls44 4线-10线译码器(余3葛莱 码输入) 7 4ls45 bcd-十进制译码器/驱动器 7 4ls46 bcd-七段译码器/驱动器

74ls147引脚图管脚图和功能真值表 优先编码器是当多个输入端同时有信号时,电路只对其中优先级别最高的输入信号进行编码。常用的集成优先编码器IC有10线-4线、8线-3线两种。10线-4线优先编码器常见的型号为54/74147、54/74LS147,8线-3线优先编码器常见的型号为54/74148、54/74LS148。 下面我们以TTL中规模集成电路74LS147为例介绍8421→BCD码优先编码器的功能。 10线-4线8421 BCD码优先编码器74LS147的真值表见表3.5。74LS147的引脚图如图3.5所示,其中第9脚NC为空。74LS147优先编码器有9个输入端和4个输出端。某个输入端为0,代表输入某一个十进制数。当9个输入端全为1时,代表输入的是十进制数0。4个输出端反映输入十进制数的BCD 码编码输出。 74LS147优先编码器的输入端和输出端都是低电平有效,即当某一个输入端低电平0时,4个输出端就以低电平0的输出其对应的8421 BCD编码。当9个输入全为1时,4个输入出也全为1,代表输入十进制数0的8421 BCD编码输出。 表3.5 74LS147的真值表

数字电路CD4511的原理(引脚及功能) CD4511是一个用于驱动共阴极 LED (数码管)显示器的 BCD 码—七段码译码器,特点:具有BCD转换、消隐和锁存控制、七段译码及驱动功能的CMOS电路能提供较大的拉电流。可直接驱动LED显示器。 CD4511 是一片 CMOS BCD—锁存/7 段译码/驱动器,引脚排列如图 2 所示。其中a b c d 为 BCD 码输入,a为最低位。LT为灯测试端,加高电平时,显示器正常显示,加低电平时,显示器一直显示数码“8”,各笔段都被点亮,以检查显示器是否有故障。BI为消隐功能端,低电平时使所有笔段均消隐,正常显示时, B1端应加高电平。另外 CD4511有拒绝伪码的特点,当输入数据越过十进制数9(1001)时,显示字形也自行消隐。LE是锁存控制端,高电平时锁存,低电平时传输数据。a~g是 7 段输出,可驱动共阴LED数码管。另外,CD4511显示数“6”时,a段消隐;显示数“9”时,d段消隐,所以显示6、9这两个数时,字形不太美观图3是 CD4511和CD4518配合而成一位计数显示电路,若要多位计数,只需将计数器级联,每级输出接一只 CD4511 和 LED 数码管即可。所谓共阴 LED 数码管是指 7 段 LED 的阴极是连在一起的,在应用中应接地。限流电阻要根据电源电压来选取,电源电压5V时可使用300Ω的限流电阻。 用CD4511实现LED与单片机的并行接口方法如下图:

潍坊学院 专业课综合课程设计说明书 设计题目:四路抢答器设计 系部:信息与控制工程学院 专业:电气自动化技术 班级:一班 学生姓名: 2013年6月10日

目录 1.设计任务和要求 (3) 2.设计方案 (3) 2.1设计思路 (3) 2.2设计原理 (4) 2.3实现功能 (4) 3.硬件设计 (5) 3.1各功能电路连线图 (5) 3.2框图和说明 (6) 4.软件设计 (7) 5.小结 (8) 6.参考文献 (9)

1设计任务与要求 1.1 可同时供四名选手参赛,其编号分别是1-4,各用一个抢答按钮,按钮的编号和选手的编号相对应,给节目主持人设置一控制开关,用于控制系统的清零(编号显示数码管灭灯)抢答的开始。 1.2 抢答器具有数据锁存和显示的功能,抢答开始后,若有选手按抢答按钮,其编号立即所存,并在数码管上显示该选手的编号,同时封锁输入电路,禁止其他选手抢答。优先抢答选手的编号一直保持到主持人主持人将系统清零为止。 2 设计方案 2.1 设计思路 2.1.1 在给定5V直流电源电压的条件下设计一个可以容纳四组参赛者的抢答器,每组设定一个抢答按钮供参赛者使用。 2.1.2 设置一个系统清零和抢答控制开关K(该开关由主持人控制),当开关K被按下时,抢答开始(允许抢答),打开后抢答电路清零。 2.1.3 抢答器具有一个抢答信号的鉴别、锁存及显示功能。即有抢答信号输入(参赛者的开关中任意一个开关被按下)时,锁存相应的编号,并在LED数码管上显示出来,同时扬声器发生声响。此时再按其他任何一个抢答器开关均无效,优先抢答选手的编号一直保持不变,直到主持人将系统清除为止。 2.1.4 开关K按下后,抢答开始,开始10S倒计时。 2.2 设计原理 2.2.1原理图

常用芯片引脚 74LS00数据手册74LS01数据手册74LS02数据手册 74LS03数据手册74LS04数据手册74LS05数据手册 74LS06数据手册74LS07数据手册74LS08数据手册 74LS09数据手册74LS10数据手册74LS11数据手册

74LS12数据手册 74LS13数据手册 74LS14数据手册 74LS15数据手册 74LS16数据手册 74LS17数据手册 74LS19数据手册 74LS20数据手册 74LS21数据手册 74LS22数据手册 74LS23数据手册

74LS26数据手册74LS27数据手册74LS28数据手册 74LS30数据手册74LS32数据手册74LS33数据手册 74LS37数据手册74LS38数据手册74LS40数据手册 74LS42数据手册

[1].要求0—15时,灭灯输入(BI )必须开路或保持高电平,如果不要灭十进制数零,则动态灭灯输入(RBI )必须开路或为高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [3].当动态灭灯输入(RBI )和A,B,C,D 输入为低电平而试灯输入为高电平时,所有输出端都为低电平并且动态灭灯输入(RBO )处于第电平(响应条件)。 [4].]当灭灯输入/动态灭灯输出(BI/RBO )开朗路或保持高电 平而试灯输入为低电平时,所有各段输出均为高电平。 表中1=高电平,0=低电平。BI/RBO 是线与逻辑,作灭灯输入(BI )或动态灭灯(RBO )之用,或者兼为二者之用。 74LS49数据手册 ·74XX49简介: [1].要求0—15时,灭灯输入(BI )必须开路或保持高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [1].要求0—15时,灭灯输入(BI )必须开路或保持高电平,如果不要灭十进制数零,则动态灭灯输入(RBI )必须开路或为高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [3].当动态灭灯输入(RBI )和A,B,C,D 输入为低电平而试灯输入为高电平时,所有各段灯输出(RBO )为低电平(响应条件)。[4].当灭灯输入/动态灭灯输出(BI/RBO )开 而试灯输入为低电平,则所有输出端都为1。

实验六编码、译码显示电路 一、实验目的 1.熟悉七段发光二极管显示器的结构及工作原理。 2.掌握分段式显示译码电路的设计方法及调试方法。 3.掌握编码器的逻辑功能及其应用。 4.掌握中规模显示译码器74LS48和优先编码器74LS148的功能和使用方法。 二、手动实验预习要求及思考题 1.复习8/3线优先编码器74LS148的工作原理及逻辑功能。 2.复习中规模译码器74LS48的工作原理及逻辑功能。 3.用发光二极管组成的七段显示器按结构分为共阴极和共阳极两种,中规模译码器74LS48应采用哪种结构形式?为什么? 4.译码电路输出与笔画段之间是否要加限流电阻器。 5.设计一个能显示0、一、二、三,四个字形的译码逻辑电路,输入两变量A、B。 三、仿真实验要求 采用EWB或者PSpice软件仿真电路,以便将仿真结果与实验结果进行比较。 四、实验仪器及器件 1.TTL集成芯片若干 2.万用表一块 3.电子学综合实验装置一台 五、实验内容与步骤 1.七段显示译码器的设计和调试 选用共阴极数码管、与非门74LS00、反相器74LS04和510?限流电阻,根据预习中设计出的能显示0、一、二、三,四个字形的译码逻辑电路连好,调试电路,到数码管能显示0、一、二、三,四个字形为止。要求写出设计过程,列出真值表,写出逻辑表达式,画出逻辑图。 选做:设计一个译码器,输入为两个变量,输出能显示出数字0~9和字母AbCdEFHP 中任四个字形。 2.测试74LS48译码逻辑功能 74LS48的各管脚的功能为: (1)试灯输入:当将LT置成低电平时,不论A、B、C、D输入状态如何,记录显示器状态。 (2)灭灯输入:当将BI置成低电平时,不论A、B、C、D输入状态如何,记录显示器状态。 (3)灭零输入:在A、B、C、D均为低电平时,把_____ RBI端分别接高电平、低电平,观 察数码管显示情况。

74ls148管脚图引脚功能表真值表逻 有些单片机控制系统和数字电路中,无法对几个按钮的同时响应做出反映,如电梯控制系统在这种情况下就出出现错误,这是绝对不允许的。于是就出现了74ls148优先编码器,先说一下他的基本原理.他允许同时输入两个以上编码信号。不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。 〈74ls148管脚功能〉〈74ls148引脚图〉 74ls148优先编码器管脚功能介绍:为16脚的集成芯片,电源是VCC(16) GND(8), I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE是使能输出端,GS为片优先编码输出端。 〈74ls148逻辑图〉〈74ls148逻辑表达式〉 使能端OE(芯片是否启用)的逻辑方程:

OE =I0·I1·I2·I3·I4·I5·I6·I7·IE 当OE输入IE=1时,禁止编码、输出(反码):A2,A1,A0为全1。 当OE输入IE=0时,允许编码,在I0~I7输入中,输入I7优先级最高,其余依次为:I6,I5,I4,I3,I2,I0,I0等级排列。 输入输出 EI I 0I 1 I 2 I 3 I 4 I 5 I 6 I 7 A 2 A 1 A GS EO 1x x x x x x x x11111 01111111111110 0x x x x x x x000001 0x x x x x x0100110 0x x x x x01101010 0x x x x011101110 0x x x0111110010 0x x01111110110 0x011111111010 00111111111110 <优先编码器74ls148功能表> 从以上的的功能表中可以得出,74ls148输入端优先级别的次序依次为I7,I 6,…,I0 。当某一输入端有低电平输入,且比它优先级别高的输入端没有低电平输入时,输出端才输出相应该输入端的代码。例如:I5=0且I6=I7=1(I6、I7优先级别高于I5) 则此时输出代码010 (为(5)10=(101)2的反码)这就是优先编码器的工作原理。