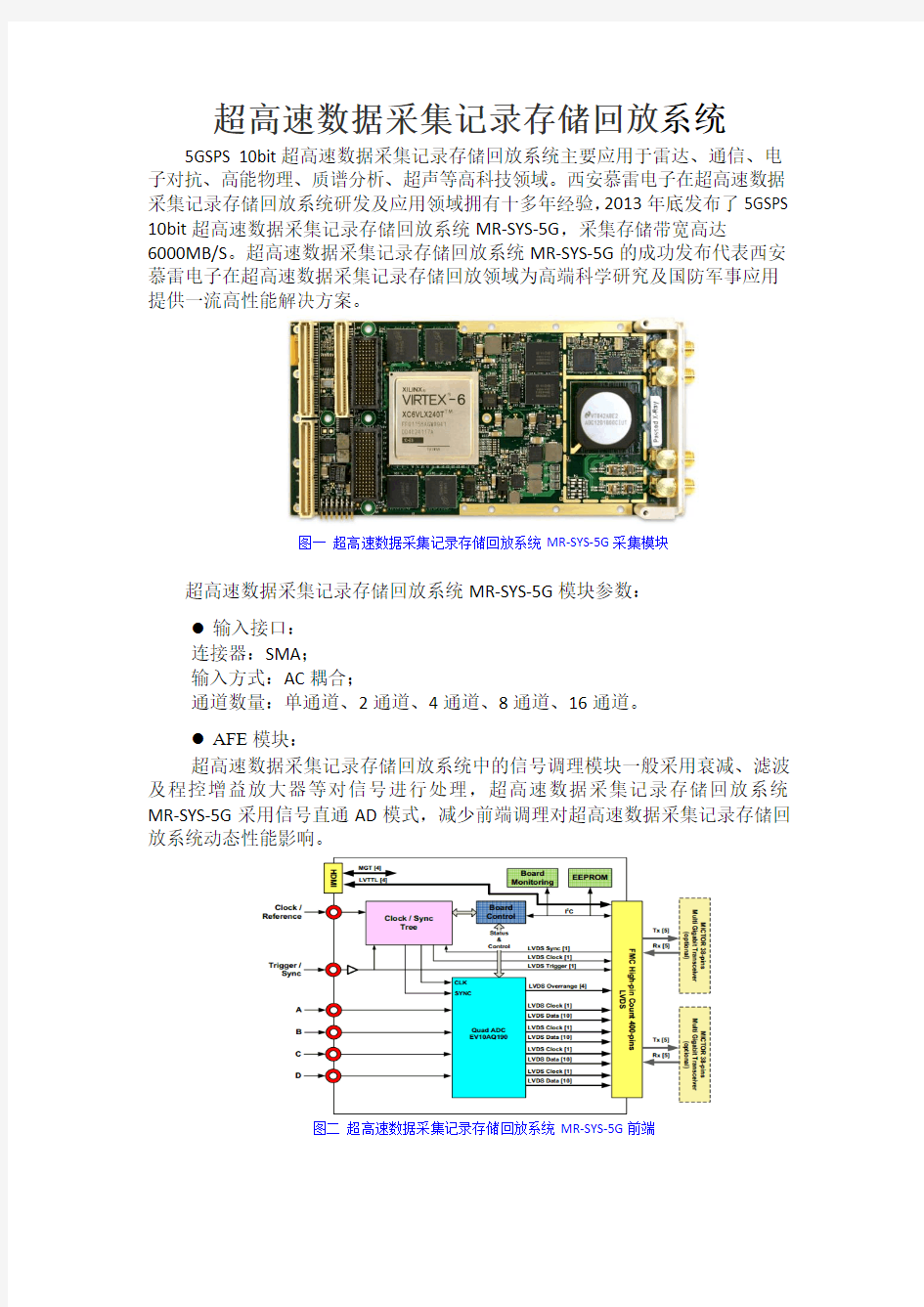

超高速数据采集记录存储回放系统5GSPS 10bit超高速数据采集记录存储回放系统主要应用于雷达、通信、电子对抗、高能物理、质谱分析、超声等高科技领域。西安慕雷电子在超高速数据采集记录存储回放系统研发及应用领域拥有十多年经验,2013年底发布了5GSPS 10bit超高速数据采集记录存储回放系统MR-SYS-5G,采集存储带宽高达

6000MB/S。超高速数据采集记录存储回放系统MR-SYS-5G的成功发布代表西安慕雷电子在超高速数据采集记录存储回放领域为高端科学研究及国防军事应用提供一流高性能解决方案。

图一超高速数据采集记录存储回放系统MR-SYS-5G采集模块

超高速数据采集记录存储回放系统MR-SYS-5G模块参数:

●输入接口:

连接器:SMA;

输入方式:AC耦合;

通道数量:单通道、2通道、4通道、8通道、16通道。

●AFE模块:

超高速数据采集记录存储回放系统中的信号调理模块一般采用衰减、滤波及程控增益放大器等对信号进行处理,超高速数据采集记录存储回放系统MR-SYS-5G采用信号直通AD模式,减少前端调理对超高速数据采集记录存储回放系统动态性能影响。

图二超高速数据采集记录存储回放系统MR-SYS-5G前端

●ADC模块:

超高速数据采集记录存储回放系统的ADC芯片采用E2V公司的EV10AQ190A,最高达5GSPS采样,模拟带宽3GHZ。

图三超高速数据采集记录存储回放系统MR-SYS-5G频率响应

●时钟管理模块:

超高速数据采集记录存储回放系统MR-SYS-5G可选择外时钟、内时钟或参考时钟

●FPGA模块:

XILINX或ALTERA的FPGA芯片广泛用于超高速数据采集记录存储回放系统中。FPGA模块开放编程是超高速数据采集记录存储回放系统的必备能力。超高速数据采集记录存储回放系统MR-SYS-5G采用ALTERA STRATIX5系列高性能FPGA。

图四超高速数据采集记录存储回放系统MR-SYS-5G

●DDR模块:

超高速数据采集记录存储回放系统一般都会配有DDR缓存,存储采集过程

中的数据。超高速数据采集记录存储回放系统MR-SYS-5G配置有16GB DDR3。

●FIFO模式

超高速数据采集记录存储回放系统将板载内存虚拟为FIFO,允许采集数据由缓冲后连续不断地通过总线传输到主机内存或硬盘中。该模式特点就是高速、大量、实时记录时间达数小时。记录时间取决于存储介质的容量。

图五超高速数据采集记录存储回放系统MR-SYS-5G

●存储记录:

超高速数据采集记录存储回放系统MR-SYS-5G输出采用PCIe GEN3.0 8LANE,传输带宽高达6000MB/S,配以西安慕雷电子为超高速数据采集记录存储回放系统定制的顶级高速固态磁盘阵列,可长达数小时持续不间断采集记录信号。超高速数据采集记录存储回放系统已广泛应用于复杂环境电磁信号采集记录存储、电子侦察、卫星导航、雷达信号高速数据记录存储等国防科研领域。

图六超高速数据采集记录存储回放系统MR-SYS-5G

西安慕雷电子发布全球顶级超高速数据采集记录存储回放系统及超宽带高

速采集记录回放系统。作为顶尖的超高速数据采集记录存储回放系统研发集成商,同时也是多家国际一流超高速数据采集记录存储回放系统厂商的合作伙伴,我们提供国际顶级高速数据采集卡、任意波形发生回放卡及相关超宽带高速数据记录回放系统。产品主要应用于雷达,通信,生物医学,超声无损检测,分布式光纤测试,质谱,高能物理,高压局放监控等领域。

PLC的高速数据采集分析与记录工具 在工业现场,设备调试时经常遇到需要对PLC各种变量捕捉分析,优化控制时序,检查动作过程是否准确等情况;在设备运行时又需要对设备的运行状态进行全方位的监控和记录,方便设备故障后,故障过程的重现与故障原因的分析,尤其一些控制逻辑复杂的设备,这种需求更加突出。 在一般情况下,SCADA监控软件的趋势记录就可以满足需求,但是SCADA在趋势与记录上存在很大的劣势,比如,采集数据量大的系统(系统本身庞大,需要采集的数据点多),采集速度要求高的系统(系统本身运行快,要求最大程度复现控制器内逻辑与数据的处理过程,如西门子TDC等),这些情况下,单纯的依靠SCADA已经无法满足我们的需要,那么就需要专用的数据采集分析与记录工具帮我们完成。 下面是对PLC的一些数据采集与记录工具的介绍。 1)、iba公司的PDA 既然要说数据采集记录工具,首先要提的当然是强大的PDA,软件本身支持很多驱动,可以选择带硬件支持的版本,一般采用控制器连接iba公司的模块,模块通过光纤连接工控机的配置方法,能够最大限度提高速度,当然也有纯软件的版本,这个软件在钢铁行业应用的比较多,如轧制过程的数据采集记录。(不过,这个软件的价格我只能呵呵了),软件截图:

2)、AUTEM公司的PLC-ANALYZER pro 关于此软件,同样提供多种驱动。支持的PLC-Driver有Siemens SIMATIC S7 / C7 / M7, SAIA xx7, VIPA, SIMATIC S5, Siemens LOGO!, SINUMERIK, SIMOTION, BOSCH, CoDeSys, PILZ, Phoenix, Jetter, Allen-Bradley, GE Fanuc, HITACHI, OMRON, Mitsubishi, Schneider, AUTEM AD_USB-Box?, Beckhoff TwinCat等,对于西门子的PLC,支持 MPI/PROFIBUS/ETHERNET等,但是在软件的实际使用时你会发现,软件功能较PDA逊色不少。软件截图:

高速数据采集系统 设计

基于FPGA和SoC单片机的 高速数据采集系统设计 一.选题背景及意义 随着信息技术的飞速发展,各种数据的实时采集和处理在现代工业控制和科学研究中已成为必不可少的部分。高速数据采集系统在自动测试、生产控制、通信、信号处理等领域占有极其重要的地位。随着SoC单片机的快速发展,现在已经能够将采集多路模拟信号的A/D转换子系统和CPU核集成在一片芯片上,使整个数据采集系统几乎能够单芯片实现,从而使数据采集系统体积小,性价比高。FPGA为实现高速数据采集提供了一种理想的实现途径。利用FPGA高速性能和本身集成的几万个逻辑门和嵌入式存储器块,把数据采集系统中的数据缓存和控制电路全部集成在一片FPGA芯片中,大大减小了系统体积,提高了灵活性。FPGA 还具有系统编程功能以及功能强大的EDA软件支持,使得系统具有升级容易、开发周期短等优点。 二.设计要求 设计一高速数据采集系统,系统框图如图1-1所示。输入模拟信号为频率200KHz、Vpp=0.5V的正弦信号。采样频率设定为25MHz。经过按键启动一次数据采集,每次连续采集128点数据,单片机读取128点数据后在LCD模块上回放显示信号波形。

图1-1 高速数据采集原理框图 三.整体方案设计 高速数据采集系统采用如图3-1的设计方案。高速数据采集系统由单片机最小系统、FPGA最小系统和模拟量输入通道三部分组成。输入正弦信号经过调理电路后送高速A/D转换器,高速A/D 转换器以25MHz的频率采样模拟信号,输出的数字量依次存入FPGA内部的FIFO存储器中,并将128字节数据在LCD模块回放显示。 图3-1 高速数据采集系统设计方案 四.硬件电路设计 1.模拟量输入通道的设计 模拟量输入通道由高速A/D转换器和信号调理电路组成。信号调理电路将模拟信号放大、滤波、直流电平位移,以满足A/D转换器对模拟输入信号的要求。

数据采集及传输处理 摘要 本文主要阐述了基于数字采集与传输处理系统的设计基本思想,包括硬件实现,应用软件实现以及驱动程序设计,同时也介绍了基于MAX485数据传输系统。 硬件的主要组成部分为AT89C51,ADC0809,MAX485,8155,LED显示。 用软件编程控制硬件实现的过程:发送方的设备把模拟信息转换为数字信息后,发送到接收方的设备上。接收设备利用LED来显示数据。 使用的核心芯片是AT89C51,这个芯片可以很好地满足我们的要求。数据采集系统用来采集模拟数据,并将模拟数据存放于存储器中作以后发送用。A/D转换器将模拟形式转换为数字量表示。使用ADC0809作为A/D转换器,它可以把连续的模拟信号转变成数字形式。选用MAX485连接两台机器进行传递信息. 软件编程的语言使用的是C 语言,它的运行的环境是keil软件。 关键词: 单片机AT89C51,ADC0809,MAX485,LED显示.

Abstract This article introduces the base method according to data collection and transmitting process system, including the hardware design, the application software design and the design of the program design, also introduces the data transmitting system according to the MAX485. The necessary hardware consists of AT89C51,ADC0809,MAX485,8155,LED display. The process of the programme of software controlling hardware operation as follow: The device on the transmitting computer converts the analog signals to digital format and this digital format is transmitted to the receiving computer. The device on the receiving computer uses the information to driver LED display. The key chip we use is AT89C51. This chip can meet our need perfectly. Data acquisition system is used to acquire analog data and store it on storage devices for later transmitting. A/D converter converts an analog format into an equivalent digital representation. We use the ADC0809 as A/D converter, which is used to convert continuous analog signals into digital format. We choose the MAX485 as the device, which is used to connect two computers for transmitting information. The programme of software language is C language, which of operation is keil software. Key words: MCS-AT89C51, A/D converter, MAX485, LED display.

激光雷达高速数据采集系统解决方案 0、引言 1、 当雷达探测到目标后, 可从回波中提取有关信息,如实现对目标的距离和空间角度定位,并由其距离和角度随时间变化的规律中得到目标位置的变化率,由此对目标实现跟踪; 雷达的测量如果能在一维或多维上有足够的分辨力, 则可得到目标尺寸和形状的信息; 采用不同的极化方法,可测量目标形状的对称性。雷达还可测定目标的表面粗糙度及介电特性等。接下来坤驰科技将为您具体介绍一下激光雷达在数据采集方面的研究。 1、雷达原理 目标标记: 目标在空间、陆地或海面上的位置, 可以用多种坐标系来表示。在雷达应用中, 测定目标坐标常采用极(球)坐标系统, 如图1.1所示。图中, 空间任一目标P所在位置可用下列三个坐标确定: 1、目标的斜距R; 2、方位角α;仰角β。 如需要知道目标的高度和水平距离, 那么利用圆柱坐标系统就比较方便。在这种系统中, 目标的位置由以下三个坐标来确定: 水平距离D,方位角α,高度H。 图1.1 用极(球)坐标系统表示目标位置

系统原理: 由雷达发射机产生的电磁能, 经收发开关后传输给天线, 再由天线将此电磁能定向辐射于大气中。电磁能在大气中以光速传播, 如果目标恰好位于定向天线的波束内, 则它将要截取一部分电磁能。目标将被截取的电磁能向各方向散射, 其中部分散射的能量朝向雷达接收方向。雷达天线搜集到这部分散射的电磁波后, 就经传输线和收发开关馈给接收机。接收机将这微弱信号放大并经信号处理后即可获取所需信息, 并将结果送至终端显示。 图1.2 雷达系统原理图 测量方法 1).目标斜距的测量 雷达工作时, 发射机经天线向空间发射一串重复周期一定的高频脉冲。如果在电磁波传播的途径上有目标存在, 那么雷达就可以接收到由目标反射回来的回波。由于回波信号往返于雷达与目标之间, 它将滞后于发射脉冲一个时间tr, 如图1.3所示。 我们知道电磁波的能量是以光速传播的, 设目标的距离为 R, 则传播的距离等于光速乘上时间间隔, 即2R=ct r 或 2 r ct R

高速数据采集卡250MSPS 14bit 250MSPS 14bit 8通道高速数据采集卡主要应用于雷达、通信、电子对抗、高能物理、质谱分析、超声等高科技领域。西安慕雷电子在高速数据采集卡研发及系统应用领域拥有十多年经验,2013年底发布了250MSPS 14bit 8通道高速数据采集卡MR-HA-250M,采集记录存储带宽高达3000MB/S。高速数据采集卡MR-HA-250M及记录存储系统的成功发布使得西安慕雷电子在高速数据采集卡及相关记录存储回放领域为国防及科研领域又提供了一套高性能解决方案。 图一高速数据采集卡MR-HA-250M 高速数据采集卡MR-HA-250M模块参数: ●输入接口: 连接器:SSMC; 输入方式:AC或DC耦合; 通道数量:8通道,可同步32通道 ●AFE模块: 高速数据采集卡中的信号调理模块一般采用衰减、滤波及程控增益放大器等对信号进行处理,高速数据采集卡MR-HA-250M采用信号直通AD模式,减少前端调理对高速数据采集卡动态性能影响。 图二高速数据采集卡MR-HA-250M

●ADC模块: 高速数据采集卡的ADC芯片采用Linear Tech LTC2157-14 (250 MSPS) 图三高速数据采集卡MR-HA-250M动态性能 ●时钟管理模块: 高速数据采集卡MR-HA-250M可选择外时钟、内时钟或参考时钟 ●FPGA模块: XILINX或ALTERA的FPGA芯片广泛用于高速数据采集卡中。FPGA模块开放编程是高速数据采集卡的必备能力。高速数据采集卡MR-HA-250M采用XILINX V6系列高性能FPGA。 ●DDR模块: 高速数据采集卡一般都会配有DDR缓存,存储采集过程中的数据。高速数据采集卡MR-HA-250M配置有4GB DDR2。 ●FIFO模式 高速数据采集卡将板载内存虚拟为FIFO,允许采集数据由缓冲后连续不断地通过总线传输到主机内存或硬盘中。该模式特点就是高速、大容量,使得高速数据采集卡记录时间达数小时。记录时间取决于存储介质的容量。 图四高速数据采集卡MR-HA-250M

------------------------------------------------------------------------------------------------------------------------------------------ 第一章 设计任务与要求 1. 设计任务 单片机在工业控制系统诸多领域得到了极为广泛的应用。特别是其中的51系列的单片机的出现,具有更好的稳定性,更快和更准确的运算精度。本次设计以8051单片机为核心,实现空调的智能控制因为8051单片机应用广泛,性能稳定,抗干扰能力强,性价比高。而且还适用于仪器仪表,不仅能完成测量还可以进行数据的处理和监控等。 本次以单片机为主控器设计单片机主电路、数据采集接口电路扩展A/D 和D/A 接口,构成一路模拟量输入的数据采集系统,要求设计制作出硬件电路、LED 显示电路、时钟信号控制电路,能够实现对多路电压值进行测量,能够显示当前实际的温度值,温度值精度小数点后1位,可以通过ADC0809模数转换芯片将采集的模拟信号转换为数字信号并在LED 显示屏显示出来。 2. 设计要求 以单片机为控制器核心扩展A/D 和D/A 接口,构成一个多路模拟量输入的数据采集系统,要求设计制作出硬件电路,编制并调试出程序。 多路数据采样系统框图

第二章设计依据 单片机在工业控制系统诸多领域得到了极为广泛的应用。特别是其中的51系列的单片机的出现,具有更好的稳定性,更快和更准确的运算精度。本次设计以8051单片机为核心,实现空调的智能控制因为8051单片机应用广泛,性能稳定,抗干扰能力强,性价比高。而且还适用于仪器仪表,不仅能完成测量还可以进行数据的处理和监控等。 51系列单片机主要功能: ●8位CPU。 ●片内带震荡器,振荡频率f ose范围为1.2到12MHz;可有时钟输出。 ●128个字节的片内数据存储器。 ●4KB的片内程序存储器。 ●程序存储器的寻址范围为64KB。 ●片外数据存储器的寻址范围为64KB。 ●21个字节专用寄存器。 ●4个8位并行I/O接口:p1、p2、p3、p0。 ●1个全双工串行I/O接口,可多机通信。 ●2个16位定时/计数器。 ●中断系统有5个中断源,可编程为2个优先级。 ●111条指令,含乘法指令和除法指令。 ●有强的位寻址、位处理能力。 ●片内采用单总线结构。 ●用单一+5V电源。 数据采样是智能仪表、自动控制系统中不可缺少的部分,本次设计中由于8051单片机本身不具备将电量信号转换成数字量的功能,所以必须扩展A/D、D/A接口。输入信号是用5 V 电源经电位器调节得到0~5 V的采样输入信号送入ADC电路。单片机分时对模拟输入信号进行采集,获得数值信号单片机内存储RAM中,也可以使用扩展RAM。经处理后的信号之后单片机将RAM中的数值量送入D/A转换电路,D/A电路通常输出与数字量相对应的模拟电流,经I/ V变换成模拟电压值。 第三章控制系统性能说明 单片机多通道温度采集测控系统采用集成温度传感器满足温度测量,并将温度信号转换成电流,转换为电压信号,通过放大电路最终交由模/数转换芯片转换成数字信号经单片机 ------------------------------------------------------------------------------------------------------------------------------------------

数据采集、存储和传输 压缩机转速为8k转/分时,频率133.33 f≈Hz,若要分析到信号频率的4倍频时,有经验公式得采样频率: 2.54133.33 1.33 f≥??≈kHz。所要采集的振动 s 信号是,x y轴两个方向的信号,故要使用采集卡的两个通道进行数据采集,所以,采样频率 f应大于2.66kHz。所以,采集卡的最高采样速率达到3kHz即可满足 s 转速为8k转/分的压缩机的振动信号采集。 中断采集: 在LabView中软件触发方式比较简单,但采样速度较低,在采集振动信号时不能满足实际要求。而采用中断触发方式可以实现数据的高速采集,最高采样速率可达100kHz。 以下是LabView下采用中断触发方式实现数据高速采集时用到的几个关键子VI的简单介绍: DeviceOpen:打开指定的设备并返回一个驱动句柄,之后所有执行相应I/O 操作的子VI 都应基于该句柄参数所获得的配置数据。该子VI 必须在调用其他驱动子VI 之前调用。 AllocDSPBuf:为用户缓冲区分配参数Count 指定大小的空间。该子VI 的输出用作FAITransfer 子VI的输入,通过MemoryType 参数可以选择以电压形式或二进制形式显示数据。程序运行结束后,LabVIEW自动释放此内存空间。EnableEvent:通过指定相应的事件类型代码来使用或禁用一个指定的事件,并通知由DriverHandle所指定的硬件设备。 MultiChannelINTSetup:开始多通道中断触发方式的A/D转换,并将采集到的数据储存到内部缓冲区,该操作将一直进行,直到调用FAIStop子VI。该子VI 运行时将自动调用AllocINTBuf子VI,分配FAIINTStart.Count参数所指定大小的内部缓冲区。与用户缓冲区不同的是,在程序结尾需另外调用子VI释放此内存空间。通过该子VI可以设置采样率、各通道增益代码、循环方式、是否使用FIFO缓存器等。 WaitFastAIOEvent:使程序进入等待状态,直到设定的事件发生(内部缓冲区半满或全满,等待结束,内部缓冲区全满)或等待时间超出用户通过Timeout参数设定的值。该子VI可以用来捕获内部缓冲区半满或全满事件。BufferChangeHandler:将数据从内部缓冲区传送到用户缓冲区。该子VI能够判断内部缓冲区当前的状态是半满还是全满,从而执行不同的操作:半满时,从内部缓冲区取出1/2Count数量的数据到用户缓冲区;全满时,不做任何传输操作。要实现连续数据采集,程序中需要反复调用该子VI。此外,如果在AllocDSPBuf中选择的是以电压形式显示数据,该子VI还负责完成从原始数据到电压值的转换。 ClearOverHandler:用来处理FAI采样缓冲区的溢出状态,并清除溢出标志。即当采集数据的数量达到FAIINTStart.Count 的值后归零,重新开始计数。OverRun:显示缓冲区中的数据是否已被及时地传送出去;HalfReady:显示内部

中图分类号:TP273 文献标识码:A 文章编号:1009-2552(2007)06-0073-03 数据采集及传输处理系统 杨永辉1,庞 宵1,李景杰2 (1.辽宁科技大学电子与信息工程学院,鞍山114044; 2.鞍钢计量厂,鞍山114001) 摘 要:为了方便地在现场监控电压或电流信号,显示出相应数值并预警出现问题的信号,很有必要设计一个低成本、观察方便、操作简易的处理系统。提出了基于数字采集及传输处理系统的基本设计思想,包括A D转换器与单片机的接口实现,MAX485的串口传输原理及并口驱动LED等,设计出了完整的电路结构与实现软件。为了编程方便及易于调试,采用C语言作为软件编程语言,开发环境是Keil软件。 关键词:数据采集;MAX485串行通信;AT89C51 System of data collection and transmitting&processing YANG Yong hui1,PANG Xiao1,LI Jing jie2 (1.School of Electronics and Information Engineering,Liaoning University o f Science and Technology,Anshan114044,China; 2.Angang Computation and Measure Company,A nshan114001,China) Abstract:In order to monitor voltage or current signals expediently at the local,display the corresponding values and alar m fault signals,it is very important to design a lo w cost system with convenient observation and straightforward operation.This article brings for ward an idea based on a system of digital data c ollection, transmitting and processing,introduces the interface between the A D converter and the single chip microcom puter,analyzes the principal of the transmitting system based on MAX485serial ports,describes the method of driving LED by parallel ports in detail,and designs a complete circuit architecture and imple mented software under this foundation.To program facilitatively and debug effortlessly,C language is adopted as the progra m ming language and the developed environment is Keil software. Key w ords:data collection;MAX485serial port communication;AT89C51 随着电子技术的迅速发展,单片机以其高可靠性、高性能、低价格、应用灵活等特点,在工业控制系统、数据采集系统、智能化仪器仪表、办公自动化等诸多领域得到极为广泛的应用。在自动控制领域,为了解设备的运行参数及运行状态,需要对各种物理量进行检测。通常采用的方法有:使用微机控制,但其设备复杂、成本较高;使用单CP U控制,虽然简单,但系统智能化及传输可靠性低。两种方法都不理想。 为了避免上述两种方法的不足,并满足现场要求,设计了一种借助单片机、显示器件、数据采集技术和现代通信技术,适用于电压和电流信号的数据采集及传输处理装置。1 方案的确定 在生产过程中需要下位机直接对生产过程进行检测,需要上位机控制并显示数据。为了提高系统的智能性、可靠性和实用性,本设计采用双C PU的方法,即在数据采集的发端和数据处理的收端都采用单片机控制,发端完成数据的采集、转换和发送,收端完成数据的接收、处理和显示功能。并在数据通信中采用差错控制技术以保证数据通信的可靠性。两片CPU都采用目前广泛应用的MC S51系列 收稿日期:2006-10-31 作者简介:杨永辉(1971-),男,1995年毕业于东北大学通信工程专业,辽宁科技大学电信学院任教,主要从事移动通信方 面的教学和科研。 73

一种高速数据采集记录装置的设计 【摘要】文章介绍了一种基于Flash的高速数据采集记录装置的实现方案;文中采用了Flash高速存储技术与FPGA的二级缓冲技术,提高了存储速度,突破存储芯片的瓶颈,成功实现了数据存储速率与传输速率完美的匹配;同时通过设计合理的电路降低了存储模块的功耗,利用可靠的通信协议,有效保证了信号数据的可靠接收和存储。 【关键词】数据记录仪;Flash;高速存储 1.系统方案设计 本文设计的数据记录系统由以下几部分组成:两台完全相同的数据记录仪、一个地面综合测试台、上位机、配套软件以及配套电缆。主要用于记录由雷达系统产生的视频回波、图像及遥测三路LVDS高速信号。系统工作时,由雷达系统首先发来启动记录信号,使已处于采集状态的两台记录仪同时工作,二者互为备份。地面测试台产生的模拟信号供记录仪存储,同时可以控制记录仪进入不同的工作状态,通过内置的USB接口读取记录仪的数据;上位机通过USB电缆与地面测试台相接,对回读的数据进行分析,同时验证记录仪是否正常工作。 2.系统硬件设计 该系统采用隔离变压器隔离接收三路LVDS数据,使得隔离前后的电路没有电气连接特性,然后再将隔离后的信号传送给存储模块;经过存储模块的均衡、解串后传给FPGA中心控制器,最后存入两片Flash中。 遥测系统输出的三路数据都有各自的启动记录信号。当记录仪接收到启动控制信号,开始记录对应路的数据,并存储到相应的存储模块中。飞行试验完毕后,可以利用备用读数电缆,将各个存储模块中数据通过测试台上传至上位机中进行分析,以便对记录仪的存储功能进行验证。在飞行模式下记录仪的供电由雷达系统完成。 记录仪由三个存储模块和一个接口模块组成。存储模块主要接收遥测系统的视频回波、图像及遥测三路LVDS信号,并对其中的有效数据进行实时存储。该模块主要包括以下几个部分:中心逻辑控制芯片FPGA、配置芯片PROM、LVDS 电缆均衡器、LVDS解串芯片、存储芯片Flash、电源模块以及60MHz晶振等[1]。如图2.1所示: 接口模块主要包括LVDS高速读数接口、RS-422长线接口、视频及图像遥测雷达信号输入接口、各个存储模块的LVDS输入接口以及数据上传和指令下发接口。高速读数接口与地面测试台主控卡的相应接口连接,通过LVDS接口高速读取其中的数据;422长线接口通过双绞线电缆与地面测试台连接,主要实现记录仪与地面测试台之间的通信。

《嵌入式综合实践》 设计报告 目录 一、树莓派简介 (2) 二、配置树莓派 (3) 1.树莓派供电 (3)

2.手动对SD存储卡进行写操作(windows) (3) 3.连接笔记本电脑显示器 (3) 三、硬件电路连接 (6) 四、DHT11简介 (7) 五、获取DHT11传感器温湿度 (7) 六、安装本地MYSQL (9) 七、连接阿里云RDS数据库 (11) 八、上传数据到传感云 (13) 九、Cron 实现定时功能 (14) 一、树莓派简介 Raspberry Pi(中文名为“树莓派”,简写为RPi,或者RasPi/RPi)是为学生计算机编程教育而设计,只有信用卡大小的卡片式电脑,其系统基于Linux。随着Windows

10 IoT的发布,我们也将可以用上运行Windows的树莓派。自问世以来,受众多计算 机发烧友和创客的追捧,曾经一“派”难求。别看其外表“娇小”,内“心”却很强大,视频、音频等功能通通皆有,可谓是“麻雀虽小,五脏俱全”。 二、配置树莓派 1.树莓派供电 树莓派的供电装置与智能手机的充电器是一样的。基本规格为DC 5V(直流电),至少达到700mA的输出电流,树莓派2的输出电流应该更大,比如1.5A或2A。 2.手动对SD存储卡进行写操作(windows) 选择一张4GB以上的SD存储卡,SD卡插入笔记本电脑卡槽(或者需要一个读卡器)。下载官方发行的树莓派操作系统发行包(https://www.doczj.com/doc/5f8113575.html,/downloads),并解压到本地。用管理员权限打开Fedora ARM Installer(http://bit.ly/ISLPc4下载),将下载的镜像写入SD存储卡。如下图: 3.连接笔记本电脑显示器 网络设置:SD卡插入树莓派的SD卡插槽,把树莓派和路由器用网线连接。打开电脑“网络和共享中心”,点击“WLAN(***)”点击“属性”,点击“共享”,在“允许其他网络用户通过此计算机的Internet来连接”前打勾。

数据采集存储系统 陈俣兵任加勒蔡露薇 摘要:本系统以C8051F360单片机最小系统为核心,结合FPGA及高速A/D数据采集模块,可靠地实现对一路外部信号进行采集、存储及FFT频谱分析。系统硬件可以分为模拟部分和数字部分。模拟电路主要包括信号调理电路、锁相环模块及A/D模块、D/A模块。调理电路主要调节信号的幅度及直流偏置,以满足A/D对输入信号1~2V的幅度要求。锁相环模块为A/D模块提供时钟信号,以实现对输入信号的整周期采样,防止频谱泄露。数字部分主要由FPGA实现,用于数据的存储、传输等。本系统对锁相环的使用实现了采样频率对输入信号的跟踪,大大增加了输入信号频率变化范围。测试显示本系统谐波分量测量误差小于1%,系统稳定可靠。 关键字:FFT C8051F360 FPGA 锁相环 一、方案选择与论证 1.系统整体方案比较与选择 方案一:采用扫频外差法。将输入信号和扫频本振产生的信号混频,使变频后信号不断移入窄带滤波器,进而逐个选出被测频谱分量。这种方法的优点是扫频范围大,但对硬件电路要求较高,分辨率不高,难以满足题目要求。 方案二:采用单片机来实现。采用单片机系统控制AD转换器将交流电压电流信号存入缓冲区后,由CPU进行频谱分析以及功率计算。此方案可以使控制模块的设计较为简单。但是,频谱分析的计算(如FFT)具有数据量大,乘法运算居多的特点。此弊端只能通过减少采样点数或外扩运算芯片来解决,前者会降低测量精度,而后者会增加外围硬件设计的复杂程度。 方案三:C8051F360单片机结合FPGA及锁相环模块实现。利用锁相环模块对输入信号频率进行跟踪,能够实现对信号每个周期采集相同点的数据,保证了单片机进行频谱分析(FFT运算)时,数据的正确性。利用FPGA设计两个双口RAM,一个用于存储采集的外部信号数据,另一个用于存储单片机进行FFT运算过程中的大量数据。此方案硬件电路十分简单,且能够按需求方便地改变采集的数据量大小,提高运算结果的精度。且FPGA的高精度晶振能保证AD均匀采样,为计算精度提供保障。 综上所述,本设计选用方案三。系统原理框图见图1-1; C8051F360单片机Cyclone II FPGA 高速ADC信号调理 LCD模块 键盘模块 模拟 信号 锁相环 模块 时钟信号 高速DAC信号调理信号 回放图1-1-1 系统原理框图

等间距采样的高速数据采集系统设计 郝亮,孟立凡,刘灿,高建中 (中北大学仪器科学与动态测试教育部重点实验室,太原030051) 摘要:简单介绍通过对窄脉冲等间距采样来测试电缆故障的基本原理,分析其脉冲的特点和处理要求;采用F PGA和MSP430F149作为主控芯片,设计了单路多次低速数据采集系统;利用Quartus II软件编写主控程序,并在Modelsim下进行仿真验证。实验结果表明,该系统方案切实可行,可有效解决电缆故障测距过程中的高精度数据采集问题。 关键词:等间距采样;数据采集;MSP430F149;F PGA 中图分类号:TN98文献标识码:B H igh2spe ed Data Acquisition System Based on Equidistance Sampling Hao Liang,Meng Lifan,Liu Can,Gao Jianzhong (Inst ruments Science and Dynamic Measurement Ministry of Education Key Laboratory, North University of China,T aiyuan030051,China) A bstract:T he basic principle of testing cable faults wit h narrow2pulse equidistance sampling is described.Pulse characteristics and pro2 cessing requirements are analyzed.The single2line repeated low2speed dat a acquisition system is designed with FPGA and MSP430F149 as main control chips.Main control procedures are programmed in Quartus II and simulated in Modelsim.Experimental result shows that t he system is practical,and the problem of high2precision data acquisition in the process of cable fault location is resolved effectively. K ey words:equidist ance sampling;data acquisit ion;MSP430F149;FPGA 引言 电缆故障是通信行业中的常见故障,而电缆测距是排除故障的前提条件。准确的电缆测距可以缩短发现故障点的时间,利于快速排除故障,减少损失。窄脉冲时域反射仪利用时域反射技术来测定电缆断点位置,可以同时检测出同轴传输系统中多个不连续点的位置、性质和大小。窄脉冲信号持续的时间非常短暂,为了能够有效地捕捉到窄脉冲信号,对A/D采样率和处理器速率提出了较高的要求,传统的数据采集已经不能满足系统设计需求。本文介绍的单路多次低速数据采集方案硬件结构简单,成本低,能够满足系统设计要求。 1系统设计理论依据 根据电磁波理论,电缆即传输线。假若在电缆的一端发送一探测脉冲,它就会沿着电缆进行传输,当电缆线路发生障碍时会造成阻抗不匹配,电磁波会在障碍点产生反射。在发射端,由测量仪器将发送脉冲和反射脉冲波形记录下来。实际测试中,具体障碍的波形有所差异:断线(开路)障碍时,反射脉冲与发射脉冲极性相同;而短路、混线障碍时,反射脉冲与发射脉冲极性相反。波形如图1所示。 图1发射脉冲与反射脉冲波形 设从发射窄脉冲开始到接收到反射脉冲波的时间为$t,则: l=v#$t 2 其中,v为脉冲波在电缆中的传输速度;l为电缆故障点与脉冲波送入端的距离。 由以上分析可知,在同一个固定障碍的线路上多次送入同一脉冲电压,其反射脉冲将同样地在同一位置多次出现。 要实现对反射窄脉冲的捕获和1m的测距分辨率(在波速为200m/L s的情况下),则$t= 2l v =2@1 200 =0.01L s =10ns。即要求抽样的时间分辨率为10ns,对应的数据采集系统频率高达100MHz。同时,最大测量范围是2km 时,要求发射脉冲的重复周期T= 2l v =2@2000 200 =20L s。

(此文档为word格式,下载后您可任意编辑修改!) 数据采集与传输系统 摘要 该数据采集与传输系统以89C51及89C2051为核心,由数据采集模块、调制解调模块、模拟信道、测试码发生器、噪声模拟器、结果显示模块等构成。在本方案中仅使用通用元器件就较好的实现了题目要求的各项指标。其中调制解调模块、噪声模拟器分别采用单片机和可编程逻辑器件实现。本数据采集与传输系统既可对8路数据进行轮检,也可设置为对一路数据单独监控。本系统硬件设计应用了EDA 工具,软件设计采用了模块化的编程方法。传输码元速率为16kHz~48kHz的二进制数据流。另外,还使用了“1”:“01”、“0”:“10”的Manchester编码方法使数据流的数据位减少,从而提高传输速率。

一、方案设计与论证 首先,我们分析一下信道与信噪比情况。本题中码元传输速率为16k波特,而信号被限定在30k~50kHz的范围内,属于典型的窄带高速率数字通信。而信噪比情况相对较好。这是因为信号带宽仅为20kHz,而噪声近似为0~43kHz()的窄带白噪声,这样即使在信号和噪声幅度比值为1:1的情况下,带内的噪声功率仍然比较小,所以系统具有较高的信噪比。 方案一: 常用的数字调制系统有:ASK、FSK、PSK等。其中FSK具有较强的抗干扰能力,但其要求的的带宽最宽,频带利用率最低,所以首先排除。ASK理论上虽然可行,但在本题目中,由于一个码元内只包括约两个周期的载波,所以采用包络检波法难以解调,也不可行。另外,对于本题目,还可以考虑采用基带编码的方法进行传输,如HDB3码,但这种编码方法其抗干扰能力较差,因此也不太适合。 方案二: PSK调制方式具有较强的抗干扰能力,同时其调制带宽相对也比较窄,因此我们考虑采用这种调制方式。为了简化系统,在实际实现时,我们采用了方波作为载波的PSK调制方式。当要求的数据传输速率较低(≤24kbps)时,对原始数据处理的方法如下:

审计数据采集与分析技术 计算机审计的含义 ?计算机审计有3层含义: –面向数据的审计 –面向现行信息系统的审计 –对信息系统生命周期的审计 面向数据的计算机审计流程 ?审前调查:电子数据的组织、处理和存储 ?数据采集:审计接口、数据库访问技术、数据采集技术 ?数据清理、转换、验证、建立中间表 ?数据分析:数据分析技术、SQL、审计软件 ?审计取证 一、审前调查及电子数据的组织、处理和存储 1.审前调查的内容和方法 ?对组织结构调查 ?对计算机信息系统的调查 ?提出数据需求 2.电子数据的组织、处理和存储 电子数据处理的特点 ?存储介质改变 ?基于一定的数据处理平台,有一定的数据模型 ?数据表示编码化(各种编码) ?带来系统控制和数据安全性的新问题 ?审计线索改变 如何表示数据 ?数据类型与数据取值 –数据类型决定了取值范围与运算范围 ?数据模型 –数据模型是对现实世界数据特征的抽象 –它提供模型化数据和信息的工具

数据模型的2个层次 ? ?概念模型 –E-R模型的要素 ?实体:客观存在并可以相互区分的事物,用方框表示 ?属性:实体的特征或性质,用椭圆表示 ?联系:实体之间的联系,用菱形表示 ?数据模型 –关系模型 –层次模型 –网状模型 数据模型的3个要素 ?数据结构 –描述模型的静态特征 –是刻画数据模型最重要的方面 ?数据操作 –描述模型的动态特性 ?数据检索 ?数据更新(增加、删除、修改) ?约束条件 –一组完整性规则的集合 ?实体完整性 ?引用(参照)完整性 ?用户定义的完整性 关系模型 ?关系模型是目前最常用的一种数据模型 ?关系数据库采用关系模型作为数据的组织方式 ?关系模型建立在严格的关系代数基础之上 ?关系模型概念单一,用关系表示实体以及实体之间的联系?关系数据库的标准语言SQL是一种非过程化语言,使用方便关系模型的数据结构 ?关系 –一张二维表,每一列都不可再分 –表中的行、列次序并不重要 ?元组 –二维表中的每一行,相当于一条记录 ?属性 –二维表中的每一列,属性有名称与类型。 –属性不可再分,不允许重复 ?主键 –由表中的属性或属性组组成,用于唯一确定一条记录?域

5 Gsps 高速数据采集系统的设计与实现 摘要:以某高速实时频谱仪为应用背景,论述了5 Gsps 采样率的高速数据采集系统的构成和设计要点,着重分析了采集系统的关键部分高速ADC(analog to digital,模数转换器)的设计、系统采样时钟设计、模数混合信号完整性设计、电磁兼容性设计和基于总线和接口标准(PCI Express)的数据传输和处理软件设计。在实现了系统硬件的基础上,采用Xilinx 公司ISE 软件的在线逻辑分析仪(ChipScope Pro)测试了ADC 和采样时钟的性能,实测表明整体指标达到设计要求。给出上位机对采集数据进行处理的结果,表明系统实现了数据的实时采集 存储功能。关键词:高速数据采集;高速ADC;FPGA;PCI Express 高速实时频谱仪是对实时采集的数据进行频谱分析,要达到这样的目的,对数据采集系 统的采样精度、采样率和存储量等指标提出了更高的要求。而在高速数据采集 系统中,ADC 在很大程度上决定了系统的整体性能,而它们的性能又受到时钟质量的影响。为满足系统对高速ADC 采样精度、采样率的要求,本设计中提 出一种新的解决方案,采用型号为EV8AQ160 的高速ADC 对数据进行采样;考虑到ADC 对高质量、低抖动、低相位噪声的采样时钟的要求,采用AD9520 为5 Gsps 数据采集系统提供采样时钟。为保证系统的稳定性,对模数混合信号完整性和电磁兼容性进行了分析。对ADC 和时钟性能进行测试,并给出上位 机数据显示结果,实测表明该系统实现了数据的高速采集、存储和实时后处理。 1 系统的构成高速数据采集系统主要包括模拟信号调理电路、高速ADC、高速时钟电路、大容量数据缓存、系统时序及控制逻辑电路和计算机接口电路等。图1 所示为5 Gsps 高速数据采集系统的原理框图。所用ADC 型号为EV8AQ160,8 bit 采样精度,内部集成4 路ADC,最高采样率达5 Gsps,可以工作在多种模式下。通过对ADC 工作模式进行配置,ADC 既可以工作在采样

第5节 电子综合设计范例4----数据采集与传输系统 一、设计任务与要求 1、设计任务 设计制作一个用于8路模拟信号采集与单向传输系统。系统方框图参见下图。 2、设计要求 求 8路0-5V 分别可调的直流电压。系统具有在发送端设定8路顺序循环采集与器。 Hz 的带通滤波器(带外衰减优于35 dB/十倍频程)作为模拟信道。 压值。 个用伪随机码形成的噪声模拟发生器,伪随机码时钟频率为96 kHz ,周期为在解调器输入他(如自制用来定量测量系统误码的简易误码率测试仪,其方框图见下图,等等)。 ⑴ 基本要 ① 被测电压为指定某一路采集的功能。 ② 采用8位A/D 变换 ③ 采用3 dB 带宽为30~50 k ④ 调制器输出的信号峰-峰值Vsp -p 为0~1 V 可变,码元速率16 kbps ;制作一个时钟频率可变的测试码发生器(如0101…码等),用于测试传输速率。 ⑤ 在接收端具有显示功能,要求显示被测路数和被测电 ⑵ 发挥部分 ① 设计制作一127位码元,生成多项式采f(x)=x 7+x 3+1。其输出峰-峰值V np-p 为0~l v 连续可调。 ② 设计一个加法电路,将调制器输出V sp-p 与噪声电压V np-p 相加送入模拟信道。 端测量信号与噪声峰-峰值之比(V sp-p /V np-p ),当其比值分别为1、3、5时,进行误码测试。测试方法:在8路顺序循环采集模式下,监视某一路的显示,检查接收数据的误码情况,监视时间为l min 。 ③ 在(V sp-p /V np-p )=3时,尽量提高传输速率,用上述第(2)项的测试方法,检查接收数据的误码情况。 ④ 其