2x20W Stereo / 1x40W Mono Digital Audio Amplifier With 24 Bands EQ Functions

Features

16/18/20/24-bits input with I2S, Left-alignment and Right-alignment data format

PSNR & DR(A-weighting)

Loudspeaker: 99dB (PSNR), 110dB (DR) @24V Multiple sampling frequencies (Fs)

32kHz / 44.1kHz / 48kHz and

64kHz / 88.2kHz / 96kHz and

128kHz / 176.4kHz / 192kHz

I2C control interface

Channel mixing

Volume control (+12dB ~ -103dB, 0.125dB/step) Power clipping function

DRC and DTC function

24 bands parametric speaker EQ

DRC and post scale boost

Check-sum coefficient protection

Noise gate function

Pop noise less muting (Quick Mute/Quick Start) Sleep function

X3 over sampling for 32kHz FS

AM interference frequency switching

Level meter

Post-scale and DRC offset volume support

Over current protection function (OCP)

Over temperature protection function (OTP)

Under voltage lockout (UVLO)

Over voltage protection function (OVP)

DC detection function (DCDET)

Clock detection function (CKDET)

Lead-free LQFP48

Applications

TV audio

Boom-box, CD and DVD receiver, docking system Powered speaker

Wireless audio Description

AD82589 is an integrated audio system solution, embedding digital audio processing power stage amplifier.

AD82589 has a programmable slew-rate controlled output buffer, which drives one (mono) or two (stereo) speakers directly. In addition, it is insusceptible to supply voltage fluctuation due to the close-loop design.

AD82589 can provide advanced audio processing capabilities, such as volume control, 24 bands EQ, audio mixing and Dynamic Range Control (DRC). These functions are fully programmable via a simple I2C interface.

Robust protection circuits are provided to protect AD82589 from damage due to accidental erroneous operation. AD82589, being a digital circuit design, is more tolerant to noise and PVT (Process, Voltage, and Temperature) variation than the analog Class-AB or Class-D audio amplifier counterpart implemented by analog circuit design. Furthermore, AD82589 is pop free during instantaneous power switching because of its built-in, robust anti-pop circuit.

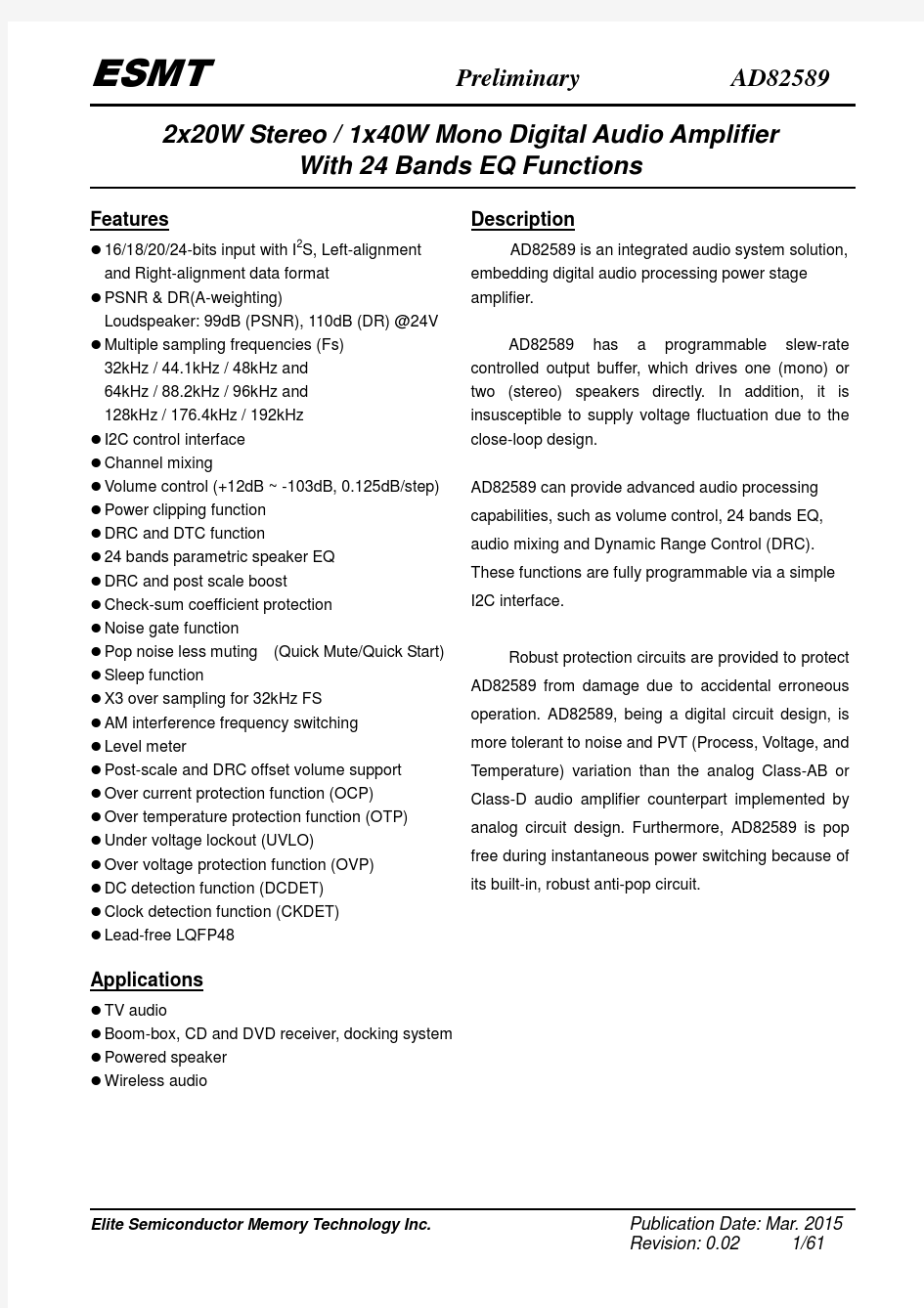

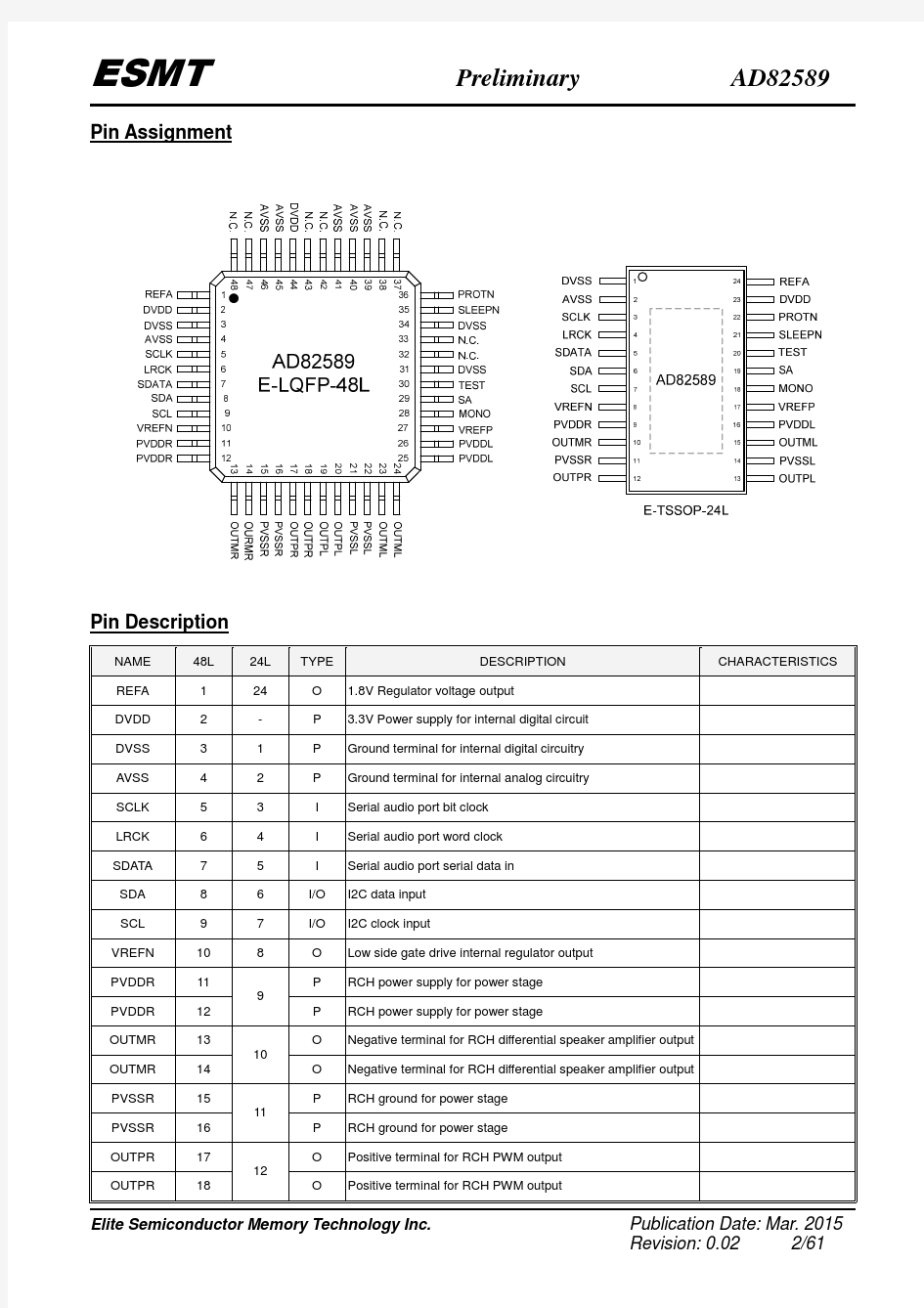

Pin Assignment

Pin Description

Functional Block Diagram

REFA SCLK SDATA LRCLK

SDA SLEEPN

SCL DVSS

MONO

DVDD

Ordering Information

Product ID Package Packing / MPQ Comments

AD82589-LG48NAY E-LQFP-48L

7X7

250Units / Tube

2.5K Units / Box(10 Tray)

Green

AD82589-QG24NAT E-TSSOP 24L

62 Units / Tube

100 Tubes / Small Box

Green

Available Package

Package Type Device No. θja(℃/W) θjt (℃/W)Ψjt (℃/W)

Exposed Thermal Pad E-LQFP-48L

7X7

AD82589 22.9 34.9 1.64 Yes (Note1) E-TSSOP 24L AD82589 26.8 27.1 1.83 Yes (Note1)

Note 1.1: The thermal pad is located at the bottom of the package. To optimize thermal performance, soldering the thermal pad to the PCB’s ground plane is suggested.

Note 1.2: θja is measured on a room temperature (T A=25℃), natural convection environment test board, which is constructed with a thermally efficient, 4-layers PCB (2S2P). The measurement is tested using the

JEDEC51-5 thermal measurement standard.

Note 1.3: θjt represents the heat resistance for the heat flow between the chip and the package’s top surface.

(The junction-to-top thermal resistance is obtained by simulating a cold plate test on the top of the

package).

Note 1.4: Ψjt represents the heat resistance for the heat flow between the chip and the exposed pad center.

(The junction-to-top characterization parameter is extracted from the simulation data to

obtainθja).

Marking Information

AD82589

Line 1 : LOGO

Line 2 : Product no.

Line 3 : Tracking Code

Line 4 : Date Code

PIN1 DOT

Absolute Maximum Ratings

Stresses beyond those listed under absolute maximum ratings (<100msec) may cause permanent damage to the device.

SYMBOL PARAMETER TEST CONDITIONS MIN MAX UNIT PVDD Supply for driver stage PVDDR, PVDDL -0.3 30 V DVDD Supply for Low voltage DVDD -0.3 3.6 V HVDD Supply for line driver HVDD -0.3 3.6 V

SCLK, LRCLK, SDATA,SCL,

V sI Speaker interface pin voltage

-0.3 3.8 V

SDA,SA,TEST,MONO, and SLEEPN

Headphone interface pin

V HI

RINN,LINN -0.3 3.6 V voltage

PROTN terminal voltage

V PROTN

PROTN -0.3 3.8 V range

T A Operating free-air temperature range -40 85 o C T J Operating junction temperature range -40 150 o C T stg Storage temperature range -65 150 o C R L Minimum Load Resistance Stereo (BTL) 3.6 ?

Recommended Operating Conditions

Parameter Symbol Min. Typ. Max. Unit Power supply voltage for driver stage PVDD 5 - 26.4 V Power supply voltage for low voltage DVDD 3.0 3.6 V Digital terminals input voltage V IN 2.2 3.3 3.6 V Operating Ambient Temperature T a0 - 70 °C Stereo Speaker Impedance (Note 2) R L 4 8 - ?Note 2: Loudspeaker over-current protection is only effective when loudspeaker drivers are properly connected with external LC filters. Please refer to the application circuit example for recommended LC filter configuration.

General Electrical Characteristics

PVDD=5V to 24V, T A=25°C, unless otherwise specified.

Item Symbol Condition Min. Typ. Max. Unit Startup Threshold Voltage V HUVLH– – 4.1 – V PVDD pin Shutdown Threshold

Voltage

V HUVLL– – 4 – V Input Voltage H level V IH– 2.0 – – V

Input Voltage L level V IL– – – 0.8 V Digital pins*1)

Input Impedance R IN_D– 3.3 – – M?

Input Voltage H level V IH– 2.2 – – V

Input Voltage L level V IL– – – 0.5 V SLEEPN pin

Input Impedance R IN_D– 3.3 – – M?PROTN pin Output Voltage V OL I OL=2mA – – 0.4 V REFA pin Output Voltage V REFA– – 1.8 – V VREFN pin Output Voltage V REFN V DDP =24V 5.5 V VREFP pin Output Voltage V REFP V DDP =24V 18.5 V

at idling state I DDPP V DDP =24V,

No load

– 39 – mA

at power-down state (SLEEPN=”L”) I DDPS

V DDP =24V,

No load, T A = 25 oC

– 20 – μA

Current drawn from PVDD

at mute state

(AMP_HARD_MUTE=1) I DDPM

V DDP =24V,

No load

– 30 – mA

Application Circuit Example Application circuit for Stereo mode

Rch

r r o r (o p e n d r a i n )

3.3V input

Lch

Electrical Characteristics and Specifications of Loudspeaker Driver

PVDD=24V, T A=25°C,R L=8?, unless otherwise specified.

Item Symbol Condition Min. Typ. Max. Unit

PVDD=24V, R L=8?,

THD+N=0.2%

– 20 – W

PVDD=24V, R L=6?, THD+N=10% – 15 – W

Stereo

PVDD=12V, R L=4?THD+N=10% – 10 – W

Maximum Instantaneous

Output

Mono Po

PVDD=24V, R L=4?,

THD+N=10%

– 40 – W

Total Harmonic Distortion Stereo,

Mono

THD+N R L=8?, Po=7.5W – 0.1 – %

Residual Noise Stereo,

Mono

Vn

R L=8?,

A-Weighted Filter

– 150 – μVrms

S/N Ratio Stereo,

Mono

SNR

R L=8?,

A-Weighted Filter

– 94 – dB

Channel Separation (L vs R) CS R L=8?, 1kHz – 90 – dB

PSRR Stereo,

Mono

PSRR

PVDD applied,

Vripple=200mVpp, f=1kHz

– 70 – dB

PVDD=24V, R L=8?,

Po=10W

– 88 – % Stereo

PVDD=12V, R L=4?,

Po=10W

– 80 – %

PVDD=24V, R L=8?,

Po=10W

– 88 – %

Maximum Efficiency

Mono η

PVDD=12V, R L=4?,

Po=10W

– 80 – %

Output Offset Voltage Stereo,

Mono

Vo – – 3 9 mV

20Hz –1 0 1 dB

Frequency Characteristics Stereo,

Mono

f

20kHz –3 0 1 dB

Interface configuration

I2S

Left-Alignment

Right-Alignment

Timing Relationship (Using I2S format as an example)

Symbol Parameter Min Typ Max Units t LR LRCIN Period (1/F S) 5.2 31.25 μs

t BL BCLK Rising Edge to LRCIN Edge 50 ns

t LB LRCIN Edge to BCLK Rising Edge 50 ns

t BCC BCLK Period (1/64F S) 81.38 488.3 ns

t BCH BCLK Pulse Width High 40.69 244 ns

t BCL BCLK Pulse Width Low 40.69 244 ns

t DS SDATA Set-Up Time ns

t DH SDATA Hold Time ns

I 2C Timing

t f

t HD;STA

t LOW

t r

t HD;DAT t SU;DAT

t f

t HIGH

t SU;STA

t HD;STA

t SU;STO

t r

t BUF

S

Sr

P

S

Standard Mode Fast Mode Parameter

Symbol

MIN. MAX. MIN. MAX. Unit SCL clock frequency

f SCL 0 100 0 400 kHz Hold time for repeated START condition t HD,STA 4.0 --- 0.6 --- μs LOW period of the SCL clock t LOW 4.7 --- 1.3 --- μs HIGH period of the SCL clock

t HIGH 4.0 --- 0.6 --- μs Setup time for repeated START condition t SU;STA 4.7 --- 0.6 --- μs Hold time for I 2

C bus data t HD;DAT 0 3.45 0 0.9 μs Setup time for I 2C bus data

t SU;DAT 250 --- 100 --- Ns Rise time of both SDA and SCL signals t r --- 1000 20+0.1Cb 300 Ns Fall time of both SDA and SCL signals t f --- 300 20+0.1Cb 300 Ns Setup time for STOP condition

t SU;STO 4.0 --- 0.6 --- μs Bus free time between STOP and the next START condition

t BUF 4.7 --- 1.3 --- μs Capacitive load for each bus line C b 400 400 pF Noise margin at the LOW level for each connected device (including hysteresis) V nL 0.1V DD

---

0.1V DD

---

V

Noise margin at the HIGH level for each connected device (including hysteresis)

V nH

0.2V DD --- 0.2V DD --- V

I 2C-Bus Transfer Protocol Introduction

AD82589 employs I 2

C-bus transfer protocol. Two wires, serial data and serial clock carry information between the devices connected to the bus. Each device is recognized by a unique 7-bit address and can operate as either a transmitter or a receiver. The master device initiates a data transfer and provides the serial clock on the bus. AD82589 is always an I 2

C slave device.

Protocol

START and STOP condition

START is identified by a high to low transition of the SDA signal.. A START condition must precede any command for data transfer. A STOP is identified by a low to high transition of the SDA signal. A STOP condition terminates communication between AD87588 and the master device on the bus. In both START and STOP , the SCL is stable in the high state.

Data validity

The SDA signal must be stable during the high period of the clock. The high or low change of SDA only occurs when SCL signal is low. AD82589 samples the SDA signal at the rising edge of SCL signal.

Device addressing

The master generates 7-bit address to recognize slave devices. When AD82589 receives 7-bit address matched with 0110x01 (where x can be selected by external SA pins), AD82589 will acknowledge at the 9th

bit (the 8th

bit is for R/W bit). The bytes following the device identification address are for AD82589 internal sub-addresses.

Data transferring

Each byte of SDA signaling must consist of 8 consecutive bits, and the byte is followed by an acknowledge bit. Data is transferred with MSB first, as shown in the figure below. In both write and read operations, AD82589 supports both single-byte and multi-byte transfers. Refer to the figure below for detailed data-transferring protocol.

Operation Descriptions

The description below explains AD82589 functions and operations

Digital Amplifier Modulation Method

AD82589 has a built-in stereo digital class D amplifier with digital signal processing capability. After the digital input audio signal is processed, the signal is modulated and generates Pulse Width Modulated (PWM) outputs. The pulse frequency that appears between OUTP* and OUTM* pins is called “Carrier Clock Frequency.” Figure 1 below shows the PWM output waveforms for an audio sine wave about the characteristics of modulation method. As shown in B of the figure, the frequency that appears between GND and OUTP* pins and between GND and OUTM* pins at no-signal input becomes the half of a carrier clock frequency. As shown in A, C of the figure, when the output power increases, one side stops its switching and the other serves as a carrier clock frequency.

Modulation Method with AD82589

OUTP*

OUTM*

A

OUTP*

OUTM*

B

OUTP*

OUTM*

C t

Carrier Clock Frequency

1

t

t

Quick Mute/Quick Start Function

Quick Mute/Quick Start function reduces pop sound significantly by varying the output envelope at a slower rate when AMP_HARD_MUTE register is turned ON or OFF.

AMP_HARD_MUTE register Mode

L Normal Operation State

H Digital Amplifier Mute State

By setting AMP_HARD_MUTE register to “H” via I2C, AD82589 performs Quick Mute operation (Decreasing the volume linearly by taking 512×1/fs), (16×96) / (carrier clock frequency)[s] later, it sets the digital amplifier output to WL (Weak Low: a state grounded through a high-value resistance), resulting in Mute state (Output Disabled).

By setting AMP_HARD_MUTE register to “L” via I2C, AD82589 moves from the mute state to normal operation state while turned down volume. Afterwards, the quick start operation (where the volume is increased linearly over 256×1/fs) is executed. Mute recovery time from Mute state is t mrcv(Typ.). If the mute state is cancelled during the Quick Mute Sequence, Quick Start Sequence will start after the quick mute sequence.

When the voltage at PVDD pin becomes lower than PVDD pin Shutdown Threshold Voltage (V HUVLL) in the mute state, for shutting down the system safely, the amplifier output is set to WL (Weak Low : a state grounded through a high-value resistance) after outputting a low signal for a given period of time.

Quick Mute and Quick Start

Sleep Function

In Sleep state, the device are stopped and consumption current becomes the minimum (IDDPS). REFA and VREFN pins outputs are pulled down, and VREFP pin is pulled high.

SLEEPN pin Mode

L Sleep State

H Normal Operation State

By setting SLEEPN pin to “L”, AD82589 performs Quick Mute operation (Decreasing the volume linearly by taking 1024×1/fs), (16×96) / (carrier clock frequency) [s] later, it sets the digital amplifier output to WL(Weak Low: a state grounded through a high-value resistance).

AD82589 goes to Sleep state when max.160ms has passed after setting SLEEPN pin to "L."

When going to sleep mode while some protection state is being activated, this protection mode is cancelled and PROTN pin output goes to Hi-Z state.

With PVDD pin output being higher than the threshold voltage to cancel the low-voltage malfunction preventing function, when changing the state of SLEEPN pin from “L” to “H,” the digital amplifier terminates the sleep state, simultaneously starts the Startup Sequence and does the quick start (raises the volume level linearly by taking 256×1/fs) to activate the oscillation after max.300ms.

Sleep Function

REFA Voltage Output Function

The voltage inputted from a DVDD power supply pin is supplied to a regulator. REFA pin outputs the voltage (REFA) regulated from the voltage coming from DVDD pin. For its stabilization, connect a bypass capacitor of 1.0μF to 4.7μF between REFA and AVSS pins (0.8μF or more should be secured including its variation and temperature change.). REFA pin must not be connected to other devices.

VREFN Voltage Output Function

The voltage inputted from a PVDD power supply pin is supplied to a regulator. VREFN pin outputs the voltage (VREFN) regulated from the voltage coming from PVDD pin. For its stabilization, connect a bypass capacitor of 1.0μF to 4.7μF between VREFN and VSS pins (0.8μF or more should be secured including its variation and temperature change.). VREFN pin must not be connected to other devices.

VREFP Voltage Output Function

The voltage inputted from a PVDD power supply pin is supplied to a regulator. VREFP pin outputs the voltage (VREFP) regulated from the voltage coming from PVDD pin. For its stabilization, connect a bypass capacitor of 1.0μF to 4.7μF between VREFP and PVDDL (PVDDR) pins (0.8μF or more should be secured including its variation and temperature change.). VREFP pin must not be connected to other devices

Digital Amplifier Startup/Shutdown Procedure

It is recommended to use the following sequences as digital amplifier start and shutdown procedure. With different sequence, unusual sound or pop noise may occur.

Recommended Digital Amplifier Startup Sequence

1. Supply the power to PVDD pin.

2. When the supply voltage reaches at the recommended voltage range, input clocks to SCLK, and LRCLK

pins.

3. Change the logical state of SLEEPN pin from “L” to “H”.

Recommended Digital Amplifier Shutdown Sequence

1. Change the logical state of SLEEPN pin from “H” to “L”.

2. After 160ms or more, stop input the signal to the input pins and shut down the power to PVDD pin.

* As long as SLEEPN pin was changed from “H” to “L” and Quick Mute {1024×1/96k + (16×96) /

(Carrier Clock Frequency)}[s]” has elapsed, unusual sound or pop noise is not generated even if the power is shut down.

Startup and Shutdown sequence

PVDD

LC Filter

On the other hand, when using a LC filter, the output circuit as shown in Figure 10, 11 should be used with the constants listed in Table 8. The use of these constants enables the filter to be a low-pass filter with its cut-off frequency being 50kHz or so and Q being 0.6 or so. When disconnecting a speaker, turn off the power in advance. When operating the device without a speaker, consumption current may increase or over current detection circuit may work due to the resonance in LC filter. When removing a speaker during operation, SLEEPN or MUTEN pin should be set to “L” or PVDD should be shut down.

LC Filter Circuit (Stereo) LC Filter Circuit (Mono)

R L

R L

R L L1 C1 C2 fc fc (to GND) Q 4? 10μH 0.33μF 0.22μF 53.7kHz 107kHz 0.59 6? 15μH 0.22μF 0.1μF 55.9kHz 130kHz 0.57 8? 22μH 0.22μF 0.1μF 46.2kHz 107kHz 0.63 16?

47μH

0.1μF

0.047μF

46.7kHz

107kHz

0.58

When using AD82589 with a speaker connected directly without connecting LC filters, or when using it with EMI countermeasure components, such as ferrite beads etc., in addition to a speaker, a speaker with an inductance higher than 20μH should be used. Otherwise, loss of the speaker and AD82589 may increase.

)

2(21

211C C L f C +××=

π2

21

2

1L

R L C C Q ×+×=

2

121)(C L toGND f C π=

Protection function

AD82589 has over current protection, over temperature protection, under voltage lock out function, DC detection, clock detection and over voltage lock out functions.

In SLEEPN=Low, UVLO state and early stage of start up sequence, all protection function is disabled.

Protection functions

Protection Function PROTN

Pin

Output

Digital

Amplifier

Output

Automatic Recovery

Detect

Seq. (IS)

Over current Protection L WL*3)Applicable*1)

100ms H/L

WL

Over Temperature Protection L*2)WL*3)

Not Applicable

(Recover when temperature go down)

100ms L

WL

Under Voltage

Lock Out (PVDD,DVDD pin) H WL*3)

Not Applicable

(Recover when pin voltage go up)

100ms L

WL

DC Detection L WL*3)Applicable*1)100ms L WL

Clock Detection (SCLK,PLLCLK) H WL*3)

Not Applicable

(Recover when clock frequency go up)

1msec L

WL

DAIF error H normal Not Applicable

(Recover when keep 64fs)

maintain

previous cycle

data

Over Voltage Protection L WL

Not Applicable

(Recover when voltage go down)

100ms L

WL

Note:

*1): Automatic recovery is performed 2.7 to 5.4 seconds (at Fs=48kHz) after a protecting function is activated, and then PROTN pin goes to “H.”

*2): When an over temperature condition is cleared, PROTN is returned to “H.”

*3): To shutting down the system safely, the amplifier output is set to WL after outputting a low or high signal for a given period of time.

PROTN pin has an open-drain output. Use a resistor of 47k? to pull up the pin with respect to an external power supply source lower than 3.3V. In order to prevent the current in excess of 2mA from being flowed into PROTN pin being in L state. If multiple AD82589s are used, all the PROTNs can be tied together for wired OR connection. PROTN pin must not connect to pins of AD82589. PROTN pin should be left open when not used.

Over current protection

This function, detecting an over current condition at the digital amplifier output, enables the over-current protection state, in which the following short-circuiting conditions are detected: VSS short (Ground or any other lower-potential point), PVDD short (supply voltage or a higher-potential point), or short-circuiting between ±output pins. The detection current, for pin-to-pin short-circuiting, is 7A (typ., PVDD=24V). In this state, digital amplifier outputs are forced to “WL” state (Weak Low: a state grounded through a high-value resistance) and PROTN pin goes to “L”. The automatic recovery operation is performed 2.7 to 5.4 seconds (at fs=48kHz) after the protection state is activated. When detected eight times in all, the protection state is held without being cancelled. The held protection state can be cancelled by setting SLEEPN pin to “L” temporarily or shutting down the power. This protection state is provided not for guarantee of IC protection in case of exceeding the maximum rating (speaker impedance) but for safety in case of unusual conditions.

Over Voltage Protection Function (OVP)

This function, detecting an unusual condition where the voltage at PVDD pin becomes higher than “PVDD pin Shutdown Threshold Voltage”, and prevent malfunction etc. In this high-voltage protection state, digital amplifier outputs become WL state (Weak Low: a state grounded through a high-value resistance). When voltages at PVDD pin become lower than high-voltage cancel threshold voltage, the high-voltage protection state is cancelled and the normal operation starts after max. 300ms. This function does not guarantee all operations even if PVDD pin voltage is over the startup threshold voltage. Be sure to use this IC within the recommended supply voltage.

PVDD Under Voltage Lock Out Function (UVLO)

This function, detecting an unusual condition where the voltage at PVDD pin becomes lower than “PVDD pin Shutdown Threshold Voltage”, and prevent malfunction etc. In this low-voltage protection state, digital amplifier outputs become WL state (Weak Low: a state grounded through a high-value resistance). When voltages at PVDD pin become higher than low-voltage cancel threshold voltage (VHUVLH), the low-voltage protection state is cancelled and the normal operation starts after max. 300ms. This function does not guarantee all operations even if PVDD pin voltage is over the startup threshold voltage VHUVLH. Be sure to use this IC within the recommended supply voltage.

0-500mm高度游标卡尺不确定度评定

0-500mm高度游标卡尺不确定度评定 1 目的 保证检测数据的准确可靠,确保正确的量值传递。 2 适用范围 适用于本中心试验室0-500mm高度游标卡尺检测结果扩展不确定度的计算。 3 不确定度的评定步骤 3.1测量方法 用0-500mm高度游标卡尺直接测量被测样品。 3.2数学模型 Lx = L 式中: Lx—被检测样品的数值mm L—游标卡尺显示数值mm 3.3标准不确定度A类评定 选取六个不同尺寸的样品分别进行6次重复测量,并用贝塞尔公式计算实验标准偏差。 选取一个样品长度为80mm测试数据见下表: 选取一个样品长度为161.2mm测试数据见下表:

选取一个样品长度为239.9mm测试数据见下表: 选取一个样品长度为321mm测试数据见下表: 选取一个样品长度为400.3mm测试数据见下表:

选取一个样品长度为491.2mm 测试数据见下表: 实际检测中只进行一次试验,则测量重复性导致的测量不确定度为: 样品长度为80mm 时: u 1=s=0.011mm 样品长度为161.2mm 时:u 2=s=0.009mm 样品长度为239.9 mm 时:u 3=s=0.011mm 样品长度为321 mm 时: u 4=s=0.011mm 样品长度为400.3 mm 时:u 5=s=0.017mm 样品长度为491.2 mm 时:u 6=s=0.02mm 3.4 标准不确定度B 类评定 高度游标卡尺示值不确定度为: 由校准证书知道, u 95=0.02mm ,自由度16=eff ν则: 12.2)16((95.0)===t v t k eff p

通用卡尺示值误差测量结果的不确定度评定 1.概述: 1.1测量依据:JJG30—2012《通用卡尺检定规程》。 1.2环境条件:温度22℃±5℃,湿度≤60%。 1.3测量标准:3级量块或5等量块。 1.4被测对象的测量范围、分度值(分辨力)、示值误差如下: 1.5测量方法 对于测量范围小于300mm的卡尺,测量点的分布不少于均匀分布的3点,对于测量范围大于500mm卡尺,测量点的分布不少于均匀分布的6点。被测卡尺各点示值误差以该点读数值(示值)与量块尺寸(测量标准)之差确定。 1.6测量模型 对分度值为0.02,测量范围为(0~200)mm游标卡尺191.8mm点示值误差校准的测量不确定进行评估。 2.数学模型 通用卡尺示值误差 e=L d - L s +L d·αd·△t d- L s·αs·△t s (1)式中:e—卡尺的示值误差; L d—卡尺的误差值; L s—量块的示值。 考虑到温度偏离20℃时,线膨胀系数及温度差的影响,上述公式可用以下形式表示 e=L d - L s +L d·αd·△t d- L s·αs·△t s (2)式中:e—卡尺的示值误差;

L d —卡尺的读数值(20℃条件下); L s —量块的示值(20℃条件下); αd 、αs —卡尺和量块的线膨胀系数; △t d 、△t s —卡尺和量块的偏离标准温度20℃的值。 3.方差和灵敏系数 由于△t d 和△t s 基本是采用同一支卡尺测量而具有相关性,其数学处理过程比较复杂,为了简化数学处理过程,需要通过如下方法将相关转化为不相关。 令δα=αd -αs δt=△t d -△t s 取L≈L d ≈L s α=αd =αs △t =△t d =△t s 得如下示值误差的计算公式: e =L d - L s +L·δα·△t - L·α·δt (3) 由公式(3)可以看出,各变量之间彼此不相关,由公式)()( 22 2 i i c x u f u ???=χ得: u c 2 =u 2(e )=c 12·u 12+ c 22·u 22+ c 32·u 32 +c 42·u 42 (4) 式中:11=??= d L e c 12-=??=s L e c t L e c ??=??= δα3 αδ?=??=L t e c 4 公式(4) 中u 1,u 2,u 3,u 4分别表示L d , L s ,δα,δt 的标准不确定度。 4.标准不确定度评定 4.1游标卡尺读数的对线误差估算的标准不确定度分量u 1 分度值为0.02mm 的游标卡尺, 对线误差分布区间为0.01mm,为均匀分布,故标准不确定度u 1 为 3 2)01.0(1?= mm u =2.89μm 4.2校准用3级量块估算的测量不确定度分量u 2 测量用的3级量块的长度尺寸偏差0.80 μm +16×10-6L (L —测量长度mm),为均匀分布,当被测尺寸在191.8mm 的情况下,故测量不确定度u 2为 u 2= =?+732 .11918 .0168.0 2.23μm 4.3卡尺和量块的热膨胀系数差估算的测量不确定度分量u 3

0-200数显游标卡尺不确定度评定 更多免费资料下载请进:https://www.doczj.com/doc/5c7151270.html,好好学习社区

0-200数显游标卡尺不确定度评定 1 目的 保证检测数据的准确可靠,确保正确的量值传递。 2 适用范围 适用于本中心试验室0-200数显游标卡尺检测结果扩展不确定度的评定。 3 不确定度的评定步骤 3.1测量方法 用0-200数显游标卡尺直接测量被测样品。 3.2数学模型 Lx = L 式中: Lx—被检测样品的数值mm L—数显游标卡尺显示数值mm 3.3标准不确定度A类评定 选取三个不同尺寸的样品分别进行6次重复测量,并用贝塞尔公式计算实验标准偏差,选取一个样品长度为52mm测试数据见下表:

选取一个样品长度为120.35测试数据见下表: 选取一个样品长度为193.3测试数据见下表: 实际检测中只进行一次试验,测量重复性导致的测量不确定度为: 样品长度为52 mm 时:u1=s=0.006mm 样品长度为120.3mm时:u2=s=0.009mm 样品长度为193.3 mm时:u3=s=0.008mm 3.4 标准不确定度B类评定 数显游标卡尺示值不确定度为: 由校准证书知道,U95=0.02mm,k=2,则: U4=U95/k=0.02/2=0.01mm

3.5 灵敏度计算 C=?L x /?L =1 3.6计算合成标准不确定度 各输入量之间互不相关,因此 样品长度为52 mm 时: 012m m .02421=+=u u u c 样品长度为120.3mm 时 :013mm .02422=+= u u u c 样品长度为为193.3 mm 时: 013mm .02 423=+= u u u c 3.7扩展不确定度的计算 样品长度为52mm 时: U=ku c =0.024mm (取包含因子k=2,置信概率P=95%) 样品长度为120.3mm 时:U=ku c =0.026mm (取包含因子k=2,置信概率P=95%) 样品长度为193.3mm 时:U=ku c =0.026mm (取包含因子k=2,置信概率P=95%) 4 不确定度的报告结果 样品长度为52mm 时: U=0.024 mm (取包含因子k=2,置信概率P=95%) 样品长度为120.3mm 时:U=0.026mm (取包含因子k=2,置信概率P=95%) 样品长度为193.3mm 时:U=0.026mm (取包含因子k=2,置信概率P=95%) 5 备注 1、 数显游标卡尺内量爪在52-193.3mm 范围的不确定度与外量爪一样,内量爪在测量圆形孔越小时不确定度误差越大。 2、当被测长度没有相应的不确定度时,请用插入法计算相应长度不确定度

数值修约规则 Rules for rounding off of numberical values UDC 511.1/2 GB/T 8170 本标准适用于科学技术与生产活动中试验测定和计算得出的各种数值。需要修约时,除另有规定者外,应按本标准给出的规则进行。 l 术语 1.1 修约间隔 系确定修约保留位数的一种方式。修约间隔的数值一经确定,修约值即应为该数值的整数倍。 例1:如指定修约间隔为0.1,修约值即应在0.1的整数倍中选取,相当于将数值修的到 位小数。 例2:如指定修约间隔为100,修约值即应在100的整数倍中选取,相当于将数值修约到“百”数位。 1.2 有效位数 对没有小数位且以若于个零结尾的数值,从非零数字最左位向右数得到的位数减去无效零 (即仅为定位用的零)的个数;对其他十进位数,从非零数字最左、位向右数而得到的位数,就是有效位数。 例1:35000,若有两个无效零,则为三位有效数,应写为350X102;若有三个无效零,则为两位有效数,应写为35 X 103。 例2:3.2、0.32、0.032、0.0032均为两位有效位数;0.0320为三位有效位数。 例3:12.490为五位有效位数;10.00为四位有效位数。 1.3 05单位修约(半个单位修约) 指修约间隔为指定数位的0.5单位,即修约到指定数位的0.5单位。 例如:将60.28修约到个数位的0.5单位,得60.5(修约方法见本规则5.1)。 2 确定修约位数的表达方式 2.1 指定数位 a.指定修约间隔为10-n(n为正整数),或指明将数值修约到n位小数; b.指定修约间隔为1,或指明将数值修约到个数位; c.指定修约间隔为10n,或指明将数值修约到10n数位(n为正整数),或指明将数值修约到“十”、“百”、“千”……数位。 2.2 指定将数值修约成n位有效位数。 3 进舍规则 3.1 拟舍弃数字的最左一位数字小于5时,则舍去,即保留的各位数字不变。 例1:将12.1498修约到一位小数,得12.1。 例2:将12.1498修约成两位有效位数,得12。 3.2 拟舍弃数字的最左一位数字大于5;或者是5,而其后跟有并非全部为0的数字时,则进一,即保留的末位数字加1。 例1:将1268修约到“百”数位,得13X102(特定时可写为1300)。 例2:将1268修约成三位有效位数,得127 X 10(特定时可写为1270)。 例3:将10.502修约到个数位,得11。 注:本标准示例中,“特定时”的涵义系指修约间隔或有效位数明确时。 3.3 拟舍弃数字的最左一位数字为5,而右面无数字或皆为0时,若所保留的末位数字为奇数(1,3,5,7,9)则进一,为偶数(2,4,6,8,0)则舍弃。 例1:修约间隔为0.1(或10-1) 拟修约数值修约值 1.050 1.0

江苏宏泰石化机械有限公司 手动平板阀(阀盖)精车大头外圆尺寸测量结果的不确定度评定 总页数: 共4页

手动平板阀(阀盖)精车大头 外圆尺寸测量结果的不确定度评定 1、概述 1.1 测量过程:手动平板阀(阀盖)外圆精车大头外径进行测量控制 1.2 测量依据:HT/Q0106-05《工艺指导书》 JJF1059.1-2012《测量不确定度评定与表示》 1.3 环境条件:按照HT/Q0106-05要求在常温条件下测量。 1.4 测量仪器:分度值为0.02mm,规格为0-300mm的游标卡尺。 1.5 测量对象:外圆尺寸为Ф268mm的阀盖,允许误差±0.5mm。 2、数学模型 加工或检验人员在规定的位置直接以数显游标卡尺进行测量; P=P1-P2 式中:P---尺寸测量误差; P1---测量读数值; P2---在参考条件下,经检定合格的游标卡尺的误差,该误差由检定证书得出; 3、输入量的标准不确定度的评定 3.1、输入量 P的标准不确定度u(P)的评定 1 输入量 P的标准不确定度的来源主要是游标卡尺的测量重复性引起的标准不 1 确定度,可以通过连续测量得到测量列,采用A类方法进行评定。由检验人员或操作人员对公称外圆为Ф268mm的阀盖规定的位置在相同条件下测量,所测量的

结果如下: 268.00,268.20,268.00,268.20,268.10, 268.10,268.00,268.00, 268.10,268.00 其平均值为 mm P n P n i i .07.26811 ==∑= 1 )()(12 --=∑=n P P x s n i i = 0.0823≈0.083mm 日常实际测量,在重复条件下连续测量5次 mm x S p u 03.05) ()(1== 3.2、输入量的标准不确定度u (P 2)的评定 (1)输入量P 2的不确定度主要来源于游标卡尺的量程可知。分度值为0.02mm 的游标卡尺最大允许误差为±0.04㎜,误差分布符合正态分布,所以采用B 类方法进行评定。游标卡尺示值误差的不确定度分量为: um mm u 13013.03 04.01=≈= 由于分度值为0.02mm ,估读误差为0.02×(1/10)=0.002mm,误差的分布符合正态分布,估读误差的标准不确定度分量为: um mm u 7.000067.03 002.02≈≈= (2)根据计量检定证书提供的测量不确定度U=0.05mm,k=2则该游标卡尺的相对不确定度为: mm u 025.02 05.03== (3)由于上述3个不确定度分量都是相互独立的,因此B 类不确定度总和为:

拉伸试验测定结果的数据 处理和分析 The Standardization Office was revised on the afternoon of December 13, 2020

拉伸试验测定结果的数据处理和分析 一、试验结果的处理 有以下情况之一者,可判定拉伸试验结果无效: (1)试样断在机械刻划的标距上或标距外,且造成断后伸长率不符合规定的最小值者。 (2)操作不当 (3)试验期间仪器设备发生故障,影响了性能测定的准确性。 遇有试验结果无效时,应补做同样数量的试验。但若试验表明材料性能不合格,则在同一炉号材料或同一批坯料中加倍取样复检。若再不合格,该炉号材料或该批坯料就判废或降级处理。 此外,试验时出现2个或2个以上的缩颈,以及断样显示出肉眼可见的冶金缺陷(分层、气泡、夹渣)时,应在试验记录和报告中注明 二、数值修约 (一)数值进舍规则 数值的进舍规则可概括为“四舍六入五考虑,五后非零应进一,五后皆零视奇偶,五前为偶应舍去,五前为奇则进一”。具体说明如下: (1)在拟舍弃的数字中,若左边第一个数字小于5(不包括5)时,则舍去,即所拟保留的末位数字不变。 例如、将13.346修约到保留一位小数,得13.3。 (2)在拟舍弃的数字中,若左边第一个数字大于5(不包括5)时,则进1,即所拟保留的末位数字加1。

例如,将52. 463修约到保留一位小数,得52.5。 (3)在拟舍弃的数字中,若左边第一个数字等于5,其右边的数字并非全部为零时,则进1,所拟保留的末位数字加1。 例如,将2.1502修约到只保留一位小数。得2.2。 (4)在拟舍弃的数字中若左边第一个数字等于5,其右边无数字或数字皆为零碎时,所拟保留的末位数字若为奇数则进1,若为偶数(包括0)则舍弃。 例如,将下列数字修约到只保留一位小数。 修约前 0.45 0.750 2.0500 3.15 修约后 0.4 0.8 2.0 3.2 (5)所拟舍弃的数字若为两位数字以上时,不得连续进行多次修约,应根据所拟舍弃数字中左边第一个数字的大小,按上述规则一次修约出结果。 例如,将17.4548修约成整数。 正确的做法是:17.4548→17 不正确的做法是:17.455→17.46→17.5→18 (二)非整数单位的修约 试验数值有时要求以5为间隔修约。此时将拟修约的数值乘以2,按指定位数依前述进舍规则修约,然后将所得数值再除以2即可。例如:将下列数字修约到个位数的0.5单位。 拟修约数值X 乘以2 2X修约值 X修约值 30.75 61.50 62.0 30.0 30.45 60.90 61.0 30.5 三、拉伸试验的力学性能指标修约 拉伸试验测定的力学性能指标,除有特殊要求外,一般按表的要求进行修约。

数值修约规则

数值修约规则 在进行具体的数字运算前,按照一定的规则确定一致的位数,然后舍去某些数字后面多余的尾数的过程被称为数字修约,指导数字修约的具体规则被称为数字修约规则。 科技工作中测定和计算得到的各种数值,除另有规定者外,修约时应按照国家标准文件《数值修约规则》进行。 数字修约时应首先确定“修约间隔”、“有效位数”,即保留位数。一经确定,修约值必须是“修约间隔”的整数倍,保留至“有效位数”。 然后指定表达方式,即选择根据“修约间隔”保留到指定位数,或将数值修约成n位“有效位数”。 使用以下“进舍规则”进行修约: 1. 拟舍弃数字的最左一位数字小于5时则舍去,即保留的各位数字不变。 2.拟舍弃数字的最左一位数字大于5;或等于5,而其后跟有并非全部为0的数字时则进一即保留的末位数字加1。(指定“修约间隔”或“有效位数”明确时,以指定位数为准。) 3.拟舍弃数字的最左一位数字等于5,而右面无数字或皆为0时,若所保留的末位数字为奇数则进一,为偶数(包含0)则舍弃。 4.负数修约时,取绝对值按照上述1~3规定进行修约,再加上负号。 不允许连续修约 数值修约简明口诀:「4舍6入5看右,5后有数进上去,尾数为0向左看,左数奇进偶舍弃」。 现在被广泛使用的数字修约规则主要有四舍五入规则和四舍六入 五留双规则。 四舍五入规则 四舍五入规则是人们习惯采用的一种数字修约规则。 四舍五入规则的具体使用方法是: 在需要保留有效数字的位次后一位,逢五就进,逢四就舍。 例如:将数字2.1875精确保留到千分位(小数点后第三位),因小数点后第四位数字为5,按照此规则应向前一位进一,所以结果为2.188。同理,将下列数字全部修约为四位有效数字,结果为: 0.53664——0.5366 10.2750——10.28

试验数据读取运算修约评定 一、有效数字 (末)的概念:任何一个数最末一位数字所对应的单位量值。 有效数字的概念:当近似数的绝对误差的模小于0.5(末)时,从左边的第一个非零数字算起,直至最末一位数字为止的所有数字。 例1:将e=2.71828……截取到百分位 得近似数 2.72,则此时引起的误差绝对值为|2.72-2.71828……|=0.00172……。 2.72的(末)为0.01,因为0.5(末)=0.5×0.01=0.005>0.00172……,所以称2.72为三位有效数字。同理:2.718为四位有效数字;2.7182不是五位有效数字。 例2:用分度值为1mm的钢直尺测出某混凝土试块边长为150mm。 150的(末)为1mm,绝对误差的模小于0.5(末)=0.5×1=0.5mm,为三位有效数字,即该测量值误差小于0.5mm。 例3:用最小刻度为0.02mm的游标卡尺量出某Φ12钢筋直径为11.96mm。 11.96的(末)为0.02mm,绝对误差的模小于0.5(末)=0.5×0.02=0.01mm,为四位有效数字,即该测量值误差小于0.01mm。 例4:用分度值为0.5mm的砖用卡尺测量出某块普通砖高度为52.5mm。 52.5的(末)为0.5mm,绝对误差的模小于0.5(末)=0.5×0.5=0.25mm,为三位有效数字,即该测量值误差小于0.25mm。 从上可知,测量结果的有效位数同所用测量仪器的最小刻度值(末)密切相关,不同的有效数代表不同的检测精度,如20.10mm比20.1mm检测精度要高。所以,数字右边的“0”不能随意取舍,因为这些“0”都是有效数字。 二、近似数运算 1、加减法运算 以参与运算的各数中(末)最大的数为准,其余的数均比它多保留一位,多余位数应舍去。计算结果的(末),应与参与运算的数中(末)最大的那个数相同。若计算结果尚需参与下一步运算,则可多保留一位。 例5:15.3m+2.786m-0.8749m 取15.3m+2.79m-0.87m=17.22m≈17.2m 计算结果为17.2m。若需参与下一步运算,则取17.22m。 2、乘除法(或乘方开方)运算 以有效数字位数最少的那个数为准,其余数的有效数字均比它多保留一位。运算结果(积、商或乘幂、方根)的有效数字位数,应与参与运算中有效数字位数最少的那个相同。若需参与下一步运算,则可多保留一位。 例6:1.1m×0.3469m×0.20900m

“测量圆筒体积”不确定度评定 1、概述 根据……,在环境温度为20℃下,用 和高度H,各对圆筒的不同位置测量6次, 测量值为: 圆筒不同位置测量结果

2、数学模型 H D V ?=2)2 (π 式中:V —— 圆筒的体积;cm 3。 D —— 圆筒的直径;cm 。 H —— 圆筒的高度。cm 。 21)2(D H V c π=??= 、 H D D V c 2 2π=??= 将上表中=D 1.0081cm 、=H 10.0110cm 代入上式计算为: c 1=0.7982 cm 2, c 2=15.8526 cm 2 3、测量不确定度的来源 测量不确定度主要来源: ①、圆筒高度测量引入标准不确定度; ? 游标卡尺的本身不确定度 ? 测量人员读数引入标准不确定度 ? 圆筒高度不均匀引入标准不确定度 ②、圆筒直径测量引入标准不确定度。 ? 千分尺本身不确定度; ? 测量人员读数引入标准不确定度; ? 圆筒直径不均匀引入标准不确定度;

4、标准不确定度分量的评定 1、圆筒高度测量引入标准不确定度(u 1) ①、游标卡尺的本身不确定度(11u ) 游标卡尺的本身存在误差引入的标准不确定度根据游标卡尺的说明书〔或技术文件(如检定规程等)〕规定其最大允许误差为±0.020mm ,并经过检定且合格。假设测量值在最大允许误差范围内的概率分布为均匀分布,即,故其标准不确定度为: ②、测量人员读数引入标准不确定度(12u ) 根据游标卡尺分度值0.01mm ,按1/20来估读,则人员估读产生的测量不确定度为。 ③、圆筒高度不均匀引入标准不确定度(13u ) 在圆筒的不同位置测量H ,共测量6次,其测量数据见上表,则标准不确定度)(3H u 为: cm 000257.06 00063 .0)()(13====n H s H s u 综合上述分析,得圆筒高度测量引入标准不确定度为 cm 0000144.001.03 220/112=?=u cm 00115.03 020 .011==u

0-150mm带表游标卡尺不确定度评定 修订日期修订 单号 修订内容摘要页次版次修订审核批准 2011/03/30 / 系统文件新制定 4 A/0 / / / 批准:审核:编制:

0-150mm带表游标卡尺不确定度评定 1 目的 保证检测数据的准确可靠,确保正确的量值传递。 2 适用范围 适用于本中心试验室0-150mm带表游标卡尺检测结果扩展不确定度的计算。 3 不确定度的评定步骤 3.1测量方法 用0-150mm带表游标卡尺直接测量被测样品。 3.2数学模型 Lx = L 式中: Lx—被检测样品的数值mm L—带表游标卡尺显示数值mm 3.3标准不确定度A类评定 选取三个不同尺寸的样品分别进行6次重复测量,并用贝塞尔公式计算实验标准偏差。 选取一个样品长度为40mm测试数据见下表: 测量次数L(mm) 1 40.04 2 40.03 3 40.02 4 40.02 5 40.04 6 40.02 平均值40.03 实验标准偏差0.010 选取一个样品长度为80mm测试数据见下表:

测量次数L(mm) 1 79.98 2 80.00 3 80.02 4 80.00 5 80.00 6 79.98 平均值80.00 实验标准偏差0.015 选取一个样品长度为120.4mm测试数据见下表: 测量次数L(mm) 1 120.43 2 120.44 3 120.46 4 120.46 5 120.45 6 120.46 平均值120.45 实验标准偏差0.013 实际检测中只进行一次试验,则测量重复性导致的测量不确定度为: 样品长度为40 mm时:u1=s=0.010mm 样品长度为80mm时:u2=s=0.015mm 样品长度为120.4 mm时:u3=s=0.013mm 3.4 标准不确定度B类评定 带表游标卡尺示值不确定度为: 由校准证书知道,u95=0.02mm,k=2,则: u4=u95/k=0.02/2=0.01mm 3.5灵敏度计算 C=Lx/L =1 3.6计算合成标准不确定度 各输入量之间互不相关,因此

中华人民共和国国家标准数值修约规则 GB/T8170 s 本标准适用于科学技术与生产活动中试验测定和计算得出的各种数值.需要修约时,除另有规定者外,应按本标准给出的规则进行。 1术语 1.1修约间隔 系确定修约保留位数的一种方式.修约间隔的数值一经确定,修约值即应为该数值的整数倍。 例1:如指定修约间隔为0.1,修约值即应在0.1的整数倍中选取,相当于将数值修约到一位小数。 例2:如指定修约间隔为100,修约值即应在100的整数倍中选取,相当于将数值修约到“百”数位。 1.2有效位数 对没有小数位且以若干个零结尾的数值,从非零数字最左一位向右数得到的位数减去无效零(即仅为定位用的零)的个数;对其他十进位数,从非零数字最左一位向右数而得到的位数,就是有效位数。 例1:35000,若有两个无效零,则为三位有效位数,应写为350×102;若有三个无效零,则为两位有效位数,应写为35×103。 例2:3.2,0.32,0.032,0.0032均为两位有效位数;0.0320为三位有效位数。z& 例3:12.490为五位有效位数;10.00为四位有效位数。 1.30.5单位修约(半个单位修约) 指修约间隔为指定数位的0.5单位,即修约到指定数位的0.5单位。+,g 例如,将60.28修约到个数位的0.5单位,得60.5(修约方法见本规则5.1) 1.40.2单位修约 指修约间隔为指定数位的0.2单位,即修约到指定数位的0.2单位。 例如,将832修约到“百”数位的0.2单位,得840(修约方法见本规则5.2) 2确定修约位数的表达方式 2.1指定数位 a. 指定修约间隔为10n(n为正整数),或指明将数值修约到n位小数;1;3 b. 指定修约间隔为1,或指明将数值修约到个数位; c. 指定修约间隔为10n,或指明将数值修约到10n数位(n为正整数),或指明将数值修约到“十”,“百”,“千”……数位。 2.2指定将数值修约成n位有效位数 3进舍规则G 3.1拟舍弃数字的最左一位数字小于5时,则舍去,即保留的各位数字不变。x 例1:将12.1498修约到一位小数,得12.1。 例2:将12.1498修约成两位有效位数,得12。> 3.2拟舍弃数字的最左一位数字大于5;或者是5,而其后跟有并非全部为0的数字时,则进一,即保留的末位数字加1。 例1:将1268修约到“百”数位,得13×102(特定时可写为1300)。 例2:将1268修约成三位有效位数,得127×10(特定时可写为1270)。 例3:将10.502修约到个数位,得11。 注:本标准示例中,“特定时”的涵义系指修约间隔或有效位数明确时。 3.3拟舍弃数字的最左一位数字为5,而右面无数字或皆为0时,若所保留的末位数字为奇数(1,3,5,7,9)则进一,为偶数(2,4,6,8,0)则舍弃。u 例1:修约间隔为0.1(或10-1) 拟修约数值 修约值 1.050 1.0. 0.3500.4

文件号: 技术文件 通用卡尺不确定度评定细则 编写 审核 批准

通用卡尺测量结果不确定度评定细则 1 目的 2 本文件用于通用卡尺校准过程中,测量设备、人员、环境条件等因素引起的不确定度评定, 使计量人员能够准确、有效地评定通用卡尺的测量结果不确定度。 2 适用范围 本文件适用于实验室所有通用卡尺的测量结果不确定度评定。 3 引用文件 GJB 3756―1999 《测量不确定度表示与评定》 JJG 30-2012 《通用卡尺》检定规程 4 测量不确定度评估 4.1 测量标准 四等量块(10-291.8mm )/MPE ≤(0.15-0.18)μm 4.2 被测对象 通用卡尺(0-1000mm )/MPE ≤一个分度值 4.3 测量过程 将被检卡尺至于00级大理石平台上,同时量块恒温到规定的时间,用被检卡尺测量标准量块,比较被检卡尺的指示值与四等量块之差,即为示值误差。 4.4 通用卡尺测量结果不确定度评定 4.4.1.1 数学模型 游标卡尺的示值误差e 计算结果模型: n n n n t a L t a L L L e ???-???+-= 式中:L ——游标卡尺的示值(20℃条件下); L n ——量块的长度(20℃条件下); n a a 、 ——分别为游标卡尺和量块的线膨胀系数; n t t ??、——分别为游标卡尺和量块偏离温度20℃时的数值。 4.4.1.2 合成标准不确定度评定模型

由于各分量互不相关,故合成不确定度评定模型为: ()()()()r u a u Ln u u c 222++=δ 式中:()Ln u —— 由量块带来的不确定度分量; ()a u —— 由线膨胀系数带来的不确定度分量; ()r u —— 由读数误差带来的不确定度分量; 4.4.2 不确定度一览表 测量不确定度来源度分析及估算见表1。 表1 示值误差测量不确定度来源分析及估算 (注:对于数显卡尺,示值误差的不确定度来源只包括量块不确定度引入的不确定度) 4.4.3 计算标准不确定度分量 4.4.3.1 量块不确定度引入的不确定度 根据计量检定规程规定,用四等量块(其不确定度=1u 0.2μm +2×10-6L n ,k =2.58)校准通用卡尺的示值误差。对于测量下限超过300mm 的通用卡尺,采用多块不低于五等的量块研合作为标准(研合量块数量不超过3块)。 L n ≤300mm ,则()58 .221 u Ln u ? = L n >300mm ,不确定度为各研合量块不确定度的方和根(由于研合量块数量不超过3块,因此研合膜的厚度分散性影响可忽略不计)。则:()2 132 122 11u u u Ln u ++= 4.4.3.2 线膨胀系数引入的不确定度

0-150mm 游标卡尺测量结果不确定度评定 1. 慨述 1.1 评定依据:JJF1059.1-2012《测量不确定度评定与表示》。 1.2 测量依据:JJG30-2012 《通用卡尺检定规程》。 1.3 环境条件:温度(20±5)℃;湿度要求不超过80%RH 。 1.4 测量标准: 5等量块,其长度尺寸的不确定度不大于U = 3.5m μ,k =2。 1.5 被测对象:测量范围为0~150mm ,分度值为0.02mm 的游标卡尺,最大允许示值误差为±0.03m m 。 1.6 测量过程:对于测量范围为0~150mm 的游标卡尺,测量点的分布不少于均匀分布的3点,本次选择示值误差测量点为:41.20mm 、81.50mm 、121.80mm 。被测游标卡尺各点示值误差以该点读数值(示值)与量块尺寸(测量标准)之差确定。 2.数学模型 a b L L L ?=- 单位:mm 式中:L ?--游标卡尺某点示值误差; a L --游标卡尺某点的实测值; b L --量块的长度尺寸。 3.输入量的标准不确定度分量评定 3.1由估值误差引入的不确定度分量u 1的评定 由游标卡尺对准估值误差引入的不确定度,采用B 类方法进行评定。 游标卡尺的分度值为0.02mm ,估值误差(半宽度)为(0.02/2=0.01)mm ,估计其均匀分布,包含因子为√3,故标准不确定度u 1为 u 1=0.01÷√3≈0.006mm 3.2由测量重复性引起的不确定度分量u 2的评定 用量块对(0~150)mm 的游标卡尺的121.80mm 检定点,连续重复测量10次,得到一组测量示值,如“表0-1”所示: 表0-1 单次测量值 单位:mm

数值修约规则试题 部门:姓名: 一、判断题(20分=2.5*8) 1、如指定修约间隔为0.1,修约值即应在0.1的整数倍中选取,相当于将数值 修约到一位小数。(√) 2、如指定修约间隔为10,修约值即应在10的整数倍中选取,相当于将数值修 约到“十”数位。(√) 3、25000,若有两个无效零,则为三位有效位数,应写为250×102;若有三个无 效零,则为两位有效位数,应写为25×103。(√) 4、3.2,0.32,0.032,0.0032,0.0320均为两位有效位数。(×) 5、532.490为六位有效位数;10.00为四位有效位数。(√) 6、拟修约数字应在确定修约位数后一次修约获得结果,可以多次按第3章规则连续修约。(×) 7、在具体实施中,有时测试与计算部门先将获得数值按指定的修约位数多一位或几位报出,而后由其他部门判定。(√) 8、16.50(+)表示实际值大于16.50,经修约舍弃成为16.50;16.50(-)表示实际值小于16.50,经修约进一成为16.50。(√) 二、填空题(50分=2*25) 1、确定修约位数的表达方式有:指定位数/修约间隔和有效数字 2、拟舍弃数字的最左一位数字小于5时,则舍弃。 (1)将10.1498修约到一位小数,得 10.1 。 (2:将10.1498修约成两位有效位数,得 10 。 3、拟舍弃数字的最左一位数字大于5;或者是5,而其后跟有并非全部为0的数字时,则进一。 (1)将1169修约到“百”数位,得12×102(特定时可写为 1200 )。(2)将1169修约成三位有效位数,得 117×10 (特定时可写为 1170 )。 (3)将11.502修约到个数位,得 12 。 4、拟舍弃数字的最左一位数字为5,而右面无数字或皆为0时,若所保留的末位数字为奇数(1,3,5,7,9)则进一,为偶数(2,4,6,8,0)则舍 弃。 (1)修约间隔为0.1(或10-1) 拟修约数值修约值 2.050 ( 2.0 ) 0.350 ( 0.4 ) (2)修约间隔为1000(或103) 拟修约数值修约值 4500 ( 4000 )

0-200mm深度游标卡尺不确定度评定 更多免费资料下载请进:https://www.doczj.com/doc/5c7151270.html,好好学习社区

0-200mm深度游标卡尺不确定度评定 1 目的 保证检测数据的准确可靠,确保正确的量值传递。 2 适用范围 适用于本中心试验室0-200mm深度游标卡尺检测结果扩展不确定度的计算。 3 不确定度的评定步骤 3.1测量方法 用0-200mm深度游标卡尺直接测量被测样品。 3.2数学模型 Lx = L 式中: Lx—被检测样品的数值mm L—带表游标卡尺显示数值mm 3.3标准不确定度A类评定 选取三个不同尺寸的样品分别进行6次重复测量,并用贝塞尔公式计算实验标准偏差。 选取一个样品长度为52mm测试数据见下表:

选取一个样品长度为120.35mm测试数据见下表: 选取一个样品长度为193.3mm测试数据见下表: 实际检测中只进行一次试验,则测量重复性导致的测量不确定度为: 样品长度为52 mm时:u1=s=0.011mm 样品长度为120.35mm时:u2=s=0.009mm 样品长度为193.3mm时:u3=s=0.011mm 3.4 标准不确定度B类评定 深度游标卡尺示值不确定度为: 由校准证书知道,u95=0.02mm,k=2,则: u4=u95/k=0.02/2=0.01mm

3.5 灵敏度计算 C=?Lx/?L =1 3.6计算合成标准不确定度 各输入量之间互不相关,因此 样品长度为52 mm 时: 015m m .02421=+=u u u c 样品长度为120.35mm 时: 013mm .02422=+=u u u c 样品长度为193.3 mm 时: 015m m .02423=+= u u u c 3.7扩展不确定度的计算 样品长度为52mm 时: U=ku c =0.030mm (取包含因子k=2,置信概率P=95%) 样品长度为120.4mm 时:U=ku c =0.026mm (取包含因子k=2,置信概率P=95%) 样品长度为192mm 时: U=ku c =0.030mm (取包含因子k=2,置信概率P=95%) 4 不确定度的报告结果 样品长度为52mm 时: U=0.030 mm (取包含因子k=2,置信概率P=95%) 样品长度为120.35mm 时:U=0.026mm (取包含因子k=2,置信概率P=95%) 样品长度为193.3mm 时: U=0.030mm (取包含因子k=2,置信概率P=95%) 5 备注 1、 带表游标卡尺内量爪在52-193.3mm 范围的不确定度与外量爪一样,内量爪在测量圆形孔越小时不确定度误差越大。 2、当被测长度没有相应的不确定度时,请用插入法计算相应长度不确定度

游标卡尺示值误差测量结果的不确定度评定 1、概述 1.1、测量方法:依据JJG30-2002《通用卡尺检定规程》。 1.2、环境条件:室内温度(20±5)℃;室内湿度≤80%RH 。 1.3、测量标准:6等量块,其长度尺寸的确定度不大于( 2.00+12L )m μ( L-测量长度),包含因子k=2.7。 1.4、测量对象:测量范围为0~300mm ,分度值为0.02mm 的卡尺,200~300mm 最大允许示值误差为±0.04mm 。 1.5、测量过程 对于测量范围为0~300mm 的卡尺,测量点的分布不少于均匀分布的3点,如300mm 的卡尺,其受检点为101.2、201.5和291.8mm 。被测卡尺各点示值误差以该点读数值(示值)与量块尺寸(测量标准)之差确定。 1.6评定结果的使用 在符合上述条件下的测量结果,一般可直接使用本不确定度的评定结果。 2、数学模型 L ?=L -b L 式中: L ?—卡尺的最大允许示值误差; L —卡尺示值; b L —量块的长度尺寸。 3、输入量的标准不确定度的评定 3.1、输入量L 的标准不确定度()L μ的评定 输入量L 的标准不确定度主要来源于卡尺分度量化误差的的不确定度,采用B 类方法进行评定。 卡尺的分度值为0.02mm ,量化误差为(2 02.0)mm ,估计其为均匀分布,包含因子为3,故标准不确定度()L μ为 ()L μ= (2 02.0)/3 =0.006mm ()L μ 可视为确实已知量,则自由度为)(L ν→∞ 3.2、输入量b L 的标准不确定度() b L μ的评定

输入量b L 的标准不确定度主要来源于量块长度尺寸的不确定度,可根据量块证书给出的量块长度尺寸的不确定度来评定,所以采用B 类方法进行评定。 测量用的量块其长度尺寸的不确定度不大于(2.00+12L )m μ(L —测量长度),包含因子k=2.7。 当被测尺寸在291.8mm (不确定度可能最大)的情况下,标准不确定度 ()b L μ为 ()b L μ=a/k= 7.22918.01200.2?+m μ=0.002mm 估计)()(b b L L μμ?为0.01,则自由度)(b L ν→∞ 4、合成标准不确定度的评定 4.1、 灵敏系数 数学模型 L ?=L -b L 灵敏系数 c 1= L L ???=1 c 2=b L L ???=-1 4.2、标准不确定度汇总表 输入量的标准不确定度汇总于表4-1 4.3、 合成标准不确定度的计算

创作编号:GB8878185555334563BT9125XW 创作者:凤呜大王* 数字修约规则 一、有效数字 所谓有效数字,就是实际能测得的数字。它的末一位为不准确数字,其余数字均为准确数字。 有效数字中“0”的意义 ?“0”有两种意义: ?1.是作为数字定位,如:在0.312中,小数点前面的“0”是定位用的,它有3位有效数字;在0.012中,“1”前面的2个“0”是定位用的,它有2位有效数字。 ?2.是有效数字,如:在10.1430中,两个“0”都是有效数字,所以它有6位有效数字。 有效数字中“0”的意义 ?综上所述,数字之间的“0”和末尾的“0”都是有效数字,而数字前面所以的“0”只起定位作用。以“0”结尾的正整数,有效数字的位数不确定。例如4500这个数,就不好确定几位有效数字。应根据实际有效数字位数书写来确定: 4.5×103 2 位有效数字 4.50×103 3 位有效数字 4.500×103 4 位有效数字 数字修约规则 ?为了适应生产和科技工作的需要,我国已经正式颁布了GB8170-87《数字修约规则》,通常称为“四舍六入五成双”法则。即当位数≤4时舍去,尾数≥6时进位,尾数=5时,应视保留的末尾数是奇数还是偶数,5前为偶数时5应舍去,5前为奇数则进位。 ? 数字修约规则 这一法则具体应用如下: ?被舍弃的第一位数字大于5,则其前一位加1 ?若被舍弃的第一位数字等于5而其后数字全部为零,则按“四舍六入五成双”

法则而定进或舍。 ?若被舍弃的第一位数字等于5而其后数字并非全为零则进1 ?若被舍弃的数字包括几位数字时,不得对该数字进行连续修约,而应根据以上各条只做1次处理。 有效数字运算规则 ?加减法 在加减法运算中,保留有效数字的位数,以小数点后位数最少的为准,即以绝对误差最大的数为准。 有效数字运算规则 ?乘除法 在乘除法运算中,保留有效数字的位数,以位数最少的数为准,即以相对误差最大的数为准。 有效数字运算规则 ?自然数 在分析化学运算中,有时会遇到一些倍数或分数的关系。例如:水的相对分子质量=2×1.008+16.00=18.02 其中“2”不能看做1位有效数字。因为它们是非测量所得到的数,是自然数,其有效数字位数,可视为无限的。 创作编号:GB8878185555334563BT9125XW 创作者:凤呜大王*

检测分析结果的数据处理与修约 一.有效数字 一个数的有效数字包括该数中所有的肯定数字再加上最后一位可疑的数字。具体来说,有效数字就是实际上能测到的数字。例如,用万分之一天平秤量最多可精确到0.1mg ,称得的质量,如以克为单位,应正确记录到小数点后四位。 二.数字修约规则 数字修约采用“四舍六入五单双”的原则,即在所拟舍去的数字中,其最左面的第一个数字小于、等于4时舍去,等于、大于6时进一;所拟舍去的数字中,其最左面的第一个数字等于5时,若其后面的数字并非全部为“0”时,则进1,若5后的数字全部为“0”就看5的前一位数,是奇数的则进位是偶数的则舍去(“0”以偶数论)。 三.计算规则 几个数据相加或相减时,计算结果的绝对误差应与各数中绝对误差最大者相等,它们的和或差只能保留一位不确定数字,即有效数字的保留应以小数点后位数最少的数字为根据。 在乘除法中,计算所得结果的相对误差必须与各测量数值中相对误差最大者相近,因此有效数字的保留应根据这一原则进行判断。一般说来,以有效数字位数最少的数为标准,弃去其他数的过多的位数,然后进行乘、除。在计算过程中,可以暂时多保留一位数字,得到最后结果时,再弃去多余的尾数。 四.分析结果的有效数字的保留 1.结果≥10% 保留4位有效数字 2.结果在1%~10%之间保留3位有效数字 3.结果≤1% 保留2位有效数字 五.极端值的取舍 对同一样品进行多次分析(如标样分析)所得到的一组数据总是有一定的离散性,这是由于随机误差引起的,是正常的。但有时出现个别偏离中值较远的较大或较小的数,称为极端值。可借助统计方法来决定取舍。常用的统计方法有格拉布斯(Gru-bbs )的T 值检验法。 将测得的一组值从小到大排成x 1,x 2,x 3,…,x n —1,x n 。先检验与邻近值差距更大的一个,即x 1或x n 。算出该组数的算数平均值(x )和标准偏差(s ),则T 值为: s x x T n -=或 s x x T 1 -=