Generic Interrupt Controller(GIC) 1. Introduction

1.1 About the Generic Interrupt Controller architecture

1.通用中断控制器架构定义:

? 该架构用于处理任何连接到GIC上的处理器的所有中断源

? 通用的中断控制器可编程接口适用于单处理器或是多处理器系统中。

2.GIC集成系统中所支持和管理的中断源,It provides:

? 寄存器用于管理中断源,中断行为和中断分发到一个或多个处理器

? Support for:

—ARM 架构虚拟扩展

—使能或禁用处理器中断的外设中断源

—软件生成的中断(SGI)

—中断屏蔽和优先级

—单处理器和多处理器环境

—在电源管理环境下的唤醒事件

3.处理器安全状态和安全与非安全访问GIC

处理器实现了ARM安全扩展有安全状态,安全或非安全:

?处理器在非安全状态只可以通过非安全方式访问GIC

?处理器在安全状态既可以通过安全也可以非安全的方式访问GIC

?运行在非安全状态的软件被描述为非安全软件

?运行在安全状态的的软件被描述为安全软件

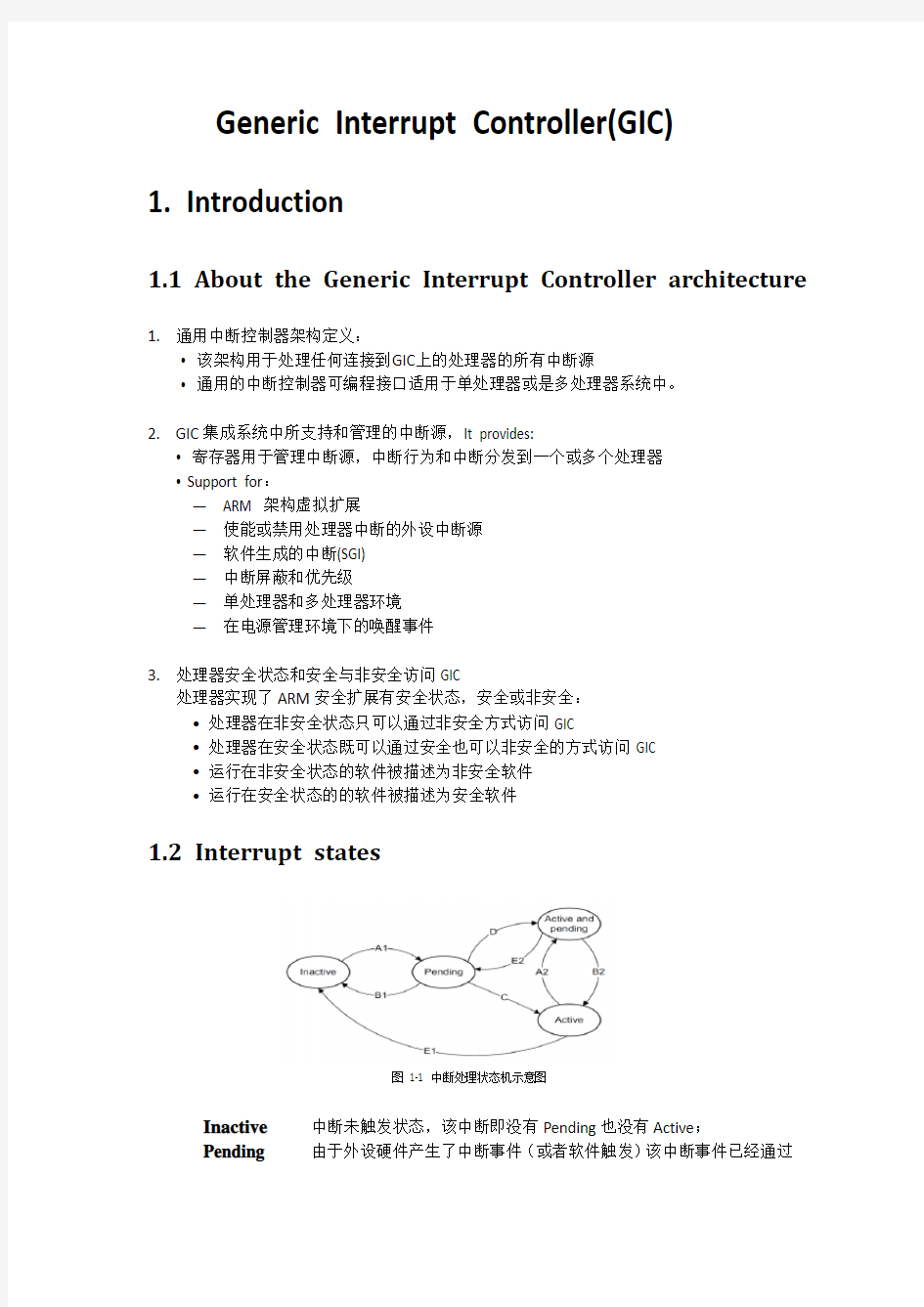

1.2 Interrupt states

图1-1 中断处理状态机示意图

Inactive中断未触发状态,该中断即没有Pending也没有Active;

Pending 由于外设硬件产生了中断事件(或者软件触发)该中断事件已经通过

硬件信号通知到GIC,等待GIC分配的哪个CPU进行处理;

Active C PU已经应答(acknowledge)了该interrupt请求,并且正在处理中

但是还没有处理完;

Active and pending 当一个中断源处于Active状态的时候,同一中断源又触

发了中断,进入pending状态。

Note:中断一旦被应答,distributor就会把该中断的状态由pending状态

改为active或者是active and pending (这是和该interrupt source的信号有关,例如如果是电平中断并且保持了该asserted电平,那么就是active and Pending)。

1.3 Interrupt Grouping

1. 除了不包括安全扩展的GICv1实现,所有的GIC架构都支持中断分组。

?默认所有的中断都是Group0中断,通过IRQ中断请求信号发送给连接到的处理器

?每一个中断可以被配置为Group1或者是Group0中断

?CPU interface可以配置成通过FIQ中断请求发送Group0中断给连接到的处理器

2. GIC包含中断分组的功能,该功能支持:

? 将每一个中断配置为Group 0或是Group 1

? 通过IRQ或是FIQ异常请求将Group 0中断发送给目标处理器

?只能通过IRQ异常请求将Group 1中断发送给目标处理器

?一个统一的方案用于处理Group 0和Group 1中断的优先级

?一些Group 0中断的配置的锁定是可选的

3. GICv2中,当用软件模型将GICC_CTLR.AckCtl设置为0,分离的寄存器被用来管理Group0和Group1中断。

—GICC_IAR, GICC_EOIR, and GICC_HPPIR for Group 0 interrupts

—GICC_AIAR, GICC_AEOIR, and GICC_AHPPIR for Group 1 interrupts. Note:当GIC实现了安全扩展并且与之相连的处理器也实现了ARM安全扩展,那么:Group 0中断为安全的中断,Group 1中断为不安全的中断。

1.4 Interrupt stype

1)Peripheral Interrupt --- 边沿触发和电平触发

Private Peripheral Interrupt(PPI)

--- ID16-ID31 are used for PPIs

PPI为每个core的私有外设中断

Share Peripheral Interrupt(SPI)

--- Interrupt numbers ID32-ID1019 are used for SPIs

SPI为各个core公用的中断

2)Software Generated Interrupt(SGI) --- 边沿触发

--- ID0-ID15 are used for SGIs(ID0-ID7是不安全中断,ID8-ID15是安全

中断)SGI为软件可以触发的中断,经常用于各个core之间的通信。该类中断

通过相关联的中断号和产生该中断的处理器的CPUID来标识

3)虚拟中断(Virtual interrupt)

4)维护中断(Maintenance interrupt)

Note:电平触发是在高或低电平保持的时间内触发, 而边沿触发是由高到低或由低到高这一瞬间触发;在GIC中PPI和SGI类型的中断可以有相同的中断ID。

1.5 Models for handling interrupts

1) 1-N mode (SPIs using the GIC 1-N model)

表示中断可以发给所有的CPU,但只能由一个CPU来处理中断;换句话说,这种类型的中断有N个目标CPU,但只能由其中一个来处理;当某一个处理器应答了该中断,便会清除在所有目标处理器上该中断的挂起状态。

2) N-N mode (PPIs and SGIs using the GIC N-N model)

表示中断可以发给所有CPU,每个CPU可以同时处理该中断。当该中断被某一个处理器应答了,这不会影响该中断在其他CPU接口上的状态。

举两个例子说明:

1)UART 接收到一包数据,产生了一个中断给GICD,GICD可以将该中断分配给CPU0-7中任何一个处理;假设该中断分配给CPU0处理了,那么在中断处理函数里面会把接收到的数据从UART FIFO读出。可以想象一下,如果CPU0在读数据时,另外一个CPU也在处理该中断,恰巧也在读数据,那么CPU0读到的数据是不全的。这就是1-N model中断,或者说SPI中断。

2)比如CPU0给CPU1-7发送中断,想告知对方自己正在处理某个进程A。这种场景下,CPU1-7都接收到中断,都进入中断处理函数,CPU1-7获取到CPU0的信息后,在进程调度时,就可以绕开进程A,而自己调度其他进程。

注:这个例子只是说明N-N model,实际上进程调度不是这样的。

1.6 Spurious interrupts

1. GIC发送给处理器的中断不再被需要,这是有可能的。如果发生上述情况,当处理器应答该中断,GIC会返回一个特殊的中断ID用来标识该中断是一个伪中断。发生伪中断的原因:? 先于处理器应答该中断,发生了:

—软件改变了该中断优先级

—软件Disable该中断

—软件改变了该中断的目标处理器

? 对于1-N模型的中断,其他处理器先于此处理器应答该中断

1.7 Banking

1) Interrupt banking

在多处理器系统中,对于PPI和SGI,GIC可以有多个中断使用同一个中断号。这样的中断称为banked interrupt,该类中断通过中断号和相关联的CPU interface可以唯一标识。

2) Register banking

是指在同一个地址实现多个副本寄存器,即多个寄存器拥有相同的地址。

?在多处理器系统中,为banked interrupt的相关寄存器在每个处理器上

提供一个独立的copy。

?在GIC实现安全扩展中,提供寄存器的安全与非安全的副本。

Note:在ARM结构中最常见的Register Banking是R8~R12,在不同模式下,使用不同的物理寄存器。

2. GIC Partitioning

通常把GIC分成两个部分,分发器(Distributor)和CPU接口(CPU Interface)。

2. 1 Distributor

2.1.1 Distributor defines

The Distributor centralizes all interrupt sources, determines the priority of each interrupt, and for each CPU interface forwards the interrupt with the highest priority

to the interface, for priority masking and preemption handling.

2.1.2 Distributor对中断的控制

1. Distributor提供可编程的接口for:

(1)中断enable或者disable的控制。Distributor对中断的控制分成两个级别。一个是全局中断的控制(GIC_DIST_CTRL)。一旦disable了全局的中断,那么任何的interrupt source 产生的interrupt event都不会被传递到CPU interface。另外一个级别是对针对各个interrupt source进行控制(GIC_DIST_ENABLE_CLEAR),disable某一个interrupt source会导致该interrupt event不会分发到CPU interface,但不影响其他interrupt source产生interrupt event的分发。

(2)控制将当前优先级最高的中断事件分发到一个或者一组CPU interface。当一个中断事件分发到多个CPU interface的时候,GIC的内部逻辑应该保证只assert 一个CPU。(?) (3)优先级控制。

(4)interrupt属性设定。例如是level-sensitive还是edge-triggered

(5)interrupt group的设定

Note: 分发器其实应该叫汇聚器,在IC的后端设计中,layout会把各个模块引过来的中断线混接到GIC(就是上面说的三种中断),然后把混聚合的中断接到CPU的irq线上,这样core就有触觉了。

2.2 CPU Interface

CPU interface这个block主要用于和processor进行接口。

2.2.1 Interface 的作用

(a)enable或者disable CPU interface向连接的CPU assert中断事件。对于ARM,CPU interface block和CPU之间的中断信号线是nIRQCPU和nFIQCPU。如果disable了中断,那么即便是Distributor分发了一个中断事件到CPU interface,但是也不会assert指定的nIRQ或者nFIQ通知processor。

(b)ackowledging中断。processor会向CPU interface block应答中断(应答当前优先级最高的那个中断),中断一旦被应答,Distributor就会把该中断的状态从pending状态修改成active或者pending and active(这是和该interrupt source的信号有关,例如如果是电平中断并且保持了该asserted电平,那么就是pending and active)。processor ack了中断之后,CPU interface就会deassert nIRQCPU和nFIQCPU信号线。

(c)中断处理完毕的通知。当interrupt handler处理完了一个中断的时候,会向写CPU interface的寄存器从而通知GIC CPU已经处理完该中断。做这个动作一方面是通知Distributor将中断状态修改为deactive,另外一方面,CPU interface会priority drop,从而允许其他的pending的interrupt向CPU提交。

(d)设定priority mask。通过priority mask,可以mask掉一些优先级比较低的中断,这些中断不会通知到CPU。

(e)设定preemption的策略

(f)在多个中断事件同时到来的时候,选择一个优先级最高的通知processor

2.2.2 Example

我们用一个实际的例子来描述GIC和CPU接口上的交互过程,具体过程如下:

Figure 2-1

首先给出前提条件:

(a)N和M用来标识两个外设中断,N的优先级大于M (b)两个中断都是SPI类型,level trigger,active-high (c)两个中断被配置为去同一个CPU

(d)都被配置成group 0,通过FIQ触发中断

下面是按照时间轴来描述交互过程:

2.2.3 Interrupt signal bypass

1. Bypass 可以理解为绕开或者旁路

Figure 2-2 Interrupt signal bypass, GICv1 without Security Extensions

Note:当CPU interface发送IRQs/FIQs中断被禁用时, IRQs/FIQs信号可以通过旁路发送给处理器。

2. Table 2-1描述了GICC_CTLR是如何控制GIC中断的输出。

Table 2-1 Interrupt signal bypass behavior, GICv1 with Security Extensions

Note:位FIQEn用来指明Group0中断是通过IRQ或者是FIQ信号来通知处理器

3. Interrupt Handling and Prioritization

3.1通用中断处理

当GIC接收到一个中断请求,将其状态设置为Pending。重新产生一个挂起状态的中断不影响该中断状态。中断处理顺序:

①GIC决定该中断是否使能,若没有被使能对GIC没有影响;

②对于每个Pending中断,GIC决定目标处理器;

③对于每个处理器,Distributor根据它拥有的每个中断优先级信息决定最高优先级的

挂起中断,将该中断传递给目标CPU Interface;

④GIC Distributor将一个中断传递给CPU Interface后,该CPU Interface决定该中断是否

有足够的优先级将中断请求发给CPU;

⑤当CPU开始处理该异常中断,它读取GICC_IAR应答中断。读取的GICC_IAR获取到

中断ID,对于SGI,还有源处理器ID。中断ID被用来查找正确的中断处理程序。GIC 识别读过程后,将改变该中断的状态:

a)当中断状态变为active时,如果该中断挂起状态持续存在或者中断再次产生,

中断状态将从Pending转化为pending & active

b)否则,中断状态将从pending状态变为active

⑥当中断完成中断处理后,它需要通知GIC处理已经完成。这个过程称为priority drop

and interrupt deactivation:

a)总是需要向EOIR寄存器写入一个有效的值(end of interrupt register)

b)也需要接着向GICC_DIR写入值(deactivate interrupt register)

3.2 Interrup priorization

这一章描述在GIC架构中的中断优先级。软件可以通过给每一个中断源分配优先级值来配置中断优先级。优先级的值是个8位的无符号二进制数,GIC支持最小16和最大256的优先级级别。如果GIC实现的优先级少于256,那么优先级字段的低阶位为RAZ/WI。这就意味着实现的优先级字段个数范围是4~8,如图3-1所示:

Table 3-1 Effect of not implementing some priority field bits

Note:

1)、如何确定优先级字段所支持的优先级位?

通过软件往可写GICD_IPRIORITYn优先级字段写入0XFF,然后回读出该字段的值便

可以确定优先级字段所支持的优先级位(因为有些位没实现是RAZ/WI)

2)、ARM 推荐在检查中断优先级范围之前先:

?对于外设中断,软件先禁用该中断

?对于SGI,软件先检查该中断确定为inactive

3.2.1 Preemption

在一个active中断处理完之前,CPU interface支持发送更高优先级的挂起中断到目标处理器。这种情况必要条件如下:

·该中断的优先级高于当前CPU interface 被屏蔽的优先级

·该中断的组优先级高于正在当前CPU interface处理的中断优先级

3.2.2 Priority masking

CPU interface的GICC_PMR寄存器定义了目标处理器的优先级阀值,GIC仅上报优先级高于阀值的pending中断给目标处理器。寄存器初始值为0,屏蔽所有的中断。

3.2.3 Priority grouping

优先级分组是将GICC_BPR(Binary Point Register)分成两个域,组优先级(group priority)和组内优先级(subpriority)。当决定抢占(preemption)的时候,组优先级相同的中断被视为一样的,不考虑组内优先级。那就意味每个优先级组内只能有一个中断被激活。组优先级又被称为抢占级别(preemption level)。GIC使用组优先级决定挂起中断是否有足够的优先级抢占当前active中断,原则如下:

·如果发生抢占,该挂起中断的组优先级一定比当前active中断的组优先级高,也就是说挂起中断的组优先级域的值小于active中断的组优先级域的值;

·如果当前CPU interface上没有active中断,最高优先级的挂起中断将被传递给处理器,而不考虑组优先级。

This 3-bit field specifies how many of the least significant bits of the 8-bit interrupt priority field are excluded from the group priority field, as Table 3-1 shows.

Table 3-1 Priority grouping by binary point

对上图的理解:如果binary point取值n,8位interrupt priority中组优先级占位的最低有效

位为第n+1位,且n+1<8。

即当binary point取不同值,n从0到7

0:最高7位用于指定抢占式优先级,最低1位用于指定响应优先级;

1:最高6位用于指定抢占式优先级,最低2位用于指定响应优先级;

以此类推,当n取7时,所有八位都用于指定响应优先级。

3.4中断分组对中断处理的影响

3.4.1特殊的中断号

GIC架构中保留了一些中断号为特殊的用途,如下:

1020 ~1021 保留

1022 :只有当GIC实现了中断分组,该中断号才被使用。GIC返回这个值给处理器作为中断应答,只有当下面几点都满足:

?读GICC_IAR作为中断应答

?优先级最高的挂起中断是Group 1中断

?位GICC_CTLR.AckCtl被设置为0

?中断具有足够的优先级,可以发送给处理器

1023 :如没有足够优先级的挂起中断可以发送给处理器,这个值可以返回给处理器作为中断应答。

Note:在支持中断分组的处理器中,1022和1023是伪中断号。

3.4.2中断分组对中断应答的影响

1.在GIC实现了支持中断分组,ARM强烈推荐将位GICC_CTLR.AckCtl设置为0,这意味着:

·对于GICv2的实现:

—Group 0的中断通过读寄存器GICC_IAR来应答或者是安全的读寄存器GICC_IAR如果GICv2的实现包括GIC安全扩展

—Group 1的中断通过读寄存器GICC_AIAR来应答或者是非安全的读寄存器GICC_IAR如果GICv2的实现包括GIC安全扩展

·对于GICv1的实现:

—通过读安全的GICC_IAR寄存器来应答Group 0中断

—通过读非安全的GICC_IAR寄存器来应答Group 1中断

在每一种情况下,读出的中断ID必须是CPU interface上优先级最高的挂起中断。

2.接下来操作的描述是基于ARM推荐的配置GICC_CTLR.AckCtl设置为0:

1)如果最高优先级的中断是安全的中断,处理器必须采取安全的读GICC_IAR去应答该中

断

2)为了应答非安全的中断,处理器可以:

·执行GICC_IAR寄存器的非安全读

·在GICv2实现中,执行GICC_AIAR寄存器的安全读

这就意味着,当非安全的软件正在处理非安全的中断,处理器可采取非安全的读GICC_IAR来应答该非安全的中断。

如果读GICC_IAR寄存器不能匹配安全的中断,这次的读不会应答任何中断且会返回:·当最高优先级的中断是非安全的,进行安全的读,返回1022

·当最高优先级的中断是安全的,进行非安全的读,返回1023

3.4.3 G IC上电或复位的配置

当GIC上电,或者之后的复位,实现了中断分组的GIC会被配置为:

·所有的中断被分配给Group 0

·FIQ的异常请求被禁用

这意味着Group 0中断是通过IRQ异常请求发送给处理器的,如图3-2所示:

Figure 3-2 Reset configuration of a GIC that includes the FIQ exception request

3.5GIC用例模型

GIC实现支持中断分组,软件通过GICD_IGROUPRn寄存器将中断分为两组,并且通过IRQ 或者FIQ异常请求,把中断发送给处理器。图3-3显示了中断处理的大致流程:

Figure 3-3 Generic GIC usage model

4. Programmers’Model

这章主要介绍了Distributor和CPU interface两部分的寄存器内容。

4.1 About the Programmer’Model

该编程模型提供了软件的接口用于操作GIC。这章描述了Distributor和CPU interface的编程模型,通过操作存储器映射寄存器接口。

4.1.1 GIC Register Name

所有的GIC寄存器都提供了缩写方便记忆,缩写规则如下:

?前三个字母是GIC,表明这是GIC寄存器;

?第四个字母是以下的其中之一:

—D, indicating a Distributor register

— C, indicating a CPU interface register

—H, indicating a virtual interface control register, typically accessed by a hypervisor

—V, indicating a virtual CPU interface register.

?其余的字母是表示特定功能的缩写,如GIC Distributor Control Register 被称作GICD_CTLR。

4.2 GIC的安全扩展对编程模型的影响

1. 该GIC安全扩展提供以下功能:

?该GIC必须支持中断分组

— GIC可能实现一些中断总是属于Group 0或者总是属于Group 1;

—否则,通过软件来配置每个中断是属于Group 0 或是Group 1;

—中断处理的某些方面依赖于中断是否是Group 0 或是Group 1;

?支持三种类型的寄存器,安全扩展寄存器如下:

—Banked:该设备实现了寄存器安全与非安全的副本,寄存器中的位分配可以不同。安全的访问总是访问寄存器的安全副本,非安全的访问总是访问寄存器非安全的副本。

—Secure:该寄存器只可以通过安全方式来访问,采取非安全的访问,返回RAZ/WI。

—Common:该寄存器既可以通过安全也可以通过非安全的方式来访问。该寄存器的一些或所有字段的访问权限可能取决于访问方式是安全的或是非安全的。

2. Configuration Lockdown

GIC的实现包括了安全扩展的,可以实现配置锁定。该系统可以发出提供的控制信号,以防止写访问:

? 用来控制配置SPI范围的寄存器字段,当那些SPIs被配置成Group 0组的中断;

?一些配置寄存器。

可以被锁定的SPI被称为Lockable SPIs (LSPIs),LSPIs的数目是实现定义好的,在0~31之间:?如果GIC支持一些LSPIs,那么第一个LSPI可能的中断号是32;

?GICD_TYPER.LSPI字段定义了LSPIs的最大值,如果该字段的值大于0,那么LSPIs的中断号范围为32~(31+GICD_TYPER.LSPI)。

Note:GIC忽略对锁定的寄存器或是寄存器字段的任何写操作。

4.3 Distributor Register Description

4.3.1 Distributor Control Register(GICD_CTLR)

1. 作用: 使能转发挂起的中断从Distributor到CPU interface。

2. Bit Assignment:

Figure 4-1 GICD_CTLR bit assignments, GICv2, and GICv1 Secure copy

Table 4-1 GICD_CTLR bit assignments, GICv2, and GICv1 Secure copy

Note:当Distributor的全局使能位被设置为0,关掉了Distributor的转发中断的功能,GIC 的其他寄存器的读写操作仍然是可以正常进行的。这就是说在重新使能Distributor之前,软件可以改变PPIs和SPIs中断的状态。(通过设置状态类寄存器,如:GICD_ISPENDRn、GICC_EOIR) 对于SGI中断,在GICv2中,软件可以管理SGI的状态;而在GICv1中,该GIC清除了SGI 的挂起状态,只有当SGI是active,因此软件无法清除SGI的挂起状态。

4.3.2 Interrupt Controller Type Register(GICD_TYPER)

1.作用:提供有关GIC的配置信息

?GIC是否实现了安全扩展

?GIC所能支持的最大中断号

? 实现的CPU interface的数目

? 如果GIC实现了安全扩展,实现可锁定共享外设中断的最大数量

2. Bit assignments:

Figure 4-2 GICD_TYPER bit assignments

Table 4-2 GICD_TYPER bit assignments

4.3.3 Interrupt Priority Register(GICD_PRIORITYRn)

1. 作用:该寄存器提供8位的优先级字段给GIC所支持的每一个中断。该字段用于存储相应中断的优先级。

2. Bit assignments

Figure 4-3 GICD_IPRIORITYR bit assignments

Table 4-3 GICD_IPRIORITYR bit assignments

3. 中断ID与该寄存器之间的联系: (如果中断ID为m,有如下关系)

?对应的GICD_IPRIORITYRn数目→ n = m / 4

?相应的GICD_IPRIORITYRn寄存器地址→ ( (0x400)+(4*n) )

? 中断ID对应中断优先级字段的偏移为→ m % 4:

—字节偏移0对应的寄存器位[7:0]

—字节偏移0对应的寄存器位[15:8]

—字节偏移0对应的寄存器位[23:16]

—字节偏移0对应的寄存器位[31:24]

4.4 CPU Interface Register Description

4.4.1 CPU interface Control Register

1. 作用:使能发送CPU interface上的中断到与之相连的处理器,并提供CPU interface额外的顶层控制。在GICv2中,这包括对中断结束(EOI)行为的控制。

2. 寄存器的位分配是不同的,在这个寄存器安全与非安全的副本中。

①图4-3和表4-3展示了在GICv2中实现了安全扩展,该寄存器的非安全副本的位分配:

Figure 4-4 GICC_CTLR bit assignments, GICv2 with Security Extensions, Non-secure copy

Table 4-4 GICC_CTLR bit assignments, GIC2 with Security Extensions, Non-secure copy ② 图4-4和表4-4展示GICC_CTLR 寄存器位分配:

? GICv2中

: — 实现了安全扩展

— 在实现了安全扩展,该寄存器的安全副本

? 在 GICv1实现了安全扩展,该寄存器的安全的副本

Figure 4-5 GICC_CTLR bit assignments, GICv2 without Security Extensions or Secure

Table 4-5 GICC_CTLR bit assignments, GICv2 without Security Extensions or Secure 4.4.2 Interrupt Priority Mask Register(GICC_PMR)

1. 作用:提供了一个中断优先级过滤器。只有优先级比在该寄存器中的值更高的中断才可以发送给处理器。

2. 使用限制:如果GIC实现了安全扩展那么:

? 不安全的访问该寄存器只可以读写优先级相对应较低一半范围的值

? 如果安全的写入已编程的GICC_PMR中的值对应于更高优先级的范围,那么:

—任何不安全的读GICC_PMR返回0x00,不管该寄存器中的值是多少;

—任何不安全的写GICC_PMR被忽略。

3. Bit assignments

Figure 4-6 GICC_PMR bit assignments

Table 4-6 GICC_PMR Register bit assignments

4.4.3 Interrupt Acknowledge Register(GICC_IAR)

1. 作用:处理器读取该寄存器来获取被发送中断的中断ID,这也被当作对该中断的应答。

2. Bit assignments

Figure 4-7 GICC_IAR bit assignments

Table 4-7 GICC_IAR bit assignments

4.4.4 End of Interrupt Register(GICC_EOIR)

1 . 作用:处理器对该寄存器进行写入以通知CPU interface:

? 处理器已经完成了具体中断的处理

? 在GICv2实现中,当GICC_CTLR.EOImode位设置成1,指明接口应该对具体的中断执行priority drop。

2. 使用限制:写入寄存器必须从中断应答寄存器对应的最新的有效的读,一次有效的读是指会返回有效的中断号而不是伪中断号。

3. Bit assignments

Figure 4-8 GICC_EOIR bit assignments

Table 4-8 GICC_EOIR bit assignments

4.4.5 Deactivate Interrup Register(GICC_DIR)

1. 作用:当中断优先级下降从中断失效中分离,对该寄存器的写入会使具体的中断失效。

2. 使用限制:写入该寄存器只有一个影响当:

?对于GIC的实现不包括安全扩展,GICC_CTLR.EOImode位被设置为1

? 对于GIC的实现包括安全扩展:

—对于安全访问该寄存器,GICC_CTLR.EOImodeS位被设置为1

—对于不安全的访问该寄存器,GICC_CTLR.EOImodeNS位被设置为1

3. Bit assignments:

Figure 4-9 GICC_DIR bit assignments

Table 4-9 GICC_DIR bit assignments