哈工大 2005 年 春 季学期

集成电路设计原理

试 题 A

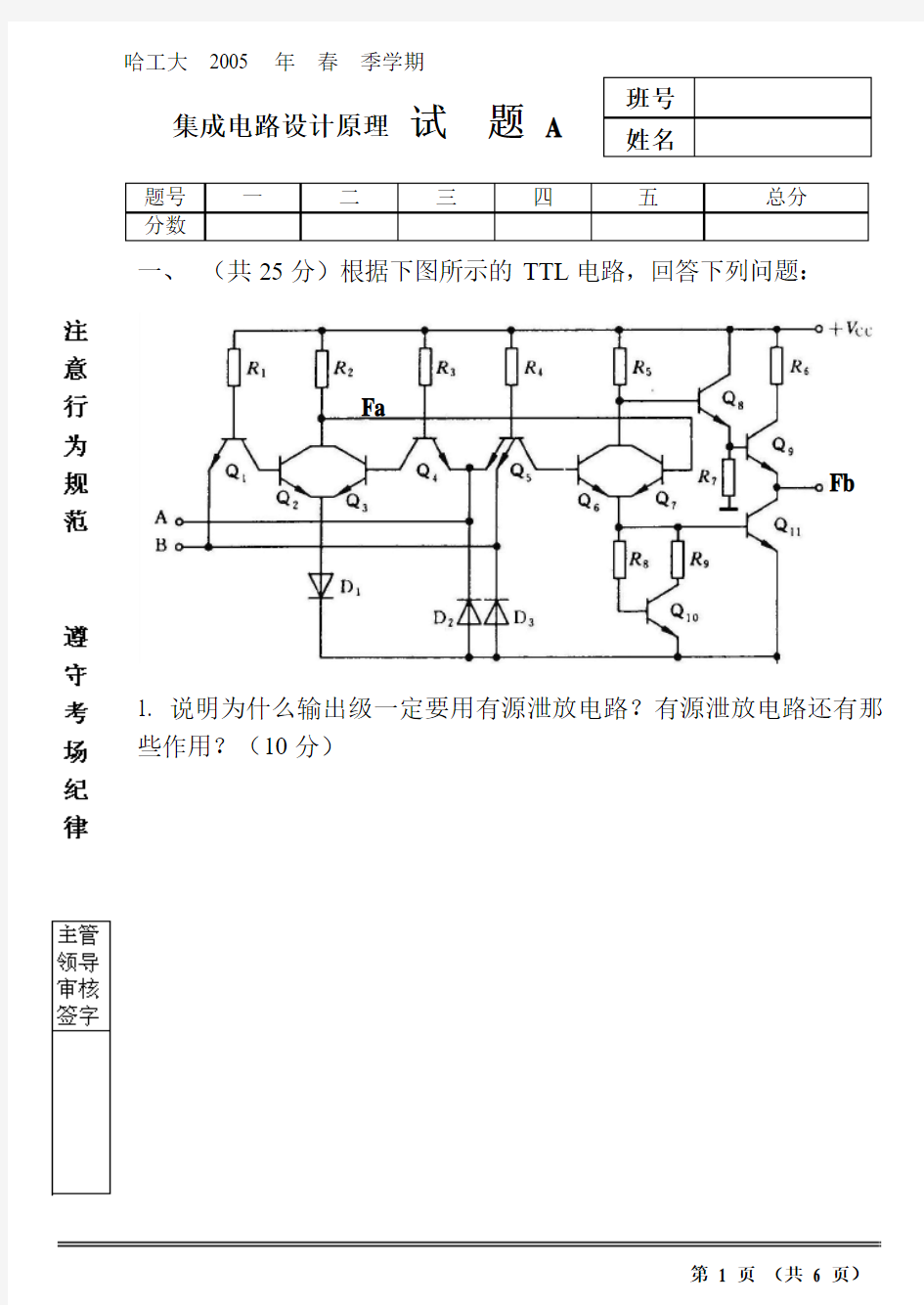

一、 (共25分)根据下图所示的TTL 电路,回答下列问题:

1. 说明为什么输出级一定要用有源泄放电路?有源泄放电路还有那些作用?(10分)

Fa

Fb

2.说明电路完成的逻辑功能,写出Fa和Fb两点的逻辑表达式。(6分)

3.如果该电路的输出低电平偏高,在版图设计上如何改进?(5分)

4.图中二极管D1、D2、D3分别起什么作用?(4分)

二、(20分)右图是一个CMOS门电路,说明它

的功能,写出逻辑表达式。如果将它用作反相器,有哪几种方式?这几种方式所构成的反相器在性能上有何不同?为什么?

A B

试题:集成电路设计原理A班号:姓名:

三、(20分)根据逻辑表达式F=AB+C,画出静态E/E饱和负载NMOS电路图和静态CMOS电路图;说明哪种是有比电路,哪种是无比电路,哪种需要抗闩锁设计,哪种需要抗静电设计;抗闩锁设计有哪些措施?

四、(25分)右图是采用典型PN结隔

Vdd

离工艺设计的版图。

1)按工艺流程顺序写出图中用到的掩

模版,并在图中标出;

2)根据版图画出对应的电路图;

3)分析电路功能,说明各个元器件的

作用。

Gnd

五、阐述全定制法和门阵列法设计集成电路的优缺点(10分)

2011年天津市高等院校春季招生统一考试 英语 本试卷分第Ⅰ卷(选择题)和第Ⅱ卷(非选择题)两部分,第Ⅰ卷1至9页,第Ⅱ卷10至11页。共150分。考试时间120分钟。 第Ⅰ卷(选择题共100分) 注意事项: 1. 答第Ⅰ卷前,考生务必将自己的姓名、准考号、考试科目涂写在答题卡上,并将 本人考试用条形码贴在答题卡的贴条形码处。 2. 每小题选出答案后,用2B铅笔把答案卡上对应题目的答案标号涂黑。如需改动, 用橡皮擦干净后,再选涂其他答案标号。答在试卷上的无效。 3. 考试结束,监考员将本试卷和答题卡一并收回。 Ⅰ.语音辨别(共5小题,每小题1分,共5分)在下列每组单词中,有一个单词的画线部分与其他单词的画线部分的读音不同。找出这个单词。 1. A.some B.both C.cold D.post 2. A.home B.hard C.help D.hour 3. A.bread B.meat C.leave D.team 4. A.chair B.chemist C.check D.churcht 5. A.try B.sky C.pity D.July Ⅱ.单项选择(共15小题,每小题1分,共15分)从每小题的四个选项中,选出可以填入空白处的最佳选项。 6.Let’s take a rest, ? A.can we B,shall we C.do we D.will we 7.Are you willing to help people who are need ? 英语第1页(共9页) A.for B.with C.in D.at 8.Wntering the house, I found Jane at the desk and something. A.sit;write B.sittting;weiting C.sat;wrote D.to sit;to write 9.—May I speak to Mr.Green? —. A.May I take a message ? B.Who are you ? C.Speaking. D.Yes,you will. 10.This is the school Istudied three years ago. A.where B.what C.that D.which 11.To you the truth, I don’t really like her. A.say B.talk C.speak D.tell 12.—Shall we make it six o’clock ? —。 A.Sorry for the trouble B.It’s a pleasure C.Ok,I will be there on time D.Not at all 13.You’d better at school during the holidays. A.staying B.not to say C.to stay D.not stay 14.Of my three students ,one is from England,and are from New York. A.the other B.the others C.another D.others 15.A snake was found in the backyard. Adeath B.died C.dead D.not stay 16.It more than 400 men two years to build the highway. A.carried B.cost C.spent D.took 17.Our class is 40 students. A.made up of B.made of C.made from D.made in 18.We don’t consider necessary for them to move into that house. 英语第2页(共9页)

集成电路设计复习题 绪论 1.画出集成电路设计与制造的主要流程框架。 2.集成电路分类情况如何? 集成电路设计 1.层次化、结构化设计概念,集成电路设计域和设计层次 2.什么是集成电路设计?集成电路设计流程。 (三个设计步骤:系统功能设计逻辑和电路设计版 图设计) 3.模拟电路和数字电路设计各自的特点和流程 4.版图验证和检查包括哪些内容?如何实现? 5.版图设计规则的概念,主要内容以及表示方法。为什么需要指定版图设计规则? 6.集成电路设计方法分类? (全定制、半定制、PLD) 7.标准单元/ 门阵列的概念,优点/缺点,设计流程 8.PLD设计方法的特点,FPGA/CPLD的概念 9.试述门阵列和标准单元设计方法的概念和它们之间的异同点。 10.标准单元库中的单元的主要描述形式有哪些?分别在IC设计的什么阶段应用? 11.集成电路的可测性设计是指什么? Soc设计复习题 1. 什么是SoC? 2. SoC设计的发展趋势及面临的挑战? 3. SoC设计的特点? 4. SoC设计与传统的ASIC设计最大的不同是什么? 5. 什么是软硬件协同设计? 6. 常用的可测性设计方法有哪些? 7. IP 的基本概念和IP分类 8. 什么是可综合RTL代码? 9. 么是同步电路,什么是异步电路,各有什么特点? 10. 逻辑综合的概念。 11. 什么是触发器的建立时间( Setup Time ),试画图进行说明。 12. 什么是触发器的保持时间( Hold Time ),试画图进行说明。 13. 什么是验证,什么是测试,两者有何区别? 14. 试画图简要说明扫描测试原理。

绪论 1、画出集成电路设计与制造的主要流程框架。 2、集成电路分类情况如何? 双极型 数字模拟混合电路按应用领域分类 集成电路设计 1.层次化、结构化设计概念,集成电路设计域和设计层次分层分级设计和模块化设计.将一个复杂的集成电路系统的设计问题分解为复杂性较低的设计级别,集成电路MSI 按规模分 LSI 类VLSI ULSI GSI 数字电 按功能分类模拟电 路组合逻辑电路 路时序逻辑电路 路线性电路 路非线性电路 单片集成 按结构分类 混合集 成 SSI PMOS 电M路OS 型NMOS CMOS B iMOS B iMOS 型 B iCMOS 电 厚路膜混合集 成 电路 薄路膜混合集 成 电路

精品文档第五章:数列历年高考题 一、单项选择题 1、(2003)已知数列{a n }是等差数列,如果a 1 =2,a 4 =-6则前4项的和S 4 是() A -8 B -12 C -2 D 4 2、(2004年)在?ABC中,若∠A、∠B、∠C成等差数列,且BC=2,BA=1,则AC 等于() A 33 2 B 1 C 3 D 7 3、(2004)在洗衣机的洗衣桶内用清水洗衣服,如果每次能洗去污垢的 3 2,则要使存留在衣服上的污垢不超过最初衣服上的2℅,该洗衣机至少要清洗的次数是()A 2 B 3 C 4 D 5 4、(2005年)在等差数列{a n }中,若a 1 +a 12 =10,则a 2 +a 3 + a 10 +a 11 等于() A 10 B 20 C 30 D 40 5、(2005年)在等比数列{a n }中,a 2 =2,a 5 =54,则公比q=() A 2 B 3 C 9 D 27 6、(2006年)若数列的前n项和S n =3n n - 2,则这个数列的第二项a 2 等于() A 4 B 6 C 8 D 10 7、(2007)为了治理沙漠,某农场要在沙漠上栽种植被,计划第一年栽种15公顷,以后每一年比上一年多栽种4公顷,那么10年后该农场栽种植被的公顷数是()A 510 B 330 C 186 D 51 8、(2007年)如果a,b,c成等比数列,那么函数y=ax2+bx+c的图像与x轴的交点 个数是() A 0 B 1 C 2 D 1或2 9、(2007年)小王同学利用在职业学校学习的知识,设计了一个用计算机进行数字变换的游戏,只要游戏者输入任意三个数a 1 ,a 2 ,a 3 ,计算机就会按照规则:a 1 + 2a 2 - a 3 ,a 2 + 3a 3 ,5a 3 进行处理并输出相应的三个数,若游戏者输入三个数后,计算机输出了29,50,55三个数,则输入的三个数依次是() A 6,10,11 B 6,17,11 C 10,17,11 D 6,24,11 10、(2008年)在等差数列{a n }中,若a 2 +a 5 =19,则a 7 =20,则该数列的前9项和是() A 26 B 100 C 126 D 155 11、(2009年)在等差数列{a n }中,若a 1 +a 8 =15,则S 8 等于() A 40 B 60 C 80 D 240 12、(2009年)甲、乙两国家2008年的国内生产总值分别为a(亿元)和4a(亿元),甲国家计划2028年的国内生产总值超过乙国,假设乙国的年平均增长率为,那么甲国的年平均增长率最少应为() A 9.6℅ B 9.2℅ C 8.8℅ D 8.4℅ 13、(2009年)如果三个实数a,b,c成等比数列,那么函数y=ax2+bx+c与y=ax+b 在同一坐标系中的图像可能是() 14、(2010年)已知2,m,8构成等差数列,则实数m的值是() A 4 B 4或-4 C 10 D 5 x

CH1 1.按规模划分,集成电路的发展已经经历了哪几代?它的发展遵循了一条业界著名的定律,请说出是什么定律? 晶体管-分立元件-SSI-MSI-LSI-VLSI-ULSI-GSI-SOC。MOORE定律 2.什么是无生产线集成电路设计?列出无生产线集成电路设计的特点和环境。 拥有设计人才和技术,但不拥有生产线。特点:电路设计,工艺制造,封装分立运行。 环境:IC产业生产能力剩余,人们需要更多的功能芯片设计 3.多项目晶圆(MPW)技术的特点是什么?对发展集成电路设计有什么意义? MPW:把几到几十种工艺上兼容的芯片拼装到一个宏芯片上,然后以步行的方式排列到一到多个晶圆上。意义:降低成本。 4.集成电路设计需要哪四个方面的知识? 系统,电路,工具,工艺方面的知识 CH2 1.为什么硅材料在集成电路技术中起着举足轻重的作用? 原材料来源丰富,技术成熟,硅基产品价格低廉 2.GaAs和InP材料各有哪些特点? P10,11 3.怎样的条件下金属与半导体形成欧姆接触?怎样的条件下金属与半导体形成肖特基接触? 接触区半导体重掺杂可实现欧姆接触,金属与掺杂半导体接触形成肖特基接触 4.说出多晶硅在CMOS工艺中的作用。P13 5.列出你知道的异质半导体材料系统。 GaAs/AlGaAs, InP/ InGaAs, Si/SiGe, 6.SOI材料是怎样形成的,有什么特点? SOI绝缘体上硅,可以通过氧隔离或者晶片粘结技术完成。特点:电极与衬底之间寄生电容大大减少,器件速度更快,功率更低 7. 肖特基接触和欧姆型接触各有什么特点? 肖特基接触:阻挡层具有类似PN结的伏安特性。欧姆型接触:载流子可以容易地利用量子遂穿效应相应自由传输。 8. 简述双极型晶体管和MOS晶体管的工作原理。P19,21 CH3 1.写出晶体外延的意义,列出三种外延生长方法,并比较各自的优缺点。 意义:用同质材料形成具有不同掺杂种类及浓度而具有不同性能的晶体层。外延方法:液态生长,气相外延生长,金属有机物气相外延生长 2.写出掩膜在IC制造过程中的作用,比较整版掩膜和单片掩膜的区别,列举三种掩膜的制造方法。P28,29 3.写出光刻的作用,光刻有哪两种曝光方式?作用:把掩膜上的图形转换成晶圆上的器件结构。曝光方式有接触与非接触两种。 4.X射线制版和直接电子束直写技术替代光刻技术有什么优缺点? X 射线(X-ray)具有比可见光短得多的波长,可用来制作更高分辨率的掩膜版。电子束

集成电路设计实习Integrated Circuits Design Labs I t t d Ci it D i L b 单元实验三(第二次课) 模拟电路单元实验-差分放大器版图设计 2007-2008 Institute of Microelectronics Peking University

实验内容、实验目的、时间安排 z实验内容: z完成差分放大器的版图 z完成验证:DRC、LVS、后仿真 z目的: z掌握模拟集成电路单元模块的版图设计方法 z时间安排: z一次课完成差分放大器的版图与验证 Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page1

实验步骤 1.完成上节课设计放大器对应的版图 对版图进行、检查 2.DRC LVS 3.创建后仿真电路 44.后仿真(进度慢的同学可只选做部分分析) z DC分析:直流功耗等 z AC分析:增益、GBW、PM z Tran分析:建立时间、瞬态功耗等 Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page2

Display Option z Layout->Options ->Display z请按左图操作 Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page3

由Schematic创建Layout z Schematic->Tools->Design Synthesis->Layout XL->弹出窗口 ->Create New->OK >选择Create New>OK z Virtuoso XL->Design->Gen From Source->弹出窗口 z选择所有Pin z设置Pin的Layer z Update Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page4

机密★启用前 山东省2019年普通高校招生(春季)考试 数学试题 1. 本试卷分卷一(选择题)和卷二(非选择题)两部分,满分120分,考试时间120分钟。考生请在答题卡上答题,考试结束后,请将本试卷和答题卡一并交回。 2.本次考试允许使用函数型计算器,凡使用计算器的题目,除题目有具体要求外,最后结果精确到0.01。 卷一(选择题共60分) 一、选择题(本大题20个小题,每小题3分,共60分。在每小题列出的四个选项中,只有一项符合题目要求,请将符合题目要求的选项字母代号选出,并填涂在答题卡上) 1.已知集合M={0, 1},N={1, 2},则MUN等于 A. {1} B. {0, 2} C. {0,1, 2} D. 2.若实数a, b满足ab>0, a+b>0,则下列选项正确的是 A. a>0, b>0 B. a>0, b<0 C. a<0, b>0 D. a<0, b<0 3.已知指数函数y=a x, 对数函数 y=log b x的图像 如图所示,则下列关系式成立的是 A. 0 3 1 3 8 98 9 7 9 7 9 C.6 D. 4-2 7.对于任意角α, β,“α=β”是“sinα=sinβ”的 A.充分不必要条件 B. 必要不充分条件 C.充要条件 D. 既不充分也不必要条件 8.如图所示,直线l⊥OP,则直线l的方程是 A.3x-2y=0 B. 3x+2y-12=0 C. 2x-3y+5=0 D. 2x+3y-13=0 9. 在(1+x)n的二项展开式中,若所有项的系数之和为64,则第3项是 A. 15x3 B. 20x3 C. 15x2 D. 20x2 10.在Rt△ABC中,∠ABC=90°,AB=3, BC=4, M是线段AC上的动点.设点M到BC的距离为x,△MBC的面积为y,则y关于x的函数是 A. y=4x,x∈(0, 4] B. y=2x, x∈(0, 3] C. y=4x,x∈(0,+∞) D. y=2x, x∈(0, +∞) 11.现把甲、乙等6位同学排成一列, 若甲同学不能排在前两位,且乙同学必须排在甲同学前面(相邻或不相邻均可),则不同排法的种数是 A..360 B.336 C.312 D.240 12. 设集合M={-2, 0, 2, 4},则下列命题为真命题的是 A. Vα∈M,α是正数 B. Vb∈M, b是自然数 C.?c∈M,c是奇数 D. ?d∈M, d是有理数 13.已知sinα = ,则cos 2α的值是 A. B.- C. D.- 14. 已知y=f(x) 在R上是减函数,若f(|a|+1) 2013年天津市高等院校春季招生统一考试 数 学 本试卷分第Ⅰ卷(选择题)和第Ⅱ卷(非选择题)两部分,第Ⅰ卷1至9页,第Ⅱ卷10至12页。共150分。考试时间120分钟。 第Ⅰ卷(选择题 共75分) 注意事项: 1. 答第Ⅰ卷前,考生务必将自己的姓名、准考号、考试科目涂写在答题卡上,并将本人考试用条形码贴在答题卡的贴条形码处。 2. 每小题选出答案后,用2B 铅笔把答案卡上对应题目的答案标号涂黑。如需改动,用橡皮擦干净后,再选涂其他答案标号。答在试卷上的无效。 3. 考试结束,监考员将本试卷和答题卡一并收回。 —、单项选择题:本大题共15小题,每小题5分,共75分。在每小题给出的四个选项 中,只有一项是最符合题目要求的。 1.已知全集U={1,2,3,4,5,6},A, ={1,2,3,6}, B={3, 5},则B ∩=C u A= A.{5} B.{3,4,5} C.{3,4,5,6} D.{1,2,3,4,5,6} 2.已知log a 4=-21 ,则a= A. 161 B=2 C.8 D=16 3.条件“χ=0”是结论“yx=0”的 A.充分但不必要条件 B.必要但不充分条件 C.充要条件 D. 既不充分也不必要条件 4.函数f(x)= 1) 12lg(2-X -X 的定义域是 A.( 21 ,-∞) B.( 21 ,1)∪(1,+∞) C.(-1,1)∪(1,+∞) D. (0,1)∪(1,+∞) 第一页 5.在数列{a n }中,若a 2=2,且满足a n =3n-1(n ≥2),则α5= A.162 B. 54 C.17 D. 14 6.若α=323 π,则α是 A.第一象限的角 B.第二象限的角 C.第三象限的角 D.第四象限的角 7.在下列函数中,周期为π的奇函数是 A. f(x)=sinx B. f(x)=cosx C. f(x)=sin2x D. f(x)=cos2x 8.在ΔABC 中,已知AB=4,BC=6,∠B=60°,则AC= A. 28 B.2 7 C. 76 D.219 9.已知点A=(3,1),B=(1,2),C=(1,2),D=(2,1),则向量??→?+?→?BD AC 2的坐标是 A. (6,-3) B.(4,1) C. (-1,2) D.(3,0) 10.若点M (1,2),N (-2,3),P(4,b)在同一条直线上,则b= A. 21 B. 23 C. 1 D. -1 11.已知点a (-1,0),B(5,0),则线段AB 为直径的圆的标准方程是 A.(x-3)2+y 2=3 B. (x-3)2+y 2=9 C.(x-2)2+y 2=3 D. (x-2)2+y 2=9 12.顶点为坐标原点,准线为直线x=-1的抛物线的标准方程是 A. y 2=4x B. y 2=-4x C. y 2=2x D. y 2=-2x 13.已知如图所示的正方体ABCD -A 1B 1C 1D 1的直观图 , 应该为虚线的线段共有 A.1条 B.2条 第二页 集成电路设计练习题2009 1、说明一个半导体集成电路成本的组成。 2、简述CMOS工艺流程。简述CMOS集成电路制造的过程中需要重复进行的工艺步骤。 3、描述你对集成电路工艺的认识。列举几种集成电路典型工艺。工艺上常提到0.25,0.18指的是什么?简述CMOS工艺技术的发展趋势。 4、你知道的集成电路设计的表达方式有哪几种? 5、现有一用户需要一种集成电路产品,要求该产品能够实现如下功能:y=lnx 其中,x为4位二进制整数输入信号。y为二进制小数输出,要求保留两位小数。电源电压为3~5v 假设公司接到该项目后,交由你来负责该产品的设计,试讨论该产品的设计全程。 6、请谈谈对一个系统设计的总体思路。针对这个思路,你觉得应该具备哪些方面的知识? 7、描述你对集成电路设计流程的认识。 8、集成电路前端设计流程,后端设计流程,相关的工具。 9、从RTL synthesis到tape out之间的设计flow,并列出其中各步使用的tool. 10、简述FPGA等可编程逻辑器件设计流程。 11、简述半定制数字电路的设计流程。 12、简要说明并比较数字集成电路几种不同的实现方法。 13、什么是集成电路的设计规则。 14、同步电路和异步电路的区别是什么? 15、画出CMOS电路的晶体管级电路图,实现Y=AB+C(D+E) 16、在CMOS电路中,要有一个单管作为开关管精确传递模拟低电平,这个单管你会用P管还是N 管,为什么? 17、硅栅COMS工艺中N阱中做的是P管还是N管,N阱的阱电位的连接有什么要求? 18、名词解释:VLSI, CMOS, EDA, VHDL, DRC, LVS, DFT, STA 19、画出CMOS与非门的电路,并画出波形图简述其功能。 实验一 EDA软件实验 一、实验目的: 1、掌握Xilinx ISE 9.2的VHDL输入方法、原理图文件输入和元件库的调用方法。 2、掌握Xilinx ISE 9.2软件元件的生成方法和调用方法、编译、功能仿真和时序仿真。 3、掌握Xilinx ISE 9.2原理图设计、管脚分配、综合与实现、数据流下载方法。 二、实验器材: 计算机、Quartus II软件或xilinx ISE 三、实验内容: 1、本实验以三线八线译码器(LS74138)为例,在Xilinx ISE 9.2软件平台上完成设计电 路的VHDL文本输入、语法检查、编译、仿真、管脚分配和编程下载等操作。下载芯片选择Xilinx公司的CoolRunner II系列XC2C256-7PQ208作为目标仿真芯片。 2、用1中所设计的的三线八线译码器(LS74138)生成一个LS74138元件,在Xilinx ISE 9.2软件原理图设计平台上完成LS74138元件的调用,用原理图的方法设计三线八线译 码器(LS74138),实现编译,仿真,管脚分配和编程下载等操作。 四、实验步骤: 1、三线八线译码器(LS 74138)VHDL电路设计 (1)三线八线译码器(LS74138)的VHDL源程序的输入 打开Xilinx ISE 6.2编程环境软件Project Navigator,执行“file”菜单中的【New Project】命令,为三线八线译码器(LS74138)建立设计项目。项目名称【Project Name】为“Shiyan”,工程建立路径为“C:\Xilinx\bin\Shiyan1”,其中“顶层模块类型(Top-Level Module Type)”为硬件描述语言(HDL),如图1所示。 图1 点击【下一步】,弹出【Select the Device and Design Flow for the Project】对话框,在该对话框内进行硬件芯片选择与工程设计工具配置过程。 山东省2018年普通高校招生(春季)考试 数学试题 卷一(选择题,共60分) 一、选择题(本大题20个小题,每小题3分,共60分。在每小题列出的四个选项中,只有一项符合题 目要求,请将符合题目要求的选项字母代号选出,并填涂在答题卡上) 1.已知集合M={a,b},N={b,c},则M I N 等于 (A )? (B ){b} (C ){a,c} (D ){a,b,c} 2.函数f (x )= 1 1-+ +x x x 的定义域是 (A )(-1,+∞) (B )(-1,1)Y (1,+∞) (B )[-1,+∞) (D )[-1,1)Y (1,+∞) 3.奇函数y=f (x )的局部图像如图所示,则 (A)f (2)> 0 > f (4) (B)f (2)< 0 < f (4) (C)f (2)> f (4)> 0 (D)f (2)< f (4)< 0 4.不等式1+lg <0的解集是 (A ) )101,0()0,101(Y - (B) )10 1 ,101(- (C) )10,0()0,10(Y - (D )(-10,10) 5.在数列{a n }中, a 1=-1,a 2=0,a n+2=a n+1+a n ,则a 5等于 (A )0 (B )-1 (C )-2 (D )-3 6. 在如图所示的平角坐标系中,向量AB uuu r 的坐标是 (A)(2,2) (B)(-2,-2) (C)(1,1) (D)(-1,-1) 7.圆()()2 2 111x y ++-=的圆心在 (A) 第一象限 (B) 第二象限 (C) 第三象限 (D) 第四象限 8.已知a b R ∈、,则“a b >”是“ 22a b >”的 (A)充分不必要条件 (B)必要不充分条件 (C)充要条件 (D)既不充分也不必要条件 9. 关于直线:20,l x -+=,下列说法正确的是 (A)直线l 的倾斜角60° (B)向 量v = ,1)是直线l 的一个方向向量 x y (第6题图) (第3题图) 集成电路设计习题答案-章 CH1 1( 按规模划分,集成电路的发展已经经历了哪几代,它的发展遵循了一条业界著名的定 律,请说出是什么定律, 晶体管-分立元件-SSI-MSI-LSI-VLSI-ULSI-GSI-SOC。MOORE定律 2( 什么是无生产线集成电路设计,列出无生产线集成电路设计的特点和环境。 拥有设计人才和技术,但不拥有生产线。特点:电路设计,工艺制造,封装分立运行。 环境:IC产业生产能力剩余,人们需要更多的功能芯片设计 3( 多项目晶圆(MPW)技术的特点是什么,对发展集成电路设计有什么意义, MPW:把几到几十种工艺上兼容的芯片拼装到一个宏芯片上,然后以步行的方式排列到一到多个晶圆上。意义:降低成本。 4( 集成电路设计需要哪四个方面的知识, 系统,电路,工具,工艺方面的知识 CH2 1( 为什么硅材料在集成电路技术中起着举足轻重的作用? 原材料来源丰富,技术成熟,硅基产品价格低廉 2(GaAs和InP材料各有哪些特点? P10,11 3(怎样的条件下金属与半导体形成欧姆接触,怎样的条件下金属与半导体形成肖特基接触, 接触区半导体重掺杂可实现欧姆接触,金属与掺杂半导体接触形成肖特基接触4(说出多晶硅在CMOS工艺中的作用。 P13 5(列出你知道的异质半导体材料系统。 GaAs/AlGaAs, InP/ InGaAs, Si/SiGe, 6(SOI材料是怎样形成的,有什么特点? SOI绝缘体上硅,可以通过氧隔离或者晶片粘结技术完成。特点:电极与衬底之 间寄生电容大大减少,器件速度更快,功率更低 7. 肖特基接触和欧姆型接触各有什么特点, 肖特基接触:阻挡层具有类似PN结的伏安特性。欧姆型接触:载流子可以容易 地利用量子遂穿效应相应自由传输。 8. 简述双极型晶体管和MOS晶体管的工作原理。P19,21 CH3 1( 写出晶体外延的意义,列出三种外延生长方法,并比较各自的优缺点。 意义:用同质材料形成具有不同掺杂种类及浓度而具有不同性能的晶体层。外 延方法: 液态生长,气相外延生长,金属有机物气相外延生长 2(写出掩膜在IC制造过程中的作用,比较整版掩膜和单片掩膜的区别,列举 三种掩膜的制造方法。P28,29 3(写出光刻的作用,光刻有哪两种曝光方式, 作用:把掩膜上的图形转换成晶 圆上的器件结构。曝光方式有接触与非接触两种。 4(X射线制版和直接电子束直写技术替代光刻技术有什么优缺点, X 射线(X-ray)具有比可见光短得多的波长,可用来制作更高分辨率的掩膜 版。电子束 扫描法,,由于高速电子的波长很短,分辨率很高 5( 说出半导体工艺中掺杂的作用,举出两种掺杂方法,并比较其优缺点。 热扩散掺杂和离子注入法。与热扩散相比,离子注入法的优点如下:1.掺杂的 过程可通过调整杂质剂量与能量来精确控制杂质分布。2.可进行小剂量的掺杂。3. 1、 CMOS analog circuit design by P.E.ALLEN 评定:理论性90 实用性70 编写 100 精彩内容:运放的设计流程、比较器、 开关电容 这本书在国内非常流行,中文版也 翻译的很好,是很多人的入门教材。 建议大家读影印版,因为ic 领域 的绝大部分文献是以英文写成的。 如果你只能读中文版,你的学习资料 将非常有限。笔者对这本书的评价 并不高,认为该书理论有余,实用性 不足,在内容的安排上也有不妥的地 方,比如没有安排专门的章节讲述反 馈,在小信号的计算方面也没有巧方法。本书最精彩的部分应该就是运放的设计流程了。这是领域里非常重要的问题,像Allen 教授这样将设计流程一步一步表述出来在其他书里是没有的。这正体现了Allen 教授的治学风格:苛求理论的完整性系统性。但是,作为一项工程技术,最关键的是要解决问题,是能够拿出一套实用的经济的保险的方案。所以,读者会发现,看完最后一章关于ADC/DAC 的内容,似乎是面面俱到,几种结构的ADC 都提到了,但是当读者想要根据需求选择并设计一种ADC/DAC 时,却无从下手。书中关于比较器的内容也很精彩,也体现了Allen 教授求全的风格。不过,正好其它教科书里对比较器的系统讲述较少,该书正好弥补了这一缺陷。Allen 教授是开关电容电路和滤波器电路的专家。书中的相关章节很适合作为开关电容电路的入门教材。该书的排版、图表等书籍编写方面的工作也做的很好。像Allen 这样的理论派教授不管在那所大学里,大概都会很快的获得晋升吧。另外,Allen 教授的学生Rincon Moca 教授写的关于LDO 的书非常详尽,值得一读。 2、 CMOS Circuit Design Layout and Simulation CMOS Mixed-Signal Circuit Design by R.J.Baker 评定:理论性80 实用性100 编写80 精彩内容:数据转换器的建模和测量、hspice 网表这本书的风格和Allen 的书刚好相反: 理论的系统性不强,但是极为实用,甚至给出 大量的电路仿真网表和hspice 仿真图线。 这本书的中文版翻译的也很好。最近出了第二 版,翻译人员换了,不知道翻译的水平如何。 不过,第二版好贵啊~~ Baker 教授在工业界 的实战经验丰富,曾经参加过多年的军方项目 的研发,接收器,锁相环,数据转换器,DRAM 等曾设计过。所以,书中的内容几乎了包含 了数字、模拟的所有重要电路,Baker 教授 山东省2016年普通高校招生(春季)考试 财经类专业知识试题 本试卷分卷一(选择题)和卷二(非选择题)两部分。满分200分,考试时间120分钟。考试结束后,将本试卷和答题卡一并交回。 卷一(选择题,共100分) 一、选择题(本大题50个小题,每小题2分,共100分。在每小题列出的四个选项中,只有一项符合题目要求,请将符合题目的要求的选项字母代号选出,填涂在答题卡上) 1、将货币资金转化为储备资金这项资金运动过程是 A筹资过程 B生产过程 C供应过程 D 销售过程 2、下列选项中,属于负债特征的是 A 由企业拥有或控制的资源 B 是企业承担的现时义务 C 债权人参与企业管理和利润分配 D 预期会给企业带来经济利益 3、下列选项中,属于所有者权益账户的是 A ‘所得税费用’账户 B ‘制造费用’账户 C ‘投资收益’账户 D ‘利润分配’账户 4、发生试算平衡表的理论基础的是 A 借贷记账法的记账的规则 B 会计基本等式 C 收入—费用=利润 D 会计核算方法 5、下列选项中导致负债和所有者权益同时变动的经济业务是 A 将现金存入银行 B 董事会分配现金股利 C 用现金分配股利 C 盈余公积转增资本 6、下列选项属于外来原始凭证的是 A 销售商品开具的增值税专用发票 B 银行结算凭证 C 入库单 D 限额领料 7、为了分清会计事项处理的先后顺序便于记账凭证与会计账簿之间的核对,确保记账凭证的 完整,填制记账凭证时应符合的要求是 A 依据真实 B 内容正确 C 连续编号 D 简明扼要 8、企业采购原材料一批,买价4000元,签发一张转账支票付款2000元,余款暂欠,应填制 A 付款凭证和转账凭证 B 收款凭证和转账凭证 C 收款凭证和付款凭证 D 两张转账凭证 9 、下列明细账中,允许采用卡片式账簿的是 A 固定资产明细账 B 应收账款明细账 C 本年利润明细账 D 实收资本明细账 10、库存现金日记账一般应采用 A 活页式账簿、三栏式账页 B 活页式账簿、多栏式账页 C 订本式账簿、三栏式账页 C 订本式账簿、数量金额式账页11、为了查明其债权债务明细,需要将企业的债权债务明细账余额与对方单位的账面记录进行 核对,这是对账工作中的 A 账实核对 B 帐账核对 C 账证核对 D 帐表核对 12、对库存现金清点后应将清查结果填入 A 账存实存对比表 B 盘存表 C 库存现金盘点报告表 D 银行存款余额调节表 13、对家电企业的产成品仓库进行财产清查,一般采用的清查方法是 A 实地盘点法 B 账实核对法 C 帐卡核对法 D 技术测算盘点法 14、各种会计核算形式的主要区别是 A 登记明细账的依据和方法不同 B 总账的格式不同 C 登记总分类账的依据和方法不同 D 编制财务报表的依据不同 15、科目汇总表核算形式的优点是 A 简单明了,易于了解 B 较详细地反应经济业务的发生情况 C 能够反应各账户之间的对应关系 D 可以起到试算平衡的作用 16、对财产清查中出现的溢余,检查后无法查明原因的,经批准后计入 A 管理费用 B 其他应收款 C 营业外收入 D 其他应付款 17、对随同产品出售而不单独计价的包装物,企业应按其实际成本结转到 A “其他业务成本”账户 B “销售费用”账户 C “制造费用”账户 D “管理费用”账户 18、下列选项中,符合无形资产摊销核算要求的是 A 自无形资产可供使用时起,至不在作为无形资产确认是止 B 当月增加的无形资产,当月不摊销,下月开始摊销 C 当月减少的无形资产,当月照常摊销,从下月停止摊销 D 当月增加的无形资产,当月不摊销;当月减少的无形资产,当月停止摊销 19、下列有关工资薪金的原始记录中,作为企业发放工资,进行工资分配依据的是 A 考勤记录和工时记录 B 产量记录 C 销售记录 D 工资汇总表 20、企业签发的银行承兑汇票,如果到期无力支付票款,应贷记的账户是 A “应付账款”账户 B “短期借款”账户 C “应收票据”账户 C “其他应付款”账户 21、下列长期借款的利息,应计入管理费用的是 A 归属于生产经营期间的长期借款利息 B 用于固定资产购建的长期借款,在尚未到达预定可使用状态前发生的利息 C 在固定资产达到预定可使用状态后发生的长期借款利息 D 归属于筹建活动的长期借款利息 22、负责制定并公布国家统一的会计制度管理的机构是 A 全国人民代表大会 B 国务院 C 国务院财政部 D 中国人民银行 23、企业在建立与实施内部控制时所遵循的原则包括 A 公开透明原则 B 成本效益原则 C 公正原则 D 诚实信用原则 1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么? 集成电路的发展过程: ?小规模集成电路(Small Scale IC,SSI) ?中规模集成电路(Medium Scale IC,MSI) ?大规模集成电路(Large Scale IC,LSI) ?超大规模集成电路(Very Large Scale IC,VLSI) ?特大规模集成电路(Ultra Large Scale IC,ULSI) ?巨大规模集成电路(Gigantic Scale IC,GSI) 划分集成电路规模的标准 2.超大规模集成电路有哪些优点? 1. 降低生产成本 VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少. 2.提高工作速度 VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得. 3. 降低功耗 芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降. 4. 简化逻辑电路 芯片内部电路受干扰小,电路可简化. 5.优越的可靠性 采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。 6.体积小重量轻 7.缩短电子产品的设计和组装周期 一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度. 3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。 1、形成N阱 2、形成P阱 3、推阱 4、形成场隔离区 5、形成多晶硅栅 6、形成硅化物 7、形成N管源漏区 8、形成P管源漏区 9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺 4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么? 互连线的要求 低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化) 与器件之间的接触电阻低 长期可靠工作 可能的互连线材料 金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率) 《模拟集成电路设计原理》期末考试 一.填空题(每空1分,共14分) 1、与其它类型的晶体管相比,MOS器件的尺寸很容易按____比例____缩小,CMOS电路被证明具有_ 较低__的制造成本。 2、放大应用时,通常使MOS管工作在_ 饱和_区,电流受栅源过驱动电压控制,我们定义_跨导_来 表示电压转换电流的能力。 3、λ为沟长调制效应系数,对于较长的沟道,λ值____较小___(较大、较小)。 4、源跟随器主要应用是起到___电压缓冲器___的作用。 5、共源共栅放大器结构的一个重要特性就是_输出阻抗_很高,因此可以做成___恒定电流源_。 6、由于_尾电流源输出阻抗为有限值_或_电路不完全对称_等因素,共模输入电平的变化会引起差动输 出的改变。 7、理想情况下,_电流镜_结构可以精确地复制电流而不受工艺和温度的影响,实际应用中,为了抑制 沟长调制效应带来的误差,可以进一步将其改进为__共源共栅电流镜__结构。 8、为方便求解,在一定条件下可用___极点—结点关联_法估算系统的极点频率。 9、与差动对结合使用的有源电流镜结构如下图所示,电路的输入电容C in为__ C F(1-A)__。 10、λ为沟长调制效应系数,λ值与沟道长度成___反比__(正比、反比)。 二.名词解释(每题3分,共15分) 1、阱 解:在CMOS工艺中,PMOS管与NMOS管必须做在同一衬底上,其中某一类器件要做在一个“局部衬底”上,这块与衬底掺杂类型相反的“局部衬底”叫做阱。 2、亚阈值导电效应 解:实际上,V GS=V TH时,一个“弱”的反型层仍然存在,并有一些源漏电流,甚至当V GS .. ;. 山东省2018 年普通高校招生(春季) 考试 英语试卷 本试卷分一卷(选择题)和二卷(非选择题)两部分,满分80 分, 考试时间60 分钟。考生请在答题卡上答题,考试结束后,请将本试卷和 答题卡一并回收。 卷一(选择题,50 分) 一、英语知识运用(本题30 个小题,每小题 1 分,共30 分。在每小题列出的四个选项中,只有一项符合题目要求,请将符合题目要求的选项 字母代号选出,并填涂在答题卡上。) 1. -- .He is from Hang Kong. --Nice to meet you. A.Let me introduce myself B.Let me introduce Tom C.This is Tom speaking D.Have a good time,Tom 2. --Could you give me some on how to improve my spoken English? --I’m so glad to hear that! A.movements B.suggestions C.greetings D.treatments 3. --Nowadays people are encouraged eat fruit and vegetables to keep . A.honest B.nervous C.healthy D.proud 4. --Why do you like swimming? --Because I find very relaxing. A. it B.one C.those D.these 5. -- ? Good idea. A.Why not join us in the game B.How did you know that C.When would you like to come D.What would you like for dinner 6.-- beautiful the park is !We may have a picnic here this weekend . --Sound great. A.What a B.What C.How a D.How 7.--It’s an impossible task for us to finish the building in half a year. --Yes,it will take one year. A.at least B.at last C.in time D.in order 8.--I think Mary is a successful woman. --I agree with you .She has nearly all her dreams. A. realized B.won C.understood D.believed 9. -- ? --Chinese folk music. A.How about going for a walk B.What’s your favorite sports C.How do you like Chinese D.What are you interested in 10. Where will the football game be held? FOOTBALL GAME Between the Sunday Club & the Youth Club On Friday ,May 18 7:00 p.m.---9:00 p.m. All football lovers are welcome! A.At the Sunny Club B.At the Youth Club C.At the City Stadium D.At the City Park 11.IF Bob wants to apply for the job, he needs to . DRIVER WANTED Full-time,5 days a week $ 20 per hour 5years’experience with a driver’s license Call Susan at 555-778-6356 A work part-time B work six days a week C call Sandy at 555-778-6356 D have work experience 12. I hope that you can come and celebrate the Spring Festival w ith my family. A do B did C does D done 13. -- ? ---I’d like to buy some traditional Chinese souvenirs. A What can I do for you B How much do they cost C What size do you take D What color do you like 14. --What did you do last weekend? ---I Mount Tai with my friends. A climb B climbed C will climb D am climbing 15.--I wonder a film. --Once a month. A.when you see B.where you see C.whether you have seen D.how often you see 16.--Who is the man by the window. --He is our English teacher. A. sits B.sat C.sitting D.is sitting 17.--Downing Hotel.Can I help you? -- . A. I’m looking for a dress for my daughter. B. I’d like to buy a ticket for tonight’s film. C. I’d like to reserve a double room for this Friday. D. I’ve caught a bad cold and’I m feeling terrible. 18.I felt very tired after a day‘s hard work, I went to bed early. A. but B. or C.while D.so 19. --I haven’t finished my dinner yet. --Hurry up ! Our friends for us. A. are waiting B.were waiting B. had waiting D.waited 20. -- I have found somewhere to live, I will send you my address. A. Unless B.Until C.Though D.Once 21. --Thank you for taking care of my pet dog while I was on business. -- . A. Best wishes B.My pleasure C.No,thanks D.Goodbye春季高考历年真题-2013年天津市春季高考数学试卷

集成电路设计练习题

专用集成电路

2018山东春季高考数学试题(卷)

集成电路设计习题答案-章

模拟集成电路设计经典教材

山东省2016年春季高考财经类专业知识试题

《超大规模集成电路设计》考试习题(含答案)完整版

模拟集成电路设计期末试卷..

2018年春季高考英语真题