第四章

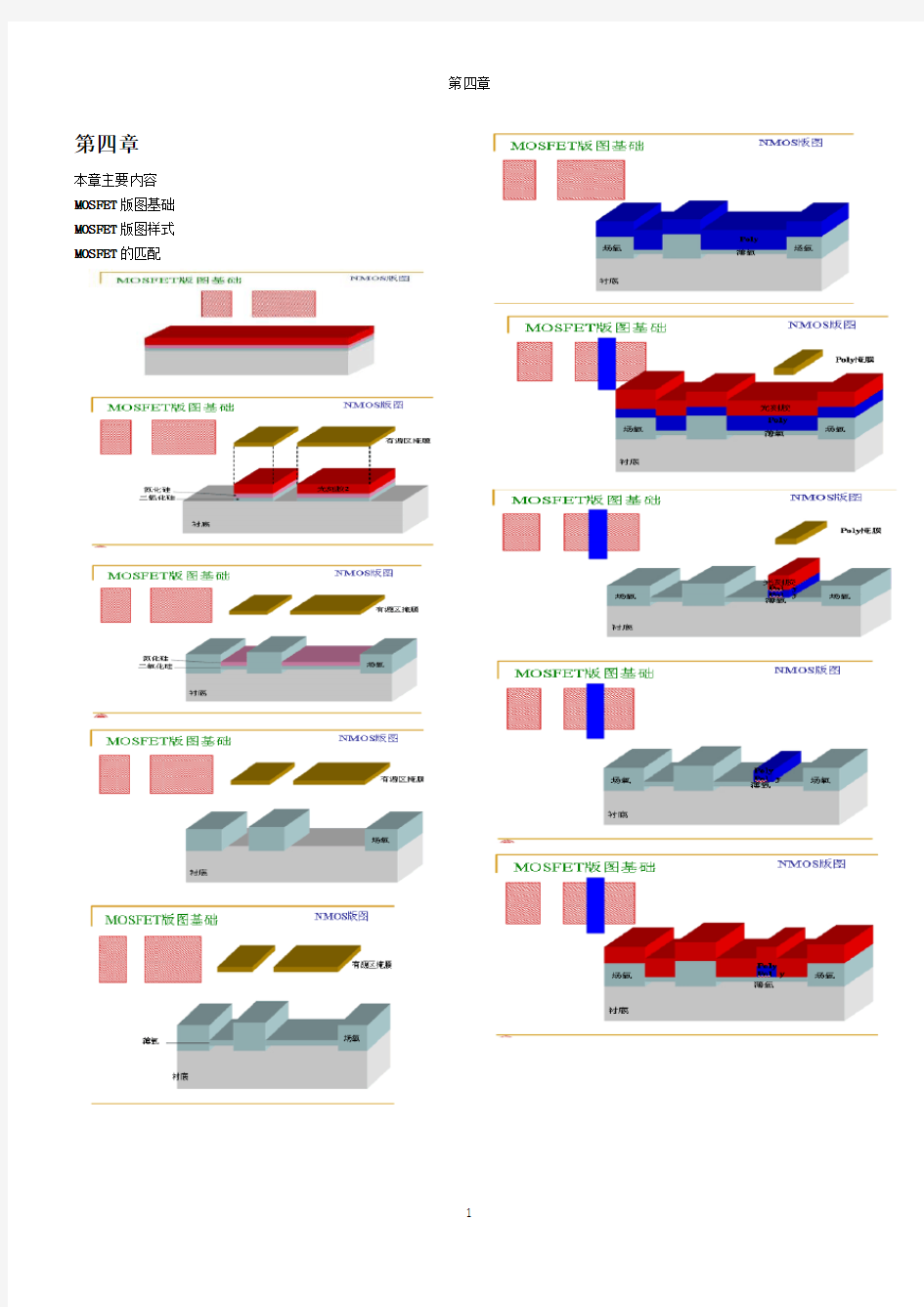

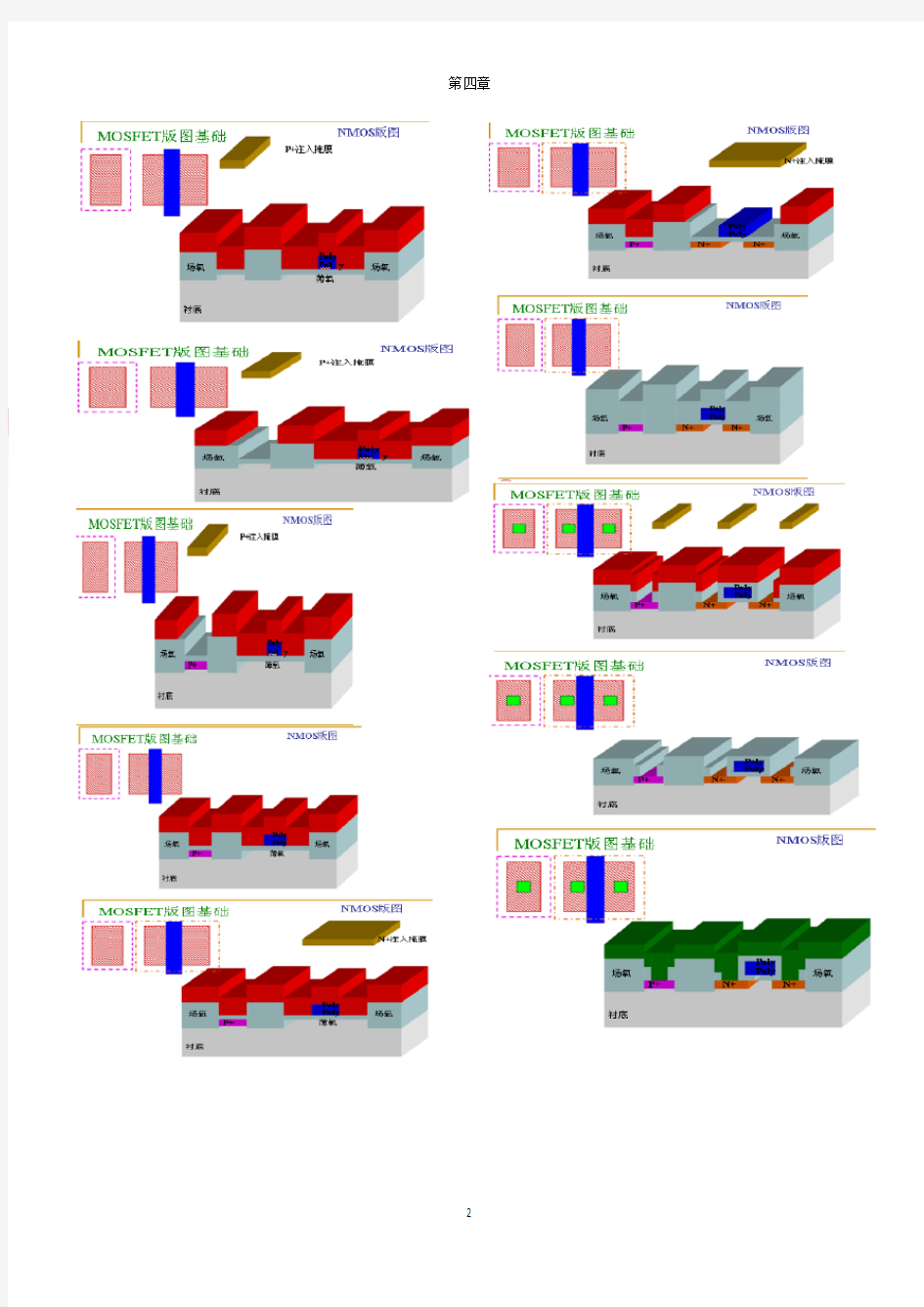

本章主要内容MOSFET版图基础MOSFET版图样式MOSFET的匹配

沟道终止注入

多晶和P+ 或N+图形相交的地方就可能形成自对准的多晶硅栅晶体管,在某些情况下,厚氧化层也可以形成MOSFET 。在生长场氧之前,向场区注入合适的杂质 可以提高晶体管的阈值电压,现代工艺中将能够提供场区掺杂的方法叫沟道终止注入。

目前大部分CMOS 工艺中使用两个互补的沟道终止注入来

同时抑制NMOS 和PMOS 的寄生沟道。对所有的P 场区进行P 沟道终止注入来增大NMOS 厚氧阈值电压;对N 型场区进行N 型沟道终止注入来增大NMOS 厚场阈值电压。

MOSFET 版图样式 使用叉指结构使源/漏的接触孔面积达到最小 通过将版图的对称性最小化电路失配

使用低阻通路避免大电流流过该器件时造成较大压降 保护关键节点,避免非正常节点注入

有利于减小寄生现象

容易实现匹配使电路更加对称

MOS 晶体管的尺寸、形状和方向会影响它们之间的互相匹配。

1.阈值电压失配大小与有源区栅面积的平方根成反比,栅面积的增大有助于减小局部不规则影响,因而大尺寸晶体管比小尺寸晶体管能够更加精确匹配。

2.工艺尺寸的缩小改善了阈值电压的失配,氧化层越薄,工艺跨导越大,使得阈值电压失配越小,如此间接改善了MOSFET 的电压匹配。所以薄栅氧的晶体管的匹配程度优于厚栅氧的晶体管。但是在电压工作范围较大的情况下,注意薄氧化层晶体管容易受沟道长度调制效应的影响。

3.工作在不同栅源电压下的短沟道晶体管,沟道长度调制效应会引起严重的失配。晶体管的习题失配与其源漏电压差成正比,与沟道长度成反比。在匹配精度要求不是很高的电流分配网络,可以使用长沟道器件来减小沟道长度调制效应。在高精度情况下,可以让匹配晶体管工作在相同源漏电压下,加入级联减小沟道长度调制效应影响。

4.方向一致性

MOSFET 的工艺跨导取决于载流子的迁移率,所以沿着不同

晶轴的MOS 在应力下表现不同的跨导,为了避免由应力产生的失配,晶体管的取向应该一致

氢化作用

匹配MOSFET 金属连线版图的不同会在原本相同的器件中引入大的失配。这种失配的原因在于结构上方存在(或缺少金属),导致了不完全话的氢化诱发了失配。

覆盖金属MOSFET 和没有覆盖金属的MOSFET 之间可能出现高达20%的系统漏电流失配。金属边缘的下方的氢扩散产生阈值电压梯度,从而造成被覆盖器件之间明显的失配,所以在关键的匹配晶体管的有源栅区上方不应该进行金属化。在任何情况下,两只匹配晶体管上方的金属化版图必须相同。

当然在次要器件可以完全在金属下方或者可以有金属穿过。

填充金属和MOSFET 匹配

现代工艺中经常使用CMP

的方法得到细线光刻所需的高平

整度平面。通常需要额外添加金属来满足一定的金属覆盖率。版图工具可以自动生成Dummy金属,但是这种方法可能导致在匹配的MOSFET上方放置金属图形。所以版图设计者必须去除掉软件在匹配金属上方的Dummy金属。

在版图设计中设计者必须留心规则中有关填充金属区域之间的距离限制来保证一定的平整度。

热效应和应力效应

另一种重要的失配;类型是由大范围的变化引起的。

1.氧化层厚度梯度:

相距较近的器件具有非常相近的氧化层厚度,但是相距较远的器件氧化层厚度有很大的区别,这些差别直接影响了阈值电压的失配。

2.应力梯度:

mos晶体管的阈值电压与应力无关,所以应力对电压的匹配几乎没有影响。存在的很小的影响可能是因为应力使硅的带隙电压发生了变化,其引起的阈值电压的变化一般不超过几毫伏,通过共质心版图可以进一步减小。

3.热梯度:

阈值电压随温度升高而降低,速率大约-2mV/℃。一般通过共质心版图来改善匹配状况。

本章重点

1、CMOS 反相器版图及剖面图

2、两输入与非门(或非门)版图

3、宽沟道器件叉指结构版图画法

4、版图设计中背栅接触孔的作用及各种结构的背栅接触

5、电路设计中如何减小失调电压或失调电流

6、共质心结构进行匹配MOSFET 的布局(电流镜和差分对)

第5章CMOS版图设计

5.1 版图设计基本概念 5.2 设计规则 5.3 基本工艺层版图 5.4 FET版图尺寸的确定 5.5 逻辑门的版图设计 5.6标准单元版图 5.7 设计层次化 2/78

3/78 5.1 版图设计基本概念 ? 什么是版图设计? ?Layout design :定义各工艺层图形的形状、尺寸以 及不同工艺层的相对位置。

?版图设计的内容 ?布局:就是将组成集成电路的各部分合理地布置在芯 片上。安排各个晶体管、基本单元、复杂单元在芯片 上的位置。 ?布线:就是按电路图给出的连接关系,在版图上布置 元器件之间、各部分之间的连接。设计走线,实现管 间、门间、单元间的互连。 ?尺寸确定:确定晶体管尺寸(W、L)、互连尺寸(宽 度)以及晶体管与互连之间的相对尺寸等。 4/78

?版图设计的目标 ?满足电路功能、性能指标、质量要求 ?尽可能节省面积,以提高集成度,降低成本 ?尽可能缩短连线,以减少复杂度,缩短延时、改善 可靠性 5/78

EDA工具的作用(EDA: Electronic Design Automation) ?版图编辑 ?规定各个工艺层上图形的形状、尺寸、位置(Layout Editor) ?规则检查 ?版图与电路图一致性检查(LVS,Layout Versus Schematic) ?设计规则检查(DRC,Design Rule Checker) ?电气规则检查(ERC,Electrical Rule Checker) ?布局布线 ?Place and route,自动给出版图布局与布线 6/78

亚洲有(48个国家) 东亚(5):中国、蒙古、朝鲜、韩国、日本 东南亚(11):菲律宾、越南、老挝、柬埔寨、缅甸、泰国、马来西亚、文莱、新加坡、印度尼西亚、东帝汶 南亚(7):尼泊尔、不丹、孟加拉国、印度、巴基斯坦、斯里兰卡、马尔代夫 中亚(5):哈萨克斯坦、吉尔吉斯斯坦、塔吉克斯坦、乌兹别克斯坦、土库曼斯坦 西亚(20):阿富汗、伊拉克、伊朗、叙利亚、约旦、黎巴嫩、以色列、巴勒斯坦、沙特阿拉伯、巴林卡塔尔,科威特、阿拉伯联合酋长国(阿联酋)、阿曼、也门、格鲁吉亚、亚美尼亚、阿塞拜疆、土耳其、塞浦路斯 欧洲国家 北欧国家(5):冰岛、挪威、丹麦、瑞典、芬兰。 西欧国家(6):英国、法国、爱尔兰、比利时、荷兰、卢森堡。 中欧国家(7):瑞士、德国、奥地利、捷克、斯洛伐克、波兰、列支敦士登。 南欧国家(18):西班牙、葡萄牙、安道尔、意大利、梵蒂冈、圣马利诺、马耳他、克罗地亚、波斯尼亚和黑塞哥维那(波黑)、斯洛文尼亚、马其顿、塞尔维亚、黑山(门特内哥罗)、阿

尔巴尼亚、罗马尼亚、希腊、保加利亚、匈牙利。 东欧国家(10):前苏联独立的欧洲国家:俄罗斯、乌克兰、白俄罗斯、爱沙尼亚、拉脱维亚、立陶宛、摩尔多瓦、格鲁吉亚、阿塞拜疆、亚美尼亚(后三者在地理位置上应该在亚洲,但和在经济、文化、政治上亚洲关系不密切,所以往往还算在欧洲)。 非洲国家 北非(8):埃及、苏丹、利比亚、突尼斯、阿尔及利亚、摩洛哥、亚速尔群岛、马德拉群岛。 东非(10):埃塞俄比亚、厄立特里亚、索马里、吉布提、肯尼亚、坦桑尼亚、乌干达、卢旺达、布隆迪和塞舌尔。 西非(18):毛里塔尼亚、西撒哈拉、塞内加尔、冈比亚、马里、布基纳法索、几内亚、几内亚比绍、佛得角、塞拉利昂、利比里亚、科特迪瓦、加纳、多哥、贝宁、尼日尔、尼日利亚和加那利群岛。 中非(8):乍得、中非、喀麦隆、赤道几内亚、加蓬、刚果、刚果民主共和国、圣多美和普林西比。 南非(15):赞比亚、安哥拉、津巴布韦、马拉维、莫桑比克、博茨瓦纳、纳米比亚、南非、斯威士兰、莱索托、马达加斯加、科摩罗、毛里求斯、留尼汪、圣赫勒拿等。 北美洲

兰州交通大学电信学院课程设计实验报告 实验名称:负反馈放大电路PCB设计 无线话筒PCB设计(选作) 试验日期: 2012年6月25日 班级: 电子科学与技术092班 姓名: 刘光智 学号: 200910112

Altium designer简介 Altium Designer 提供了唯一一款统一的应用方案,其综合电子产品一体化开发所需的所有必须技术和功能。Altium Designer 在单一设计环境中集成板级和FPGA系统设计、基于FPGA和分立处理器的嵌入式软件开发以及PCB版图设计、编辑和制造。并集成了现代设计数据管理功能,使得Altium Designer成为电子产品开发的完整解决方案-一个既满足当前,也满足未来开发需求的解决方案。 一、实验目的 1.了解并学会运用Altium designer软件绘制简单PCB 2.会运用Alitum designer软件设计库元件 3.掌握印刷电路板布线流程 4.掌握印刷电路板设计的基本原则 二、设计内容 1.要求用Alitum designer软件画出电路原理图 2.按照所画原理图自动生成PCB版图 3.会自己设计元件和库 三、实验步骤(负反馈放大器PCB设计) 1、新建工程、为工程添加项目:在D盘新建一个自己的文件夹重命名为ffk,运行Alitum designer软件,然后单击文件/新建/工程/PCB工程,然后右击所建的PCB工程选择给工程添加原理图,然后添加PCB,建完PCB工程保存工程到D/ffk内,保存时三个文件都命名为ffk.扩展名 2、画原理图:在原理图窗口画出所要画的PCB原理图,本次实验所画电路图如图1: 图1 3、对所画电路图进行编译:点击工程/Compile Document mic.SchDoc,然后点击工程/Compile PCB Project PCB_mic.PrjPCB,然后打开Messages窗口查看编译结果,若有错误按照提示对错误进行改正再编译,直至没有错误结束编译

西安科技大学 高新学院 微电子专业实验报告 专业:微电子 班级:1001 姓名:黄升 学号:1001050120 指导老师:王进军

设计软件:tanner软件 实验目的和要求: 1、掌握L-edit软件的基本设定和集成电路工艺和版图的图层关系。 2、根据性能和指标要求,明确设计要求和规则。 3、电路版图实现过程中电源线的走法。 4、掌握L-edit和S-edit仿真环境,完成异或门的仿真。 5、掌握LVS环境变量。 异或门版图的设计方法: 1、确定工艺规则。 2、绘制异或门版图。 3、加入工作电源进行分析。 4、与LVS比较仿真结果。 实验内容: 完成COMS异或门版图设计,COMS异或门原理如下,要求在S-edit 中画出每一电路元件,并给出输入输出端口及电源线和地线。(一)异或逻辑关系式及真值表:F=A⊕B=A′B+ AB′

(二)原理图: (三)版图:

(四)仿真分析: Main circuit:Module0 .include“E:\ProgramFiles\tannerEDA\T-Spice10.1\models\m12_125.md M1 N3 A Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M2 F B N3 Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M3 F N3 B Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M4 N3 A Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M5 F B A Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M6 F A B Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u v7 Vdd Gnd 5.0 v8 B Gnd pulse(0.05.00 In In 100n 200n) v9 A Gnd pulse(0.05.00 In In 100n 400n) .tran In 800n .print tran v(A) v(B) v(F) End of main circuit:Module0

第一章:绪论 1.1 简介 1.1.1 集成电路 集成电路版图设计是电路系统设计与集成电路工艺之间的中间环节。通过集成电路版图设计,将立体的电路系统转变为二维平面图形。利用版图制作掩模板,就可以由这些图形限定工艺加工过程,最终还原为基于半导体材料的立体结构。 以最基本的MOS器件为例,工艺生产出的器件应该包含源漏扩散区、栅极以及金属线等结构层。按照电路设计的要求,在版图中用不同图层分别表示这些结构层,画好各个图层所需的图形,图形的大小等于工艺生产得到的器件尺寸。正确摆放各图层图形之间的位置关系,绘制完成的版图基本就是工艺生产出的器件俯视图。 器件参数如MOS管的沟道尺寸,由电路设计决定,等于有源区与栅极重叠部分的尺寸。其他尺寸由生产工艺条件决定,不能随意设定。 在工艺生产中,相同结构层相连即可导电,而不同结构层之间是由氧化层隔绝的,相互没有连接关系,只有制作通孔才能在不同结构层之间导电。与工艺生产相对应的版图中默认不同图层之间的绝缘关系,因此可以不必画氧化层,却必须画各层之间的通孔。另外,衬底在版图设计过程中默认存在,不必画出。而各个N阱、P阱均由工艺生产过程中杂质掺杂形成,版图中必须画出相应图形。 1.1.2 版图设计基本知识 版图设计是创建工程制图(网表)的精确的物理描述的过程,而这一物理描述遵守由制造工艺、设计流程以及仿真显示为可行的性能要求所带来的一系列约束。版图设计得好坏,其功能正确与否,必须通过验证工具才能确定。版图的验证通常包括三大部分:设计规则检查(DRC)、电学规则检查(ERC)和版图与电路图对照(LVS)。只有通过版图验证的芯片设计才进行制版和工艺流片。 设计规则的验证是版图与具体工艺的接口, 因此就显得尤为重要, Cadence 中进行版图验证的工具主要有dracula和diva。Dracula 为独立的验证工具, 不仅可以进行设计规则验证(DRC) , 而且可以完成电学规则验证(ERC)、版图与电路验证(LV S)、寄生参数提取(L PE) 等一系列验证工作, 功能强于Diva。 1.2 软件介绍 Cadence是一个大型的EDA软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA设计和PCB板设计。Cadence在仿真、电路图设计、自动布局布线、

实验报告 课程名称:集成电路原理 实验名称:模拟集成电路版图设计与验证小组成员: 实验地点:科技实验大楼606 实验时间:2017年6月19日 2017年6月19日 微电子与固体电子学院

一、实验名称:模拟集成电路版图设计与验证 二、实验学时:4 三、实验原理 1、电路设计与仿真 实验2内容,根据电路的指标和工作条件,然后通过模拟计算,决定电路中各器件的参数(包括电参数、几何参数等),EDA软件进行模拟仿真。 2、工艺设计 根据电路特点结合所给的工艺,再按电路中各器件的参数要求,确定满足这些参数的工艺参数、工艺流程和工艺条件。 3、版图设计 按电路设计和确定的工艺流程,把电路中有源器件、阻容元件及互连以一定的规则布置在Candence下的版图编辑器内。并优化版图结构。 四、实验目的 本实验是基于微电子技术应用背景和《集成电路原理》课程设置及其特点而设置,为IC设计性实验。其目的在于: 1、根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路版图设计,掌握基本的IC版图布局布线技巧。 2、学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的的设计与验证。 通过该实验,使学生掌握CMOS模拟IC版图设计的流程,加深对课程知识的感性认识,增强学生的设计与综合分析能力。 五、实验内容 1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

2、根据实验2所得参数,自主完成版图设计,并掌握布局布线的基本技巧。 3、整理版图生成文件,总结、撰写并提交实验报告。 六、实验仪器设备 (1)工作站或微机终端一台 (2)EDA仿真软件1套 七、实验步骤 1、根据实验指导书掌握Cadence EDA仿真环境的调用。熟悉版图编辑器Layout Editor的使用。了解基本的布局布线方法及元器件的画法。 2、根据实验2所计算验证的两级共源CMOS运放的元器件参数如表1所示,在版图设计器里画出相应的元器件,对V+、V-、V out、V DD、GND的压焊点位置合理化放置,通过金属画线将各个元器件按实验2的电路图合理连接,避免跳线。 表 1运放各器件版图参数

哈尔滨理工大学数字集成电路设计实验报告 学院:应用科学学院 专业班级:电科12 - 1班 学号:32 姓名:周龙 指导教师:刘倩 2015年5月20日

实验一、反相器版图设计 1.实验目的 1)、熟悉mos晶体管版图结构及绘制步骤; 2)、熟悉反相器版图结构及版图仿真; 2. 实验内容 1)绘制PMOS布局图; 2)绘制NMOS布局图; 3)绘制反相器布局图并仿真; 3. 实验步骤 1、绘制PMOS布局图: (1) 绘制N Well图层;(2) 绘制Active图层; (3) 绘制P Select图层; (4) 绘制Poly图层; (5) 绘制Active Contact图层;(6) 绘制Metal1图层; (7) 设计规则检查;(8) 检查错误; (9) 修改错误; (10)截面观察; 2、绘制NMOS布局图: (1) 新增NMOS组件;(2) 编辑NMOS组件;(3) 设计导览; 3、绘制反相器布局图: (1) 取代设定;(2) 编辑组件;(3) 坐标设定;(4) 复制组件;(5) 引用nmos组件;(6) 引用pmos组件;(7) 设计规则检查;(8) 新增PMOS基板节点组件;(9) 编辑PMOS基板节点组件;(10) 新增NMOS基板接触点; (11) 编辑NMOS基板节点组件;(12) 引用Basecontactp组件;(13) 引用Basecontactn 组件;(14) 连接闸极Poly;(15) 连接汲极;(16) 绘制电源线;(17) 标出Vdd 与GND节点;(18) 连接电源与接触点;(19) 加入输入端口;(20) 加入输出端口;(21) 更改组件名称;(22) 将布局图转化成T-Spice文件;(23) T-Spice 模拟; 4. 实验结果 nmos版图

版图设计实验报告 课程名称:集成电路版图设计 姓名: 学号; 专业;电子科学与技术 教师;老师

目录 (一)实验目的 (3) (二)实验步骤 (4) 1,搭建环境···································································································· 2,运用ic6151··························································································· 3,作图··········································································································· 4,Run DRC·························································································· 5,画原理图··························································································· 6,Run LVS········································································································(三)实验总结·················································································································

CMOS反相器电路版图设计与仿真 姓名:邓翔 学号:1007010033 导师:马奎 本组成员:邓翔石贵超王大鹏

CMOS反相器电路版图设计与仿真 摘要:本文是基于老师的指导下,对cadence软件的熟悉与使用,进行CMOS反相器的电路设计和电路的仿真以及版图设计与版图验证仿真。 关键字:CMOS反相器;版图设计。 Abstract:This article is based on the teacher's guidance, familiar with cadence software and use, for CMOS inverter circuit design and circuit simulation and landscape and the landscape design of the simulation. Key word:CMOS inverter;Landscape design. 一引言 20世纪70年代后期以来,一个以计算机辅助设计技术为代表的新的技术改革浪潮席卷了全世界,它不仅促进了计算机本身性能的进步和更新换代,而且几乎影响到全部技术领域,冲击着传统的工作模式。以计算机辅助设计这种高技术为代表的先进技术已经、并将进一步给人类带来巨大的影响和利益。计算机辅助设计技术的水平成了衡量一个国家产业技术水平的重要标志。 计算机辅助设计(Computer Aided Design,CAD)是利用计算机强有力的计算功能和高效率的图形处理能力,辅助知识劳动者进行工程和产品的设计与分析,以达到理想的目的或取得创新成果的一种技术。它是综合了计算机科学与工程设计方法的最新发展而形成的一门新兴学科。计算机辅助设计技术的发展是与计算机软件、硬件技术的发展和完善,与工程设计方法的革新紧密相关的。采用计算机辅助设计已是现代工程设计的迫切需要。 电子技术的发展使计算机辅助设计(CAD)技术成为电路设计不可或缺的有力工具。国内外电子线路CAD软件的相继推出与版本更新,是CAD技术的应用渗透到电子线路与系统设计的各个领域,如电路图和版图的绘制、模拟电路仿

世界地图划分 亚洲有(48个国家) 东亚(5):中国、蒙古、朝鲜、韩国、日本 东南亚(11):菲律宾、越南、老挝、柬埔寨、缅甸、泰国、马来西亚、文莱、新加坡、印度尼西亚、东帝汶 南亚(7):尼泊尔、不丹、孟加拉国、印度、巴基斯坦、斯里兰卡、马尔代夫 中亚(5):哈萨克斯坦、吉尔吉斯斯坦、塔吉克斯坦、乌兹别克斯坦、土库曼斯坦 西亚(20):阿富汗、伊拉克、伊朗、叙利亚、约旦、黎巴嫩、以色列、巴勒斯坦、沙特阿拉伯、巴林卡塔尔,科威特、阿拉伯联合酋长国(阿联酋)、阿曼、也门、格鲁吉亚、亚美尼亚、阿塞拜疆、土耳其、塞浦路斯 欧洲国家 北欧国家(5):冰岛、挪威、丹麦、瑞典、芬兰。 西欧国家(6):英国、法国、爱尔兰、比利时、荷兰、卢森堡。 中欧国家(7):瑞士、德国、奥地利、捷克、斯洛伐克、波兰、列支敦士登。 南欧国家(18):西班牙、葡萄牙、安道尔、意大利、梵蒂冈、圣马利诺、马耳他、克罗地亚、波斯尼亚和黑塞哥维那(波

黑)、斯洛文尼亚、马其顿、塞尔维亚、黑山(门特内哥罗)、阿尔巴尼亚、罗马尼亚、希腊、保加利亚、匈牙利。 东欧国家(10):前苏联独立的欧洲国家:俄罗斯、乌克兰、白俄罗斯、爱沙尼亚、拉脱维亚、立陶宛、摩尔多瓦、格鲁吉亚、阿塞拜疆、亚美尼亚(后三者在地理位置上应该在亚洲,但和在经济、文化、政治上亚洲关系不密切,所以往往还算在欧洲)。 非洲国家 北非(8):埃及、苏丹、利比亚、突尼斯、阿尔及利亚、摩洛哥、亚速尔群岛、马德拉群岛。 东非(10):埃塞俄比亚、厄立特里亚、索马里、吉布提、肯尼亚、坦桑尼亚、乌干达、卢旺达、布隆迪和塞舌尔。 西非(18):毛里塔尼亚、西撒哈拉、塞内加尔、冈比亚、马里、布基纳法索、几内亚、几内亚比绍、佛得角、塞拉利昂、利比里亚、科特迪瓦、加纳、多哥、贝宁、尼日尔、尼日利亚和加那利群岛。 中非(8):乍得、中非、喀麦隆、赤道几内亚、加蓬、刚果、刚果民主共和国、圣多美和普林西比。 南非(15):赞比亚、安哥拉、津巴布韦、马拉维、莫桑比克、博茨瓦纳、纳米比亚、南非、斯威士兰、莱索托、马达加斯加、科摩罗、毛里求斯、留尼汪、圣赫勒拿等。 北美洲 美国、加拿大

实验一:CMOS反相器的版图设计 一、实验目的 1、创建CMOS反相器的电路原理图(Schematic)、电气符号(symbol)以及版图(layout); 2、利用’gpdk090’工艺库实例化MOS管; 3、运行设计规则验证(Design Rule Check,DRC)确保版图没有设计规则错误。 二、实验要求 1、打印出完整的CMOS反相器的电路原理图以及版图; 2、打印CMOS反相器的DRC报告。 三、实验工具 Virtuoso 四、实验内容 1、创建CMOS反相器的电路原理图; 2、创建CMOS反相器的电气符号; 3、创建CMOS反相器的版图; 4、对版图进行DRC验证。

1、创建CMOS反相器的电路原理图及电气符号图 首先创建自己的工作目录并将/home/iccad/cds.lib复制到自己的工作目录下(我的工作目录为/home/iccad/iclab),在工作目录内打开终端并打开virtuoso(命令为icfb &). 在打开的icfb –log中选择tools->Library Manager,再创建自己的库,在当前的对话框上选择File->New->Library,创建自己的库并为自己的库命名(我的命名为lab1),点击OK后在弹出的对话框中选择Attach to an exiting techfile并选择gpdk090_v4.6的库,此时Library manager的窗口应如图1所示: 图1 创建好的自己的库以及inv 创建好自己的库之后,就可以开始绘制电路原理图,在Library manager窗口中选中lab1,点击File->New->Cell view,将这个视图命名为inv(CMOS反相器)。需要注意的是Library Name一定是自己的库,View Name是schematic,具体如图2所示: 图2 inv电路原理图的创建窗口 点击OK后弹出schematic editing的对话框,就可以开始绘制反相器的电路原理图(schematic view)。其中nmos(宽为120nm,长为100nm.)与pmos(宽为240nm,长为100nm.)从gpdk090_v4.6这个库中添加,vdd与gnd在analogLib这个库中添加,将各个原件用wire连接起来,连接好的反相器电路原理图如图3所示:

实验三: 1、反相器直流工作点仿真 1)偏置电压设置:Vin=1V;Vdd=2V; 2)NMOS沟道尺寸设置:Wnmos= ;Lnmos= ; 3)PMOS沟道尺寸设置:设置PMOS的叉指数为3,每个叉指的宽度为变量wf;这样Wpmos=3*wf;设置wf=Wnmos;Lpmos= ; 4)直流工作点仿真结果:Ids= ;Vout= ;NMOS工作在工作区域;PMOS 工作在工作区域;该反相器的功耗为; 2、反相器直流工作点扫描设置 1)偏置电压设置:Vin=1V;Vdd=2V; 2)在直流仿真下设置Wnmos= ;Lnmos= ;扫描参数为PMOS的叉指宽度wf,扫描范围为到;扫描步长为;仿真输出wf为横坐标、Vout为纵坐标的波形曲线; 观察wf对Vout的影响; 3)在上述步骤的基础上,记录输出电压Vout=1V时对应的PMOS的叉指宽度wf= ; 3、扫描反相器的直流电压转移特性 1)在上述步骤的基础上,记录Ids= ;该反相器的功耗Pdc= ; 2)扫描参数为Vin,扫描电压范围为到;扫描步长为;仿真输出Vin为横坐标、Vout为纵坐标的波形曲线;观察Vin对Vout的转移特性;结合理论分析在转移特性曲线上标出A、B、C、D、E五个工作区域; 3)扫描参数为Vin,扫描电压范围为到;扫描步长为;仿真输出Vin为横坐标、Ids为纵坐标的波形曲线;观察Vin对Ids的转移特性;结合理论分析反相器的静态功耗和动态功耗; 4、仿真反相器的瞬态特性 1)为反相器设置负载电容为; 2)设置Vin为Vpluse信号源,高电平为;低电平为;Rise time= ;Fall time= ; 周期为; 3)设置瞬态仿真stop time= ;step= ;maxstep= ; 4)观察仿真结果,该反相器的传输延迟= ;

第一章基本概念 (1) ☆☆集成电路:Integrated Circuit ,缩写IC IC是通过一系列特定的加工工艺,将晶体管、二极管等有源器件和电阻、电容、电感等无源器件,按照一定的电路互连,“集成”在一块半导体晶片(如硅或砷化镓)上,封装在一个外壳内,执行特定电路或系统功能的一种器件。 (2)特征尺寸定义为器件中最小线条宽度(对MOS器件而言,通常指器件栅电极所决定的沟道几何长度),也可定义为最小线条宽度与线条间距之和的一半。 (3)就设计方法而言,设计集成电路的方法可以分为三种方式: 全定制(Full-Custom Design Approach) 半定制(Semi-Custom Design Approach) (标准单元、积木块、门阵列、门海) 可编程IC (PLD:Programmable Logic Device) (PROM 、GAL 、PLA、PAL、PLD 、FPGA ) (4)☆☆积木块法(BB)与标准单元法(sc)不同之处是:第一,它既不要求每个单元(或称积木块)等高,也不要求等宽。每个单元可根据最合理的情况单独进行版图设计,因而可获得最佳性能。设计好的单元存入库中备调用。第二,它没有统一的布线通道,而是根据需要加以分配。 (5)☆☆门阵列方法与门海方法的比较 门阵列方法的设计特点: 设计周期短,设计成本低,适合设计适当规模、中等性能、要求设计时间短、数量相对较少的电路。 不足:设计灵活性较低;门利用率低;芯片面积浪费。 门海方法的设计特点: 门利用率高,集成密度大,布线灵活,保证布线布通率。 不足:仍有布线通道,增加通道是单元高度的整数倍,布线通道下的晶体管不可用。(6)集成电路设计:根据电路功能和性能要求,在正确选择系统配置、电路形式、器件结构、工艺方案和设计规则的情况下,尽量减小芯片面积,降低设计成本,缩短设计周期以保证全局优化,设计出满足需求的集成电路。其最终的输出结果是掩膜版图,通过制版和工艺流片可以得到所需的集成电路。 (7)版图是一组相互套合的图形,各层版图相应于不同的工艺步骤,每一层版图用不同的图案来表示,版图与所采用的制备工艺紧密相关。 (8)版图设计:根据逻辑与电路功能和性能要求以及工艺水平要求来设计光刻用的掩膜版图,是集成电路设计的最终输出。 (9)布图规划:在一定约束条件下对设计进行物理划分,并初步确定芯片面积和形状、单元区位置、功能块的面积形状和相对位置、I/O位置,产生布线网格,还可以规划电源、地线以及数据通道分布。 (10)布局:根据级别最低的功能块中各基本单元直接的连接关系或较高级别的功能块中各较小功能块之间的连接关系,分配各基本单元或较小功能块的位置,使芯片面积尽可能的小。(11)布线:进行单元间或功能块间的连接,合理分配布线空间,使布线均匀,布通率达到百分之百。

福州大学物信学院 《集成电路版图设计》 实验报告 姓名:席高照 学号:111000833 系别:物理与信息工程 专业:微电子学 年级:2010 指导老师:江浩

一、实验目的 1.掌握版图设计的基本理论。 2.掌握版图设计的常用技巧。 3.掌握定制集成电路的设计方法和流程。 4.熟悉Cadence Virtuoso Layout Edit软件的应用 5.学会用Cadence软件设计版图、版图的验证以及后仿真 6.熟悉Cadence软件和版图设计流程,减少版图设计过程中出现的错误。 二、实验要求 1.根据所提供的反相器电路和CMOS放大器的电路依据版图设计的规则绘制电路的版图,同时注意CMOS查分放大器电路的对称性以及电流密度(通过该电路的电流可能会达到5mA) 2.所设计的版图要通过DRC、LVS检测 三、有关于版图设计的基础知识 首先,设计版图的基础便是电路的基本原理,以及电路的工作特性,硅加工工艺的基础、以及通用版图的设计流程,之后要根据不同的工艺对应不同的设计规则,一般来说通用的版图设计流程为①制定版图规划记住要制定可能会被遗忘的特殊要求清单②设计实现考虑特殊要求及如何布线创建组元并对其进行布局③版图验证执行基于计算机的检查和目视检查,进行校正工作④最终步骤工程核查以及版图核查版图参数提取与后仿真 完成这些之后需要特别注意的是寄生参数噪声以及布局等的影响,具体是电路而定,在下面的实验步骤中会体现到这一点。 四、实验步骤 I.反相器部分: 反相器原理图:

反相器的基本原理:CMOS反相器由PMOS和NMOS构成,当输入高电平时,NMOS导通,输出低电平,当输入低电平时,PMOS导通,输出高电平。 注意事项: (1)画成插齿形状,增大了宽长比,可以提高电路速度 (2)尽可能使版图面积最小。面积越小,速度越高,功耗越小。 (3)尽可能减少寄生电容和寄生电阻。尽可能增加接触孔的数目可以减小接触电阻。(4)尽可能减少串扰,电荷分享。做好信号隔离。 反相器的版图: 原理图电路设计: 整体版图:

成绩评定表 学生姓名班级学号7 专业课程设计题目CMOS反相器评 语 组长签字: 成绩 日期20 年月日

课程设计任务书 学院信息科学与工程学院专业 学生姓名班级学号 课程设计题目CMOS反相器 实践教学要求与任务: 1.用tanner软件中的S-Edit编辑CMOS反相器。 2.用tanner软件中的TSpice对CMOS反相器电路进行仿真并观察波形。 3.用tanner软件中的L-Edit绘制CMOS反相器版图,并进行DRC验证。 4.用tanner软件中的TSpice对版图电路进行仿真并观察波形。 5.用tanner软件中的layout-Edit对电路网表进行LVS检验观察原理图与版图的匹配程度。 工作计划与进度安排: 第一周 周一:教师布置课设任务,学生收集资料,做方案设计。 周二:熟悉软件操作方法。 周三~四:画电路图 周五:电路仿真。 第二周 周一~二:画版图。 周三:版图仿真。 周四:验证。 周五:写报告书,验收。 指导教师: 201 年月日专业负责人: 201 年月日 学院教学副院长: 201 年月日

目录 目录............................................................................................................................ III 1.绪论 (1) 1.1设计背景 (1) 1.2设计目标 (1) 2.CMOS反相器 (2) 2.1CMOS反相器电路结构 (2) 2.2CMOS反相器电路仿真 (3) 2.3CMOS反相器的版图绘制 (4) 2.4CMOS反相器的版图电路仿真 (4) 2.5LVS检查匹配 (5) 总结 (7) 参考文献 (8) 附录一:原理图网表 (9) 附录二:版图网表 (10)

设计题目:三输入与或门 一、设计的目的和意义 设计目的: 1、熟悉并认识版图设计规则(DRC)检测 2、熟悉IC制造工艺文件 3、熟练运用软件设计电路和版图、 4、设计意义: 1.配合集成电路设计基础、集成电路设计硬件描述语言、超大规模集成电 路CAD、器件模型CAD、集成电路版图设计、微电子工艺等课程,培养 IC设计的实践能力; 2.进一步掌握基本的集成电路与器件设计和调试的方法与步骤;掌握设计 输入、编译、模拟、仿真、综合、布图、下载及硬件测试等IC设计基本 过程; 3.初步掌握应用典型的HDL(VHDL、Verilog),基于FPGA的IC设计调试 工具、Zeni2003物理设计工具进行集成电路设计、模拟与硬件仿真的方 法和过程; 4.进一步巩固所学IC设计相关的理论知识,提高运用所学知识分析和解决 实际集成电路工程设计问题的能力; 5.经过查找资料、选择方案、设计仿真器件或电路、检查版图设计、撰写 设计报告等一系列实践过程,实现一次较全面的IC设计工程实践训练,通过理论联系实际,提高和培养创新能力,为后续课程的学习,毕业设 计,毕业后的工作打下基础。 二、设计的主要内容和要求 主要内容: 设计一个CMOS结构三输入与或门(F=AB+C)的版图,并作DRC验证。 要求: 1.用三输入的与或非门和一个非门构建与门。 2.与或非门和非门都用CMOS结构实现。 3.利用九天EDA工具PDT画出其相应版图。 4.利用几何设计规则文件进行在线DRC验证并修改版图。

三、试验思想及说明 根据要求1将试验结果所示的表达式 F =AB+C转化为符合要求的逻辑表达式为: 。 画出相关的真值表如下: 用逻辑电路表示为: 然后画出相应的棒状图如下:

实验报告册 课程名称:集成电路版图设计教程姓名: 学号: 院系: 专业: 教师: 2016 年5 月15 日 实验一: OP电路搭建

一、实验目的: 1.搭建实体电路。 2.为画版图提供参考。 3.方便导入网表。 4.熟悉使用cadence。 二、实验原理和内容: 根据所用到的mn管分析各部分的使用方法,简化为几个小模块,其中有两个差分对管。合理运用匹配规则,不同的MOS管可以通过打孔O来实现相互的连接。 三、实验步骤: 1.新建设计库。在file→new→library;在name输入自己的学号;右边选择:attch to……;选择sto2→OK。然后在tools→library manager下就可看到自己建的库。 2.新建CellView。在file→new→CellView;cell栏输入OP,type →选择layout。 3.加器件。进入自己建好的电路图,选择快捷键I进行调用器件。MOS 管,在browse下查找sto2,然后调用出自己需要的器件。

4.连线。注意:若线的终点没有别的电极或者连线,则要双击左键才能终止画线。一个节点只能引出3根线。无论线的起点或是终点,光标都应进入红色电极接电。 5.加电源,和地符号。电源Vdd和地Vss的符号在analoglib库中选择和调用,然后再进行连线。 (可以通过Q键来编辑器件属性,把实验规定的MOS管的width和length数据输入,这样就可以在电路图的器件符号中显示出来) 6.检查和保存。命令是check and save。(检查主要针对电路的连接关系:连线或管脚浮空,总线与单线连接错误等)如果有错和警告,在‘schematic check’中会显示出错的原因,可以点击查看纠正。(画完后查看完整电路按快捷键F,连线一定要尽量节约空间,简化电路) 四、实验数据和结果: 导出电路网表的方法:新建文件OP,file→Export→OP(library browser 选NAND2),NAND.cdl,Analog √

中国地区划分区域划分 地图 Standardization of sany group #QS8QHH-HHGX8Q8-GNHHJ8-HHMHGN#

华北地区:北京市、天津市、河北省、山西省、内蒙古自治区东北地区:辽宁省、吉林省、黑龙江省华东地区:上海市、江苏省、浙江省、安徽省、福建省、江西省、山东省华中地区:河南省、湖北省、湖南省 华南地区:广东省、海南省、广西壮族自治区 西南地区:重庆市、四川省、贵州省、云南省、西藏自治区 西北地区:陕西省、甘肃省、青海省、宁夏回族自治区、新疆维吾尔族自治区 香港特别行政区、澳门特别行政区、台湾省 我国有4个直辖市:北京市、上海市、天津市、重庆市 十五个副省级城市:哈尔滨市、长春市、沈阳市、大连市、济南市、青岛市、南京市、杭州市、宁波市、武汉市、厦门市、西安市、广州市、深圳市、成都市

其中:大连市、青岛市、宁波市、厦门市、深圳市为计划单列市!??????????????????????????????????? 行政区划为: 1、华北地区:北京、天津、河北、山西、内蒙古(5个省、区、市)。 2、东北地区:辽宁、吉林、黑龙江、大连(4个省、市)。 3、华东地区:上海、江苏、浙江、安徽、福建、江西、山东、宁波、厦门、青岛(10个省、市)。 4、中南地区:河南、湖北、湖南、广东、广西、海南、深圳(7个省、区、市)。 5、西南地区:重庆、四川、贵州、云南、西藏(5个省、区、市)。 6、西北地区:陕西、甘肃、青海、宁厦、新疆(5个省、区)。 澳门、香港属特别行政区,台湾由于政治原因现没在化分内,但实际上应属中南区!

CMO反相器电路版图设计与仿真 姓名:邓翔 学号:33 导师:马奎 本组成员:邓翔石贵超王大鹏

CMO反相器电路版图设计与仿真 摘要:本文是基于老师的指导下,对cade nee软件的熟悉与使用, 进行CMO反相器的电路设计和电路的仿真以及版图设计与版图验证仿真。 关键字:CMO反相器;版图设计。 Abstract:This article is based on the teacher's guida nee, familiar with cade nee software and use, for CMOS in verter circuit design and circuit simulation and Iandscape and the Iandscape design of the simulatio n. Key word : CMOS inverter;Landscape design. 一引言 20世纪70年代后期以来,一个以计算机辅助设计技术为代表的新的技术改革浪潮席卷了全世界,它不仅促进了计算机本身性能的进步和更新换代,而且几乎影响到全部技术领域,冲击着传统的工作模式。以计算机辅助设计这种高技术为代表的先进技术已经、并将进一步给人类带来巨大的影响和利益。计算机辅助设计技术的水平成了衡量一个国家产业技术水平的重要标志。 计算机辅助设计(Computer Aided Design,CAD是利用计算机强有力的计算功能和高效率的图形处理能力,辅助知识劳动者进行工程和产品的设计与分析,以达到理想的目的或取得创新成果的一种技术。它是综合了计算机科学与工程设计方法的最新发展而形成的一门新兴学科。计算机辅助设计技术的发 展是与计算机软件、硬件技术的发展和完善,与工程设计方法的革新紧密相关的。采用计算机辅助设计已是现代工程设计的迫切需要。 电子技术的发展使计算机辅助设计(CAD)技术成为电路设计不可或缺的有力工具。国内外电子线路CAD软件的相继推出与版本更新,是CAD技术的应用渗透到电子

中国历代的地理版图变化,从中可以看到华夏民族几千年来到发展、鼎盛和屈辱,总体来说是由弱到强,国土面积由小到大,看后五部令人感叹! 一,夏:夏朝(约前2070-前1600 )是中国史书中记载的第一个世袭制朝代。夏朝活动的主要区域是黄河中下游一带(相当于今山西、河南、河北地区),都城建于安邑。 二,商:商朝(约公元前1600年—约公元前1046年),是中国历史上的第二个朝代,是中国第一个有直接的同时期的文字记载的王朝,夏、商、周并称为中国的“三代”。朝的统治区域,以现在的河南为中心。

三,周:周朝(前1046年—前256年)是中国历史上继商朝之后的第三个王朝。西周,周灭商前,周族活动于黄河上游(今陕西、甘肃一带)。 四,秦:公元前246年,秦王嬴政即位,于前230年至前221年十年间灭掉六国,建立中国历史上第一个大统一王朝——秦朝。

五,西汉:西汉(公元前202年—公元8年12月)是中国历史上继秦朝之后的大一统王朝,共历十二帝,享国二百一十年,史称前汉,与东汉统称为汉朝。

六,东汉:东汉(25年—220年)是中国历史上继秦朝、西汉、新朝之后的大一统王朝,传八世共十四帝,历经一百九十五年,又称后汉,与西汉合称汉朝。

七,三国:公元220年曹丕称魏帝,221年刘备称汉帝,222年孙权建年号,成三国鼎立之势。 八,西晋(公元266年—公元316年)是中国历史上三国时期之后的大一统王朝之一,另与东晋合称晋朝。

九,东晋(317年-420年),是由西晋宗室司马睿南迁后建立起来的政权,建都洛阳的西晋覆亡,史称东晋。 十,南北朝前期(420年-581年)——魏、齐。

目录 第一部分.前言 第二部分.实验的基础知识 第三部分.实验内容 1.cadence virtuoso schematic进行电路图的绘制2.cadence virtuoso analog environment电路性能模拟3.cadence virtuoso layout editor进行版图设计4.cadence virtuoso DRC Extract LVS以及后仿真等。第四部分.附件 1.Cadence schematic simple tutorial 2.cadence virtuoso layout editor tutorial 3.SMIC0.18um library

第一部分.前言 本实验为微电子系专业选修课程《模拟CMOS集成电路设计》的配套实验。本实验围绕如何实现一个给定性能参数要求的简单差分运算放大器而展开。 通过该实验,使得学生能够建立模拟集成电路设计的基本概念,了解设计的基本方法,熟悉模拟CMOS集成电路设计的典型流程,了解在每一个流程中所应用的EDA工具,并能较熟练地使用每个流程对应的设计工具。通过让学生自己分析每个流程中所出现的问题,把课程所学知识联系实际,从而增强学生分析问题、解决问题的能力。 本实验的内容以教材一至十章内容为基础,因此,该实验适合在开课学期的后半部分时间开展。 本实验讲义内容安排如下,首先是前言,其次是基础知识,接下来是实际实验内容,具体分成四个过程,最后是附录。建议在实际实验开始之前依次浏览三个附件文档。

第二部分.实验的基础知识 该实验内容所涉及的基础知识包括两部分:电路方面、流程方面和EDA设计工具使用方面。 1.电路有关的基础知识。 该实验是围绕如何实现基于SMIC0.18um工艺下,一个给定性能参数要求的简单差分运算放大器而展开,因此,以电流镜做负载的基本五管差分运算放大器的性能分析是该实验的理论基础。具体内容在讲义以及课件相关章节中有详细介绍。以下用一张图简单重述该电路的有关性能与各元件参数之间的关系分析结论。 相关的设计公式如下: