时序逻辑电路的自启动设计与仿真

摘要:在时序逻辑电路的设计中,电路能否自启动关系到整个系统的可靠性和稳定性,所以,时序电路的自启动设计是系统设计中的一个重要环节。本文以六位移位型计数器的自启动设计为例,阐明了设计具有自启动功能的时序逻辑电路的原理及方法,总结了利用卡诺图及早发现不能自启动并加以解决的规律。并把该六位移位型计数器的设计在MAX+plusII 软件中进行了仿真,得到了正确的时序波形。

关键词:卡诺图;自启动设计;MAX+plusII

引言

在时序逻辑电路的设计中,当逻辑电路可能出现的总状态数不等于有效状态数时,就会有无效状态出现。如果无效状态能自动回到有效状态,称电路能够自启动;反之,称电路不能自启动。移位型计数器是一种特殊形式的计数器。它由移位寄存器和反馈电路组成,故又称为反馈移位寄存器。然而,这类计数器往往不能自启动。不能自启动的电路就会对电路的可靠性及稳定性形成较大的隐患。当电路加电时,有可能偶然落入无效状态,这时将导致电路无法正常工作;在电路正常工作时,若受到外界的意外干扰,也可能落入无效状态中,此时电路的正常工作也将被终止并出错。所以自启动问题是数字电路系统设计中必须解决的问题。本文以六位移位型计数器的自启动设计为例,介绍了时序电路设计过程中利用卡诺图及早发现不能自启动现象并加以解决的自启动设计方法,并把该设计在MAX+plusII中仿真实现。

1 设计原理与方法[1][2]

利用小规模器件设计时序逻辑电路的步骤一般为:(1)根据设计要求,画出状态转换图(2)分配状态,列状态转换表,填写卡诺图(3)在卡诺图中根据不同的触发器,圈出驱动方程(4)检查电路是否能够自启动,必要时回到第三步修改设计(5)画出逻辑电路图

从以上一般设计步骤中可以看出,检查电路能否自启动这一步是在最后进行的,如果发现电路不能自启动,而设计又要求电路能自启动,就必须回过头来重新修改设计了。那么能否在前边的设计过程中就注意到电路能否自启动,并且在发现不能自启动时采取措施加以解决呢?事实上这是可以做到的,下面通过一个例子来说明。

2 自启动设计剖析[3]

用JK 触发器设计一个模6的移位型计数器(分频)器,要求电路能自启动。

2.1分析设计要求

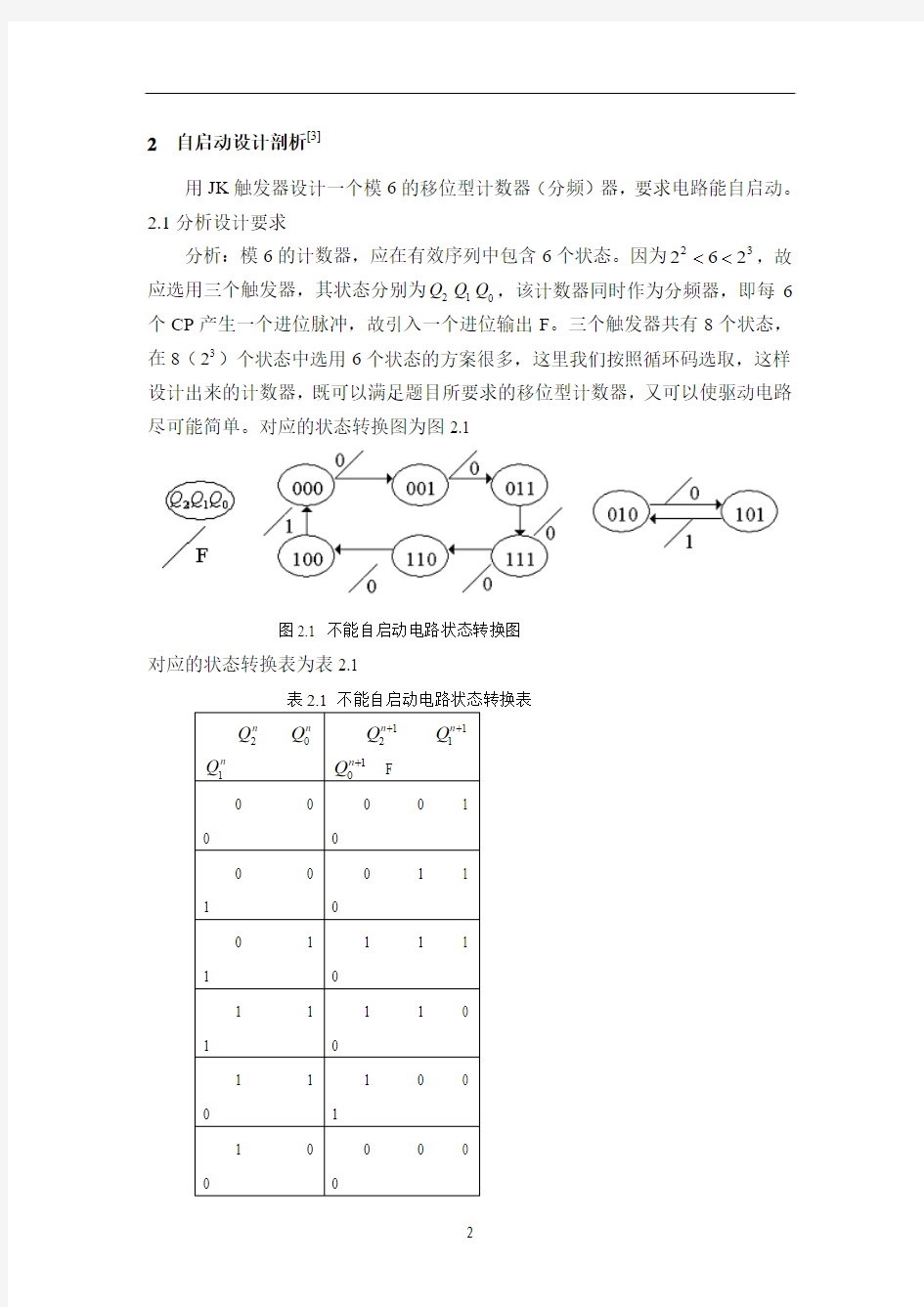

分析:模6的计数器,应在有效序列中包含6个状态。因为32262<<,故

应选用三个触发器,其状态分别为2Q 1Q 0Q ,该计数器同时作为分频器,即每6

个CP 产生一个进位脉冲,故引入一个进位输出F 。三个触发器共有8个状态,

在8(32)个状态中选用6个状态的方案很多,这里我们按照循环码选取,这样

设计出来的计数器,既可以满足题目所要求的移位型计数器,又可以使驱动电路

尽可能简单。对应的状态转换图为图

2.1

图2.1 不能自启动电路状态转换图

对应的状态转换表为表2.1

由状态转换表可画出12+n Q 11+n Q 10

+n Q 和F 的卡诺图2.2。 如果单纯地从化简结果最简单出发化简状态方程,则通过对图2.2的4个卡

诺图圈合并,可直接得到3个触发器的状态方程和输出方程,但为了方便地得到

驱动方程,应使画圈合并的结果能符合JK 触发器的状态方程,比如在图(a )中

对12+n Q 画圈合并时应使结果符合12+n Q =X n Q 2+X n Q 2,即每个乘积项中必须有n Q 2

图2.2 卡诺图 (或n Q 2),下面开始合并求得各状态方程及输出方程。图(a )中,按常规的方

法,应将中间4个小方格合并,合并后的结果为12+n Q =n Q 1,未包含n Q 2(或n Q 2),

所以画圈时应选择能保留2Q 的小方格合并,此时合并的结果为

12

+n Q =n Q 1n Q 2+n Q 1n Q 2,同理可得图(b ),(c ),(d )中的化简结果为11+n Q =n Q 0n Q 1+n Q 0n Q 1,1J =n Q 0,1K =n Q 0;10

+n Q =n Q 2n Q 0+n Q 2n Q 0,0J =n Q 2,0K =n Q 2;F=n Q 2n Q 1。综上所述,这三个触发器的状态方程为:

12+n Q =n Q 1n Q 2+n Q 1n Q 2

11+n Q =n Q 0n Q 1+n Q 0n Q 1

1

0+n Q =n

Q 2_n Q 0+n Q 2n Q 0 对于无效状态010和101分别代入以上状态方程得到状态转换表2.2

表2.2 不能自启动状态转换表

由此可知,电路没有自启动特性,因此要修改设计。

2.2不能自启动电路的设计讨论

在以上合并1的过程中,如果把任意项的X 包括在圈内,则等于把X 取作

了1;如果把任意项X 画在圈外,则等于把X 取为0。这无形中已经为无效状态

指定了次态。如果这个指定的次态属于有效循环中的状态,那么电路是能够自启

动的。反之,如果它也是无效状态,则电路将不能自启动。在后一种情况下,就

需要修改状态方程的化简方式,将无效状态的次态改为某个有效状态。

由分解的12+n Q 11+n Q 10

+n Q 的卡诺图可以看出,在12+n Q 和10+n Q 的分解卡诺图中,010小方格中的任意项X 都划在了圈内,也就是化简时把n Q 2和n Q 0的次态取作了

1,而在11+n Q 的分解卡诺图中,010小方格中的任意项X 划在了圈外,即化简时

将n Q 1的次态定成了0。这就意味着,把无效状态010的次态定成了101这个无

效状态。同时101这个无效状态在分解的卡诺图12+n Q 11+n Q 10

+n Q 中化简时,只有11+n Q 中101小方格中的任意项X 划在了圈内,即在化简时只把n Q 1的次态取作了

1;而在12+n Q 和10+n Q 的分解卡诺图中,101小方格中的任意项X 都划在了圈外,

这也就是说将n Q 2和n Q 0的次态都定为了0,这就意味着把101这个无效状态的次

态定成了010这个无效状态。这样本例中的两个无效状态010和101就形成了一

个死循环,使得这个电路不可能在时钟信号的作用下,自动脱离这个无效循环而

进入有效循环,因此电路不能自启动。

实际上这个问题在前边的设计画圈时就应该注意到,这里的问题就出在将所

有的无效状态010和101的次态,在设计之初就全被定为101和010这两个无效

状态,从而导致每个无效状态都不能直接或间接(即经过其他无效状态后)转为

某一有效状态,从而导致此电路无法自启动。

2.3不能自启动电路的设计修改与规律说明

为使电路能够自启动,解决方法通常是修改无效循环中的状态转换关系,断

开无效循环并把无效状态引至有效状态,从而解决不能自启动的问题。

本例中打断死循环是有技巧的,从状态转换图可看出,本电路已经符合了移

位寄存器的规律:12+n Q =n Q 1,11+n Q =n Q 0。所以在强制将010拉回到有效序列时,

令12+n Q 11+n Q 10

+n Q =100,这样就不用修改触发器2和触发器1的驱动信号,只修改触发器0的设计即可。

也就是在分解的12+n Q 11+n Q 10

+n Q 的卡诺图中,只需将10+n Q 卡诺图中010小方格中的X (即在以前的设计中规定的1)强制地规定为0,按照以上原则重新画圈

合并,得到修正后的状态方程为:

12+n Q =n Q 1n Q 2+n Q 1n Q 2

11+n Q =n Q 0n Q 1+n Q 0n Q 1

10+n Q =n Q 2n Q 1n Q 0+n Q 2n Q 0

相应的驱动方程为: 2J =n Q 1,2K =n Q 1

1J =n Q 0,1K =n Q 0

0J =n Q 2n Q 1,0K =n Q 2

与以前设计中的驱动方程相比较,只有触发器0的驱动信号发生了变化。此时将

010和101代入修正后的状态方程,可得新的状态转换表2.3,对应的状态转换

图为图2.3。从而完成了在一开始的状态化简的过程中就注意到了电路能否自启

动的移位型计数器的自启动设计。

表2.3 能自启动状态转换表

图2.3 能自启动电路状态转换图

3 设计仿真

现在以能自启动的六进制移位计数器为例,利用MAX+plusII软件,输入设计原理图并进行仿真。MAX+plusII软件具有许多优点,它首先具有集成的开发环境,开放的交互界面,并且支持多种形式的设计输入,设计与结构无关;此外它还具有方便的应用环境等优点,因此使用这个软件对电子线路进行设计与仿真十分方便快捷。

3.1基于原理图的设计方法[4][5]

3.1.1创建工程项目

任何一项设计都是一项工程(Project),为了便于对设计文件进行管理,首先建立一个名为ghl的文件夹。

在初始界面中依次执行File,Project,Name命令,调出Project Name(项目名称)对话框,在其中的Drives下拉列表选择驱动器e盘,在Directories栏中选择路径文件夹,e盘ghl,在Project Name文本框中输入项目名称ziqidong,单击ok按钮关闭对话框。

3.1.2输入设计文件

(1) 建立原理图文件

进入原理图编辑环境,依次执行File,New命令,弹出文件类型选择对话框,选择对应的文件类型Graphic Eaditor File(图形编辑器文件),右侧下拉列表中可以选择同一类型文件中的不同保存方式,单击ok按钮关闭该对话框,进入原理图编辑环境。

打开已有文件,依次执行File,Open命令,打开查找文件窗口,在其中选择驱动器e盘,路径ghl和文件类型,符合条件的文件出现在文件列表中,选择所需要的文件ziqidong.gdf后,单击ok按钮关闭该窗口,打开选定的文件。(2) 放置元件

在绘图工具栏的选择工具(箭头)上单击,移动光标到编辑区中合适位置,单击定位,出现闪耀的黑点,依次执行Symbol(符号),Enter Symbol命令,打开Enter Symbol(输入符号)对话框。

在对话框Symbol Libraries列表中选择元件库(其中mf是74系列元件库,prim是基本元件库,mega-lpm是参数化模块库),单击ok按钮选中元件库(本例中选择mf元件库和prim元件库),库中的元件出现在Symbol File列表框中,在其中选择所需元件(74112),单击ok,则元件出现在光标定位处,拖到合适的位

置,松开鼠标左键放置。

重复上述步骤,在mf 中再选一片(74112),在prim 库中选择input (输入端),

output (输出端),and2(二输入与门)放于图中,并移动到合适位置,放置相同

的元件可利用复制和粘贴功能以简化操作。

(3)标注引出端名称

双击引出端标注后删除原有标注,输入新标注(output :012Q Q Q ;input :prn ,

cln ,clk )。

(4)放置连线

移动光标到引出端上,此时光标变为小十字形,按住鼠标左键,拖动鼠标(此

时光标变为大十字形)到另一引出端松开鼠标左键,放置连线。完成连接后的原

理图如图3.1.1和图3.1.2所示。

(5)保存文件

依次执行File 和Save As 命令,保存文件。文件名为ziqidong.gdf 和

bunengziqidong.gdf 。

图3.1.1 能自启动电路原理图

3.1.3编译设计项目

(1) 选择用于编程的器件型号

依次执行Assingn,Device命令,弹出选择器件类型对话框

在Device Family中选择器件系列,在Device中选择器件型号,单击ok 按钮关闭该对话框。

(2)编译文件

执行MAX+plusII中的Compiler命令,弹出Compiler编译对话框,单击Start 按钮开始编译。编译完成后出现编译信息,显示编译中出现的错误和警告。单击“确定”按钮完成编译,若有错误,则需要按信息提示进行修改。

图3.1.2 不能自启动原理图

注意:对图形文件进行修改后,应依次执行File,Project,Set Project to Current File 命令,然后重新执行MAX+plusII中的Compiler命令,进行编译。

3.2时序仿真

3.2.1创建仿真波形文件

执行MAX+plusII中的Waveform Eaditor命令,打开波形编辑环境。与其他环境相比,编辑区中显示波形,左侧的画图工具栏被波形编辑工具栏取代。

依次执行File,End Time命令,在调出的End Time(结束时间)对话框输入结束时间以设定仿真时间长度,单击ok按钮关闭对话框。

执行Options消去Snap to Grid以便能任意设置输入电平值或输入信号周期。

依次执行Node,Enter Nodes from SNF命令,调出Enter Nodes fromSNF(从

SNF输入信号节点)对话框,单击右上方的List按钮,编译文件各节点出现在Available Nodes&Groups列表框中,在Available Nodes&Groups(可用节点/组列表)中选择节点,单击” ”按钮加入到Selected Nodes &Groups(选定节点/组列表)列表框中。

单击ok按钮回到波形编辑窗口,各选中的节点及波形出现在窗口中。

3.2.2 编译波形文件

光标指向待选择的信号(如clock),单击选中该波形(变为黑色)

在编辑区左侧的波形编辑工具栏中选择所需信号类型,单击相应按钮,即可将选定的信号设置为该类型。

依次执行File,Save命令,保存文件(与设计文件ziqidong同名,扩展名为wdf)。

3.2.3运行仿真

依次执行MAX+plusII,Simulator命令,打开仿真时间设置对话框,在其中可以设置仿真的开始时间和终止时间;设置完毕后单击Start按钮,进行仿真。

仿真运行完毕后,出现仿真信息窗口,单击“确定”按钮关闭信息窗口。若存在错误,则按照提示信息修改后重复上述步骤。

在仿真时间设置对话框中单击Open SCF按钮,观察仿真波形,可以利用放大或缩小工具改变仿真波形,以便于观察。完成仿真后的时序图如图3.2.1和图3.2.2所示。

图3.2.1 不能自启动仿真波形

3.3运行时间分析[6]

执行Utilties ,Analyzer Timing 命令,时间分析器开始运行时间分析。结束

后显示表3.2.1和表3.2.2的延时矩阵,从中可以分析各个输出对时钟的延迟时间。

以下表3.2.1和表3.2.2分别是不能自启动电路和能自启动电路中0Q ,1Q ,2Q 和

F 这四个输出对时钟信号的延时矩阵表。

由于这三个JK 触发器之间是相互独立的,故它们的输入与输出之间就有可

能存在着不同的时延。在此以能自启动电路的时延矩阵为例,来说明由于不同触

发器的时延可能不同而造成的仿真波形的微小失真。由能自启动延时矩阵可以看

图3.2.2 能自启动仿真波形

表3.2.1 不能自启动延时矩阵表

表3.2.2 能自启动延时矩阵表

到,第二个触发器的时延比第一个和第三个触发器的时延长0.1ns ,这就是说当

第一和第三个触发器的状态分别由0→1,0→0时,第二个触发器仍然保持在1

状态,故此时的n

Q

2

n

Q

1

n

Q

的次态为110,出现了010→110→100这个循环,显

然010→110→100这个循环与自启动设计原理中打断死循环时将010→100这个循环不一致,故仿真出现了失真。出现这种失真的原因就在于这三个触发器的时延不同,这个失真010→110→100循环仅仅出现了0.1ns,而这0.1ns恰好是第二个触发器的时延比其它两个触发器的时延长出来的0.1ns,由此分析可以说明此电路设计符合自启动设计时的010→100的设计要求。

结束语

由全篇文章的叙述可见,在时序电路的自启动设计过程中,可以充分借助任意项及早发现不能自启动的现象并寻找出有关自启动设计的规律,在设计之初修改设计。因此克服了设计者多次反复修改才能实现自启动设计的局限性,从而缩短了设计周期,提高了设计效率。

参考文献

[1]王毓银.数字电路逻辑设计[M].北京:高等教育出版社,1999.178—240

[2]康华光.电子技术基础(数字部分)[M].北京:高等教育出版社,1999.164—299

[3]李中震.数字电路与逻辑设计[M].成都:成都电讯工程学院出版社,1989.123—211

[4]谭会生,张昌凡.EDA技术及应用[M].西安:西安电子科技大学出版社,2001.209—231

[5]潘松,黄继业.EDA技术实用教程[M].北京:科学出版社,2005.140—260

[6]王锁萍,龚建荣,张豫滇.电子设计自动化(EDA)教程[M].成都:电子科技大学出版社,2000.188—301

The Self-Starting Design and Emulation

of Sequential Logic Circuit

Department of Electronics 0302 Student Hongling Gao

Tutor Aizhen Wang

Abstract:In the design of sequential logic circuit, whether the circuit can start by itself matters the reliability and stability of the entire system. Thus, the self-starting design of sequential logic circuit is an important part in the system design.Taking the

self-starting design of six shift counter as an example,the paper explains the principle and methods of designing sequential logic circuit with the function of self-starting and summs up to make use of Karnaugh map to discover the unable self-starting law and sove it at an early date. At last ,the design of six shift-counter is emulated by using the MAX + plusII software.Meanwhile,it achieves the correct waveform.

Key words:Karnaugh Map; Design of Self-starting; MAX + plusII

《时序逻辑电路》练习题及答案 [6.1] 分析图P6-1时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。 图P6-1 [解] 驱动方程:311Q K J ==, 状态方程:n n n n n n n Q Q Q Q Q Q Q 13131311⊕=+=+; 122Q K J ==, n n n n n n n Q Q Q Q Q Q Q 12212112 ⊕=+=+; 33213Q K Q Q J ==,, n n n n Q Q Q Q 12313 =+; 输出方程:3Q Y = 由状态方程可得状态转换表,如表6-1所示;由状态转换表可得状态转换图,如图A6-1所示。电路可以自启动。 表6-1 n n n Q Q Q 123 Y Q Q Q n n n 111213+++ n n n Q Q Q 123 Y Q Q Q n n n 1112 13+++ 0 00 00 1 010 01 1 0010 0100 0110 1000 100 10 1 110 11 1 000 1 011 1 010 1 001 1 图A6-1 电路的逻辑功能:是一个五进制计数器,计数顺序是从0到4循环。 [6.2] 试分析图P6-2时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。A 为输入逻辑变量。

图P6-2 [解] 驱动方程:21 Q A D =, 21 2Q Q A D = 状态方程:n n Q A Q 21 1 =+, )(122112n n n n n Q Q A Q Q A Q +==+ 输出方程:21Q Q A Y = 表6-2 由状态方程可得状态转换表,如表6-2所示;由状态转换表 可得状态转换图,如图A6-2所示。 电路的逻辑功能是:判断A 是否连续输入四个和四个以上“1” 信号,是则Y=1,否则Y=0。 图A6-2 [6.3] 试分析图P6-3时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,检查电路能否自启动。 图P6-3 [解] 321Q Q J =,11=K ; 12Q J =,312Q Q K =; 23213Q K Q Q J ==, =+11n Q 32Q Q ·1Q ; 211 2 Q Q Q n =++231Q Q Q ; 3232113Q Q Q Q Q Q n +=+ Y = 32Q Q 电路的状态转换图如图A6-3所示,电路能够自启动。 图A6-3 [6.4] 分析图P6-4给出的时序电路,画出电路的状态转换图,检查电路能否自启动,说明电路实现的功能。A 为输入变量。 n n Q AQ 12 Y Q Q n n 1 112++ 000 00 1 010 01 1 100 11 1 110 10 1 010 100 110 00 1 11 1 100 010 000

引言 人类社会进步,各种仪器测试设备的以电子设备代替成为趋势,各类测试仪器都希望通过电子设备来实现。电子设备在实现相应参数的测量时,具有简单容易操作,而且数据便于计算机处理等优点。目前科技的飞速进展与集成电路的发展应用,有密不可分的关系。十九世纪工业革命主要以机器节省人力,二十世纪的工业的革命则主要以电脑为人脑分劳。而电脑的发展归于集成电路工业。 集成电路是将各种电路器件集成于半导体表面而形成的电路。近年来集成电路几乎成为所有电子产品的心脏。由于集成电路微小化的趋向,使电子产品得以“轻、薄、短、小”。故集成电路工业又称微电子工业。差不多在同时数字计算机的发展提供了应用晶体管的庞大潜在市场。 20世纪90年代以后,电子科学和技术取得了飞速的发展,其标志就是电子计算机的普及和大规模集成电路的广泛应用。在这种情况下,传统的关于数字电路的内容也随之起了很大的变化,在数字电路领域EDA工具已经相当成熟,无论是电路内容结构设计还是电路系统设计,以前的手工设计都被计算机辅助设计或自动设计所取代。 通过长期的学习微电子专业理论知识,我们应该多动手实践把理论知识与实践相结合,加强对理论知识的把握。本文是十进制同步计数器的设计,对十进制同步计数器的设计进行电路原理图设计以及仿真,版图设计,版图验证。 1 设计技术要求 (1)项目名称:十进制同步计数器的设计 (2)使用工艺:2.0um硅栅工艺(tanner)或者1.0um硅栅工艺(cadence) (3)供电电源:5V (4)输入要求:异步清除,CMOS电平 (5)进行原理图设计,并完成电路的仿真 (6)版图设计,完成LVS一致性检验,生成相应的GDSII文档 2 设计构思及理论 2.1 设计思路 十进制同步计数器的设计可以细化成下列步骤: ①建立最简原始状态图。 ②确定触发器级数,进行状态编码。 ③用状态装换卡诺图化简,求状态方程和输出方程。 ④查自启动特性。 ⑤确定触发类型,求驱动方程。 ⑥画逻辑图。

解决逻辑电路自启动问题的方法在时序逻辑电路中,当逻辑电路可能出现的总状态数不等于有效状态时,就会有无效状态。如果无效状态能回到有效状态时,称电路能够自启动。反之,则不能自启动。 能自启动的电路不会对电路工作状态造成影响,但不能自启动的电路会对电路的可靠性及稳定性形成较大的隐患。当电路加电时就可能偶然落入无效状态 ,这时电路将不能正常工作. 在电路正常工作时,如果受外部意外的干扰,也可能落入无效状态,此时电路的正常工作将被终止、并出错.所以自启动问题是数字电路系统设计中必须解决的问题. (1)自启动问题的典型解决方法 自启动问题是设计过程中必须考虑的问题.自启动问题在相关书籍和文章中,都有较经典的解决方法. 为叙述方便, 以时序电路设计中的典型设计,计数器电路的设计为例来说明.在计数器中, 如果无效状态形成循环(无效循环) ,则电路不能自启动(无效状态不能回到有效状态) .解决方法通常是修改无效循环中的状态转换关系,断开无效循环并把无效状态引导至有效状态,使电路的状态图形成能自启动的状态图,从而解决不能自启动的问题.现用3位扭环形计数器(图1)为例来说明:无效状态010和101形成一个无效循环,所以电路不能自启动.解决的方法是断开无效循环,把无效状态101引导至有效状态110上, 完成自启动, 最后设计结果如图2所示.

此方法直接、彻底的解决了自启动问题.但这个方法有一个很大的局限性:当无效循环较多时,把无效状态一个一个的引导至有效状态的步骤可能很繁杂, 要有一定的经验和技巧, 虽然最后都能解决自启动问题,但最终的设计结果可能会很复杂.对于设计过程困难、设计结果复杂的设计,是否还有另外的设计方法呢? 这就是本文讨论的要点. (2)加电预置电路和检测复位电路解决自启动问题首先想到的是加电预置,在打开电源的瞬间,使电路处在一个有效状态下,从而避免进入无效状态,来解决自启动问题.图3电路在打开电源的瞬间,电路处在111状态(可任选一个有效状态来预置. 由于

实验十Moore型同步时序逻辑电路的分析与设计 一.实验目的: 1.同步时序逻辑电路的分析与设计方法 2.掌握时序逻辑电路的测试方法。 二.实验原理: 1.Moore同步时序逻辑电路的分析方法: 时序逻辑电路的分析,按照电路图(逻辑图),选择芯片,根据芯片管脚,在逻辑图上标明管脚号;搭接电路后,根据电路要求输入时钟信号(单脉冲信号或连续脉冲信号),求出电路的状态转换图或时序图(工作波形),从中分析出电路的功能。 2.Moore同步时序逻辑电路的设计方法: (1)分析题意,求出状态转换图。 (2)状态分析化简:确定等价状态,电路中的等价状态可合并为一个状态。(3)重新确定电路状态数N,求出触发器数n,触发器数按下列公式求:2n-1 (7)利用卡诺图如图2,求状态方程、驱动方程。 (8)自启动检验:将各无效状态代入状态方程,分析状态转换情况,画出完整的 状态转换图,如图3所示,检查是否能自启动。 5.2 时序逻辑电路的设计方法 本次重点内容: 1、同步时序逻辑电路的设计方法。 2、异步时序逻辑电路的设计方法。 教学过程 5.2.1 同步时序逻辑电路的设计 一、同步时序逻辑电路的设计方法 设计关键:根据设计要求→确定状态转换的规律→求出各触发器的驱动方程。 设计步骤:(先简单介绍,通过以下的举例后,再进行总结,特别再点出设计关键)1.根据设计要求,设定状态,确定触发器数目和类型。画出状态转换图。 2.状态化简 前提:保证满足逻辑功能要求。 方法:将等价状态(多余的重复状态)合并为一个状态。 3.状态分配,列出状态转换编码表 通常采用自然二进制数进行编码。N为电路的状态数。 每个触发器表示一位二进制数,因此,触发器的数目n可按下式确定 2n≥N>2n–1 4.画状态转换卡诺图,求出状态方程、输出方程 选择触发器的类型(一般可选JKF/F或DF/F,由于JK触发器使用比较灵活,因此,在设计中多选用JK触发器。)将状态方程和触发器的特性方程进行比较→驱动方程。 5.根据驱动方程和输出方程画逻辑图。 6.检查电路有无自启动能力。 如设计的电路存在无效状态时,应检查电路进入无效状态后,能否在时钟脉冲作用下自动返回有效状态工作。如能回到有效状态,则电路有自启动能力;如不能,则需修改设计,使电路具有自启动能力。 二、同步时序逻辑电路的设计举例 [例1] 试设计一个同步七进制加法计数器。 解:设计步骤 (1)根据设计要求,设定状态,画状态转换图。 七进制→7个状态→用S0,S1,…,S6表示 状态转换图如下所示: (2)状态化简。 本例中7个状态都是有效状态。 (3)状态分配,列状态转换编码表。 根据式2n≥N>2n–1,→ N=7,n=3,即采用三个触发器。 选用三位自然二进制加法计数编码→列出状态转换编码表。 (4)选择触发器的类型,求出状态方程,驱动方程和输出方程。根据状态转换编码表→得到各触发器次态和输出函数的卡诺图。得 输出方程为: Y= Q2n Q1n 第37卷第4期 2010年7月 浙江大学学报(理学版J Journal of Zhejiang University(Science Edition https://www.doczj.com/doc/402043856.html,/sci V01.37NO.4 Jul.2010 基于次态卡诺图的tJr、K激励函数最小化方法及时序逻辑电路自启动设计 任骏原 (渤海大学物理系,辽宁锦州121000 搐要:分析了JK触发嚣的激励函数和次态函数的关系并在卡诺图上建立二者的联系,提出了在触发器的次态卡诺图上直接求解最小化.,、K激励函数的方法,讨论了无效状态的赋值问题及自启动设计方法,对简化时序逻辑电路的设计过程具有实用意义. 关键词:JK触发器;激励函数;自启动;时序逻辑电路设计 中图分类号:TP 332.1文献标志码:A 文章编号:1008—9497(201004—425—03 REN Jun-yuan(Department of Physics,Bohai University,Jinzhou 121000,Liaoning Province,China Minimization method of J and K excitation function based Oil next-state karnau【gh maps and self-starting design of sequential logic circuits.Journal of Zhejiang University(Science Edition,2010,37(4:425--427 Abstract:The relation between excitation function and next—state function of JK flip-flop was analyzed based on Kar-naugh maps.The 实验二 时序逻辑电路的设计 一、实验目的: 1、 掌握时序逻辑电路的分析方法。 2、 掌握VHDL 设计常用时序逻辑电路的方法。 3、 掌握时序逻辑电路的测试方法。 4、 掌握层次电路设计方法。 5、 理解时序逻辑电路的特点。 二、实验的硬件要求: 1、 EDA/SOPC 实验箱。 2、 计算机。 三、实验原理 1、时序逻辑电路的定义 数字逻辑电路可分为两类:组合逻辑电路和时序逻辑电路。组合逻辑电路中不包含记忆单元(触发器、锁存器等),主要由逻辑门电路构成,电路在任何时刻的输出只和当前时刻的输入有关,而与以前的输入无关。时序电路则是指包含了记忆单元的逻辑电路,其输出不仅跟当前电路的输入有关,还和输入信号作用前电路的状态有关。 2、同步时序逻辑电路的设计方法 同步时序逻辑电路的设计是分析的逆过程,其任务是根据实际逻辑问题的要求,设计出能实现给定逻辑功能的电路。同步时序电路的设计过程: (1)根据给定的逻辑功能建立原始状态图和原始状态表。 ①明确电路的输入条件和相应的输出要求,分别确定输入变量和输出变量的数目和符号; ②找出所有可能的状态和状态转换之间的关系; ③根据原始状态图建立原始状态表; (2)状态化简---求出最简状态图。 合并等价状态,消去多余状态的过程称为状态化简。 等价状态:在相同的输入下有相同的输出,并转换到同一个次态去的两个状态称为等价状态。 (3)状态编码(状态分配)。 给每个状态赋以二进制代码的过程。 根据状态数确定触发器的个数,n n M 221-≤∠(M 为状态数;n 为触发器的个数)。 (4)选择触发器的类型。 (5)求出电路的激励方程和输出方程。 (6)画出逻辑图并检查自启动能力。 3、时序逻辑电路的特点及设计时的注意事项 ①时序逻辑电路与组合逻辑电路相比,输出会延时一个时钟周期。 ②时序逻辑电路一般容易消除“毛刺”。 ③用VHDL 描述时序逻辑电路时,一般只需将时钟信号和异步控制(如异步复位)信号作为敏感信号。 时序逻辑电路的分析方法 时序逻辑电路的分析:根据给定的电路,写出它的方程、列出状态转换真值表、画出状态转换图和时序图,而后得出它的功能。 同步时序逻辑电路的分析方法 同步时序逻辑电路的主要特点:在同步时序逻辑电路中,由于所有触发器都由同一个时钟脉冲信号CP来触发,它只控制触发器的翻转时刻,而对触发器翻转到何种状态并无影响,所以,在分析同步时序逻辑电路时,可以不考虑时钟条件。 1、基本分析步骤 1)写方程式: 输出方程:时序逻辑电路的输出逻辑表达式,它通常为现态和输入信号的函数。 驱动方程:各触发器输入端的逻辑表达式。 状态方程:将驱动方程代入相应触发器的特性方程中,便得到该触发器的状态方程。 2)列状态转换真值表: 将电路现态的各种取值代入状态方程和输出方程中进行计算,求出相应的次态和输出,从而列出状态转换真值表。如现态的起始值已给定时,则从给定值开始计算。如没有给定时,则可设定一个现态起始值依次进行计算。 3)逻辑功能的说明: 根据状态转换真值表来说明电路的逻辑功能。 4)画状态转换图和时序图: 状态转换图:是指电路由现态转换到次态的示意图。 时序图:是在时钟脉冲CP作用下,各触发器状态变化的波形图。 5)检验电路能否自启动 关于电路的自启动问题和检验方法,在下例中得到说明。 2、分析举例 例、试分析下图所示电路的逻辑功能,并画出状态转换图和时序图。 解:由上图所示电路可看出,时钟脉冲CP加在每个触发器的时钟脉冲输入端上。因此,它是一个同步时序逻辑电路,时钟方程可以不写。 ①写方程式: 输出方程: 驱动方程: 状态方程: ②列状态转换真值表: 状态转换真值表的作法是: 从第一个现态“000”开始,代入状态方程,得次态为“001”,代入输出方程,得输出为“0”。 第七章 时序逻辑电路的设计 1、 选择题 1.下列逻辑电路中为时序逻辑电路的是 。 A.变量译码器 B.加法器 C.数码寄存器 D.数据选择器 2.同步时序电路和异步时序电路比较,其差异在于后者 。 A.没有触发器 B.没有统一的时钟脉冲控制 C.没有稳定状态 D.输出只与内部状态有关 3.若要设计一个脉冲序列为1101001110的序列脉冲发生器,应选用 个触发器。 .3 C.4 D.10 A.2 B 2、 判断题(正确打√,错误的打×) 1.同步时序电路由组合电路和触发器两部分组成。( ) 2.组合电路不含有记忆功能的器件。( ) 3.时序电路不含有记忆功能的器件。( ) 4.同步时序电路具有统一的时钟CP控制。( ) 5.异步时序电路的各级触发器类型不同。( ) 6.在同步时序电路的设计中,若最简状态表中的状态数为2N,而又是用N级触发器来实现其电路,则不需检查电路的自启动性。( ) 7.时序逻辑电路与组合逻辑电路的最大区别在于,它具有存储和记忆功能。() 8.异步时序电路中的各触发器的状态转换不是在同一时刻进行的。() 3、 填空题 1.寄存器按照功能不同可分为两类: 寄存器和 寄存器。 2.数字电路按照是否有记忆功能通常可分为两类: 、。 3.由四位移位寄存器构成的顺序脉冲发生器可产生 个顺序脉冲。 4.时序逻辑电路按照其触发器是否有统一的时钟控制分为 时序电路和 时序电路。 四、分析题 1:用JK触发器和门电路设计一个同步七进制计数器。 2:分析图7202所示时序电路的逻辑功能,设各触发器为TTL型,初始状态为Q = 0,试写出: 1、驱动方程; 2、状态方程; 图7202 3:分析如图7209所示时序电路的逻辑功能,试写出: 1、各触发器的驱动方程; 2、状态方程和输出方程; 3、画出电路的状态转换图; 图7209 4:分析如图7208时序逻辑电路的功能,设触发器初始状态为0,试写出: 1、各触发器的驱动方程; 2、状态方程和输出方程; 3、画出状态转换图,时序图; 第1题: 设计一个串行数据检测器,对它的要求是:连续输入3个或3个以上的1时输出为1,其他输入情况下输出为0。 答案 输入数据作为输入变量,用X 表示;检测结果为输出变量,用Y 表示。 设电路没有输入1以前的状态为0S ,输入一个1状态为1S ,连续输入两个1后的状态为2S ,连续输入3个1以后的状态为3S 。状态转换图为: 求得触发器的输入方程为:X K XQ J ==101; 1;010==K Q X J 输出方程:1XQ Y = 画出逻辑图 第2题: 试用JK 触发器和门电路设计一个同步七进制计数器。 答案 因为七进制计数器需要有7个不同的状态,所以需要用三个触发器组成。根据题目要求画出状态转换图: 卡诺图为: 从卡诺图得到的状态方程为: 驱动方程为: 设计得到的逻辑电路图为: 第3题:设计一“011”序列检测器,每当输入011码时,对应最后一个1,电路输出为1。答案 画出原始状态图(或称转移图) 输入端X:输入一串行随机信号 输出端Z:当X出现011序列时,Z=1;否则Z=0 选用T 触发器 表达式为: T 触发器的驱动方程为: 第4题: 用JK 触发器设计时序逻辑电路,状态表如下所示: n n Q Q 01 Y Q Q n n /1 11++ A=0 A=1 00 01/0 11/0 01 10/0 00/0 10 11/0 01/0 11 00/1 10/1 答案 所要设计的电路由4个状态,需要用两个JK 触发器实现,求得JK 触发器的激励方程为:100==K J 011Q A K J ⊕== 输出方程:01Q Q Y = 由输出方程和激励方程画电路 A B C D 1/0 0/0 0/0 1/1 0/0 0/0 1/0 1/0 011XQ Q T +=000XQ Q X T +=0 1Q XQ Z =011XQ Q T +=0 00XQ Q X T +=0 1Q XQ Z = 东南大学电工电子实验中心 实验报告 课程名称:数字逻辑电路设计实践 第4 次实验 实验名称:基本时序逻辑电路 院(系):信息科学与工程学院专业:信息工程姓名:学号: 实验室: 实验组别: 同组人员:无实验时间: 评定成绩:审阅教师: 时序逻辑电路 一、实验目的 1.掌握时序逻辑电路的一般设计过程; 2.掌握时序逻辑电路的时延分析方法,了解时序电路对时钟信号相关参数的基本要求; 3.掌握时序逻辑电路的基本调试方法; 4.熟练使用示波器和逻辑分析仪观察波形图,并会使用逻辑分析仪做状态分析。 二、实验原理 1.时序逻辑电路的特点(与组合电路的区别): ——具有记忆功能,任一时刻的输出信号不仅取决于当时的输出信号,而且还取决于电路原来的值,或者说还与以前的输入有关。 2.时序逻辑电路的基本单元——触发器(本实验中只用到D触发器) 触发器实现状态机(流水灯中用到) 3.时序电路中的时钟 1)同步和异步(一般都是同步,但实现一些任意模的计数器时要异步控制时钟端) 2)时钟产生电路(电容的充放电):在内容3中的32768Hz的方波信号需要自己通 过电路产生,就是用到此原理。 4.常用时序功能块 1)计数器(74161) a)任意进制的同步计数器:异步清零;同步置零;同步置数;级联 b)序列发生器 ——通过与组合逻辑电路配合实现(计数器不必考虑自启动) 2)移位寄存器(74194) a)计数器(一定注意能否自启动) b)序列发生器(还是要注意分析能否自启动) 三、实验内容 1.广告流水灯 a.实验要求 用触发器、组合函数器件和门电路设计一个广告流水灯,该流水等由8个LED组成,工作时始终为1暗7亮,且这一个暗灯循环右移。 ①写出设计过程,画出设计的逻辑电路图,按图搭接电路。 ②将单脉冲加到系统时钟端,静态验证实验电路。 ③将TTL连续脉冲信号加到系统时钟端,用示波器和逻辑分析仪观察并记录时钟脉 冲CLK、触发器的输出端Q2、Q1、Q0和8个LED上的波形。 b.实验数据 ①设计电路。 1)问题分析 流水灯的1暗7亮对应8个状态,故可采用3个触发器实现;而且题目要求输出8 个信号控制8个灯的亮暗,故可以把3个触发器的输出加到3-8译码器的控制端,对应的8个译码器输出端信号控制8个灯的亮暗。 2)设三个触发器输出端状态为Q2Q1Q0,则状态图如下 时序逻辑电路的设计 一、实验目的 1. 熟悉集成计数器的逻辑功能和各控制端的作用。 2. 掌握计数器的使用方法。 3. 掌握任意进制计数器的设计方法。 4. 了解8421BCD和5421BCD的编码规则。 二、实验器材 集成计数器74LS90、四2输入与非门74LS00、双4输入与非门74LS20、四异或门74LS86、六非门74LS04、显示译码器7447/7448、七段数码管 三、实验任务及要求 1. 设计要求 (1)用1片74LS90和1片与非门设计一个5进制计数器。 (2)用2片74LS90和1片与非门设计一个四十以内(十以上)的任意进制计数器。 2.实验内容 (1)测试所用芯片74LS90的逻辑功能(置0、置9、8421BCD计数输出功能)。(2)组装所设计的时序逻辑电路,并验证其功能是否正确。 提示:计数器的状态输出端分别接在实验箱上的显示译码器的输入端,用七段数码管显示计数状态值。CP接实验箱上的可调连续脉冲。 四、实验原理 1. 74LS90的逻辑功能 74LS90是二-五-十进制异步计数器。 (1)R9(1)=R9(2)=“1”,Q3Q2Q1Q0=1001,置9; (2)R0(1)=R0(2)=“1”,R9(1)‖R9(2)=“0”,Q3Q2Q1Q0=0000,置0; (3)计数脉冲由CP0端输入,输出由Q0端引出,即得二进制计数器; (4)计数脉冲由CP1端输入,输出由Q3,Q2,Q1端引出,即得五进制计数器;(5)将Q0和CP1相连,计数脉冲由CP0端输入,输出由Q3,Q2,Q1,Q0端引出,即得8421BCD码十进制计数器; 2. 时序逻辑电路的基本设计方法 Step 1:明确设计电路功能,作出基于功能涉及到的所有编码排序的状态转换图;Step 2:判断电路是否有输入或输出变量,并根据状态转换图画出状态转换表; Step 3:根据状态转换表,分离出各触发器输出量Q 0~Q m (m=1、2、3…)、输出 变量Y的卡诺图并化简,得到各个触发器的状态方程; 第六章 时序逻辑电路 【题 】 分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。 Y 图P6.3 【解】驱动方程: 11323131233 J =K =Q J =K =Q J =Q Q ;K =Q ?? ??? 输出方程:3Y Q = 将驱动方程带入JK 触发器的特性方程后得到 状态方程为: n+11313131n 1 2121221n+1 3321 Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q +?=+=?=+=⊕??=?e 电路能自启动。状态转换图如图 【题 】 分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。A 为输入逻辑变量。 图A6.3 Y 图P6.5 【解】 驱动方程: 12 21212() D AQ D AQ Q A Q Q ?=??==+?? 输出方程: 21Y AQ Q = 将驱动方程带入JK 触发器的特性方程后得到状态方程为: n+1 12 n+1 212() Q AQ Q A Q Q ?=??=+?? 电路的状态转换图如图 1 图A6.5 【题 】 分析图时序电路的逻辑功能,画出电路的状态转换图,检查电路能否自启动,说明电路能否自启动。说明电路实现的功能。A 为输入变量。 A Y 图P6.6 【解】驱动方程: 11221 1 J K J K A Q ==?? ==⊕? 输出方程: 1212Y AQ Q AQ Q =+ 将驱动方程带入JK 触发器的特性方程后得到状态方程为: n+111 n+1 2 12 Q Q Q A Q Q ?=??=⊕⊕?? 电路状态转换图如图。A =0时作二进制加法计数,A =1时作二进制减法计数。 01图A6.6 【题 】 分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。 思考题与习题题解 5-1 填空题 (1)组合逻辑电路任何时刻的输出信号,与该时刻的输入信号有关;与电路原来所处的状态无关;时序逻辑电路任何时刻的输出信号,与该时刻的输入信号有关;与信号作用前电路原来所处的状态有关。 (2)构成一异步n2进制加法计数器需要 n 个触发器,一般将每个触发器接成计数或T’型触发器。计数脉冲输入端相连,高位触发器的 CP 端与邻低位Q端相连。 (3)一个4位移位寄存器,经过 4 个时钟脉冲CP后,4位串行输入数码全部存入寄存器;再经过 4 个时钟脉冲CP后可串行输出4位数码。 (4)要组成模15计数器,至少需要采用 4 个触发器。 5-2 判断题 (1)异步时序电路的各级触发器类型不同。(×)(2)把一个5进制计数器与一个10进制计数器串联可得到15进制计数器。(×)(3)具有 N 个独立的状态,计满 N 个计数脉冲后,状态能进入循环的时序电路,称之模N计数器。(√) (4)计数器的模是指构成计数器的触发器的个数。(×) 5-3 单项选择题 (1)下列电路中,不属于组合逻辑电路的是(D)。 A.编码器 B.译码器 C. 数据选择器 D. 计数器 (2)同步时序电路和异步时序电路比较,其差异在于后者( B )。 A.没有触发器 B.没有统一的时钟脉冲控制 C.没有稳定状态 D.输出只与内部状态有关 (3)在下列逻辑电路中,不是组合逻辑电路的有( D )。 A.译码器 B.编码器 C.全加器 D.寄存器 (4)某移位寄存器的时钟脉冲频率为100KHz,欲将存放在该寄存器中的数左移8位,完成该操作需要(B)时间。 μS μS μS (5)用二进制异步计数器从0做加法,计到十进制数178,则最少需要( C )个触发器。 (6)某数字钟需要一个分频器将32768Hz的脉冲转换为1HZ的脉冲,欲构成此分频器至少需要(B)个触发器。 时序逻辑电路的设计 班级 姓名 学号 实验四时序逻辑电路的设计 一、实验目的 1. 学习时序逻辑电路的分析方法和设计方法。 2. 熟悉并掌握利用中小规模芯片实现时序逻辑电路的方法。 3. 提高调试数字电路的能力。 二、实验任务 利用实验盒中的计数器芯片74LS90、74LS161及其他器件设计并实现一个数字钟电路,具体要求如下: 1. 时间显示范围00:00~11:59; 2. 任何时刻可实现手动清零; 3. 实现整点报时功能,声响从54 分起、整点止,并要求报时声音清晰响亮。选择 学习机上的脉冲源做时钟信号;数码管LED4~LED1 显示小时和分钟;蜂鸣器做整点报时。 三、提高任务 1. 为数字钟电路设计对表调时功能。用学习机右侧数字键盘中的“START”按键作为 调时脉冲输入,其内部电路见图1。 图1 学习机上“START”按键的内部电路 2. 为数字钟电路设计一个上电自动清零电路,即通电后从00:00 开始计时。 四、实验说明 1. 了解芯片的引脚排列,特别注意74LS90 的电源和地引脚编号与其他芯片不同。 2. 学习机上的蜂鸣器BDC 为直流蜂鸣器:工作电压为3~12V 的直流电压。蜂鸣器 的工作电流约8~15mA。若门电路不能直接驱动蜂鸣器,可搭建图2 驱动电路。 图 2(a) 9011 引脚图 图 2(b )驱动电路 3. 学习机上的带译码器数码管 LED1~LED3 用作数字 钟的分个位、分十位和小时个位的显示。 不带译码器 LED4 作为小时的十位数字显示。小时十 位只需显示数字“0”和“1”,建议用图 4 电路连接方式 实现。其中: (1) 数码管公共端“com ”接学习机中的地“GND ”; (2) 数码管的b 、c 段接学习机中的5V ; (3) 数码管的a 、d 、e 和f 四段相互连接后,接到数字钟小时十位的输出端。 五、电路设计 1. 设计思路及工作原理 首先实现计时功能,分为分钟模块和小时模块,分钟模块用2片74LS90构成,其中一片接成十进制,输出端接到数码管上显示分钟的个位,并向下一级给出进位信号,另一片接成六进制,输出接到数码管上显示分钟的十位,并向下一级给出进位信号。小时模块用一片74LS161构成,由于小时的输出非一般,所以需要经过一系列门电路。 其次实现清零功能,由于3个芯片均有异步清零端,但有的为高电平,有的为低电平,所以只需将清零信号及反相后的信号分别接在清零端就行。 然后实现报时功能,只需将两片74LS90的输出端经过几个门电路即可实现54~59给出高电平。 再实现上电清零功能,只需在清零的开关和地之间并一个电容就行,这样上电后清零端给出低电平。 最后实现调时功能,加上一个控制电路很容易实现调时,但是也会出现思考题3中出现的问题,解决方案见下。 2. 电路性能测试结果。 能有效计时、报时、清零、调时,实现了要求的功能。 图 4 LED4 的连接图 3. 在实验中遇到的问题及解决方法。 主要问题有两个:一是调时时按一下跳很多次,开始时考虑的解决方法是仿照上电清零,在开关两端加电容,但是把实验盒中的电容用了个遍也没有解决问题,后来突然一下才想到可以用D 触发器的;二是开始时加上了蜂鸣器的驱动电路,后来发现其实芯片输出的电流是可以直接驱动蜂鸣器的。 4. 此次实验的收获。 学会了时序电路的设计和调试方法。 A、与当时的输入信号有关,与电路的原状态无关。 B、与当时的输入信号有关,与电路的原状态有关。 C、与当时的输入信号无关,与电路的 原状态有关。 D、 2、时序逻辑电路中必须含有: A、存储电路 B、编码器 C、加法器 D、 3、同步时序逻辑电路所有触发器的时钟输入端都接同一个时钟脉冲。 A、各触发器不同时具备触发翻转的条 件 B、各触发器同时具备触发翻转的条件 C、各触发器的触发翻转有先有后 D、 4、异步时序逻辑电路各触发器的时钟输入所接不是同一的时钟脉冲。 A、结构简单,速度快 B、结构复杂,速度慢 C、结构简单,速度慢 D、 5、异步时序逻辑电路,各触发器: A、触发翻转有先有后 B、同时触发翻转 C、无法确定 D、 第二题、多项选择题(每题2分,5道题共10分) 1、时序逻辑电路从结构上讲,包含有: A、存储元件 B、触发器或含有反馈延迟电路 C、译码器 2、时序逻辑电路的输出信号: A、与当时的输入信号无关 B、与当时的输入信号有关 C、与电路的原状态有关 D、与电路的原状态无关 3、同步时序逻辑电路: A、所有触发器的时钟输入端都接同一个时钟脉冲 B、各触发器同时具备触发翻转的条件 C、速度快;结构简单 D、速度快;结构复杂 4、时序逻辑电路的逻辑功能可用()来描述。 A、状态方程 B、状态表 C、状态图 D、时序图 5、时序逻辑电路的分析是指已知逻辑图: A、列写逻辑方程式 B、计算状态表 C、画电路的状态图 D、画电路的时序图 E、判定电路的功能 第三题、判断题(每题1分,5道题共5分) 1、时序逻辑电路中必须含有存储电路。 正确错误 2、时序逻辑电路中的存储电路只能用延迟元件组成,不能用触发器构成。 正确错误 3、同步时序逻辑电路各触发器同时具备触发翻转的条件。 正确错误 4、异步时序逻辑电路结构简单,速度慢。 时序逻辑电路分析例题 1、分析下图时序逻辑电路。 解: 1、列出驱动方程:111==K J 1//122Q A AQ K J +== 2、列出状态方程: 将驱动方程代入JK 触发器的特性方程Q K JQ Q //*+=得: /1*1Q Q = 212/1//21//2/1*2Q AQ Q Q A Q Q A Q AQ Q +++= 3、列出输出方程: 21//2/1Q Q A Q AQ Y += 4、列出状态转换表: (1)当A=1时: 根据:/1*1Q Q =;21/2/1*2Q Q Q Q Q +=;/ 2 /1Q Q Y =得: (2)当A=0时: 根据:/1*1Q Q =;2/1/ 21*2Q Q Q Q Q +=;21Q Q Y =得: 5、画状态转换图: 6、说明电路实现的逻辑功能: 此电路是一个可逆4进制(二位二进制)计数器,CLK 是计数脉冲输入端,A 是加减控制端,Y 是进位和借位输出端。当控制输入端A 为低电平0时,对输入的脉冲进行加法计数,计满4个脉冲,Y 输出端输出一个高电平进位信号。当控制输入端A 为高电平1时,对输入的脉冲进行减法计数,计满4个脉冲,Y 输出端输出一个高电平借位信号。 2、如图所示时序逻辑电路,试写出驱动方程、状态方程,画出状态图,说明该电路的功能。 解:驱动方程 ?? ?=⊕=1010K Q X J n ???=⊕=11 1K Q X J n 状态方程 ()()n n n n n n n n n n n n n n Q XQ Q Q X Q Q X Q Q Q X Q Q X Q Q X Q 0 1010 1 10 01011011+=⊕=+=⊕=++ CP X Z 第十六单元时序逻辑电路 (8学时——第49~56学时) 主要内容:时序逻辑电路的分析与设计 教学重点:时序逻辑电路的分析与设计方法 教学难点:时序逻辑电路的设计 教学方法:启发式教学、探究式教学 教学手段:实验、理论、实际应用相结合 第一部分知识点 一、时序电路概述 时序电路的状态及输出是与时间顺序有关的,由组合电路和存储电路(多为触发器)组成,1、特点 任意时刻的输出,不仅与该时刻的输入有关、还与电路原来的状态有关。 2、分类 按逻辑功能分为计数器、寄存器等,按触发器工作分为同步电路和异步电路,按电路输出信号特性分为Mealy型(输出与输入及电路现态有关)和Moore型(输出仅与电路现态有关)电路。 二、时序电路的分析 1、分析步骤 (1)写出电路的时钟方程(各触发器的CP表达式)、输出方程(各输出端表达式)及驱动方程(各触发器的触发信号表达式)。 (2)求出电路的状态方程(各触发器的状态表达式) (3)计算得出电路工作状态表 (4)画状态图及时序图 (5)分析电路功能 2、分析举例 分析时序电路 (1)时钟方程CP 0=CP 1=CP 2=CP 输出方程n n n Q Q Q Y 01 2= 驱动方程n Q J 20=、n Q K 20=, n Q J 01=、n Q K 01=, n Q J 12=、n Q K 12= (2)状态方程 将J 、K 代入JK 触发器特征方程n n n Q K Q J Q +=+1 得各触发器状态方程: n n Q Q 210=+ 、 n n Q Q 011=+ 、 n n Q Q 112=+ (3)计算得到状态表 现 态 次 态 输 出 n Q 2 n Q 1 n Q 0 12|n Q + 11+n Q 10+n Q Y 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 1 0 0 0 0 1 0 1 0 0 1 1 0 1 1 1 1 0 1 1 1 (4)画状态图及时序图 (5)逻辑功能 这是一个有六个工作状态的同步工作电路,属Moore 型电路。 (6)有效态和无效态 时序逻辑电路的设计 、实验目的 1. 熟悉集成计数器的逻辑功能和各控制端的作用。 2. 掌握计数器的使用方法。 3. 掌握任意进制计数器的设计方法。 4. 了解8421BCD和5421BCD的编码规则。 二、实验器材 集成计数器74LS90、四2输入与非门74LS00、双4输入与非门74LS20、四异或门74LS86、六非门74LS04、显示译码器7447/7448、七段数码管 三、实验任务及要求 1. 设计要求 (1)用1 片74LS90和1 片与非门设计一个5 进制计数器。 (2)用2片74LS90和1片与非门设计一个四十以内(十以上)的任意进制计数器。 2. 实验内容 (1)测试所用芯片74LS90的逻辑功能(置0、置9、8421BCD计数输出功能)。(2)组装所设计的时序逻辑电路,并验证其功能是否正确。 提示:计数器的状态输出端分别接在实验箱上的显示译码器的输入端,用七段数码管显示计数状态值。CP接实验箱上的可调连续脉冲。 四、实验原理 1. 74LS90的逻辑功能 74LS90是二-五-十进制异步计数器。 (1)R9(1)=R9(2)=“ 1”,Q3Q2Q1Q0=1001,置9; (2)R0(1)=R0(2)=“ 1”,R9(1)‖R9(2)=“0”,Q3Q2Q1Q0=0000置, 0; (3)计数脉冲由CP0端输入,输出由Q0 端引出,即得二进制计数器; (4)计数脉冲由CP1 端输入,输出由Q3,Q2,Q1端引出,即得五进制计数器; (5)将Q0和CP1相连,计数脉冲由CP0端输入,输出由Q3,Q2,Q1,Q0端引出,即得8421BCD码十进制计数器; 2. 时序逻辑电路的基本设计方法 Step 1:明确设计电路功能,作出基于功能涉及到的所有编码排序的状态转换图;Step 2 :判断电路是否有输入或输出变量,并根据状态转换图画出状态转换表;Step 3 :根据状态转换表,分离出各触发器输出量Q0~Q m(m=1、2、3, )、输出变量Y 的卡诺图并化简,得到各个触发器的状态方程; 《时序逻辑电路》练习题及答案 []分析图P6-1 时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。 图P6-1 [解] 驱动方程:3 1 1 Q K J= =,状态方程:n n n n n n n Q Q Q Q Q Q Q 1 3 1 3 1 3 1 1 ⊕ = + = + ; 1 2 2 Q K J= =,n n n n n n n Q Q Q Q Q Q Q 1 2 2 1 2 1 1 2 ⊕ = + = + ; # 3 3 2 1 3 Q K Q Q J= =,,n n n n Q Q Q Q 1 2 3 1 3 = + ; 输出方程:3 Q Y= 由状态方程可得状态转换表,如表6-1所示;由状态转换表可得状态转换图,如图A6-1所示。电路可以自启动。 表6-1 n n n Q Q Q 1 2 3 Y Q Q Q n n n1 1 1 2 1 3 + + +n n n Q Q Q 1 2 3 , Y Q Q Q n n n1 1 1 2 1 3 + + + 000 001 010 011 0010 0100 0110 — 1000 100 101 110 111 0001 0111 0101 ; 0011 图A6-1 电路的逻辑功能:是一个五进制计数器,计数顺序是从0到4循环。 []试分析图P6-2时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。A为输入逻辑变量。 # 图P6-2 [解] 驱动方程:2 1 Q A D=, 2 1 2 Q Q A D= 状态方程: n n Q A Q 2 1 1 = + , ) ( 1 2 2 1 1 2 n n n n n Q Q A Q Q A Q+ = = + 输出方程:2 1 Q Q A Y=表6-2 @ 由状态方程可得状态转换表,如表6-2所示;由状态转换表 可得状态转换图,如图A6-2所示。 电路的逻辑功能是:判断A是否连续输入四个和四个以上 “1”信号,是则Y=1,否则Y=0。 图A6-2 []试分析图P6-3时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,检查电路能否自启动。 、 图P6-3 [解] 3 2 1 Q Q J=,1 1 = K; 1 2 Q J=, 3 1 2 Q Q K=; 2 3 2 1 3 Q K Q Q J= =, = +1 1 n Q 3 2 Q Q· 1 Q; 2 1 1 2 Q Q Q n= + +2 3 1 Q Q Q; 3 2 3 2 1 1 3 Q Q Q Q Q Q n+ = + Y = 3 2 Q Q 电路的状态转换图如图A6-3所示,电路能够自启动。 ' 图A6-3 n n Q AQ 1 2 Y Q Q n n1 1 1 2 + + 000 < 001 010 011 100 111 110 101 010 $ 100 110 001 111 100 010 000时序逻辑电路的设计方法

基于次态卡诺图的J、K激励函数最小化方法及时序逻辑电路自启动解读

实验二 时序逻辑电路的设计[1]

同步时序逻辑电路的分析方法

第七章:时序逻辑电路设计

时序逻辑电路设计题

东南大学-数字电路实验-第4章-时序逻辑电路

时序逻辑电路设计

时序逻辑电路课后答案

第5章时序逻辑电路思考题与习题题解

时序逻辑电路的设计

时序逻辑电路的分析

时序逻辑电路分析举例

时序逻辑电路

时序逻辑电路设计

《时序逻辑电路》练习题及答案