基于TMS320VC5402的DSP

基本系统的设计Ξ

姜 滨

(华中科技大学光电子工程系 武汉 430074)

摘 要

本文以美国Texas Instruments(TI)公司C5000TM系列DSP中TMS320VC5402为例,介绍用Flash Rom和SRAM构建DSP基本应用系统的硬件设计方法,以及DSP硬件设计中应注意的几个问题。

关键词:DSP FPG A CPLD

中图法分类号:TP391

The Design of DSP B asic System based on TMS320VC5402

Jiang Bin

(Photoelectron Engineering Department,HUST,Wuhan430074)

Abstract:This paper introduces the hardware design of DSP basic system constructed by Flash Rom and SRAM,taking TMS320VC5402of C5000TM serial from Texas Instruments(TI)for example,and proposes some is2 sues which we shall pay attention to in hardware design.

K ey w ords:DSP,FPG A,CPLD

Class number:TP391

数字信号处理(DSP)芯片以其高速、低功耗和高集成度在军事、航天等领域大显身手;随着半导体工艺的进步和工业民用领域的大量采用,近几年来,DSP价格大幅下调(某些品种价格已与单片机相当),而性能却不断提高,现已广泛应用于通信、工业控制和消费领域,DSP正日益成为现代信息产业的重要基石。根据TI公司预测,DSP和Ana2 log器件将成为因特网时代的主导。

1 TI公司TMS320系列DSP

目前,TI公司力推的主流DSP为C24X TM、C54X TM和C6000TM,C24X TX系列是16位定点DSP,以较高的性价比广泛应用于马达控制、工业数字控制、信息家电等方面; C54X TM系列是C5000TM中的第二代产品,其特点是高速、低功耗,最适合用于便携式设备(如手机、数码相机、PDA等)和对功耗有严格要求的地方;C6000TM是一个32位高性能的DSP,它包括C62xx、C64xx、C67xx三个系列(其中C67xx为点DSP),采用了Veloci TT 超长指令字(VL IW)结构,C62xx、C64xx、C67xx的单片处理速度最高可分别达到2400M IPS、4800M IPS和1GFLOPS,主要用

Ξ收到本文时间:2002年11月19日

于无线基站、网络、视频和图像处理领域,需要注意的是它的功耗较大和对PCB的设计、制板工艺要求较高。

下一步C24X TM系列将过渡到C28X TM,它是C2000TM中高端产品。C5000TM系列的下一代产品将是速度更快、功耗更低、外设更丰富的C55X TM和OMAP TM系列。现在DSP 处理器发展的趋势是向结构多样化,集成单片化、用户化方向发展,开发工具更完善,评价体系更全面更专业。其中多核结构和DSP 核+RISC结构已经成为DSP的两个主要发展方向。

2 TMS320C54x性能

TMS320C54x是TI公司1996年推出的新一代16位定点DSP产品,它采用修正的哈佛结构,片内集成8条总线(1条程序存储器总线、3条数据存储器总线和4条地址总线)、在片存储器和在片复用外设。速度由30~532M IPS不等。

TMS320C54x主要特点:

?1个40位的算术逻辑单元,2个40位的累加器,2个40位的专用加法器,1个17×17的并行乘法器,1个40位的桶形移位器。8个辅助寄存器和1个软件栈。

?内部集成Viterbi加速器,用于提高Viterbi编译码的速度。

?可工作在三种低功耗方式(IDL E1、I2 DL E2、IDL E3)。

1192K WORD寻址空间(64KW程序空间、64KW数据空间、64KW I/O空间),某些型号的程序空间可扩展到8M WORD。

?片内存储区可灵活配置为程序/数据存储器。

?多种复用外设;McBSP、HPI、GPIO、TDM、DMA、Timer、PLL。

?双电源供电,提供P GE和B G A两种形式的封装。3 TMS320VC5402基本系统结构设计

TMS320VC5402-100是目前使用较广的一种型号,最高频率100MHz,市场零售价一般为50-70,性价比极高。它含4K×16bit片内ROM、16K×16bit片内DARAM、6个DMA通道、2个McBSP、2个Timer,外部程序空间可扩展到1M×16bit。

3.1主要控制逻辑信号说明

TMS320VC5402与读写控制逻辑有关的引脚信号说明如下:

引角名称I/O/Z说明

DS/,PS/,IS/O/Z

数据、程序、I/O空间选择

使能信号

MSTRB/O/Z存储器选通信号

R/W O/Z读/写信号

IOSTRB/O/Z I/O选通信号

3.2设计要求

由于DSP芯片的速度较高,为提高DSP 的运行效率和达到最大处理能力,一般对其外围芯片的速度也要求较高,同时又要考虑系统在线编程调试的要求。所以,DSP+FP2 G A/CPLD+Flash Rom的配置是DSP系统设计的一般要求,这个结构的最大的特点是结构灵活,有较强的通用性,适于模块化设计,从而能够提高算法效率;同时其开发周期较短,系统易于维护和扩展,适合于实时信号处理。对于片外数据空间一般建议选用高速的SRAM,尽量减少DSP的等待周期。用户程序一般在上电时从外部ROM加载到片内RAM区运行。

本设计选用器件:

程序存储器Flash Rom:256K×16一片

数据存储器SRAM:64K×16一片

可编程逻辑器件CPLD:一片

3.3程序区和数据区设置

对于程序存储器和数据存储器的设置方

法比较灵活,根据不同系统需要有多种选择方法。一种简单的方法是将Flash R om 定义到程序区(PS/作为片选),SRAM 定义到数据区(DS/作为片选);一种方法是将Flash Rom 和SRAM 全部定义到数据区,但由于数据区只

能寻址64K ,所以对于大于64K 的范围要使用分页处理;一种方法是将Flash Rom 和SRAM 全部定义到程序区,充分利用C5402

的程序空间可扩展到1M 字的特点,将Flash Rom 放置在低位,SRAM 放置到高位,可以简化对SRAM 存取的逻辑;还有一种方法是将SRAM 定义到程序区,Flash Rom 定义到数据区,这样做主要是有利于并行加载。3.4逻辑设计

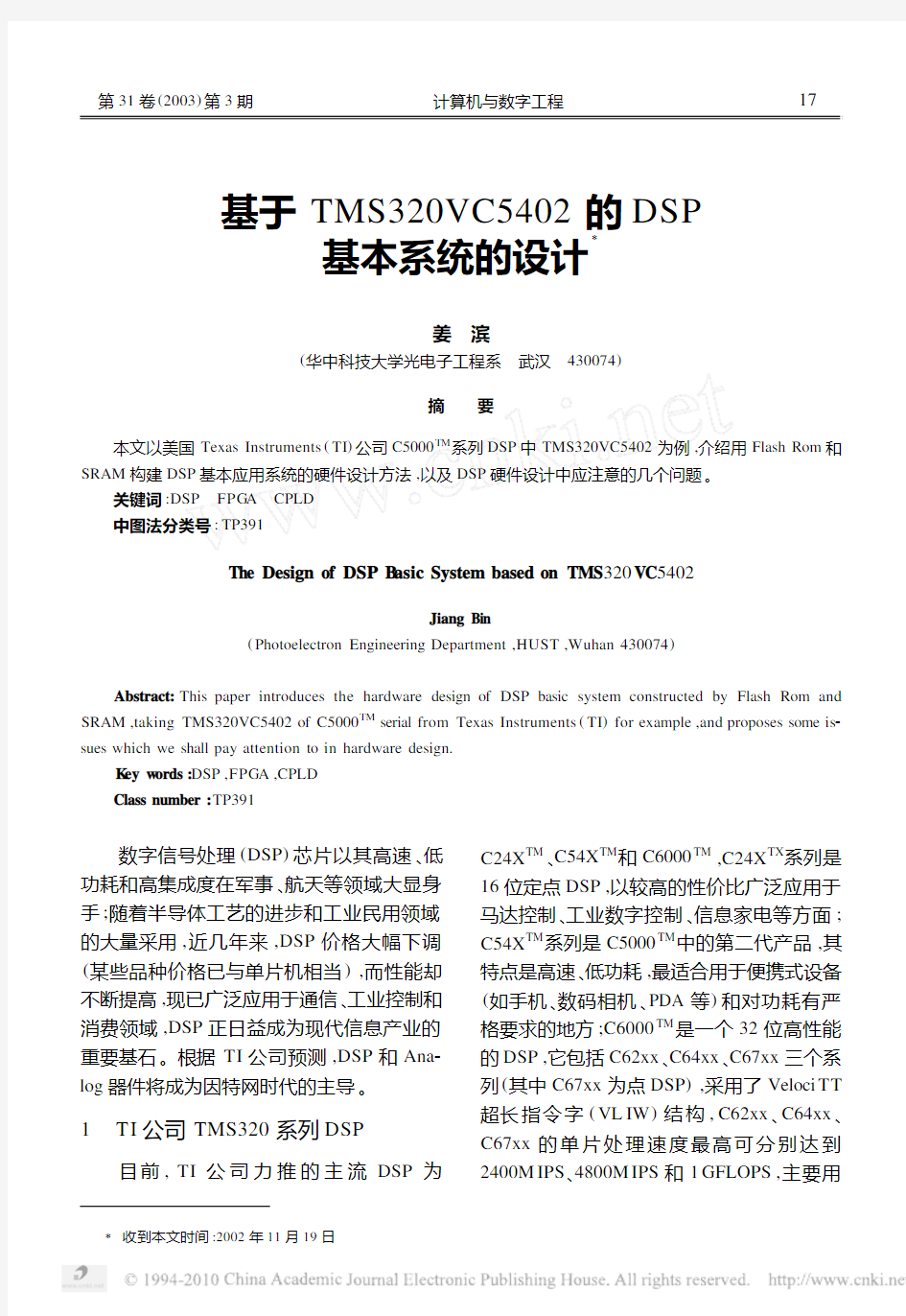

系统框图如图1。存储器的读写信号的产生

:

图1

WE/=MSTRB/+R/W

RE/=MSTRB/+!R/W

RE/连接到存储器的OE/端。由于数据

区0000-3FFFH 映射到片内,而仅在DROM =0时4000-7FFFH 32K 的空间可

映射到片外,所以为充分利用64K 的SRAM ,将它分成32K 的两页,由I/O 空间

产生SRAM 的高位地址A15,这样就能实现对64K 的SRAM 空间全部寻址(如果SRAM 大于64KW ,也可进行类似处理,只要分成多页即可)。A15信号产生逻辑为:

if (IOSTRB/‘EV EN T and IOSTRB/=’0’

)then D0#<=D0;

end if

4 设计中应注意的问题

对于一个有单片机系统设计经验的工程师而言,C5000TM 系统硬件设计并不是特别困难。虽然其主频一般在100MHz 以上,如果使用内部PLL ,外部频率也只需要10~20MHz 左右,所以一般不用特别考虑使用高

频电路的设计方法,仅将几个关键的控制信号处理好就可以了。但在设计中还需要注意以下几个问题:

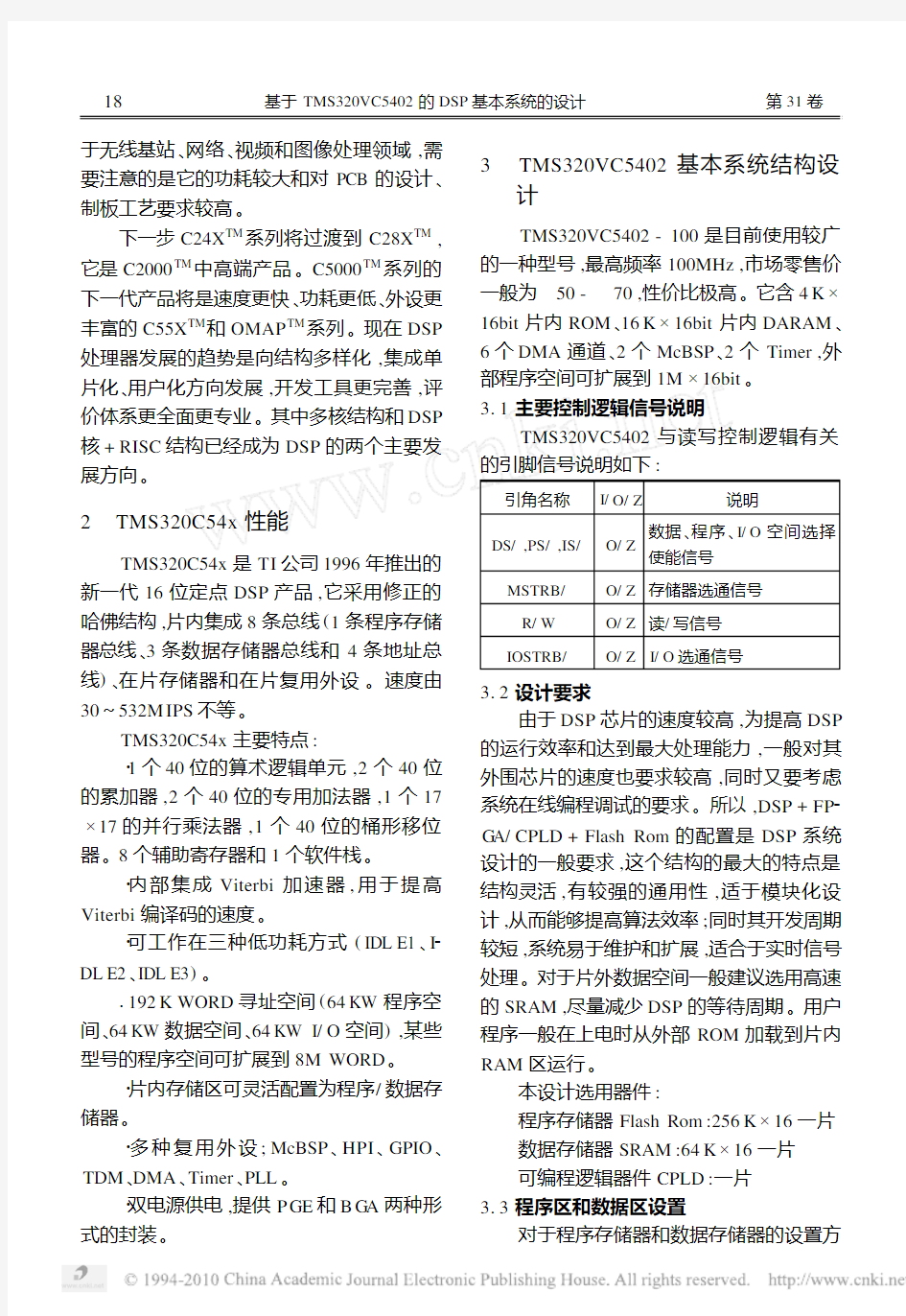

a )3V 和5V 混合设计问题

由于DSP 芯片一般是双电源供电,核电为1.5V ~2.5V (根据不同型号芯片而不

同),IO 引脚电源为3.3V ,而目前市场上5V 的器件还在大量使用,这样就存在3V 和5V (一般为外围接口芯片)电压器件混合设计问题,如果处理不好,将使DSP 芯片损坏。所以,在混合电压系统中,不同电源电压的逻辑器件相互接口时会存在以下3个主要问题:输入/输出引脚最大电压的容限问题;两个电源间电流的互串问题;必须满足的输入转换门限

电平问题。由于篇幅所限,在此不展开论述。图2为三种类型常用器件的电压门限的比较图,可供参考。具体设计时还要参考各器件的DAT ASHEET 。在此推荐几种常用的电压转换芯片:SN74LVCC3245、SN74LVCC4245、SN74LVC4245A 、SN74ALVC164245以及C BT

系列器件等。

图2

b )时钟设计

时钟信号的好坏直接决定了系统的稳定

性,C5000TM DSP 提供内部和外部两种方式的时钟发生模式。使用内部振荡器的优点是价格便宜、电路简单、节约面积、信号电平总能满足要求。一般建议使用内部振荡器。使用内部振荡器时,外部晶体推荐使用基次谐波晶体,等效串联电阻应小于30Ω,负载电容小于10pf ,在PCB 设计时晶体和电容应尽量靠近DSP 芯片。如果使用外部振荡器,则要考虑时钟信号电平不能大于电源电压、占空比要求、沿时间要求、高低电平宽度要求。建议在靠近时钟源的地方加入端接电阻以改善时钟信号性能。

c )FP G A 和CPLD 的选择CPLD 器件一般容量较小、价格适中,适

用于只需要小规模逻辑组合的地方。而FP 2G A 不仅可以替代复杂的逻辑器件和功能器

件,如FIFO 、双口RAM 等,实现在线编程配

置,还可以用FP G A 实现一些运算结构较规则的简单算法,对大量的原始数据进行算法预处理(比用DSP 完成速度快),然后再将数据交给DSP 进行复杂算法处理。这样可以大大提高DSP 系统处理效率。但一般FPA G 的价格较贵,对开发工具和环境的要求也较高。

参考文献

[1]TMS320VC5402FIXED -POIN T DIGITAL

SIGNAL PROCSEEOR ,Texas Instruments Inc ,2000

[2]戴明桢等.TMS320C54x 结构、原理及应用.北京

航空航天大学出版社

第六章Matlab/Dsp builder硬件模块设计 Matlab是国内强大的数学分析工具,广泛用于科学计算和工程计算,还可以进行复杂的数字信号处理系统的建模、参数估计及性能分析。Simulink是Matlab的一个组成部分,用于图形化建模仿真。DSP Builder是Altera公司推出的一个面向DSP开发的系统级工具,它构架在多个软件工具之上,并把系统级(算法级建模)和RTL级(硬件实现)两个设计领域的设计工具连接起来放在Matlab/Simulink平台上,而将QuartrsⅡ作为底层设计工具置于后台,从而最大程度地发挥了这三种工具的优势。DSP Builder作为Simulink中的一个工具箱,使得用FPGA设计DSP系统完全可以通过Simulink的图形化界面进行,只要简单地进行DSP Builder工具箱中的模块调用即可。Matlab/DSP Builder尤其适用于一些在Quartus Ⅱ上不方便完成或不能完成的设计项目(如涉及算法类及模拟信号处理与生产方面的系统处理)。DSP Builder还可以自动完成大部分的设计过程和仿真,直到把设计文件下载到FPGA 中。 DSP Builder提供了Quartus? II软件和MATLAB/Simulink工具之间的接口。其具有如下特性: 1.用于连接Mathwork的MATLAB(信号处理工具箱和滤波器设计工具箱),Simulink环境和Altera? 的Quartus II设计软件环境。 2.支持Altera 的DSP核,这些核均可以从Altera的网站上下载(例如:FIR Compiler、Reed-Solomon Compiler等等)。 3.可以利用Altera的DSP开发板来快速的实现设计的原型。 4.支持SignalTap? II逻辑分析仪(一种嵌入式的信号分析仪,它可以探测到DSP开发板上Altera器件内部的信号,并把数据引入到MATLAB的工作区以便于进行可视化的分析)。 5.包括了用户可以创建的定制的逻辑,用于配合SOPC Builder和Nios? II嵌入式处理器设计。 6.包括了PLL块,用于多时钟设计。 7.包括了状态机块。 8.针对DSP系统的算法和实现,支持统一的表示方法。 9.根据MATLAB和Simulink的测试矢量,可以自动生成VHDL测试激励或Quartus II 矢量文件(.vec)。 10.自动调用VHDL综合器和Quartus II编译器。 11.仿真可以设定为比特或周期精度。 12.提供多种的定点运算和逻辑操作,用于配合使用Simulink 软件。 13.支持多种Altera 的器件: Stratix、Stratix II 和 Stratix GX 器件; Cyclone 和 Cyclone II 器件; APEXII、APEX 20KC 和 APEX 20KE 器件; Mercury器件; ACEX? 1K 器件; FLEX? 10K 和 FLEX 6000 器件。 利用Matlab和DSP Builder进行模块设计也是SOPC技术的一个组成部分。这是由于利用Matlab/DSP Builder/QuartrsⅡ可完成纯硬件的DSP算法模型及实现,从而构成嵌入式系统外围接口的协处理模块,再进一步构成软件程序中的精简指令,DSP模块或其他功能模块可以成为单片FPGA电路系统中的一个组成部分,而且通过Matlab/DSP Builder,可以直接为Nios嵌入式处理器设计各类加速器,并以指令的形式加入到Nios的指令系统,从而成为

学号1049721203024 成绩 课程作业 DSP技术 题目:基于DSP2812定时器产生方波 学院(系):信息工程学院 专业班级:电子与通信工程124班 学生姓名:毛大龙 指导教师:孟哲 硬件□软件□ ppt□ 2012年 1 月 8 日

基于DSP2812定时器产生方波硬件设计 1.系统硬件设计内容 本次设计所设计的定时器(信号发生器)是采用TI公司生产的DSP芯片TMS320VC2812和D/A转换芯片TLC7528组成,产生稳定的方波。 我们主要是利用了数字信号处理器以及数模转换器两个部分,其中DSP芯片 TMS320VC2812是系统的核心处理器(控制器),TLC7528芯片是一个模数转换器,主要通过c2812芯片产生的时钟信号作为模数转换器的使能信号,TLC7528被驱动后,将系统产生的数字信号进行转化(数模转换),输出连续的模拟信号,即产生一定占空比的方波(初次我们设定的PWM波占空比为10%,产生的波形频率为1KHZ)最后通过示波器把模拟波形输出到示波器上,整个系统设计简单,清晰易懂。 2.系统设计思想 本系统是以TMS320VC2812这个DSP芯片为核心,通过DSP芯片进行控制和处理,从而产生稳定的方波(PWM)波形,通过D/A转换芯片实现把数字信号转换为模拟信号。整个硬件系统所要做的就是正确连接DSP芯片和D/A转换芯片,确保芯片正常工作,得到稳定的输出波形结果。 系统整体设计方案框图如下: 图1—1 系统整体硬件设计方案 3.系统硬件电路设计原理及框图 3.1系统硬件电路设计原理 整个硬件电路设计主要由中心处理器和模数转换器构成,其核心部分就是

5 DSP控制及硬件电路的设计 5.1 DSP控制 目前市面上流行的主控制器包括:51单片机系列、DSP系列和FPGA。在这中间:虽然51单片机有着成本低廉,体积小的优势;但因其计算能力弱,和外设较少的缺陷,无法满足本系统的需要。FPGA又称现场可编程门阵列,其时序脉冲准确,运算速度快,在需要进行大量重复运算的工程项目中得到了广泛应用。但FPGA以并行运算为主,并需要使用硬件描述语言(verilog 或VHDL)来实现电路设计,相比较单片机有很大不同,这造成开发难度较大,门槛较高。DSP是近几年得到快速发展的控制器,其外设丰富,运算速度快,能满足实时性要求较高的工业现场;尤其适用于控制算法复杂,计算量大的工程项目。 综合以上分析,本文矿用光伏供电系统选择DSP芯片 TMS320LF2407作为最终的控制芯片。TMS320LF2407芯片集成度高,运算速度快,外设丰富,价格适中,作为本设计的控制器,拥有其他芯片所不具备的优势。 5.1.1 TMS320LF2407的技术参数 (1)TMS320LF2407供电电压为3.3V,供电电压低,通态损耗小。最高工作频率40MHZ,指令周期短,指令周期为25ns,能够满足较大载波频率时的计算需求,具备实时控制能力。 (2)TMS320LF2407拥有丰富的存储器资源:包括32K字

程序闪存空间, 1.5K字的数据/程序随机存储器,544字的双口随 机存储器和2k字的单口RAM。除此之外,TMS320LF2407片内还集成有64K数据存储器空间以及64K程序存储器空间; 其I/O 寻址空间达64K,能有效满足使用需要; TMS320LF2407可用于扩展的外部存储器达到192K字。 (3)TMS320LF2407拥有两个事件管理器模块EV A和EVB。每个事件管理器模块上均集成有以下资源:两个16位通用定时器(通过倍频器可以达到很高的工作频率)和8个16位PWM 波生成通道; 为检测上升下降脉冲,片上集成有3个捕获单元。每个模块还可实现以下功能: 可编程的PWM死区控制功能,防止上下桥臂同接收触发信号,同时导通; 输出A、B、C三相对称和非对称触发信号;当接受低电平外部中断信号时,关闭PWM 通道片内光电编码器接口电路,停止发出触发信号; A/D转换功能。 (4)拥有10位模数转换器,最小转换时间为375ns,A/D转换器拥有独立和级连两种工作方式,使用事件管理器EV A、EVB 来实现触发。 (5)拥有16位串行外设接口模块(SPI),和串行通讯接口模块(SCI) (6)拥有5个外部中断资源,除复位中断外,还拥有两个电机驱动保护中断,和两个可屏蔽中断。 (7)除高性能模式外,电源管理还包括低功耗模式,在运算

目录 摘要...................................................... I 第1章绪论 ..................................................................... 错误!未定义书签。第2章总体设计 (1) 2.1系统要实现的功能 (1) 2.2系统的设计流程 (2) 1.2原理框图 (2) 第3章DSP最小系统电路设计.................................... 错误!未定义书签。 3.1电源电路设计 (2) 3.2复位电路设计 (3) 3.3时钟电路设计 (3) 3.4JTAG接口电路设计..................... 错误!未定义书签。 3.5DSP的串行接口电路设计 (4) 3.6存储器FLASH扩展设计 (4) 第4章软件设计 (5) 4.1仿真工作原理及测试步骤 (9) 4.2测试程序 (9) 4.3测试的注意事项 (10) 总结 ................................................................................... 错误!未定义书签。致谢 . (8) 参考文献 (8) 第1章绪论 DSP 有两种涵义,一种是Digital Signal Processing,指的是数字信号处理技术;一种是Digital Signal Processor,指的是数字信号处理器。两者是不可分割的,前者是理论上的技术,要通过后者变成实际产品,两者结合起来才成为解决某一实际问题和实现某一方案的手段。数字信号处理器是目前IT 领域中发展极为迅速的一类微处理器,其功能强大,应用范围相当广泛,能够完成实时的数字信号处理任务。DSP 的性能几乎决定了电子产品的性能。在人们生活当中,DSP可谓无处不在,例如手机,电视机,数码相机,MP3等等都有DSP的存在。DSP 已经成为通信、计算机和消费类电子产品等领域的基础器件。因此,只有理论的学习是不够的,设计一个DSP

2010 - 2011学年第 2 学期《DSP芯片的原理与开发应用》 题目:DSP硬件开发平台设计 班级: 学号: 姓名: 指导教师: 成绩:

基于DSP E1-16XS的硬件开发平台设计 引言 嵌入式系统硬件的核心是各种类型的嵌入式处理器,目前全世界嵌入式处理器的品种已经超过1000多种,流行体系结构有30多个系列,嵌入式处理器一般可以分为嵌入式微处理器、嵌入式微控制器、嵌入式DSP处理器和嵌入式片上系统。 与标准微处理器相比,嵌入式微处理器只保留了和嵌入式应用有关的功能,并且为了满足嵌入式应用的特殊要求,在工作温度、抗电磁干扰、可靠性等方面都做了各种增强。 DSP嵌入式系统是DSP系统嵌入到应用电子系统中的一种通用系统,这种系统既具有DSP器件在数据处理方面的优势,又具有应用目标所需要的技术特征,在许多嵌入式应用领域,既需要在数据处理方面具有独特的优势的DSP,也需要在智能控制方面技高一筹的微处理器(MCU);因此,将DSP与MCU融合在一起的双核平台,将成为DSP技术发展的一种新潮流。德国Hyperstone公司是真正把DSP 成功嵌入32位微处理器的厂商之一,尤其是它的E1-XS系列更是这方面的佼佼者。 1 E1-16XS微处理器结构概述 Hyperstone RISC/DSP架构框图如图1所示,Hyperstone内核是专为RISC和DSP功能的集成而设计的,但它不是两个不同内核在单个芯片上的简单组合,而是一个集成的内核和指令集。这一全集成的内核基于单处理器模式,带有单指令流。RISC和DSP单元间简单且高效的通信由1个96路的32位内部存储器实现,每个时钟周期内可以执行3条指令的操作,所以在100MHz的频率下可以达到300 MOPS这样优秀的性能。 Hyperstone E1-16XS是一款0.25μm CMOS工艺的微处理器,它结合了高性能的RISC微处理器和DSP处理器,利用简洁高效的指令,使嵌入式DSP处理器的实时性得以充分的发挥。该处理器主要具有如下的特点: 1、32位RISC/DSP处理器ALU、DSP单元和Load/Store单元并行处理,内部

- -- DSP最小系统电路设计 第1章绪论 DSP 有两种涵义,一种是Digital Signal Processing,指的是数字信号处理技术;一种是Digital Signal Processor,指的是数字信号处理器。两者是不可分割的,前者是理论上的技术,要通过后者变成实际产品,两者结合起来才成为解决某一实际问题和实现某一方案的手段。数字信号处理器是目前IT 领域中发展极为迅速的一类微处理器,其功能强大,应用范围相当广泛,能够完成实时的数字信号处理任务。DSP的性能几乎决定了电子产品的性能。在人们生活当中,DSP可谓无处不在,例如手机,电视机,数码相机,MP3等等都有DSP的存在。DSP 已经成为通信、计算机和消费类电子产品等领域的基础器件。因此,只有理论的学习是不够的,设计一个DSP最小系统,掌握这门重要技术,才能更深刻地理解和掌握DSP,为今后进行高精度、高性能的电子设计打下基础。 DSP 芯片是模拟信号变换成数字信号以后进行高速实时处理的专用微处理器,其处理速度比最快的CPU还快10-50 倍,具有处理速度高、功能强、性能价格比好以及速度功耗比高等特点,被广泛应用于具有实时处理要求的场合。 DSP 系统以DSP 芯片为基础,具有以下优点。 1.高速性 DSP 系统的运行速度较高,最新的DSP运行速度高达1000MIPS 以上。 2.编程方便 可编程DSP可使设计人员在开发过程中灵活方便的对软件进行修改和升级。 3.稳定性好 DSP 系统以数字处理为基础,受环境温度及噪声的影响比较小,可靠性高。 4.可重复性好 数字系统的性能基本上不受元器件参数性能的影响,便于测试、调试和大规模生产。 5.集成方便 DSP 系统中的数字部件有高度的规范性,便于大规模集成。 6.性价比高 常用的DSP价格在5美元以下。

绪论 DSP(数字信号处理器)是在模拟信号变换成数字信号以后进行高速实时信号处理的专用处理器,其处理速度比最快的CPU还快10~50倍。DSP具有可编程特性、运算速度快及接口灵活的特点,使得它在电子产品的研制中发挥着越来越大的作用。采用DSP器件来实现数字信号处理系统已经成为当今社会的发展趋势。 在DSP领域,美国TI(德州仪器)公司生产的TMS320家族DSP芯片以其独特的哈佛结构、硬件密集型方案以及灵活的指令系统,成为数字信号处理器产业中的领先者。其C5000系列是16位定点、速度为40M1PS~200MIPS、可编程、低功耗和高新能的DSP,在有线和无线通信、IP电话、便携式信息系统、手机、助听器等领域得到了广泛应用。 最小系统模块是使得DSP芯片能够工作的最精简模块。如何以最短的开发周期.开发出适于自己应用的高性能低成本的DSP最小系统模块,是进行DSP系统开发的第一步。最小系统模块设计包括硬件设计和软件设计。 本次设计是对TI公司生产的16位定点DSP芯片——TMS320VC5402进行最小系统模块硬件设计,它可以很方便地与外围模块组合成不同功能的应用系统。

1 DSP简介 1.1 DSP 的应用领域 在近 20 多年时间里,DSP 芯片的应用已经从军事、航空航天领域扩大到信号处理、通信、雷达、消费等许多领域。主要应用有信号处理、通信、语音、图形、图像、军事、仪器仪表、自动控制、医疗、家用电器等。 DSP 主要应用市场为3C 领域,占整个市场需求的 90%。数字蜂窝电话是 DSP 最为重要的应用领域之一。由于 DSP 具有强大的计算能力,使得移动通信的蜂窝电话重新崛起,并创造了一批诸如 GSM、CDMA 等全数字蜂窝电话网。在Modem 器件中,DSP 更是成效卓著,不仅大幅度提高了传输速率,且具有接收动态图像能力。另外,可编程多媒体 DSP 是 PC 领域的主流产品。以XDSL Modem为代表的高速通信技术与MPEG 图像技术相结合,使得高品位的音频和视频形式的计算机数据有可能实现实时交换。目前的硬盘空间相当大,这主要得益于CDSP(可定制 DSP)的巨大作用。预计在今后的 PC 机中,一个 DSP 即可完成全部所需的多媒体处理功能。DSP 也是消费类电子产品中的关键器件。由于 DSP的广泛应用,数字音响设备的更新换代周期变得非常短暂。用于图像处理的 DSP,一种用于 JPEG 标准的静态图像数据处理;另一种用于动态图像数据处理。 1.2 DSP的特点 DSP 芯片是模拟信号变换成数字信号以后进行高速实时处理的专用微处理器,其处理速度比最快的 CPU 还快 10-50 倍,具有处理速度高、功能强、性能价格比好以及速度功耗比高等特点,被广泛应用于具有实时处理要求的场合。 DSP 系统以 DSP 芯片为基础,具有以下优点。 1.高速性,DSP运行速度高达1000MIPS以上 2.编程方便,可编程DSP可使设计人员在开发过程中灵活方便的对软件进行修改和升级。

DSP课程设计 计算机与信息工程学院 通信工程产业班 李盛 一、基本DSP硬件系统设计 硬件任务设计概述 要求: 1、基本DSP硬件系统以TMS320C54x系列为核心处理器,包括最小系统、存 储器扩展、显示器、键盘、AD、DA等电路模块; 2、硬件设计画出主要芯片及电路模块之间的连接即可,重点考查电路模块方 案设计与系统地址分配; 3、设计方案以电路示意图为主,辅以必要的文字说明。 总体方案设计 本次硬件电路大体如下 TMS320C54x 模块电路原理图设计 1,电源模块 C54X数字信号处理器电源包括内核电源和外部接口电源,其外部接口电

源为3.3V,内部则根据型号不同而采用了不同的电压。由于C54X处理器大多应用于低功耗场合,因此电源电路的设计需要注意电源的转换效率和电路的复杂程度,而高效率的DC-DC转换电路就十分适合这种应用。 TPS54110能够提供1.5A的连续电流输出,其输出电压可调,低电压输出范围覆盖0.9~3.3V,能够较好地满足C54X处理器的供电要求,具体内容如下图: 2,时钟电路模块 任何工作都按时间顺序。用于产生时间的电路就是时钟电路。实时时钟电路DS1302是一种具有涓细电流充电能力的电路,主要特点是采用串行数据传输,可为掉电保护电源提供可编程的充电功能,并且可以关闭充电功能。采用普通32.768KHz晶振。 3,JTAG仿真模块 JTAG仿真器 4,复位电路模块 在系统上电过程中,如果电源电压还没有不稳定,这时DSP进入工作状态可能造成不可预知的后果,甚至造成硬件的损坏,因此有必要在系统中加入上电复位电路,上电复位电路的作用可以保证上电可靠,并在需要时实现手工复位。 5,数码管电路模块 一共12个引脚,8个段选。从上面左边第一排开始,按顺时针顺序依次往下遍历所有引脚。 6,SRAM:IS61LV6416模块 如图,电路SRAM中的借口与DSP芯片借口相连接构成电路系统。 硬件设计结果与分析 利用protel分别完成了电源电路,时钟电路,复位电路等外设电路的绘制,完成了最小系统的schematic原理图,并生成了PCB图,PCB板及3D效果图。 电路原理图

DSP系统的设计过程 总的来说,DSP系统的设计还没有非常好的正规设计方法。 DSP系统设计一般方法 第一步明确任务 必须根据应用系统的目标确定系统的性能指标、信号处理的要求,通常可用数据流程图、数学运算序列、正式的符号或自然语言来描述。 第二步算法仿真 一般来说,为了实现系统的最终目标,需要对输入的信号进行适当的处理,而处理方法的不同会导致不同的系统性能,要得到最佳的系统性能,就必须在这一步确定最佳的处理方法,即数字信号处理的算法(Algorithm),因此这一步也称算法模拟阶段。例如,语音压缩编码算法就是要在确定的压缩比条件下,获得最佳的合成语音。算法模拟所用的输入数据是实际信号经采集而获得的,通常以计算机文件的形式存储为数据文件。如语音压缩编码算法模拟时所用的语音信号就是实际采集而获得并存储为计算机文件形式的语音数据文件。有些算法模拟时所用的输入数据并不一定要是实际采集的信号数据,只要能够验证算法的可行性,输入假设的数据也是可以的。 第三步设计实时DSP系统 实时DSP系统的设计包括硬件设计和软件设计两个方面。硬件设计首先要根据系统运

算量的大小、对运算精度的要求、系统成本限制以及体积、功耗等要求选择合适的DSP芯片。然后设计DSP芯片的外围电路及其他电路。软件设计和编程主要根据系统要求和所选的DSP芯片编写相应的DSP汇编程序,若系统运算量不大且有高级语言编译器支持,也可用高级语言(如C语言)编程。由于现有的高级语言编译器的效率还比不上手工编写汇编语言的效率,因此在实际应用系统中常常采用高级语言和汇编语言的混合编程方法,即在算法运算量大的地方,用手工编写的方法编写汇编语言,而运算量不大的地方则采用高级语言。采用这种方法,既可缩短软件开发的周期,提高程序的可读性和可移植性,又能满足系统实时运算的要求。 DSP硬件和软件设计完成后,就需要进行硬件和软件的调试。软件的调试一般借助于DSP开发工具,如软件模拟器、DSP开发系统或仿真器等。调试DSP算法时一般采用比较实时结果与模拟结果的方法,如果实时程序和模拟程序的输入相同,则两者的输出应该一致。应用系统的其他软件可以根据实际情况进行调试。硬件调试一般采用硬件仿真器进行调试,如果没有相应的硬件仿真器,且硬件系统不是十分复杂,也可以借助于一般的工具进行调试。系统的软件和硬件分别调试完成后,就可以将软件脱离开发系统而直接在应用系统上运行。当然,DSP系统的开发,特别是软件开发是一个需要反复进行的过程,虽然通过算法模拟基本上可以知道实时系统的性能,但实际上模拟环境不可能做到与实时系统环境完全一致,而且将模拟算法移植到实时系统时必须考虑算法是否能够实时运行的问题。如果算法运算量太大不能在硬件上实时运行,则必须重新修改或简化算法。

5 DSP 控制及硬件电路的设计 5.1 DSP 控制 目前市面上流行的主控制器包括:51单片机系列、DSP 系列和FPGA 。在这中间:虽然51单片机有着成本低廉,体积小的优势;但因其计算能力弱,和外设较少的缺陷,无法满足本系统的需要。FPGA 又称现场可编程门阵列,其时序脉冲准确,运算速度快,在需要进行大量重复运算的工程项目中得到了广泛应用。但FPGA 以并行运算为主,并需要使用硬件描述语言(verilog 或VHDL )来实现电路设计,相比较单片机有很大不同,这造成开发难度较大,门槛较高。DSP 是近几年得到快速发展的控制器,其外设丰富,运算速度快,能满足实时性要求较高的工业现场;尤其适用于控制算法复杂,计算量大的工程项目。 综合以上分析,本文矿用光伏供电系统选择DSP 芯片 TMS320LF2407作为最终的控制芯片。TMS320LF2407芯片集成度高,运算速度快,外设丰富,价格适中,作为本设计的控制器,拥有其他芯片所不具备的优势。 5.1.1 TMS320LF2407的技术参数 (1)TMS320LF2407供电电压为3.3V ,供电电压低,通态损耗小。最高工作频率40MHZ ,指令周期短,指令周期为25ns ,能够满足较大载波频率时的计算需求,具备实时控制能力。 (2)TMS320LF2407拥有丰富的存储器资源:包括32K 字 程序闪存空间, 1.5K字的数据/程序随机存储器,544字的双口随机存储器和2k 字的单口RAM 。除此之外,TMS320LF2407片内还集成有64K 数据存储器空间以及 64K 程序存储器空间; 其I/O寻址空间达64K ,能有效满足使用需要; TMS320LF2407可用于扩展的外部存储器达到192K 字。

绪论 一个完整的DSP系统通常是由DSP芯片和其他相应的外围器件构成。DSP硬件系统主要包括电源电路、复位电路、时钟电路等。DSP的时钟电路用来为TMS320C54x芯片提供时钟信号,由一个内部振荡器和一个锁相环PLL组成,可通过晶振或外部的时钟驱动。以下我们将着重讨论DSP 硬件系统的基本设计中时钟电路的设计。 关键字TMS320C54x 时钟产生器软件可编程PLL

精品文档 目录 绪论................................................................................................. I 第一章时钟产生器. (1) 第二章软件可编程PLL (2) 第一节软件配置PLL介绍 (2) 一时钟模式介绍 (2) 二时钟模式设置 (2) 第二节程序 (6) 一倍频模式向倍频模式的切换 (6) 二倍频模式向分频模式的切换 (7) 三分频模式向倍频模式的切换 (8) 四分频模式向分频模式的切换 (9) 第三章心得体会 (10) 第四章参考文献 (11)

TMS320C54X X1X2\CLKIN 4 1 3 2 Vdd TSM320C54X X1X2\CLKIN C1C2 晶体 外部晶振

第二章软件可编程PLL 第一节软件配置PLL介绍 软件可编程PLL的特点是有高度的灵活性,它包括一个用来提供各种时钟乘数因子的时钟标定位、直接开放和禁止PLL的功能和一个PLL 锁存定时器,该锁存定时器可以延迟期间PLL时钟模式的切换直到所存操作完成为止。 一时钟模式介绍 带有内部的软件可编程PLL的期间可以设置为下面两种时钟模式:PLL模式:输入时钟(CLKIN)乘以31个可能的因子中的一个因子,这些因子取值范围为0.25~15,他们可以通过PLL电路获取。 DIV(分频器)模式:输入时钟(CLKIN)处以2或4.当用DIV模式时,所有的模拟部分,包括PLL电路,都被禁止以使功耗降到最小。 二时钟模式设置 复位操作之后,时钟操作模式立即由3个外部引脚CLKMD1,CLKMD2,CLKMD3的直来确定。3个CLKMD引脚所对应的模式如表1所示,复位之后,软件可编程PLL可以被变成设置为所需的模式。下列时钟模式引脚作何可以在复位时开放PLL:C5402中是CLKMD(3-1)=000b 110b.当这些时钟模式引脚被组合式,内部的PLL锁相定时器不再激活,因此,系统必须延迟释放复位以保证PLL锁存时间的延迟得以满足。