Question Answer

&

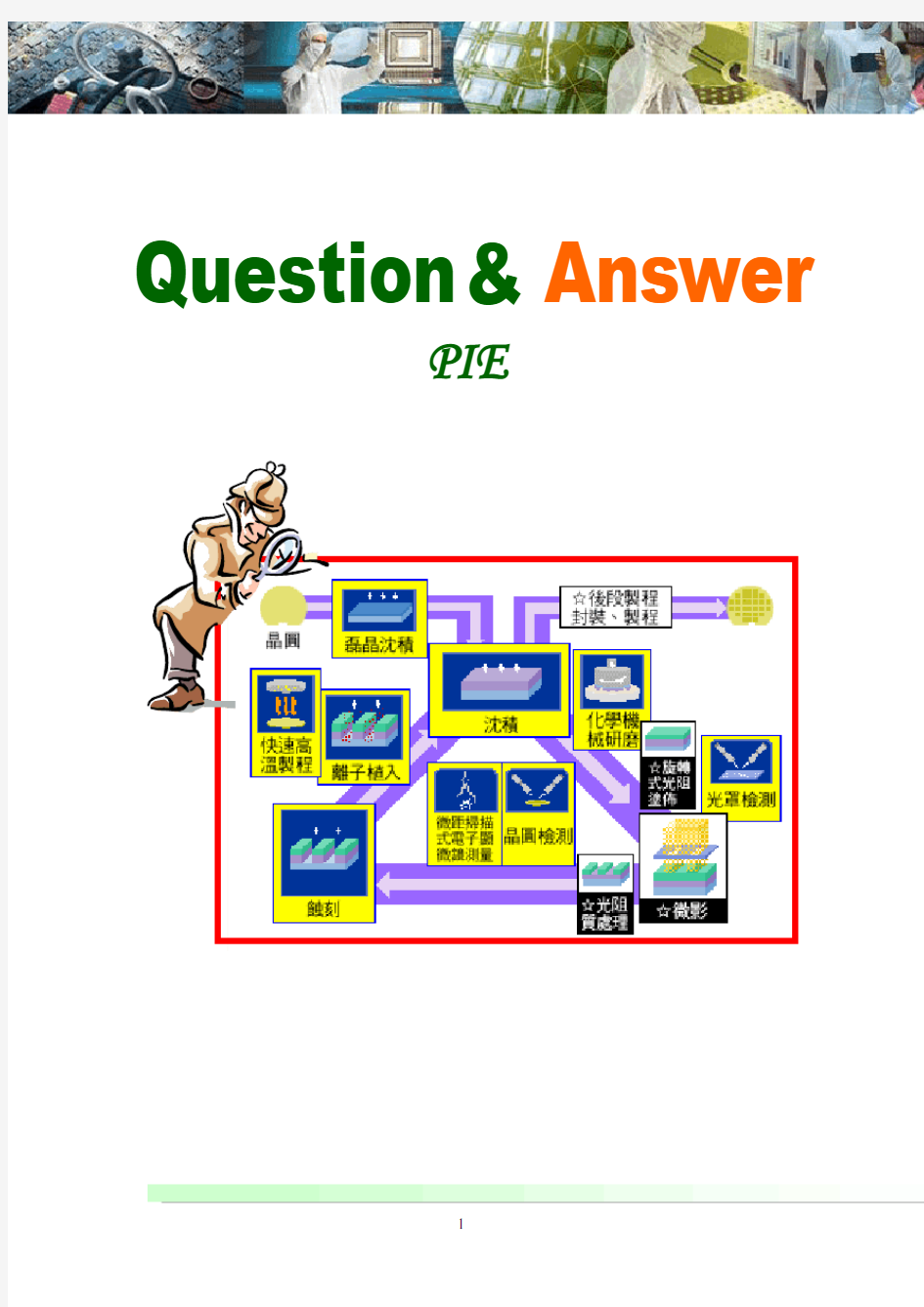

PIE

PIE

1. 何谓PIE? PIE的主要工作是什幺?

答:Process Integration Engineer(工艺整合工程师), 主要工作是整合各部门的资源, 对工艺持续进行改善, 确保产品的良率(yield)稳定良好。

2. 200mm,300mm Wafer 代表何意义?

答:8吋硅片(wafer)直径为200mm , 直径为300mm硅片即12吋.

3. 目前中芯国际现有的三个工厂采用多少mm的硅片(wafer)工艺?未来北京的Fab4(四厂)采用多少mm的wafer工艺?

答:当前1~3厂为200mm(8英寸)的wafer, 工艺水平已达0.13um工艺。未来北京厂工艺wafer将使用300mm(12英寸)。

4. 我们为何需要300mm?

答:wafer size 变大,单一wafer 上的芯片数(chip)变多,单位成本降低200→300 面积增加2.25倍,芯片数目约增加2.5倍

5. 所谓的0.13 um 的工艺能力(technology)代表的是什幺意义?

答:是指工厂的工艺能力可以达到0.13 um的栅极线宽。当栅极的线宽做的越小时,整个器件就可以变的越小,工作速度也越快。

6. 从0.35um->0.25um->0.18um->0.15um->0.13um 的technology改变又代表的是什幺意义?

答:栅极线的宽(该尺寸的大小代表半导体工艺水平的高低)做的越小时,工艺的难度便相对提高。从0.35um -> 0.25um -> 0.18um -> 0.15um -> 0.13um 代表着每一个阶段工艺能力的提升。

7. 一般的硅片(wafer)基材(substrate)可区分为N,P两种类型(type),何谓N, P-type wafer?

答:N-type wafer 是指掺杂negative元素(5价电荷元素,例如:P、As)的硅片, P-type 的wafer 是指掺杂positive 元素(3价电荷元素, 例如:B、In)的硅片。

200mm300mm

8〞12〞

8. 工厂中硅片(wafer)的制造过程可分哪几个工艺过程(module)?

答:主要有四个部分:DIFF(扩散)、TF(薄膜)、PHOTO(光刻)、ETCH (刻蚀)。其中DIFF又包括FURNACE(炉管)、WET(湿刻)、IMP(离子

注入)、RTP(快速热处理)。TF包括PVD(物理气相淀积)、CVD(化学气

相淀积) 、CMP(化学机械研磨)。硅片的制造就是依据客户的要求,不

断的在不同工艺过程(module)间重复进行的生产过程,最后再利用电

性的测试,确保产品良好。

9. 一般硅片的制造常以几P几M 及光罩层数(mask layer)来代表硅片工艺的

时间长短,请问几P几M及光罩层数(mask layer)代表什幺意义?

答:几P几M代表硅片的制造有几层的Poly(多晶硅)和几层的metal(金属导线).一般0.15um 的逻辑产品为1P6M( 1层的Poly和6层的metal)。而光罩层数(mask layer)代表硅片的制造必需经过几次的PHOTO(光刻).

10. Wafer下线的第一道步骤是形成start oxide 和zero layer? 其中start oxide 的目的是为何?

答:①不希望有机成分的光刻胶直接碰触Si 表面。

②在laser刻号过程中,亦可避免被产生的粉尘污染。

11. 为何需要zero layer?

答:芯片的工艺由许多不同层次堆栈而成的, 各层次之间以zero layer当做对准的基准。

12. Laser mark是什幺用途? Wafer ID 又代表什幺意义?

答:Laser mark 是用来刻wafer ID, Wafer ID 就如同硅片的身份证一样,一个ID代表一片硅片的身份。

13. 一般硅片的制造(wafer process)过程包含哪些主要部分?

答:①前段(frontend)-元器件(device)的制造过程。

②后段(backend)-金属导线的连接及护层(passivation)

14. 前段(frontend)的工艺大致可区分为那些部份?

答:①STI的形成(定义AA区域及器件间的隔离)

②阱区离子注入(well implant)用以调整电性

③栅极(poly gate)的形成

④源/漏极(source/drain)的形成

⑤硅化物(salicide)的形成

15. STI 是什幺的缩写? 为何需要STI?

答:STI: Shallow Trench Isolation(浅沟道隔离),STI可以当做两个组件(device)间的阻隔, 避免两个组件间的短路.

16. AA 是哪两个字的缩写? 简单说明 AA 的用途?

答:Active Area, 即有源区,是用来建立晶体管主体的位置所在,在其上形成源、漏和栅极。两个AA 区之间便是以STI 来做隔离的。

17. 在STI 的刻蚀工艺过程中,要注意哪些工艺参数?

答:①STI etch (刻蚀)的角度;

②STI etch 的深度; ③STI etch 后的CD 尺寸大小控制。

(CD control, CD=critical dimension)

18. 在STI 的形成步骤中有一道liner oxide (线形氧化层), liner oxide 的特性

功能为何?

答:Liner oxide 为1100C, 120 min 高温炉管形成的氧化层,其功能为:

①修补进STI etch 造成的基材损伤;

②将STI etch 造成的etch 尖角给于圆化( corner rounding)。

③④⑥定义光阻1625?Nitride

110?P AD Oxide Substrate 1625?Nitride 110?P AD Oxide

Substrate

一般深度16250?Nitride 110?P AD Oxide 光阻

Substrate 為4000A~5000A

进行蚀刻

填入氧化层

HDP Oxide 5800?HDP

1625?Nitride 110?P AD Oxide

200?Liner Oxide Substrate >1400?Nitride

110?PA D Oxide Substrate STI CMP 去除SiN & Oxide 完成STI

Substrate

AA 区

110?S AC Oxide ②⑤①角度

尺寸大小 圆化

要注意SiN 的remain 及

HDP oxide 的loss

这里的SAC oxide 是在 SiN remove 及 pad oxide remove 后,再重新长过的 oxide

19. 一般的阱区离子注入调整电性可分为那三道步骤? 功能为何?

答:阱区离子注入调整是利用离子注入的方法在硅片上形成所需要的组件

电子特性,一般包含下面几道步骤:

①Well Implant :形成N,P 阱区;

②Channel Implant :防止源/漏极间的漏电;

③Vt Implant :调整Vt (阈值电压)。 20. 一般的离子注入层次(Implant layer )工艺制造可分为那几道步骤?

答:一般包含下面几道步骤:

①光刻(Photo)及图形的形成; ②离子注入调整;

③离子注入完后的ash (plasma(等离子体)清洗)

④光刻胶去除(PR strip )

21. Poly (多晶硅)栅极形成的步骤大致可分为那些?

答:①Gate oxide(栅极氧化层)的沉积;

②Poly film 的沉积及SiON(在光刻中作为抗反射层的物质)的沉积);

③Poly 图形的形成(Photo); ④Poly 及SiON 的Etch ;

⑤Etch 完后的ash( plasma(等离子体)清洗)及光刻胶去除(PR strip );

⑥Poly 的Re-oxidation (二次氧化)。

22. Poly (多晶硅)栅极的刻蚀(etch)要注意哪些地方?

答:①Poly 的CD(尺寸大小控制; ②避免Gate oxie 被蚀刻掉,造成基材(substrate )受损.

23. 何谓 Gate oxide (栅极氧化层)?

答:用来当器件的介电层,利用不同厚度的 gate oxide ,可调节栅极电压对不同器件进行开关

栅极电压

Gate oxide Source

基Gate(栅极)

漏极电压

Drain 漏极

栅极氧化层

Substrate 基材源极本器件

示意图(Device)

24. 源/漏极(source/drain)的形成步骤可分为那些?

答:①LDD 的离子注入(Implant );

②Spacer 的形成; ③N+/P+IMP 高浓度源/漏极(S/D)注入及快速热处理(RTA :Rapid

Thermal Anneal)。

25. LDD 是什幺的缩写? 用途为何?

答:LDD: Lightly Doped Drain. LDD 是使用较低浓度的源/漏极, 以防止组件产生热载子效应的一项工艺。

26. 何谓 Hot carrier effect (热载流子效应)?

答:在线寛小于0.5um 以下时, 因为源/漏极间的高浓度所产生的高电场,导致载流子在移动时被加速产生热载子效应, 此热载子效应会对gate

oxide 造成破坏, 造成组件损伤。

27. 何谓Spacer? Spacer 蚀刻时要注意哪些地方?

答:在栅极(Poly)的两旁用dielectric (介电质)形成的侧壁,主要由

Ox/SiN/Ox 组成。蚀刻spacer 时要注意其CD 大小,profile(剖面轮廓),及remain oxide(残留氧化层的厚度)

28. Spacer 的主要功能?

答:①使高浓度的源/漏极与栅极间产生一段LDD 区域; ②作为Contact Etch 时栅极的保护层。

29. 为何在离子注入后, 需要热处理( Thermal Anneal)的工艺?

答:①为恢复经离子注入后造成的芯片表面损伤;

②使注入离子扩散至适当的深度; ③使注入离子移动到适当的晶格位置。

30. SAB 是什幺的缩写? 目的为何?

答:SAB :Sa licide b lock, 用于保护硅片表面,在RPO (Resist Protect Oxide)

的保护下硅片不与其它Ti, Co 形成硅化物(salicide) N-Well P

P N-Well P P

LDD 离子植入

N-Well P

P 形成Spacer N-Well P+P+

N+/P+高浓度离子植入

②

③

④①

31. 简单说明SAB 工艺的流层中要注意哪些?

答:①SAB 光刻后(photo ),刻蚀后(etch)的图案(特别是小块区域)。要

确定有完整的包覆(block )住必需被包覆(block )的地方。

②remain oxide (残留氧化层的厚度)。

32. 何谓硅化物( salicide)?

答:Si 与 Ti 或 Co 形成 TiSix 或 CoSix, 一般来说是用来降低接触电阻值(Rs, Rc )。

33. 硅化物(salicide)的形成步骤主要可分为哪些?

答:①Co(或Ti)+TiN 的沉积;

②第一次RTA (快速热处理)来形成Salicide 。

③将未反应的Co(Ti)以化学酸去除。

④第二次RTA (用来形成Ti 的晶相转化, 降低其阻值)。

34. MOS 器件的主要特性是什幺?

答:它主要是通过栅极电压(Vg )来控制源,漏极(S/D)之间电流,实现其开关特性。

35. 我们一般用哪些参数来评价device 的特性?

答:主要有Idsat 、Ioff 、Vt 、Vbk(breakdown)、Rs 、Rc ;一般要求Idsat 、

Vbk (breakdown)值尽量大, Ioff 、Rc 尽量小,Vt 、Rs 尽量接近设计值.

36. 什幺是Idsat?Idsat 代表什幺意义?

答:饱和电流。也就是在栅压(Vg)一定时,源/漏(Source/Drain)之间流动的最大电流.

37. 在工艺制作过程中哪些工艺可以影响到Idsat?

答:Poly CD(多晶硅尺寸)、Gate oxide Thk(栅氧化层厚度)、AA(有源区)宽度、Vt imp.条件、LDD imp.条件、N+/P+ imp. 条件。

38. 什幺是Vt? Vt 代表什幺意义?

答:阈值电压(Threshold Voltage ),就是产生强反转所需的最小电压。当

栅极电压Vg N+ RPO 保护的地方不会形成Salicide 39. 在工艺制作过程中哪些工艺可以影响到Vt? 答:Poly CD 、Gate oxide Thk. (栅氧化层厚度)、AA(有源区)宽度及Vt imp.条件。 40. 什幺是Ioff? Ioff 小有什幺好处 答:关态电流,Vg=0时的源、漏级之间的电流,一般要求此电流值越小越 好。Ioff 越小, 表示栅极的控制能力愈好, 可以避免不必要的漏电流(省电)。 41. 什幺是 device breakdown voltage? 答:指崩溃电压(击穿电压),在 Vg=Vs=0时,Vd 所能承受的最大电压,当Vd 大于此电压时,源、漏之间形成导电沟道而不受栅压的影响。 在器件越做越小的情况下,这种情形会将会越来越严重。 42. 何谓ILD? IMD? 其目的为何? 答: ILD :Inter Layer Dielectric, 是用来做device 与 第一层metal 的 隔离(isolation ),而IMD :Inter Metal Dielectric ,是用来做metal 与 metal 的隔离(isolation ).要注意ILD 及IMD 在CMP 后的厚度控制。 43. 一般介电层ILD 的形成由那些层次组成? 答:① SiON 层沉积(用来避免上层B,P 渗入器件); ② BPSG (掺有硼、磷的硅玻璃)层沉积; ③ PETEOS (等离子体增强正硅酸乙脂)层沉积; 最后再经ILD Oxide CMP(SiO 2的化学机械研磨)来做平坦化。 44. 一般介电层IMD 的形成由那些层次组成? 答:① SRO 层沉积(用来避免上层的氟离子往下渗入器件); ② HDP-FSG (掺有氟离子的硅玻璃)层沉积; ③ PE-FSG (等离子体增强,掺有氟离子的硅玻璃)层沉积; 使用FSG 的目的是用来降低dielectric k 值, 减低金属层间的寄生电容。 最后再经IMD Oxide CMP(SiO 2的化学机械研磨)来做平坦化。 IMD Metal-1 CT 45. 简单说明Contact(CT)的形成步骤有那些? 答:Contact是指器件与金属线连接部分,分布在poly、AA上。 ①Contact的Photo(光刻); ②Contact的Etch及光刻胶去除(ash & PR strip); ③Glue layer(粘合层)的沉积; ④CVD W(钨)的沉积 ⑤W-CMP 。 46. Glue layer(粘合层)的沉积所处的位置、成分、薄膜沉积方法是什幺? 答:因为W较难附着在Salicide上,所以必须先沉积只Glue layer再沉积W Glue layer是为了增强粘合性而加入的一层。主要在salicide与W(CT)、 W(VIA)与metal之间, 其成分为Ti和TiN, 分别采用PVD 和CVD方 式制作。 47. 为何各金属层之间的连接大多都是采用CVD的W-plug(钨插塞)? 答:①因为W有较低的电阻; ②W有较佳的step coverage(阶梯覆盖能力)。 48. 一般金属层(metal layer)的形成工艺是采用哪种方式?大致可分为那些步骤? 答:①PVD (物理气相淀积) Metal film 沉积 ②光刻(Photo)及图形的形成; ③Metal film etch 及plasma(等离子体)清洗(此步驺为连序工艺,在同 一个机台内完成,其目的在避免金属腐蚀) ④ Solvent光刻胶去除。 49. Top metal和inter metal的厚度,线宽有何不同? 答:Top metal通常要比inter metal厚得多,0.18um工艺中inter metal为4KA,而top metal要8KA.主要是因为top metal直接与外部电路相接,所承受 负载较大。一般top metal 的线宽也比inter metal宽些。 50. 在量测Contact /Via(是指metal与metal之间的连接)的接触窗开的好不好时, 我们是利用什幺电性参数来得知的? 答:通过Contact 或Via的Rc值,Rc值越高,代表接触窗的电阻越大, 一般来说我们希望Rc 是越小越好的。 51. 什幺是Rc? Rc代表什幺意义? 答:接触窗电阻,具体指金属和半导体(contact)或金属和金属(via),在相接触时在节处所形成的电阻,一般要求此电阻越小越好。 52. 影响Contact (CT) Rc的主要原因可能有哪些? 答:①ILD CMP 的厚度是否异常; ②CT 的CD大小; ③CT 的刻蚀过程是否正常; ④接触底材的质量或浓度(Salicide,non-salicide); ⑤CT的glue layer(粘合层)形成; ⑥CT的W-plug。 53. 在量测Poly/metal导线的特性时, 是利用什幺电性参数得知? 答:可由电性量测所得的spacing & Rs 值来表现导线是否异常。 54. 什幺是spacing?如何量测? 答:在电性测量中,给一条线(poly or metal)加一定电压,测量与此线相邻但不相交的另外一线的电流,此电流越小越好。当电流偏大时代表导线间 可能发生短路的现象。 55. 什幺是Rs? 答:片电阻(单位面积、单位长度的电阻),用来量测导线的导电情况如何。 一般可以量测的为AA(N+,P+), poly & metal. 56. 影响Rs有那些工艺? 答:①导线line(AA, poly & metal)的尺寸大小。(CD=critical dimension) ②导线line(poly & metal)的厚度。 ③导线line (AA, poly & metal) 的本身电导性。(在AA, poly line 时可 能为注入离子的剂量有关) 57. 一般护层的结构是由哪三层组成? 答:①HDP Oxide(高浓度等离子体二氧化硅) ②SRO Oxide(Silicon rich oxygen富氧二氧化硅) ③SiN Oxide 58. 护层的功能是什幺? 答:使用oxide或SiN层, 用来保护下层的线路,以避免与外界的水汽、空气相接触而造成电路损害。 59. Alloy 的目的为何? 答:①Release 各层间的stress(应力),形成良好的层与层之间的接触面 ②降低层与层接触面之间的电阻。 60. 工艺流程结束后有一步骤为WAT,其目的为何? 答:WAT(wafer acceptance test), 是在工艺流程结束后对芯片做的电性测量,用来检验各段工艺流程是否符合标准。(前段所讲电学参数Idsat, Ioff, Vt, Vbk(breakdown), Rs, Rc就是在此步骤完成) 61. WAT电性测试的主要项目有那些? 答:①器件特性测试; ②Contact resistant (Rc); ③Sheet resistant (Rs); ④Break down test; ⑤电容测试; ⑥Isolation (spacing test)。 62. 什么是WAT Watch系统? 它有什么功能? 答:Watch系统提供PIE工程师一个工具, 来针对不同WAT测试项目,设置不同的栏住产品及发出Warning警告标准, 能使PIE工程师早期发现工艺上的问 题。 63. 什么是PCM SPEC? 答:PCM (Process control monitor) SPEC广义而言是指芯片制造过程中所有工艺量测项目的规格,狭义而言则是指WAT测试参数的规格。 64. 当WAT量测到异常是要如何处理? 答:①查看WAT机台是否异常,若有则重测之 ②利用手动机台Double confirm ③检查产品是在工艺流程制作上是否有异常记录 ④切片检查 65. 什么是EN? EN有何功能或用途? 答:由CE发出,详记关于某一产品的相关信息(包括Technology ID, Reticle and some split condition ETC….)或是客户要求的事项(包括HOLD, Split, Bank, Run to complete, Package….),根据EN提供信息我们才可以建立 Process flow及处理此产品的相关动作。 66. PIE工程师每天来公司需要Check哪些项目(开门五件事)? 答:①Check MES系统, 察看自己Lot情况 ②处理in line hold lot.(defect, process, WAT) ③分析汇总相关产品in line数据.(raw data & SPC) ④分析汇总相关产品CP test结果 ⑤参加晨会, 汇报相关产品信息 67. WAT工程师每天来公司需要Check哪些项目(开门五件事)? 答:①检查WAT机台Status ②检查及处理WAT hold lot ③检查前一天的retest wafer及量测是否有异常 ④是否有新产品要到WAT ⑤交接事项 68. BR工程师每天来公司需要Check哪些项目(开门五件事)? 答:①Pass down ②Review urgent case status ③Check MES issues which reported by module and line ④Review documentation ⑤Review task status 69. ROM是什幺的缩写? 答:ROM: Read only memory唯读存储器 读写功能特性耗电速度组成 DRAM具有读写功用随机存取记忆体 (Random access memory) 电力消失后更不存在 已记忆的资料 处理速度较SRAM慢 一个电晶体 一个电容 SRAM具有读写功用随机存取记忆体 (Random access memory) 电力消失后更不存在 已记忆的资料 处理速度最快一般是6个电晶体 EPROM具有读写功用只读记忆体 (Read only memory) 电力消失后仍然存在 已记忆的资料 ROM只能读不能写只读记忆体 (Read only memory) 电力消失后仍然存在 已记忆的资料 70. 何谓YE? 答:Yield Enhancement 良率改善 71. YE在FAB中所扮演的角色? 答:针对工艺中产生缺陷的成因进行追踪,数据收集与分析,改善评估等工作。 进而与相关工程部门工程师合作提出改善方案并作效果评估。 72. YE工程师的主要任务? 答:①降低突发性异常状况。(Excursion reduction) ②改善常态性缺陷状况。(Base line defect improvement) 73. 如何reduce excursion? 答:有效监控各生产机台及工艺上的缺陷现况, defect level异常升高时迅速予以查明,并协助异常排除与防止再发。 74. 如何improve base line defect? 答:藉由分析产品失效或线上缺陷监控等资料,而发掘重点改善目标。持续不断推动机台与工艺缺陷改善活动,降低defect level使产品良率于稳定中不断提 升 75. YE 工程师的主要工作内容? 答:①负责生产过程中异常缺陷事故的追查分析及改善工作的调查与推动。 ②评估并建立各项缺陷监控(monitor)与分析系统。 ③开发并建立有效率的缺陷工程系统,提升缺陷分析与改善的能力。 ④协助module建立off-line defect monitor system, 以有效反应生产机台状 况。 76. 何谓Defect? 答:Wafer上存在的有形污染与不完美,包括 ① Wafer上的物理性异物(如:微尘,工艺残留物,不正常反应生成物)。 ②化学性污染(如:残留化学药品,有机溶剂)。 ③图案缺陷(如:Photo或etch造成的异常成象,机械性刮伤变形,厚度 不均匀造成的颜色异常)。 ④ Wafer本身或制造过程中引起的晶格缺陷。 77. Defect的来源? 答:①素材本身:包括wafer,气体,纯水,化学药品。 ②外在环境:包含洁净室,传送系统与程序。 ③操作人员:包含无尘衣,手套。 ④设备零件老化与制程反应中所产生的副生成物。 78. Defect的种类依掉落位置区分可分为? 答:①Random defect : defect分布很散乱 ②cluster defect : defect集中在某一区域 ③Repeating defect : defect重复出现在同一区域 79. 依对良率的影响Defect可分为? 答:①Killer defect =>对良率有影响 ②Non-Killer defect =>不会对良率造成影响 ③Nuisance defect =>因颜色异常或film grain造成的defect,对良率亦无影响 80. YE一般的工作流程? 答:①Inspection tool扫描wafer ②将defect data传至YMS ③检查defect增加数是否超出规格 ④若超出规格则将wafer送到review station review ⑤确认defect来源并通知相关单位一同解决 81. YE是利用何种方法找出缺陷(defect)? 答:缺陷扫描机(defect inspection tool)以图像比对的方式来找出defect.并产出defect result file. 82. Defect result file包含那些信息? 答:①Defect大小 ②位置,坐标 ③Defect map 83. Defect Inspection tool 有哪些型式? 答:Bright field & Dark Field 84. 何谓Bright field? 答:接收反射光讯号的缺陷扫描机 85. 何谓Dark field? 答:接收散射光讯号的缺陷扫描机 86. Bright field 与Dark field 何者扫描速度较快? 答:Dark field 87. Bright field 与Dark field 何者灵敏度较好? 答:Bright field 88. Review tool 有哪几种? 答:Optical review tool 和 SEM review tool. 89. 何为optical review tool? 答:接收光学信号的optical microscope. 分辨率较差,但速度较快,使用较方便 90. 何为SEM review tool? 答:SEM (scanning electron microscope) review tool 接收电子信号. 分辨率较高但速度慢,可分析defect 成分,并可旋转或倾斜defect 来做分析 91. Review Station 的作用? 答:藉由 review station 我们可将 Inspection tool 扫描到的defect 加以分类,并做成分析,利于寻找defect 来源 92. YMS 为何缩写? 答:Yield Management System 93. YMS 有何功能? 答:① 将inspection tool 产生的defect result file 传至review station ② 回收review station 分类后的资料 ③ 储存defect 影像 Light source visible UV and visible Laser (532nm,2W)Laser (488nm,75mW)光源入射角度 normal(直射)normal normal oblique(斜射)WPH (每小时产出数量) 2~3pcs 2~3pcs 17pcs(5X)~14pcs(5um)scan layer Throughput 快Sensitivity 较差价格低 优缺点Throughput 慢Sensitivity 好 价格高L/S layer,CMP film deposition,CMP Bright field Dark field 94. 何谓Sampling plan? 答:即为采样频率,包含: ①那些站点要Scan ②每隔多少Lot要扫1个Lot ③每个Lot要扫几片Wafer ④每片Wafer要扫多少区域 95. 如何决定那些产品需要scan? 答:①现阶段最具代表性的工艺技术。 ②有持续大量订单的产品。 96. 选择监测站点的考虑为何? 答:①以Zone partition的观念,两个监测站点不可相隔太多工艺的步骤。 ②由yield loss analysis手法找出对良率影响最大的站点。 ③容易作线上缺陷分析的站点。 97. 何谓Zone partition 答:将工艺划分成数个区段,以利辨认缺陷来源。 98. Zone partition的做法? 答:①应用各检察点既有的资料可初步判断工艺中缺陷主要的分布情况。 ②应用既有的缺陷资料及defect review档案可初步辨认异常缺陷发生的工 艺站点。 ③利用工程实验经由较细的Zone partition可辨认缺陷发生的确切站点或机 台 99. 何谓yield loss analysis? 答:收集并分析各工艺区间所产生的缺陷对产品良率的影响以决定改善良率的可能途径。 100. yield loss analysis的功能为何? 答:①找出对良率影响最大的工艺步骤。 ②经由killing ratio的计算来找出对良率影响最大的缺陷种类。 ③评估现阶段可达成的最高良率。 101. 如何计算killing ratio? 答:藉由defect map与yield map的迭图与公式的运算,可算出某种缺陷对良率的杀伤力。 从什么地方开始讲呢?就从产业链开始吧。 有需求就有生产就有市场。 市场需求(或者潜在的市场需求)的变化是非常快的,尤其是消费类电子产品。这类产品不同于DRAM,在市场上总是会有大量的需求。也正是这种变化多端的市场需求,催生了两个种特别的半导体行业——Fab和Fab Less Design House。 我这一系列的帖子主要会讲Fab,但是在一开头会让大家对Fab周围的东西有个基本的了解。 像Intel、Toshiba这样的公司,它既有Design的部分,也有生产的部分。这样的庞然大物在半导体界拥有极强的实力。同样,像英飞凌这样专注于DRAM 的公司,活得也很滋润。至于韩国三星那是个什么都搞的怪物。这些公司,他们通常都有自己的设计部门,自己生产自己的产品。有些业界人士把这一类的企业称之为IDM。 但是随着技术的发展,要把更多的晶体管集成到更小的Chip上去,Silicon Process的前期投资变得非常的大。一条8英寸的生产线,需要投资7~8亿美金;而一条12英寸的生产线,需要的投资达12~15亿美金。能够负担这样投资的全世界来看也没有几家企业,这样一来就限制了芯片行业的发展。准入的高门槛,使许多试图进入设计行业的人望洋兴叹。 这个时候台湾半导体教父张忠谋开创了一个新的行业——foundry。他离开TI,在台湾创立了TSMC,TSMC不做Design,它只为做Design的人生产Wafer。这样,门槛一下子就降低了。随便几个小朋友,只要融到少量资本,就能够把自己的设计变成产品,如果市场还认可这些产品,那么他们就发达了。同一时代,台湾的联华电子也加入了这个行当,这就是我们所称的UMC,他们的老大是曹兴诚。——题外话,老曹对七下西洋的郑和非常钦佩,所以在苏州的UMC友好厂(明眼人一看就知道是UMC在大陆偷跑)就起名字为“和舰科技”,而且把厂区的建筑造的非常有个性,就像一群将要启航的战船。 ----想到哪里就说到哪里,大家不要见怪。 作者:core-logic回复日期:2005-12-2616:44:42 ============================================= 在TSMC和UMC的扶植下,Fab Less Design House的成长是非常可观的。从UMC中分离出去的一个. 小小的Design Group成为了著名的“股神”联发科。当年它的VCD/DVD 相关芯片红透全世界,股票也涨得令人难以臵信。我认识一个台湾人的老婆,在联发科做Support工作,靠它的股票在短短的四年内赚了2亿台币,从此就再也不上班了。 Fab Less Design House的成功让很多的人大跌眼镜。确实,单独维持Fab的成本太高了,所以很多公司就把自己的Fab剥离出去,单独来做Design。 Foundry专注于Wafer的生产,而Fab Less Design House专注于Chip的设计,这就是分工。大家都不能坏了行规。如果Fab Less Design House觉得自己太牛了,想要自建Fab来生产自己的Chip,那会遭到Foundry的抵制,像UMC就利用专利等方法强行收购了一家Fab Less Design House辛辛苦苦建立起来的Fab。而如果Foundry自己去做Design,那么Fab Less Design House就会心存疑惑——究竟自己的Pattern Design会不会被对方盗取使用?结果导致Foundry的吸引力降低,在产业低潮的时候就会被Fab Less Design House抛弃。 ' 总体来讲,Fab Less Design House站在这个产业链的最高端,它们拥有利润的最大头,它们投入小,风险高,收益大。其次是Foundry(Fab),它们总能拥有可观的利润,它们投入大,风险小,受益中等。再次是封装测试(Package&Testing),它们投入中等,风险小,收益较少。当然,这里面没有记入流通领域的分销商。事实上分销商的收益和投入是无法想象和计量的。我认识一个分销商,他曾经把MP3卖到了50%的利润,但也有血本无归的时候。 所以Design House是“三年不开张,开张吃三年。”而Fab和封装测试则是赚个苦力钱。对于Fab来讲,同样是0.18um的8英寸Wafer,价格差不多,顶多根据不同的Metal层数来算钱,到了封装测试那里会按照封装所用的模式和脚数来算钱。这样Fab卖1200美元的Wafer被Designer拿去之后,实际上卖多少钱就与Fab它们没有关系了,也许是10000美元,甚至更高。但如果市场不买账,那么Design House可能就直接完蛋了,因为它的钱可能只够到Fab去流几个Lot的。 作者:core-logic回复日期:2005-12-2617:44:19 ============================================= 我的前老板曾经在台湾TSMC不小心MO,结果跑死掉一批货,结果导致一家Design House倒闭。题外话——Fab的小弟小妹看到动感地带的广告都气坏了,什么“没事MO一下”,这不找抽吗?没事MO(Miss Operation)一下,一批货25片损失两万多美元,奖金扣光光,然后被fire。 在SMIC,我带的一个工程师MO,结果导致一家海龟的Design House直接关门放狗。这个小子很不爽的跳槽去了一家封装厂,现在混得也还好。 所以现在大家对Fab的定位应该是比较清楚的了。 Fab有过一段黄金时期,那是在上个世纪九十年代末。TSMC干四年的普通工程师一年的股票收益相当于100个月的工资(本薪),而且时不时的公司就广播,“总经理感谢大家的努力工作,这个月加发一个月的薪水。” 但是过了2001年,也就是SMIC等在大陆开始量产以来,受到压价竞争以及市场不景气的影响,Fab的好时光就一去不复返了。高昂的建厂费用,高昂的成本折旧,导致连SMIC这样产能利用率高达90%的Fab还是赔钱。这样一来,股票的价格也就一落千丈,其实不光是SMIC,像TSMC、UMC的股票价格也大幅下滑。 但是已经折旧折完的Fab就过得很滋润,比如先进(ASMC),它是一个5英寸、6英寸的Fab,折旧早完了,造多少赚多少,只要不去盖新厂,大家分分利润,日子过的好快活。 所以按照目前中国大陆这边的状况,基本所有的Fab都在盖新厂,这样的结论就是:很长的一段时间内,Fab不会赚钱,Fab的股票不会大涨,Fab的工程师不会有过高的收入。虽然一直在亏本,但是由于亏本的原因主要是折旧,所以Fab总能保持正的现金流。而且正很多。所以结论是:Fab赔钱,但绝对不会倒闭。如果你去Fab工作,就不必担心因为工厂倒闭而失业。 作者:core-logic回复日期:2005-12-2621:30:35 ============================================= 下面讲讲Fab对人才的需求状况。 Fab是一种对各类人才都有需求的东西。无论文理工,基本上都可以再Fab 里找到职位。甚至学医的MM都在SMIC找到了厂医的位臵。很久以前有一个TSMC工程师的帖子,他说Fab对人才的吸纳是全方位的。(当然坏处也就是很多人才的埋没。)有兴趣的网友可以去找来看看。 一般来讲,文科的毕业生可以申请Fab厂的HR,法务,文秘,财会,进出口,采购,公关之类的职位。但是由于是Support部门这些位臵的薪水一般不太好。那也有些厉害的MM选择做客户工程师(CE)的,某些MM居然还能做成制程工程师,真是佩服啊佩服。 理工科的毕业生选择范围比较广: 计算机、信息类的毕业生可以选择作IT,在Fab厂能够学到一流的CIM技术,但是由于不受重视,很多人学了本事就走人先了。 工程类的毕业生做设备(EE)的居多,一般而言,做设备不是长久之计。可以选择做几年设备之后转制程,或者去做厂商(vendor),钱会比较多。当然,也有少数人一直做设备也发展得不错。比较不建议去做厂务。 材料、物理类的毕业生做制程(PE)的比较多,如果遇到老板不错的话,制程倒是可以常做的,挺两年,下面有了小弟小妹就不用常常进Fab了。如果做的不爽,可以转PIE或者TD,或者厂商也可以,这个钱也比较多。 电子类的毕业生选择做制程整合,也就是Integration(PIE)得比较多,这个是在Fab里主导的部门,但如果一开始没有经验的话,容易被PE忽悠。所以如果没有经验就去做PIE的话,一定要跟着一个有经验的PIE,不要管他是不是学历比你低。 所有硕士或者以上的毕业生,尽量申请TD的职位,TD的职位比较少做杂七杂八的事情。但是在工作中需要发挥主动性,不然会学不到东西,也容易被PIE之类的人骂。 将来有兴趣去做封装、测试的人可以选择去做产品工程师(PDE)。 有兴趣向Design转型的人可以选择去做PIE或者PDE。 喜欢和客户打交道的人可以选择去做客户工程师CE,这个位臵要和PIE搞好关系,他们的Support是关键。 有虐待别人倾向,喜欢看着他人无助神情的人可以考虑去做QE。QE的弟兄把PIE/PE/EE/TD/PDE之类的放挺简直太容易了。:) 其他的想到再说。 作者:core-logic回复日期:2005-12-2709:31:23 ============================================= Fab中PIE要略微比PE和EE好一些,相对进fab的机会要少。 PIE主要的工作有很多,但总而言之是和产品密切相关的。SMIC上海厂有DRAM和Logic两种截然不同的产品,相应的PIE职责也有区别。 Memory PIE(基本都在一厂)通常是分段管理,一般是有人负责Isolation(FOX/STI),有人负责Capacitance,有人负责Transistor,有人负责后段Interconnect。总体分工比较明确,少数资深的工程师会负责全段的制程。Memory 的产品通常种类较少,总量较大,比较少有新的产品。SMIC的Memory有堆栈型和沟槽型两大类,都在一厂有量产。 Logic PIE(两个厂都有)才是真正意义上的Fab PIE,一般来讲Fab要赚钱,Logic的产品一定要起来。Logic PIE通常会分不同的Technology来管理产品,比如0.35um LG/MM/HS;0.18um LG/MM/HS/SR;0.13um LG/SR等等。Logic 的产品种类非常多,但每颗的总量一般不会太大,如果能够有1000pcs/月的量,那已经是比较大的客户了。——如果遇到这样的新客户,大家可以去买他的股票,一定可以赚钱。 Logic PIE的主要工作通常有Maintain和NTO两大类,前者针对量产的大量产品的良率提高,缺陷分析等。后者主要是新产品的开发和量产。具体的工作么,拿NTO来讲,有Setup process flow, pirun, fab out report, defect reduction, yield analysis, customer meeting, ... ...等等。 相比较而言,进fab倒不是最主要的,分析数据和写报告的工作为主。 偷个懒,把原来写的一部分搬过来。 作者:core-logic回复日期:2005-12-2710:25:51 ============================================= 半导体集成电路制造工艺 一、集成电路的定义:集成电路是指半导体集成电路,即以半导体晶片材料为主,经热氧化工艺:干氧氧化、水汽氧化、湿氧氧化加工制造,将无源元件、有源元件和互连线集成在基片内部、表面或基片之上,执行十八、根据器件要求确定氧化方法:1、高质量氧化:干氧氧化或分压氧化;2、厚某种电子功能的微型化电路。微型化电路有集成电路、厚膜电路、薄膜电路和混合层的局部氧化或场氧化:干氧(10min)+湿氧+干氧(10min)或高压氧化;3、低表面态电路等多种形式。氧化:掺氯氧化;湿氧氧化加掺氯气氛退火或分压氧化(H2O或O2+N2 或Ar 或He 等)。二、集成电路的分类:十九、热氧化过程中硅中杂质的再分布1、硅中掺磷(1)温度一定时,水汽氧化(湿氧按电路功能分类:分为以门电路为基础的数字逻辑电路和以放大器为基础的线性电氧化)导致杂质再分布程度较大,其NS/NB 大于干氧氧化;(2)同一氧化气氛下,氧化路,还有微波集成电路和光集成电路等。温度越高,磷向硅内扩散的速度越快,表面堆积现象减小,NS/NB 趋于1。2、硅中按构成集成电路基础的晶体管分类:分为双极型集成电路和MOS型集成电路两大类。掺硼(1)温度一定时,水汽氧化(湿氧氧化)导致杂质再分布程度增大,NS/NB 小前者以双极型平面晶体管为主要器件;后者以MOS场效应晶体管为基础。于干氧氧化;(2)同一氧化气氛下,氧化温度越高,硼向硅表面扩散速度加快,补三、衡量集成电路的发展 DRAM( 3*107(集成度), 135mm2(外型尺寸), 0.5 μm偿了表明杂质的损耗,NS/NB 趋于1。看看运动方向(特征尺寸), 200mm (英寸)) ,二十二、热氧化过程四、摩尔定律:IC集成度每1.5 年翻一番五、集成电路的发展展望目标:集成度↑、可靠性↑、 速度↑、功耗↓、成本↓。努力方向:线宽↓、晶片直径↑、设计技术↑六、硅微电子技术发展的几个趋势:1、单片 系统集成(SoC)System on a chip Application Specific Integrated Circuit 特定用途集成电路2、整硅片集成(WSI)3、半定制电路的 设计方法4、微电子机械系统(MEMS)5、真空微电子技术七、集成电路制造中的基本工艺技术横向加工:图形的产生与转移(又称为光刻,包括曝光、显影、刻蚀等)。纵向加工:薄膜制备(蒸发、溅射、氧化、CVD 等),掺杂(热扩散、离子注入、中子嬗变等)八、补充简要说明工艺1-1 1、氧化剂扩散穿过滞留层达到SiO2 表面,其流密度为F1 。2、氧化剂扩散穿过SiO2层达到SiO2-Si界面,流密度为F2 。3、氧化剂在Si 表面与Si 反应生成SiO2 ,流密度为F3。4、反应的副产物离开界面。二十三、CVD的薄膜及技术分类化学 气相淀积(Chemical Vapor Deposition)是指单独地或综合的利用热能、辉光放电等离子体、紫外光照射、激光照射或其它形式的能源,使气态物质在固体的热表面上发生化学反应并在该表面上淀积,形成稳定的固态物质的工艺过程二十四、CVD薄膜分类:半导体集成 电路制造中所用的薄膜材料,包括介质膜、半导体膜、导体膜以及 第1章 集成电路的基本制造工艺 1.6 一般TTL 集成电路与集成运算放大器电路在选择外延层电阻率上有何区别?为什么? 答:集成运算放大器电路的外延层电阻率比一般TTL 集成电路的外延层电阻率高。 第2章 集成电路中的晶体管及其寄生效应 复 习 思 考 题 2.2 利用截锥体电阻公式,计算TTL “与非”门输出管的CS r 2.2 所示。 提示:先求截锥体的高度 up BL epi mc jc epi T x x T T -----= 然后利用公式: b a a b WL T r c -? = /ln 1ρ , 2 1 2?? =--BL C E BL S C W L R r b a a b WL T r c -? = /ln 3ρ 321C C C CS r r r r ++= 注意:在计算W 、L 时, 应考虑横向扩散。 2.3 伴随一个横向PNP 器件产生两个寄生的PNP 晶体管,试问当横向PNP 器件在4种可能 的偏置情况下,哪一种偏置会使得寄生晶体管的影响最大? 答:当横向PNP 管处于饱和状态时,会使得寄生晶体管的影响最大。 2.8 试设计一个单基极、单发射极和单集电极的输出晶体管,要求其在20mA 的电流负载下 ,OL V ≤0.4V ,请在坐标纸上放大500倍画出其版图。给出设计条件如下: 答: 解题思路 ⑴由0I 、α求有效发射区周长Eeff L ; ⑵由设计条件画图 ①先画发射区引线孔; ②由孔四边各距A D 画出发射区扩散孔; ③由A D 先画出基区扩散孔的三边; ④由B E D -画出基区引线孔; ⑤由A D 画出基区扩散孔的另一边; ⑥由A D 先画出外延岛的三边; ⑦由C B D -画出集电极接触孔; ⑧由A D 画出外延岛的另一边; ⑨由I d 画出隔离槽的四周; ⑩验证所画晶体管的CS r 是否满足V V OL 4.0≤的条件,若不满足,则要对所作 的图进行修正,直至满足V V OL 4.0≤的条件。(CS C OL r I V V 00 ES += 及己知 V V C 05.00ES =) 第3章 集成电路中的无源元件 复 习 思 考 题 3.3 设计一个4k Ω的基区扩散电阻及其版图。 试求: (1) 可取的电阻最小线宽min R W =?你取多少? 答:12μm (2) 粗估一下电阻长度,根据隔离框面积该电阻至少要几个弯头? 答:一个弯头 第4章 晶体管 (TTL)电路 复 习 思 考 题 4.4 某个TTL 与非门的输出低电平测试结果为 OL V =1V 。试问这个器件合格吗?上 机使用时有什么问题? 答:不合格。 4.5 试分析图题4.5所示STTL 电路在导通态和截止态时各节点的电压和电流,假定各管的 β=20, BEF V 和一般NPN 管相同, BCF V =0.55V , CES V =0.4~0.5V , 1 CES V =0.1~0.2V 。 答:(1)导通态(输出为低电平) V V B 1.21= , V V B 55.12= ,V V B 2.13= ,V V B 5.04= ,V V B 8.05= , 第一部分考试试题 第0章绪论 1.什么叫半导体集成电路? 2.按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写? 3.按照器件类型分,半导体集成电路分为哪几类? 4.按电路功能或信号类型分,半导体集成电路分为哪几类? 5.什么是特征尺寸?它对集成电路工艺有何影响? 6.名词解释:集成度、wafer size、die size、摩尔定律? 第1章集成电路的基本制造工艺 1.四层三结的结构的双极型晶体管中隐埋层的作用? 2.在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响?。 3.简单叙述一下pn结隔离的NPN晶体管的光刻步骤? 4.简述硅栅p阱CMOS的光刻步骤? 5.以p阱CMOS工艺为基础的BiCMOS的有哪些不足? 6.以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法。 7. 请画出NPN晶体管的版图,并且标注各层掺杂区域类型。 8.请画出CMOS反相器的版图,并标注各层掺杂类型和输入输出端子。 第2章集成电路中的晶体管及其寄生效应 1.简述集成双极晶体管的有源寄生效应在其各工作区能否忽略?。 2.什么是集成双极晶体管的无源寄生效应? 3. 什么是MOS晶体管的有源寄生效应? 4. 什么是MOS晶体管的闩锁效应,其对晶体管有什么影响? 5. 消除“Latch-up”效应的方法? 6.如何解决MOS器件的场区寄生MOSFET效应? 7. 如何解决MOS器件中的寄生双极晶体管效应? 第3章集成电路中的无源元件 1.双极性集成电路中最常用的电阻器和MOS集成电路中常用的电阻都有哪些? 2.集成电路中常用的电容有哪些。 3. 为什么基区薄层电阻需要修正。 4. 为什么新的工艺中要用铜布线取代铝布线。 5. 运用基区扩散电阻,设计一个方块电阻200欧,阻值为1K的电阻,已知耗散功率为20W/c㎡,该电阻上的压降为5V,设计此电阻。 第4章TTL电路 1.名词解释 企划部岗位职责说明书 编制单位:企划部 编制时间:二零一叁年十月 企划部岗位职责说明书 第一章:总则 第一条本规范旨在通过制定企划部门业务标准和管理标准,规范企划部得策划行为,以发挥企划部门在企业创新体制中的核心作用。 第二条本规范旨在全面提高企划部的策划业务水平和部门管理水平,进而提高企业整体的策划与创新能力,建立与保持市场竞争优势,实现企业可持续性发展。 第二章:企划部职能定位 第三条企划部的职能 公司发展的战略规划及实施;策划展会、活动、宣传等项目的组织、实施;主持企业文化策划,组织企业文化建设;企划文案的指导、审核与方向性文案的撰写工作;主持营销战略策划、产品战略策划、市场推广策划、品牌战略策划、广告策划;策划、督导内部VI的设计和导入;制订网站建设方案及推广计划,并实施。 主要职能: (一)制订品牌形象、广告审核、投放计划及相关新闻稿件的发布; (二)根据整体的经营目标安排市场推广; (三)制定公司的发展战略规划、项目核心策略,并指导实施; (四)策划公司展会、活动、宣传等项目的组织、实施、监督、控制、协调、分析、修正、评估、报告等执行细则,及与合作方的沟通; (五)主持企业文化策划,组织企业文化建设; (六)负责企划文案的指导、审核; (七)主持营销战略策划、产品战略策划、市场推广策划、品牌战略策划、广告策划; (八)策划、督导公司识别系统VI的设计、导入与统一实施,并对结果进行检查和管理; (九)搜集、建立与执行相关市场信息和资源渠道,了解同行的策划动态,并进行汇总、分析; (十)参与制订网站建设方案及推广计划,并实施; (十一)方向性文案、新闻稿、软文及对外宣传文案撰写工作; (十二)配合广告公司进行各类广告、宣传资料的创意、设计、排版。 (十三)依据公司识别系统VI设计公司内各种宣传牌、指示牌、员工胸牌等。 第三章:岗位职责 第四条企划部根据工作内容将职责岗位进行明确。设定企划部经理、推广活动管理、平面设计与文案管理三个岗位。 第五条企划部经理岗位职责 职位名称企划部经理所属部门企划部 岗位等级部门经理直属上级总经理直属下级 推广活动管理 平面设计与文案管理 生产部直接上级总经理部门编号1上级部门下属分部门 内外协调负责公司内外部的工作配合和协调工作 1生产制度流程的初步制定权职员工培训 对生产职员工进行行为规范、生产安全、操作技能等方面的培训与指导,改善工作态度,提升工作能力内部管理 负责部门内部合理分工;对部门员工进行培训、指导,提升部门团队能力;落实公司制度,提高部门服务质量生产质量管理 确保生产质量,对发生的质量问题,参与公司质量问题分析,监督落实解决方案安全生产管理 严格执行安全生产规章制度,定期检查本部门安全教育执行情况;及时、妥善处理安全隐患整改及安全事故统计管理 统计、收集生产计划完成情况,并做出生产分析计划管理 根据订单情况制定生产作业计划并具体实施日常生产管理 制定、修订与生产管理相关管理流程、操作标准等文件;组织生产安全;把握生产进度,实施动态管理生产调度管理 各项生产进度控制;生产调度情况的统计、汇总生产部 部门职能说明书 部门名称 部门编制 职能概述负责生产过程管理、质量管理、安全管理、生产现场管理,按时完成公司下达的生产计划。 主要工作职责描述 编制数1663电气装配工 根据技术装配图纸、工艺、质量要求进行设备的电气装配工作机械装配工 根据技术装配图纸、工艺、质量要求进行设备的机械装配工作调试工 负责设备出厂功能调试及测试内部:公司各职能部门 外部:供应商、其他合作单位 部门岗位设置及职责描述 岗位名称 职责描述生产主管 生产交期、产品品质、生产成本, 推动生产计划、现场改善、效率提升、安全管理及成本控制部门核心指标 1.部门费用预算达成率;生产费用 2.生产计划完成率;交期达成率;产品质量合格率;劳动生产率;安全生产事故 3.客户满意度、部门协作满意度 4.部门培训计划完成率、员工任职资格达标率 主要业务相关部门 部门权限 1.生产制度、流程的初步制定权 2.生产日常管理工作的建议权,权限范围内的审核权、核对权、决定权 3.根据工作需要,要求其他各部门提供相关信息、资料、需求的权力 4.在部门职责范围内按照制度自主开展各项工作的权利 5.本部门人员的录用、解聘建议权及工作调配权;有权考核部门人员、决定内部奖惩,并提供薪酬分配建议 6.公司规定、上级主管授予的其他权限 总经理审核人力资源制作 半导体集成电路型号命名法 1.集成电路的型号命名法 集成电路现行国际规定的命名法如下:(摘自《电子工程手册系列丛书》A15,《中外集成电路简明速查手册》TTL,CMOS电路以及GB3430)。 器件的型号由五部分组成,各部分符号及意义见表1。 2.集成电路的分类 集成电路是现代电子电路的重要组成部分,它具有体积小、耗电少、工作特性好等一系列优点。 概括来说,集成电路按制造工艺,可分为半导体集成电路、薄膜集成电路和由二者组合而成的混合集成电路。 按功能,可分为模拟集成电路和数字集成电路。 按集成度,可分为小规模集成电路(SSI,集成度<10个门电路〉、中规模集成电路(MSI,集成度为10~100个门电路)、大规模集成电路(LSI,集成度为100~1000个门电路)以及超大规模集成电路(VLSI,集成度>1000个门电路)。 按外形,又可分为圆型(金属外壳晶体管封装型,适用于大功率),扁平型(稳定性好、体积小)和双列直插型(有利于采用大规模生产技术进行焊接,因此获得广泛的应用)。 目前,已经成熟的集成逻辑技术主要有三种:TTL逻辑(晶体管-晶体管逻辑)、CMOS 逻辑(互补金属-氧化物-半导体逻辑)和ECL逻辑(发射极耦合逻辑)。 TTL逻辑:TTL逻辑于1964年由美国德克萨斯仪器公司生产,其发展速度快,系列产品多。有速度及功耗折中的标准型;有改进型、高速及低功耗的低功耗肖特基型。所有TTL 电路的输出、输入电平均是兼容的。该系列有两个常用的系列化产品, CMOS逻辑:CMOS逻辑器件的特点是功耗低,工作电源电压范围较宽,速度快(可达7MHz)。 ECL逻辑:ECL逻辑的最大特点是工作速度高。因为在ECL电路中数字逻辑电路形式采用非饱和型,消除了三极管的存储时间,大大加快了工作速度。MECL I系列产品是由美国摩托罗拉公司于1962年生产的,后来又生产了改进型的MECLⅡ,MECLⅢ型及MECL10000。 3.集成电路外引线的识别 使用集成电路前,必须认真查对和识别集成电路的引脚,确认电源、地、输入、输出及控制等相应的引脚号,以免因错接而损坏器件。引脚排列的一般规律为: 圆型集成电路:识别时,面向引脚正视。从定位销顺时针方向依次为1,2,3,4 ……。图1 集成器件俯视图 – 158 – Question Answer & PIE PIE 1. 何谓PIE? PIE的主要工作是什幺? 答:Process Integration Engineer(工艺整合工程师), 主要工作是整合各部门的资源, 对工艺持续进行改善, 确保产品的良率(yield)稳定良好。 2. 200mm,300mm Wafer 代表何意义? 答:8吋硅片(wafer)直径为200mm , 直径为300mm硅片即12吋. 3. 目前中芯国际现有的三个工厂采用多少mm的硅片(wafer)工艺?未来北京的Fab4(四厂)采用多少mm的wafer工艺? 答:当前1~3厂为200mm(8英寸)的wafer, 工艺水平已达0.13um工艺。未来北京厂工艺wafer将使用300mm(12英寸)。 4. 我们为何需要300mm? 答:wafer size 变大,单一wafer 上的芯片数(chip)变多,单位成本降低200→300 面积增加2.25倍,芯片数目约增加2.5倍 5. 所谓的0.13 um 的工艺能力(technology)代表的是什幺意义? 答:是指工厂的工艺能力可以达到0.13 um的栅极线宽。当栅极的线宽做的越小时,整个器件就可以变的越小,工作速度也越快。 6. 从0.35um->0.25um->0.18um->0.15um->0.13um 的technology改变又代表的是什幺意义? 答:栅极线的宽(该尺寸的大小代表半导体工艺水平的高低)做的越小时,工艺的难度便相对提高。从0.35um -> 0.25um -> 0.18um -> 0.15um -> 0.13um 代表着每一个阶段工艺能力的提升。 7. 一般的硅片(wafer)基材(substrate)可区分为N,P两种类型(type),何谓N, P-type wafer? 答:N-type wafer 是指掺杂negative元素(5价电荷元素,例如:P、As)的硅片, P-type 的wafer 是指掺杂positive 元素(3价电荷元素, 例如:B、In)的硅片。 200mm300mm 8〞12〞 集成电路的种类与用途 作者:陈建新 在电子行业,集成电路的应用非常广泛,每年都有许许多多通用或专用的集成电路被研发与生产出来,本文将对集成电路的知识作一全面的阐述。 一、集成电路的种类 集成电路的种类很多,按其功能不同可分为模拟集成电路和数字集成电路两大类。前者用来产生、放大和处理各种模拟电信号;后者则用来产生、放大和处理各种数字电信号。所谓模拟信号,是指幅度随时间连续变化的信号。例如,人对着话筒讲话,话筒输出的音频电信号就是模拟信号,收音机、收录机、音响设备及电视机中接收、放大的音频信号、电视信号,也是模拟信号。所谓数字信号,是指在时间上和幅度上离散取值的信号,例如,电报电码信号,按一下电键,产生一个电信号,而产生的电信号是不连续的。这种不连续的电信号,一般叫做电脉冲或脉冲信号,计算机中运行的信号是脉冲信号,但这些脉冲信号均代表着确切的数字,因而又叫做数字信号。在电子技术中,通常又把模拟信号以外的非连续变化的信号,统称为数字信号。目前,在家电维修中或一般性电子制作中,所遇到的主要是模拟信号;那么,接触最多的将是模拟集成电路。 集成电路按其制作工艺不同,可分为半导体集成电路、膜集成电路和混合集成电路三类。半导体集成电路是采用半导体工艺技术,在硅基片上制作包括电阻、电容、三极管、二极管等元器件并具有某种电路功能的集成电路;膜集成电路是在玻璃或陶瓷片等绝缘物体上,以“膜”的形式制作电阻、电容等无源器件。无源元件的数值范围可以作得很宽,精度可以作得很高。但目前的技术水平尚无法用“膜”的形式制作晶体二极管、三极管等有源器件,因而使膜集成电路的应用范围受到很大的限制。在实际应用中,多半是在无源膜电路上外加半导体集成电路或分立元件的二极管、三极管等有源器件,使之构成一个整体,这便是混合集成电路。根据膜的厚薄不同,膜集成电路又分为厚膜集成电路(膜厚为1μm~10μm)和薄膜集成电路(膜厚为1μm以下)两种。在家电维修和一般性电子制作过程中遇到的主要是半导体集成电路、厚膜电路及少量的混合集成电路。 按集成度高低不同,可分为小规模、中规模、大规模及超大规模集成电路四类。对模拟集成电路,由于工艺要求较高、电路又较复杂,所以一般认为集成50个以下元器件为小规模集成电路,集成50-100个元器件为中规模集成电路, 芯片制造-半导体工艺教程 Microchip Fabrication ----A Practical Guide to Semicondutor Processing 目录: 第一章:半导体工业[1][2][3] 第二章:半导体材料和工艺化学品[1][2][3][4][5]第三章:晶圆制备[1][2][3] 第四章:芯片制造概述[1][2][3] 第五章:污染控制[1][2][3][4][5][6] 第六章:工艺良品率[1][2] 第七章:氧化 第八章:基本光刻工艺流程-从表面准备到曝光 第九章:基本光刻工艺流程-从曝光到最终检验 第十章:高级光刻工艺 第十一章:掺杂 第十二章:淀积 第十三章:金属淀积 第十四章:工艺和器件评估 第十五章:晶圆加工中的商务因素 第十六章:半导体器件和集成电路的形成 第十七章:集成电路的类型 第十八章:封装 附录:术语表 #1 第一章半导体工业--1 芯片制造-半导体工艺教程点击查看章节目录 by r53858 概述 本章通过历史简介,在世界经济中的重要性以及纵览重大技术的发展和其成为世界领导工业的发展趋势来介绍半导体工业。并将按照产品类型介绍主要生产阶段和解释晶体管结构与集成度水平。 目的 完成本章后您将能够: 1. 描述分立器件和集成电路的区别。 2. 说明术语“固态,” “平面工艺”,““N””型和“P”型半导体材料。 3. 列举出四个主要半导体工艺步骤。 4. 解释集成度和不同集成水平电路的工艺的含义。 5. 列举出半导体制造的主要工艺和器件发展趋势。 一个工业的诞生 电信号处理工业始于由Lee Deforest 在1906年发现的真空三极管。1真空三极管使得收音机, 电视和其它消费电子产品成为可能。它也是世界上第一台电子计算机的大脑,这台被称为电子数字集成器和计算器(ENIAC)的计算机于1947年在宾西法尼亚的摩尔工程学院进行首次演示。 这台电子计算机和现代的计算机大相径庭。它占据约1500平方英尺,重30吨,工作时产生大量的热,并需要一个小型发电站来供电,花费了1940年时的400, 000美元。ENIAC的制造用了19000个真空管和数千个电阻及电容器。 真空管有三个元件,由一个栅极和两个被其栅极分开的电极在玻璃密封的空间中构成(图1.2)。密封空间内部为真空,以防止元件烧毁并易于电子的====移动。 真空管有两个重要的电子功能,开关和放大。开关是指电子器件可接通和切断电流;放大则较为复杂,它是指电子器件可把接收到的信号放大,并保持信号原有特征的功能。 真空管有一系列的缺点。体积大,连接处易于变松导致真空泄漏、易碎、要求相对较多的电能来运行,并且元件老化很快。ENIAC 和其它基于真空管的计算机的主要缺点是由于真空管的烧毁而导致运行时间有限。 这些问题成为许多实验室寻找真空管替代品的动力,这个努力在1947年12月23曰得以实现。贝尔实验室的三位科学家演示了由半导体材料锗制成的电子放大器。 集成电路的种类和用途 在电子行业,集成电路的应用非常广泛,每年都有许许多多通用或专用的集成电路被研发与生产出来,本文将对集成电路的知识作一全面的阐述。 集成电路的种类 集成电路的种类很多,按其功能不同可分为模拟集成电路和数字集成电路两大类。前者用来产生、放大和处理各种模拟电信号;后者则用来产生、放大和处理各种数字电信号。所谓模拟信号,是指幅度随时间连续变化的信号。例如,人对着话筒讲话,话筒输出的音频电信号就是模拟信号,收音机、收录机、音响设备及电视机中接收、放大的音频信号、电视信号,也是模拟信号。所谓数字信号,是指在时间上和幅度上离散取值的信号,例如,电报电码信号,按一下电键,产生一个电信号,而产生的电信号是不连续的。这种不连续的电信号,一般叫做电脉冲或脉冲信号,计算机中运行的信号是脉冲信号,但这些脉冲信号均代表着确切的数字,因而又叫做数字信号。在电子技术中,通常又把模拟信号以外的非连续变化的信号,统称为数字信号。目前,在家电维修中或一般性电子制作中,所遇到的主要是模拟信号;那么,接触最多的将是模拟集成电路。 集成电路按其制作工艺不同,可分为半导体集成电路、膜集成电路和混合集成电路三类。半导体集成电路是采用半导体工艺技术,在硅基片上制作包括电阻、电容、三极管、二极管等元器件并具有某种电路功能的集成电路;膜集成电路是在玻璃或陶瓷片等绝缘物体上,以“膜”的形式制作电阻、电容等无源器件。无源元件的数值范围可以作得很宽,精度可以作得很高。但目前的技术水平尚无法用“膜”的形式制作晶体二极管、三极管等有源器件,因而使膜集成电路的应用范围受到很大的限制。在实际应用中,多半是在无源膜电路上外加半导体集成电路或分立元件的二极管、三极管等有源器件,使之构成一个整体,这便是混合集成电路。根据膜的厚薄不同,膜集成电路又分为厚膜集成电路(膜厚为1μm~10μm)和薄膜集成电路(膜厚为1μm以下)两种。在家电维修和一般性电子制作过程中遇到的主要是半导体集成电路、厚膜电路及少量的混合集成电路。 按集成度高低不同,可分为小规模、中规模、大规模及超大规模集成电路四类。对模拟集成电路,由于工艺要求较高、电路又较复杂,所以一般认为集成50个以下元器件为小规模集成电路,集成50-100个元器件为中规模集成电路,集成100个以上的元器件为大规模集成电路;对数字集成电路,一般认为集成1~10等效门/片或10~100个元件/片为小规模集成电路,集成10~100个等效门/片或100~1000元件/片为中规模集成电路,集成100~10,000个等效门/片或1000~100,000个元件/片为大规模集成电路,集成10,000以上个等效门/片或100,000以上个元件/片为超大规模集成电路。 按导电类型不同,分为双极型集成电路和单极型集成电路两类。前者频率特性好,但功耗较大,而且制作工艺复杂,绝大多数模拟集成电路以及数字集成电路中的TTL、ECL、HTL、LSTTL、STTL型属于这一类。后者工作速度低,但输人阻抗高、功耗小、制作工艺简单、易于大规模集成,其主要产品为MOS型集成电路。MOS电路又分为NMOS、PMOS、CMOS型。 NMOS集成电路是在半导体硅片上,以N型沟道MOS器件构成的集成电路;参加导电的是电子。PMOS型是在半导体硅片上,以P型沟道MOS器件构成的集成电路;参加导电的是空穴。CMOS型是由NMOS晶体管和PMOS晶体管互补构成的集成电路称为互补型MOS集成电路,简写成CMOS集成电路。 除上面介绍的各类集成电路之外,现在又有许多专门用途的集成电路,称为专用集成电路。 岗位职责说明书范例 一、基本信息 职位名称部长标准编号 所属部门企划部职等职级七级 直接上级职位总裁办主任直接下属职位部门内成员 晋升方向总裁办主任/行政总监轮转岗位人力资源部部长/行政 部部长 二、岗位概要 负责编制集团战略规划和经营计划,工作计划审核、跟踪和总结分析,并负责制度建设、体系建设和企业文化建设的推动。 三、职权描述&KPI 职责权限 1.根据三鼎控股集团的战略发展规划,做好集团的战略衔接与配合工 作。 2. 协助集团拟定中长期发展战略规划,并跟踪战略规调 整和具体规划的落实。 3. 负责拟定集团的年度战略规划和年度经营计划书,并组织各单位进 行年度目标分解。 4. 负责集团制度建设工作的推进及业务流程的优化,促进集团的管理 正规化与制度化。 5. 收集行业信息和国内外同行业先进企业资料,总结先进经营理念、 管理体制、管理方法,提高内部管理水平,为集团提高核心竞争力和管理、技术创新提供建设性意见。 6. 负责制定集团ISO系列体系的审核和改进方案,推动管理体系持续 有效运行。 7. 负责集团经营规划会议、经营分析会议的组织与召开。 8. 负责集团重大项目的前期调研,策划、立项、可行性论证、项目评 估,协助项目谈判与实施,跟踪投资项目进展。 9. 负责集团企业文化项目的策划并组织实施。1.对战略规划和年 度经营计划的 制定有参与和 审议权。 2.对集团管理工作 的提升有建议 权。 3.对集团战略目标 的分解有建议 权。 4. 对制度的建设 和流程优化有 审核权。 5. 对集团企业文 化项目策划有 建议权。 10. 完成上级交办的其他工作任务。 KPI指标 1、计划总结汇总及时、有效性; 2、工作计划达成率。 四、工作条件描述 工作时间特征描述正常工作时间,偶尔需要加班 工作环境描述85%以上在集团总部办公室内,温度适中危险性描述危险系数低,无个人生命或严重受伤危险使用工具设备电脑、网络设备、电话、打印机、办公车辆五、工作沟通 类别沟通对象沟通 频率 沟通能力沟通内容 组织内部沟通 总裁办主任经常重要工作汇报各子公司/职能部 门 频繁重要工作交流 组织外部沟通 各协作单位经常普通公共关系联络其他公司外人员偶尔普通有关公司发展事项 六、任职资格 项目必备条件 教育培训 背景 学历专业本科 其他管理类专业,接受过企业管理的系统培训。培训经历企业战略管理、目标管理等培训。 工作经验 要求工作经验 5年以上工作经验,3年以上企业战略规划管理经验,2年以上大型 集团部门管理经验。 能力要求 具备极强的全局观和综合协调能力,卓越的计划管理和控制能力、 文字处理能力,有较强的洞察力及推动、解决问题的能力。 基本技能 要求 内容掌握企业经营管理知识、法律知识,熟练操作日常办公软件。个人特质内容责任心强、敬业、自律、系统思维良好、正直、具有成就动机。 Question & PIE Answer PIE 1. 何谓PIE? PIE 的主要工作是什幺? 答:Process Integration Engineer(工艺整合工程师), 主要工作是整合各部门的资源, 对工艺持续进行改善, 确保产品的良率(yield)稳定良好。 2. 200mm,300mm Wafer 代表何意义? 答:8吋硅片(wafer)直径为200mm , 直径为300mm硅片即12吋. 目前中芯国际现有的三个工厂采用多少mm的硅片(wafer)工艺?未来北京3.的Fab4(四厂)采用多少mm的wafer 工艺? 答:当前1~3 厂为200mm(8 英寸)的wafer, 工艺水平已达0.13um 工艺。 未来北京厂工艺wafer 将使用300mm(12 英寸)。 4. 我们为何需要300mm? 答:wafer size 变大,单一wafer 上的芯片数(chip)变多,单位成本降低200→300 面积增加2.25倍,芯片数目约增加2.5 倍 5. 所谓的0.13 um 的工艺能力(technology)代表的是什幺意义?答:是指工厂的工艺能力可以达到0.13 um 的栅极线宽。当栅极的线宽做的越小时,整个器件就可以变的越小,工作速度也越快。 从0.35um->0.25um->0.18um->0.15um->0.13um 的technology改变又代表的是什幺意义? 答:栅极线的宽(该尺寸的大小代表半导体工艺水平的高低)做的越小时,工艺的难度便相对提高。从0.35um -> 0.25um -> 0.18um -> 0.15um -> 0.13um 代表着每一个阶段工艺能力的提升。 一般的硅片(wafer)基材(substrate)可区分为N,P 两种类型(type),何谓N, P-type wafer? 答:N-type wafer 是指掺杂negative 元素(5 价电荷元素,例如:P、As)的硅片, P-type 的wafer 是指掺杂positive 元素(3 价电荷元素, 例如:B、 In)的硅片。 8. 工厂中硅片(wafer)的制造过程可分哪几个工艺过程(module)?答:主要有四个部分:DIFF (扩散)、TF(薄膜)、PHOTO (光刻)、ETCH (刻蚀)。其中 第一次作业: 1,集成时代以什么来划分?列出每个时代的时间段及大致的集成规模。答: 类别时间 数字集成电路 模拟集成电路MOS IC 双极IC SSI 1960s前期 MSI 1960s~1970s 100~500 30~100 LSI 1970s 500~2000 100~300 VLSI 1970s后期~1980s后期>2000 >300 ULSI 1980s后期~1990s后期 GSI 1990s后期~20世纪初 SoC 20世纪以后 2,什么是芯片的集成度?它最主要受什么因素的影响? 答:集成度:单个芯片上集成的元件(管子)数。受芯片的关键尺寸的影响。 3,说明硅片与芯片的主要区别。 答:硅片是指由单晶生长,滚圆,切片及抛光等工序制成的硅圆薄片,是制造芯片的原料,用来提供加工芯片的基础材料;芯片是指在衬底上经多个工艺步骤加工出来的,最终具有永久可是图形并具有一定功能的单个集成电路硅片。 4,列出集成电路制造的五个主要步骤,并简要描述每一个步骤的主要功能。 答:晶圆(硅片)制备(Wafer Preparation); 硅(芯)片制造(Wafer Fabrication):在硅片上生产出永久刻蚀在硅片上的一整套集成电路。硅片测试/拣选(Die T est/Sort):单个芯片的探测和电学测试,选择出可用的芯片。 装配与封装(Assembly and Packaging):提供信号及电源线进出硅芯片的界面;为芯片提供机械支持,并可散去由电路产生的热能;保护芯片免受如潮湿等外界环境条件的影响。 成品测试与分析(或终测)(Final T est):对封装后的芯片进行测试,以确定是否满足电学和特性参数要求。 5,说明封装的主要作用。对封装的主要要求是什么。 答:封装的作用:提供信号及电源线进出硅芯片的界面;为芯片提供机械支持,并可散去由电路产生的热能;保护芯片免受如潮湿等外界环境条件的影响。 主要要求:电气要求:引线应当具有低的电阻、电容和电感。机械特性和热特性:散热率应当越高越好;机械特性是指机械可靠性和长期可靠性。低成本:成本是必须要考虑的比较重要的因素之一。 6,什么是芯片的关键尺寸?这种尺寸为何重要?自半导体制造业开始以来,芯片的关键尺寸是如何变化的?他对芯片上其他特征尺寸的影响是什么? 答:芯片上器件的物理尺寸被称为特征尺寸;芯片上的最小的特征尺寸被称为关键尺寸,且被作为定义制造工艺水平的标准。 为何重要:他代表了工艺上能加工的最小尺寸,决定了芯片上的其他特征尺寸,从而决定了芯片的面积和芯片的集成度,并对芯片的性能有决定性的影响,故被定义为制造工艺水平的标准。 数字集成电路的分类 数字集成电路有多种分类方法,以下是几种常用的分类方法。 1.按结构工艺分 按结构工艺分类,数字集成电路可以分为厚膜集成电路、薄膜集成电路、混合集成电路、半导体集成电路四大类。图如下所示。 世界上生产最多、使用最多的为半导体集成电路。半导体数字集成电路(以下简称数字集成电路)主要分为TTL、CMOS、ECL三大类。 ECL、TTL为双极型集成电路,构成的基本元器件为双极型半导体器件,其主要特点是速度快、负载能力强,但功耗较大、集成度较低。双极型集成电路主要有TTL(Transistor-Transistor Logic)电路、ECL(Emitter Coupled Logic)电路和I2L(Integrated Injection Logic)电路等类型。其中TTL电路的性能价格比最佳,故应用最广泛。 ECL,即发射极耦合逻辑电路,也称电流开关型逻辑电路。它是利用运放原理通过晶体管射极耦合实现的门电路。在所有数字电路中,它工作速度最高,其平均延迟时间tpd可小至1ns。这种门电路输出阻抗低,负载能力强。它的主要缺点是抗干扰能力差,电路功耗大。 MOS电路为单极型集成电路,又称为MOS集成电路,它采用金属-氧化物半导体场效应管(Metal Oxide Semi-conductor Field Effect Transistor,缩写为MOSFET)制造,其主要特点是结构简单、制造方便、集成度高、功耗低,但速度较慢。MOS集成电路又分为PMOS(P-channel Metal Oxide Semiconductor,P沟道金属氧化物半导体)、NMOS(N-channel Metal Oxide Semiconductor,N沟道金属氧化物半导体)和CMOS(Complement Metal Oxide Semiconductor,复合互补金属氧化物半导体)等类型。 MOS电路中应用最广泛的为CMOS电路,CMOS数字电路中,应用最广泛的为4000、4500系列,它不但适用于通用逻辑电路的设计,而且综合性能也很好,它与TTL电路一起成为数字集成电路中两大主流产品。CMOS数字集成电路电路主要分为4000(4500系列)系列、54HC/74HC系列、54HCT/74HCT系列等,实际上这三大系列之间的引脚功能、排列顺序是相同的,只是某些参数不同而已。例如,74HC4017与CD4017为功能相同、引脚排列相同的电路,前者的工作速度高,工作电源电压低。4000系列中目前最常用的是B 系列,它采用了硅栅工艺和双缓冲输出结构。 Bi-CMOS是双极型CMOS(Bipolar-CMOS)电路的简称,这种门电路的特点是逻辑部分采用CMOS结构,输出级采用双极型三极管,因此兼有CMOS电路的低功耗和双极型电路输出阻抗低的优点。 (1)TTL类型 这类集成电路是以双极型晶体管(即通常所说的晶体管)为开关元件,输入级采用多发射极晶体管形式,开关放大电路也都是由晶体管构成,所以称为晶体管-晶体管-逻辑,即Transistor-Transistor-Logic,缩写为TTL。TTL电路在速度和功耗方面,都处于现代数字集成电路的中等水平。它的品种丰富、互换性强,一般均以74(民用)或54(军用)为型号前缀。 ①74LS系列(简称LS,LSTTL等)。这是现代TTL类型的主要应用产品系列,也是逻辑集成电路的重要产品之一。其主要特点是功耗低、品种多、价格便宜。 ②74S系列(简称S,STTL等)。这是TTL的高速型,也是目前应用较多的产品之一。 企划部部门职责+职责说明书 一、企划部部门职责 1、负责公司对外形象的建立与宣传,树立企业形象,扩大企业品牌影响力。 2、负责制定公司对外宣传策略、宣传计划和宣传预算工作。 3、负责公司视觉形象和识别系统的整合、策划与规范工作。 4、负责公司对外宣传平台的运营、管理工作。 5、负责公司对外宣传资料的收集、整理和规范工作。 6、负责公司外部媒体、协会的探索、开发、对接、维护和宣传工作。 7、负责公司外部活动的组织、策划实施与落地工作。 8、负责行业发展趋势、同行竞品(企业+产品)的资料收集、整理和分析。 9、负责公司荣誉申报工作。 10、负责公司网络舆情监控与公关工作。 二、企划岗位说明书 1、岗位职责与工作任务 岗位职责1:负责公司对外形象的建立与宣传,树立企业形象,扩大企业品牌影响力 工作任务: 1负责根据公司的发展战略,对公司品牌进行精准定位。 2通过一定的宣传手段对公司品牌进行包装,包括但不限于:品牌故事、线上宣传(公众号、官网、搜索引擎等)、线下(活动、荣誉、海报等); 岗位职责2:负责制定公司对外宣传策略、宣传计划和宣传预算工作 工作任务: ①根据公司的发展战略规划,制定公司年度宣传策略。 ②匹配公司的宣传策略,制定年度、季度宣传计划,同时根据计划制定相关的宣传预算。 岗位职责3:负责公司视觉形象和识别系统的整合、策划与规范工作 工作任务: ①根据公司发展战略,制定合适的形象定位,并根据发展需求,梳理视觉形象类目,并协调设计人员进行设计。 ②负责公司视觉形象的宣传、推广、使用和管理标准的制定工作。 岗位职责4:负责公司对外宣传平台的运营、管理工作 工作任务: ①负责公司对外宣传平台的定位、宣传策略的制定; ②负责公司对外宣传平台的搭建、管理工作。 ③负责公司对外平台宣传资料的撰写、拟定、审核工作,平台包括但不限于:微信公众号、官网、微博等。 生产部经理的岗位职责 (一)生产副总经理岗位职责: 1. 组织建立和完善生产指挥系统,编制生产计划,检查生产工作,确保生产任务的完成 2. 根据生产运行计划,掌握生产进度,搞好各车间的协调,组织分配劳动力,平衡调度设备材料 3. 每周一次定期召开生产会,分析生产形势,提出解决问题的办法和措施 4. 根据生产需求,编制物资采购计划,并认真实施,及时联系解决生产缺口物资 5. 抓好设备管理,提出更新改造方案,定期组织维修保养 6. 负责生产中的技术和质量保证工作,发现问题及时组织解决和处理,重大问题直接报总经理 (二)总工程师岗位职责: 1.在总经理的领导下,负责公司的全面技术管理工作 2.贯彻执行国家有关的技术政策、标准及各项管理制度 3. 主持技术会议,研究和处理重大技术质量问题 4.负责制定、引进和推广新技术 5.负责职工技术培训工作,并对所属技术人员进行考核 6.负责组织公司的技术交流、专题研讨会和对外的技术交流活动 7. 负责按质量管理体系中有关程序规定的要求审批公司的技术文件 (三)研发中心职责: 1. 围绕公司总体战略规划及年度经营目标;制订产品计划,制订公司各产品的年度产品开发计划 2. 对公司现有产品与市场部沟通,进行销售跟踪 3. 根据市场反馈情报资料,及时在设计上进行改良,调整不理想因素,使产品适应市场需求,增加竞争力 4. 负责组织产品设计过程中的设计评审,技术验证和技术确认 5. 负责相关技术、工艺文件、标准样品件的制定、审批、归档和保管,建立健全技术档案管理制度 6.负责并设计与开发有关的新理念、新技术、新工艺、新材料等情报资料的收集、整理、归档 (四)生产部职责: 1. 服从生产副总经理的指挥,认真执行其工作指令 2.严格执行公司规章制度,认真履行其工作职责 3.负责抓好安全生产,加强安全生产的控制、实施、严格执行安全法规 4.负责组织生产现场管理工作 5.抓好生产统计分析报告,及时编制年、季、月度生产统计报表 第8章动态逻辑电路 填空题 对于一般的动态逻辑电路,逻辑部分由输出低电平的网组成,输出信号与电源之间插入了栅控制1、 极为时钟信号的 ,逻辑网与地之间插入了栅控制极为时钟信号的。 【答案:NMOS, PMOS, NOMS】 对于一个级联的多米诺逻辑电路,在评估阶段:对PDN网只允许有跳变,对 PUN网只允许有跳变,2、 PDN与PDN相连或PUN与PUN相连时中间应接入。 【答案:】 解答题 从逻辑功能,电路规模,速度3方面分析下面2电路的相同点和不同点。从而说明CMOS动态组合逻辑1、 电路的特点。 【答案:】 图A是CMOS静态逻辑电路。图B是CMOS动态逻辑电路。2电路完成的均是NAND的逻辑功能。图B的逻辑部分电路使用了2个MOS管,图A使用了4个MOS管,由此可以看出动态组合逻辑电路的规模为静态电路的一半。图B的逻辑功能部分全部使用NMOS管,图A即使用NMOS也使用PMOS,由于NMOS的速度高于PMOS,说明动态组合逻辑电路的速度高于静态电路。 2、分析下面的电路,指出它完成的逻辑功能,说明它和一般动态组合逻辑电路的不同,说明其特点。 【答案:】 该电路可以完成OUT=AB的与逻辑。与一般动态组合逻辑电路相比,它增加了一个MOS管M kp,这个MOS 管起到了电荷保持电路的作用,解决了一般动态组合逻辑电路存在的电荷泄漏的问题。 3、分析下列电路的工作原理,画出输出端OUT的波形。 【答案:】 答案: 4、结合下面电路,说明动态组合逻辑电路的工作原理。 【答案:】 动态组合逻辑电路由输出信号与电源之间插入的时钟信号PMOS,NMOS逻辑网和逻辑网与地之间插入的时钟信号NMOS组成。当时钟信号为低电平时,PMOS导通,OUT被拉置高电平。此时电路处于预充电阶段。 当时钟信号为低电平时,PMOS截至,电路与V DD的直接通路被切断。这时NOMS导通,当逻辑网处于特定逻辑时,电路输出OUT被接到地,输出低电平。否则,输出OUT仍保持原状态高电平不变。例如此电路, NMOS网构成逻辑网中A与C,或B与C同时导通时,可以构成输出OUT到地的通路,将输出置为低电平。 第7章传输门逻辑 填空题 写出传输门电路主要的三种类型和他们的缺点:(1),缺点:;(2),缺点:;(3),缺1、 点:。 【答案:NMOS传输门,不能正确传输高电平,PMOS传输门,不能正确传输低电平,CMOS传输门, 电路规模较大。】 2、传输门逻辑电路的振幅会由于减小,信号的也较复杂,在多段接续时,一般要插入。 【答案:阈值损失,传输延迟,反相器。】 3、一般的说,传输门逻辑电路适合逻辑的电路。比如常用的和。 【答案:异或,加法器,多路选择器】 解答题 1、分析下面传输门电路的逻辑功能,并说明方块标明的MOS管的作用。 【答案:】半导体集成电路制造工艺

半导体集成电路习题及答案

半导体集成电路考试题目与参考答案

企划部岗位职责说明书

生产部 部门职能说明书

半导体集成电路型号命名法

半导体集成电路制造PIE常识

集成电路的种类与用途全解

芯片制造-半导体工艺教程

集成电路的种类和用途

企划部长岗位职责说明书

半导体集成电路制造PIE常识讲解

半导体集成电路工艺复习

数字集成电路的分类

企划部部门职责+职责说明书

生产部经理的岗位职责说明书

半导体集成电路复习题及答案