5

4

3

2

1

MSI

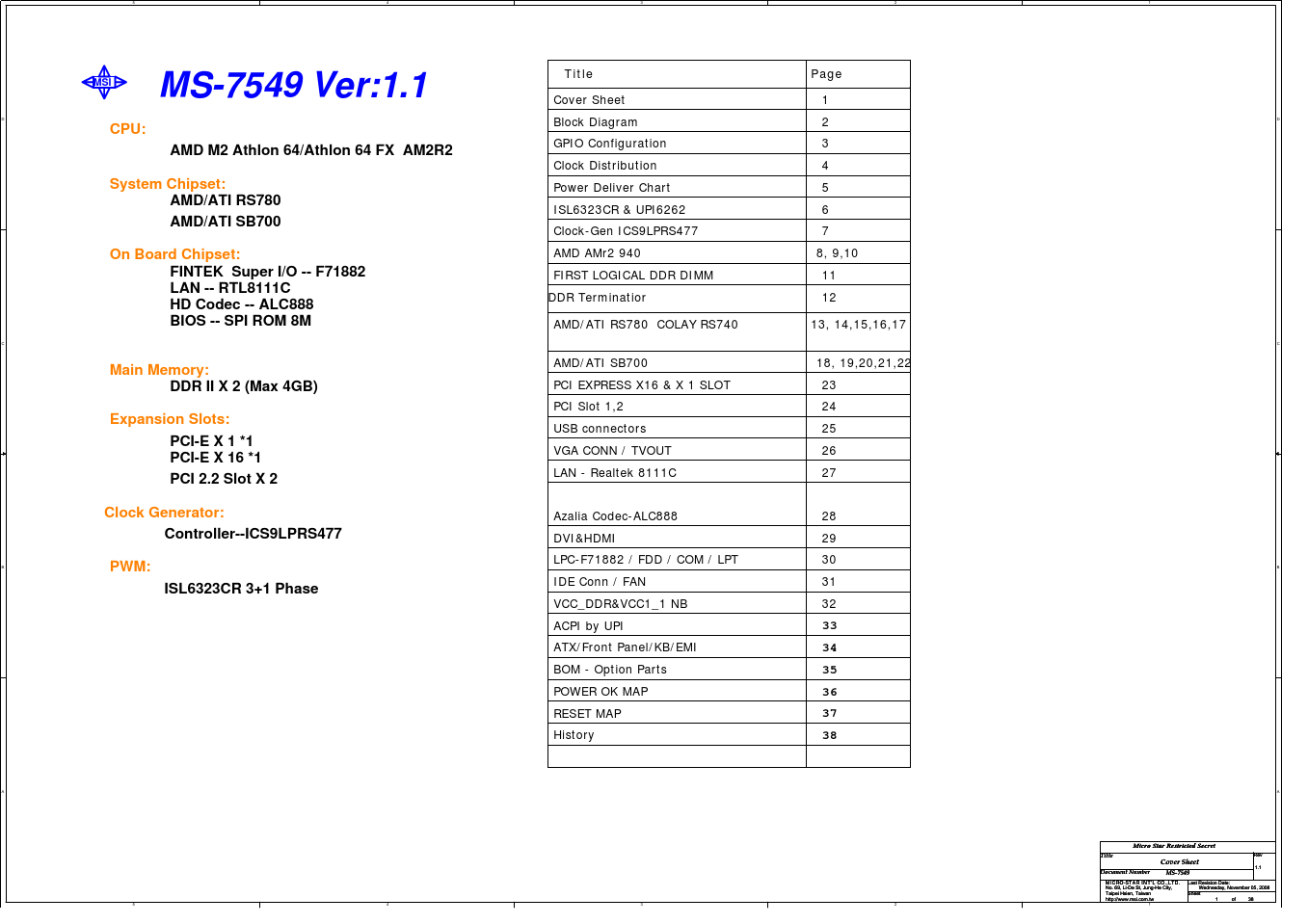

MS-7549 Ver:1.1

AMD M2 Athlon 64/Athlon 64 FX AM2R2

Title Cover Sheet Block Diagram GPIO Configuration Clock Distribution Power Deliver Chart ISL6323CR & UPI6262 Clock-Gen ICS9LPRS477 AMD AMr2 940 FIRST LOGICAL DDR DIMM DDR Terminatior AMD/ATI RS780 COLAY RS740 AMD/ATI SB700 PCI EXPRESS X16 & X 1 SLOT PCI Slot 1,2

Page 1 2 3 4 5 6 7 8, 9,10 11 12 13, 14,15,16,17

C D

D

CPU:

System Chipset: AMD/ATI RS780 AMD/ATI SB700 On Board Chipset: FINTEK Super I/O -- F71882 LAN -- RTL8111C HD Codec -- ALC888 BIOS -- SPI ROM 8M

C

Main Memory: DDR II X 2 (Max 4GB) Expansion Slots: PCI-E X 1 *1 PCI-E X 16 *1 PCI 2.2 Slot X 2 Clock Generator: Controller--ICS9LPRS477

B

18, 19,20,21,22 23 24 25 26 27

USB connectors VGA CONN / TVOUT LAN - Realtek 8111C

Azalia Codec-ALC888 DVI&HDMI LPC-F71882 / FDD / COM / LPT

28 29 30 31 32

B

PWM: ISL6323CR 3+1 Phase

IDE Conn / FAN VCC_DDR&VCC1_1 NB ACPI by UPI ATX/Front Panel/KB/EMI BOM - Option Parts POWER OK MAP RESET MAP History

33 34 35 36 37 38

A

A

Micro Star Restricted Secret

Title Document Number

Rev

Cover Sheet

MS-7549

1.1

MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan https://www.doczj.com/doc/3e247924.html,

5 4 3 2 1

Last Revision Date: Wednesday, November 05, 2008 Sheet of 1 38

5

4

3

2

1

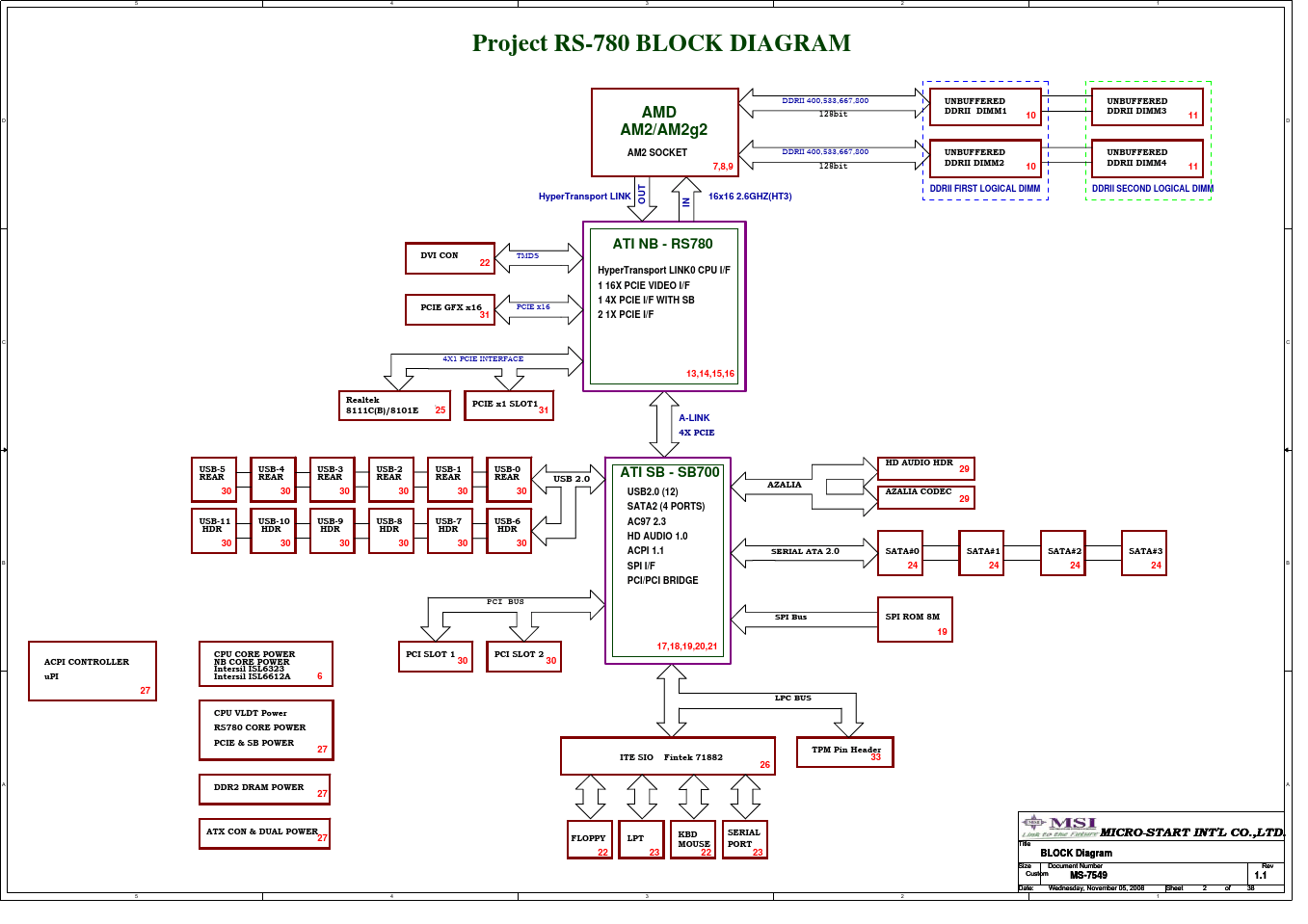

Project RS-780 BLOCK DIAGRAM

DDRII 400,533,667,800

D

AMD AM2/AM2g2

AM2 SOCKET

7,8,9 OUT HyperTransport LINK 16x16 2.6GHZ(HT3)

128bit

UNBUFFERED DDRII DIMM1

10

UNBUFFERED DDRII DIMM3

11

D

DDRII 400,533,667,800 128bit

UNBUFFERED DDRII DIMM2

10

UNBUFFERED DDRII DIMM4

11

DDRII FIRST LOGICAL DIMM

DDRII SECOND LOGICAL DIMM

DVI CON

22

TMDS

ATI NB - RS780

HyperTransport LINK0 CPU I/F 1 16X PCIE VIDEO I/F 1 4X PCIE I/F WITH SB 2 1X PCIE I/F

C

PCIE GFX x16 31

C

PCIE x16

4X1 PCIE INTERFACE

Realtek 8111C(B)/8101E

25

PCIE x1 SLOT1

31

A-LINK 4X PCIE HD AUDIO HDR AZALIA AZALIA CODEC

USB-5 REAR 30 USB-11 HDR 30

B

USB-4 REAR 30 USB-10 HDR 30

USB-3 REAR 30 USB-9 HDR 30

USB-2 REAR 30 USB-8 HDR 30

USB-1 REAR 30 USB-7 HDR 30

USB-0 REAR 30 USB-6 HDR 30

IN

13,14,15,16

USB 2.0

ATI SB - SB700

USB2.0 (12) SATA2 (4 PORTS) AC97 2.3 HD AUDIO 1.0 ACPI 1.1 SPI I/F PCI/PCI BRIDGE

29 29

SERIAL ATA 2.0

SATA#0 24

SATA#1 24

SATA#2 24

SATA#3 24

B

PCI BUS

SPI Bus

SPI ROM 8M 19

ACPI CONTROLLER uPI 27

CPU CORE POWER NB CORE POWER Intersil ISL6323 Intersil ISL6612A

PCI SLOT 1 6

30

PCI SLOT 2

17,18,19,20,21 30

LPC BUS

CPU VLDT Power RS780 CORE POWER PCIE & SB POWER 27 ITE SIO Fintek 71882 TPM Pin Header 33

A

26

A

DDR2 DRAM POWER

27

ATX CON & DUAL POWER 27

FLOPPY 22

LPT 23

KBD MOUSE 22

SERIAL PORT 23

MICRO-START INT'L CO.,LTD.

Title

BLOCK Diagram

Size Document Number Custom MS-7549 Date: Wednesday, November 05, 2008

1

Rev

1.1

Sheet 2 of 38

5

4

3

2

5

4

3

2

1

SB700/750 GPIO Config SB700/750 GPIO Config

GPIO Name PCICLK5/GPIO41 REQ3#/GPIO70 REQ4#/GPIO71 GNT3#/GPIO72 GNT4#/GPIO73 INTE#/GPIO33 INTF#/GPIO33 INTG#/GPIO33

D

SB700/750 GPIO Config

Function description PCI_CLK5 PREQ#3 PREQ#4 Unused Unused PCI_INTA# PCI_INTB# PCI_INTC# PCI_INTD# Unused PREQ#5 RI# Unused A20GATE KBRST# LPC_PME# LPC_SMI3 Unused FP_RST# WAKE# Unused SMBALERT# SB_GPIO10 SB_GPIO6 SB_GPIO4 SB_GPIO0 SB_GPIO39 SB_GPIO40 SPKR SCLK SDATA SCLK1 SDATA1 Unused SPI_WP# LC_SENSE SB_GPIO5 Unused OC6# OC5# OC4# OC3# OC2# OC1# OC0# SDATA_IN_R Unused Unused Unused Pin T3 AE6 AB6 AC6 AE5 AD3 AC4 AE2 AE3 AB8 AD7 E2 H7 Y15 W15 K4 K24 F1 J2 H6 F2 J6 AE18 AD18 AA19 W18 V17 W20 W21 AA18 W18 K1 K2 AA20 Y18 C1 Y19 G5 B9 B8 A8 A9 E5 F8 E4 J7 J8 L8 M3 Page 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 19 21 21 21 21 21 21 21 21 21 21 21 21 21 GPIO Name AZ_DOCK_RST#/GPM8# PS2_DAT/EC_GPIO0 PS2_CLK/EC_GPIO1 SPI_CS2#/EC_GPIO2 IDE_RST#/F_RST#/EC_GPO3 PS2KB_DAT/EC_GPIO4 PS2KB_CLK/EC_GPIO5 PS2M_DAT/EC_GPIO6 PS2M_CLK/EC_GPIO7 USBCLK/14M_25M_48M_OSC KSO_16/EC_GPIO8 KSO_17/EC_GPIO9 EC_PWM0/EC_GPIO10 SCL2/EC_GPIO11 SDA2/EC_GPIO12 SCL3_LV/EC_GPIO13 SDA3_LV/EC_GPIO14 EC_PWM1/EC_GPIO15 EC_PWM2/EC_GPIO16 EC_PWM3/EC_GPIO17 KSI_0/EC_GPIO18 KSI_1/EC_GPIO19 KSI_2/EC_GPIO20 KSI_3/EC_GPIO21 KSI_4/EC_GPIO22 KSI_5/EC_GPIO23 KSI_6/EC_GPIO24 KSI_7/EC_GPIO25 KSO_0/EC_GPIO26 KSO_1/EC_GPIO27 KSO_2/EC_GPIO28 KSO_3/EC_GPIO29 KSO_4/EC_GPIO30 KSO_5/EC_GPIO31 KSO_6/EC_GPIO32 KSO_7/EC_GPIO33 KSO_8/EC_GPIO34 KSO_9/EC_GPIO35 KSO_10/EC_GPIO36 KSO_11/EC_GPIO37 KSO_12/EC_GPIO38 KSO_13/EC_GPIO39 KSO_14/EC_GPIO40 KSO_15/EC_GPIO41 SATA_ACT#/GPIO67 IDE_D0/GPIO15 IDE_D1/GPIO16 IDE_D2/GPIO17 IDE_D3/GPIO18 Type 3.3V Function description Unused Unused Unused Unused Unused Unused Unused Unused Unused USB_48M_CLK Unused Unused Unused Unused Unused Unused Unused Unused SB_GP16 Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused SATA_LED# Unused Unused Unused Unused Pin L5 H19 H20 H21 F25 D22 E24 E25 D23 C8 A18 B18 F21 D21 F19 E20 E21 E19 D19 E18 G20 G21 D25 D24 C25 C24 B25 C23 B24 B23 A23 C22 A22 B22 B21 A21 D20 C20 A20 B20 B19 A19 D18 C18 W11 AD24 AD23 AE22 AC22 Page 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 21 GPIO Name IDE_D4/GPIO19 IDE_D5/GPIO20 IDE_D6/GPIO21 IDE_D7/GPIO22 IDE_D8/GPIO23 IDE_D9/GPIO24 IDE_D10/GPIO25 IDE_D11/GPIO26 IDE_D12/GPIO27 IDE_D13/GPIO28 IDE_D14/GPIO29 IDE_D15/GPIO30 SPI_DI/GPIO12 SPI_DO/GPIO11 SPI_CLK/GPIO47 SPI_HOLD#/GPIO31 SPI_CS#/GPIO32 LAN_RST#/GPIO14 ROM_RST#/GPIO14 FANOUT0/GPIO3 FANOUT1/GPIO48 FANOUT2/GPIO49 FANIN0/GPIO50 FANIN1/GPIO51 FANIN2/GPIO52 TEMPIN0/GPIO61 TEMPIN1/GPIO62 TEMPIN2/GPIO63 TEMPIN3/TALERT#/GPIO64 VIN0/GPIO53 VIN1/GPIO54 VIN2/GPIO55 VIN3/GPIO56 VIN4/GPIO57 VIN5/GPIO58 VIN6/GPIO59 VIN7/GPIO60 Type 3.3V Function description Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused SPI_DATAIN SPI_DATAOUT SPI_CLK SPI_HOLD_L SPI_CS# CPU_PRESENT# Unused Unused COM_GPIO Unused Unused Unused Unused Unused Unused Unused TALERT3 Unused Unused Unused Unused Unused Unused Unused Unused Pin AD21 AE20 AB20 AD19 AE19 AC20 AD20 AE21 AB22 AD22 AE23 AC23 G6 D2 D1 F4 F3 U15 J1 M8 M5 M7 P5 P8 E8 B6 A6 A5 B5 A4 B4 C4 D4 D5 D6 A7 B7

C D

Type 3.3V

Page 20

INTH#/GPIO33 LDRQ1#/GNT5#/GPIO68 BMREQ#/REQ5#/GPIO68 RI#/EXTEVNT0# SLP_S2/GPM9# GA20IN/GEVENT0# KBRST#/GEVENT1# LPC_PME#/GEVENT3# LPC_SMI#/EXTEVNT1# S3_STATE/GEVENT5# SYS_RESET#/GPM7# WAKE#/GEVENT8# BLINK/GPM6# MBALERT#THRMTRIP#/GEVENT2# SATA_ISO#/GPIO10 CLK_REQ3#/SATA_IS1#/GPIO6 SMARTVOLT/SATA_IS2/GPIO4 CLK_REQ0#SATA_IS3#/GPIO0 CLK_REQ1#/SATA_IS4#/GPIO3 CLK_REQ2#/SATA_IS5#/GPIO40 SPKR/GPIO2 SCL0/GPOC0# SDA0/GPOC1# SCL1/GPOC2# SDA1/GPOC3# DDC1_SCL/GPIO9 DDC1_SDA/GPIO8 LLB3/GPIO66 SHUTDOWN#/GPIO5 DDR3_RST#/GEVENT7# SB_OC6#/IR_TX1/GEVENT6# USB_OC5#IR_TX0/GPM5# USB_OC4#IO_RX0/GPM4# USB_OC3#/IR_RX1/GPM3# USB_OC2#/GPM2# USB_OC1#/GPM1# USB_OC0#/GPM0# AZ_SDIN0/GPIO42 AZ_SDIN1/GPIO43 AZ_SDIN2/GPIO44 AZ_SDIN3/GPIO46

C

F71882

GPIO Name

B

GPIO Config

Type 3.3V Function description Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused Unused SPI_DATAIN SPI_DATAOUT SPI_CLK SPI_HOLD_L SPI_CS# CPU_PRESENT# Unused Unused COM_GPIO Unused Unused Unused Unused Unused Unused Pin AD21 AE20 AB20 AD19 AE19 AC20 AD20 AE21 AB22 AD22 AE23 AC23 G6 D2 D1 F4 F3 U15 J1 M8 M5 M7 P5 P8 E8 B6 A6

Title

A

Page 20

VIDO5/GP27 VIDO4/GP26 VIDO1/GP21/VGP0 PME#/GP54 KRST#/GP62 GA20/JP7 KDAT/GP61 KCLK/GP60 MDAT/GP57 MCLK/GP56 SUSC#/GP53 PSON#/GP42 PANSWH#/GP43 PWRON#/GP44 PCIRST3#/GP11 PCIRST2#/GP12 FAN_CTL3/GP36 FAN_TAC3/GP36 FAN_CTL2/GP51 FAN_TAC2/GP52 FAN_CTL1 FAN_TAC1 VID2/GP32

PCI Config.

DEVICE PCI Slot 1 MCP1 INT Pin PCI_INTE# PCI_INTF# PCI_INTG# PCI_INTH# PCI_INTF# PCI_INTG# PCI_INTH# PCI_INTE# REQ#/GNT# PREQ#0 PGNT#0 IDSEL AD18 CLOCK PCICLK0

B

PCI Slot 2

PREQ#1 PGNT#1

AD19

PCICLK1

A

VID3/GP33 VID3/GP33 VID4/GP34 VID5/GP35

MICRO-START INT'L CO.,LTD.

GPIO Configuration

Size Document Number Custom MS-7549 Date: Wednesday, November 05, 2008 Sheet 3 of 38 Rev

1.1

5

4

3

2

1

5

4

3

2

1

DIMM3

D

DIMM4

D

CPU_HT_CLK

DIMM1

DIMM2

NB_HT_CLK 3 PAIR MEM CLK 3 PAIR MEM CLK 3 PAIR MEM CLK

PCI CLK0 33MHZ PCI CLK1

PCI SLOT 0 33MHz

3 PAIR MEM CLK

25M_48M_66M_OSC

33MHZ PCI CLK2 33MHZ PCI CLK3 33MHZ

PCI SLOT 1 33MHz

AMD/ATI SB SB700

HT REFCLK 100MHz DIFF RS780

IEEE1394 33MHz SUPER IO IT8718F 33MHz

AM2/AM2g2 CPU AM2 SOCKET

AMD/ATI NB RS780

NB_DISP_CLK

1 PAIR CPU CLK 200MHZ NB-OSCIN 14.318MHZ NB ALINK PCIE CLK 100MHZ SB ALINK PCIE CLK 100MHZ GPP_CLK3 PCIE_RCLK/ NB_LNK_CLK

PCI CLK4 33MHZ

TPM 33MHz

PCI CLK5 33MHZ

C

LEO CHIP 33MHz

C

EXTERNAL CLK GEN.

NB GFX PCIE CLK 100MHZ NB GPP PCIE CLK 100MHZ (RX780) PCIE GFX CLK 100MHZ PCIE GPP CLK 100MHZ PCIE GPP CLK 100MHZ PCIE GPP CLK 100MHZ

B

LPC_CLK0 33MHZ LPC CLK1 33MHZ SLT_GFX_CLK

PCIE GFX SLOT 1 - 16 LANES

GPP_CLK0

SB_BITCLK 48MHZ

PCIE GPP SLOT 1 - 1 LANE PCIE GPP SLOT 2 - 4 LANES PCIE GBE

25MHZ OSC INPUT

HD AUDIO ALC 662/883

25MHz LAN

GPP_CLK1

25MHz

GPP_CLK2

B

USB CLK 48MHZ

USB_CLK

SIO CLK 48MHZ

25MHz SATA

32.768KHz

14.31818MHz

A

External clock mode Internal clock mode

A

MICRO-START INT'L CO.,LTD.

Title

Clock Distribution

Size Document Number Custom MS-7549 Date:

5 4 3 2

Rev

1.1

Sheet

1

Wednesday, November 05, 2008

4

of

38

5

4

3

2

1

Power Deliver Chart

AMD AM2r2 CPU

2.5V Shunt Regulator VRM SW REGUALTOR

VDDA25 (S0, S1)

VDDA 2.5V VDDCORE 0.8-1.55V

0.2A 110A

D

D

ATX P/S WITH 1A STBY CURRENT

5VSB +/-5% 5V +/-5%

3.3V +/-5%

12V +/-5%

-12V +/-5%

CPU PW 12V +/-5%

VCCP (S0, S1) / VCC_NB (S0, S1) VCC_DDR (S0, S1, S3) VTT_DDR (S0, S1, S3)

0.9V VTT_DDR REGULATOR

DDR2 MEM I/F VDD MEM 1.8V 10A VTT MEM 0.9V 2A VLDT 1.2V 0.5A

DDRII DIMMX4

VDD MEM

12A 2A

5VDIMM Linear REGULATOR

1.8V VDD SW REGULATOR 1.1V VCC Linear REGULATOR

VTT_DDR

NB_VCC1P1 (S0, S1) NB RS780 VCC_1V2 (S0, S1)

VDDHT/RX 1.1V VDDHTTX 1.2V VDDPCIE 1.1V NB CORE VDDC 1.1V VDDA18PCIE 1.8V PLLs 1.8V

1.2A 0.5A 2A 7A 0.9A 0.1A

1.8V VCC Linear REGULATOR

1.2V VCC Linear REGULATOR

+1.8V_S0 (S0, S1)

VDD18/VDD18_MEM 0.01A 1.8V VDD_MEM 1.8V/1.5V0.5A AVDD 3.3V

C

0.135A

C

SB700

VCC3_SB Linear REGULATOR X4 PCI-E ATA I/O ATA PLL

0.8A 0.5A 0.01A 80mA 0.6A

VCC3_SB (S0, S1, S3, S5)

PCI-E PVDD SB CORE CLOCK

1.2V_SB Linear REGULATOR

+1.2VSB (S0, S1)

1.2V S5 PW

VCC3_SB (S0, S1, S3, S5)

3.3V S5 PW USB CORE I/O

0.22A 0.01A 0.2A 0.45A

VCC3 (S0, S1)

3.3V I/O +5VA Linear REGULATOR 5VDUAL Linear REGULATOR

B

AUDIO CODEC +5VA (S0, S1)

3.3V CORE 5V ANALOG

B

0.1A 0.1A

VCC3_SB (S0, S1, S3, S5)

SUPER I/O

+3.3VDUAL (S3) 0.01A +3.3V (S0, S1) +5V (S0, S1)

0.01A 0.1A

PCI Slot (per slot)

A

X1 PCIE per 3.3V 12V 3.0A 0.5A

X16 PCIE per 3.3V 12V 3.0A 5.5A

USB X6 FR VDD 5VDual 3.0A

USB X6 RL VDD 5VDual 3.0A

2XPS/2 5VDual 0.5A

ENTHENET

3.3V (S3)

IEEE-1394 x1

3.3V (S0, S1) 0.1A

A

5V 3.3V 12V 3.3VDual -12V

5.0A 7.6A 0.5A 0.375A 0.1A

0.1A

3.3V (S0, S1) 0.5A

12V (S0, S1) 1.1A

3.3Vaux 0.1A

3.3VDual 0.1A

MICRO-START INT'L CO.,LTD.

Title

Power Deliver Chart

Size C Date:

5 4 3 2

Document Number

Rev

MS-7549

Wednesday, November 05, 2008

1

1.1

Sheet 5 of 38

5

4

3

2

1

+12VIN

ISL6323CR CKT for Hybride

VCC5_SB VCC5 R606 10.7KR1%0402 R568 X_2.2R1%0805 R631 R617 2.2R1%0805 U_G1 R611 1R0805 2.2R1%0805 +12VIN R622 10KR0402 PHASE1 C791 C4.7u10Y0805 C767 C1u25X0805-RH L_G1 R625 0R0805 G C778 C0.1u16Y0402

VIN VCCP C796 C1u16X5 N-P0803BDG_TO252-3-RH N-P0803BDG_TO252-3-RH Q83 Q94 G G D D S S C753 C10u16Y1206 1+ EC73 2

D

VCC5_SB

D

CD680u4EL9-RH EC72 1+ 2 CHOKE13 1 CH-0.5u40A-RH-1 2 CD680u4EL9-RH VCCP 1+ EC70 2

R628 10KR0402

R595

1KR1%0402 C Q88 N-MMBT3904_NL_SOT23

33 VCORE_EN#

VCORE_EN# R633 10KR0402 VCC5

B E

D

Q90 G

D

Q91 75N02 C775

R620 2.2R1%0805 CP55 X_COPPER CP54

CD680u4EL9-RH 1+ X_COPPER EC62 2

S

VCC

R623 10KR0402 33 PWR_GOOD 8 PWROK_PWM 8 CPUVID5 8 CPUVID4 8 CPUVID3 8 CPUVID2 8 CPUVID1 8 CPUVID0 VCCP_NB 24 37 34 9 8 7 6 5 4 C761 R596 X_470R1%0402 R605 360R1%0402 UPI6262_NB R567 X_C680p50X0402-RH C798 R613 100R0402 10

C

U37 EN VDDPWRGD PWROK VID5 VID4 VID3/SVC VID2/SVD VID1/SEL VID0/VFIXEN

10

7X7 QFN

ISL6323CR PVCC1_2 29 BOOT1 UGATE1 PHASE1 LGATE1 ISEN1+ ISEN131 32 33 30 20 21 R600 2.2R1%0805 U_G1 PHASE1 L_G1 ISEN1+ ISEN1IPHASE1 R577 R616

S

75N02 C784 C0.1u25X VIN C790 255R1%0402-RH ISEN1 C770 C794 C0.1u16Y0402 C0.1u16X0402 S U_G2 R599 1R0805 C1u16X5 N-P0803BDG_TO252-3-RH N-P0803BDG_TO252-3-RH Q82 Q86 G G D D S R632 C783 C0.1u25X PHASE2 D Q84 G S S 75N02 C755 C1000p50X0402 IPHASE2 ISEN2 C787 C0.1u16Y0402 C0.1u16X0402 R607 2.2R1%0805 U35 6 7 C782 C0.1u25X PWM3 C1u16X5 PHASE 4 3 GND D Q87 G 2.2R1%0805 S S 75N02 CP52 C763 C1000p50X0402 X_COPPER IPHASE3 ISEN3 VIN D Q80 R593 PWM LGATE 5 L_G3 R598 0R0805 G 8 1 2 U_G3 R615 2.2R1%0805 PHASE3 R609 C788 1R0805 C0.1u25X 10KR0402 C797 C1u16X5 N-P0803BDG_TO252-3-RH N-P0803BDG_TO252-3-RH G Q85 G Q93 R581 D D S S C768 C10u16Y1206 +12VIN VIN D Q92 10KR0402 C759 C10u16Y1206 C1000p50X0402 IPHASE1 ISEN1

output CAP

CD680u4EL9-RH 1+ EC75 2

CD680u4EL9-RH EC64 1+ 2 CD680u4EL9-RH 1+ EC66 2

C793 X_C0.1u16Y0402

C795 1.2KR1%0402 C0.01u25X0402 48 COMP_NB C10p50N0402-RH 1 FB_NB

R571 6.8KR1%0402-RH 2.2R1%0805

BOOT2 UGATE2 PHASE2 LGATE2 ISEN2+ ISEN2-

27 26 25 28 22 23

CD680u4EL9-RH CHOKE16 1 R634 2.2R1%0805 CP57 X_COPPER CP56 X_COPPER VCCP_NB CH-0.5U40A-RH-1 2 EC69 2

C

NB_VSEN

R579

0R0402 C776 X_C0.1u16Y0402

ISEN_NB_A R587 R589 X_0R0402 R572 0R0402 C780 X_C0.1u16Y0402 R642

0R0402

2

VSEN_NB RGND_NB

U_G2 PHASE2 L_G2 ISEN2+ ISEN2IPHASE2 PWM3 ISEN3+ ISEN3IPHASE3 R575 R576 R608 R597

VCCP

1+

6262_VCCNB 3

CD680u4EL9-RH

ISEN2 255R1%0402-RH C771 C765 C0.1u16X0402 C0.1u16Y0402 ISEN3 255R1%0402-RH C773

L_G2

R580

0R0805

G

10

NB_GND VCCP

R569

0R0402 VCCP R610 100R0402 R640 X_100R0402 R601 C766 X_470R1%0402 R574 C757 C0.01u25X0402 1.2KR1%0402 18 C752 C33p50N0402 17 R591 560R1%0402-RH 1.1KR1%0402 C774 15 C0.01u25X0402 13 12 C760 X_C0.1u16Y0402 C781 X_C0.1u16Y0402 C758 C0.1u16Y0402 VSEN RGND FB RCOMP COMP

R641 6.8KR1%0402-RH

X_C1000p50X0402

PWM3 ISEN3+ ISEN3-

35 44 43

75N02

R621 100R0402 8 COREFB_H R588 COREFB_H 0R0402 6262_VCCP

C764 C0.1u16Y0402 8 COREFB_L R603 0R0402 R614 100R0402 R578 4.99KR1%0402

PWM4 ISEN4+ ISEN4-

36 46 45

R643 6.8KR1%0402-RH VCC5 X_0R0805 VCC5 0R0805

NB-output CAP

1+

EC68 2

CD680u4EL9-RH 1+ EC71 2

PVCC_NB BOOT_NB APA RESET OFS FS UGATE_NB PHASE_NB LGATE_NB GND ISEN_NB

42 40 39 38 41 47

R590

2.2R1%0805

+12VIN

VCC PVCC

UGATE BOOT

CD680u4EL9-RH

C754 C1u25X0805-RH R627 2.2R1%0805 UGATE_NB PHASE_NB LGATE_NB C769

19 VCC5 R592 C751 R626 5 56KR1%0402 X_C0.1u16Y0402 69.8KR1%0402-RH VCC5 GND 12V +12VIN

B

CHOKE14 1

CH-0.5U40A-RH-1 2 VCCP

16 14 11

ISL6612ACBZT_SOIC8-RH R604 X_6.2KR1%0402 75N02 ISEN_NB_A C772 C0.1u16X0402 C785 C0.1u16X0402

CP58 X_COPPER

B

R612 X_10KR1%0402

49

3 4

1 2 R619 X_10KR0402

PHASE_NB_A R586 120KR1%0402 GND 12V C779 X_C0.01u25X0402 JPWR3 PWRCONN4P_CREAM-RH-1

R624 6.8KR1%0402-RH

+12VIN

CHOKE12 1 2 1 1 1 1 1 VIN C792 EC67 2 input CAP C789CH-1.1u27A2.5m-RH 2 VCC5 + EC63 2 R573 3VDUAL R585 X_4.7KR0402 + EC76 2 + EC74 2 + EC65 +

D

BOTTOM PAD CONNECT TO GND Through 8 VIAs

UGATE_NB R629 1R0805 R602 G

C762 C1u16X5 Q81 N-P0803BDG_TO252-3-RH

C786 C10u16Y1206

S

VCCP_NB CHOKE15 1 CH-0.5U40A-RH-1 2

10KR0402 R618 X_2.2R/0603 PHASE_NB D Q76 G S S C777 D Q89 R594 2.2R1%0805

X_C0.01u25X0402 C0.1u16Y0402 CD1000u16EL20-RH-3 CD1000u16EL20-RH-3 CD1000u16EL20-RH-3 CD1000u16EL20-RH-3 CD1000u16EL20-RH-3 VCC_DDR

C756 X_C0.1u16Y0402

LGATE_NB

R630

0R0805

G

CP53 X_COPPER

CP51 X_COPPER

U38

1

X_300R0402

CPUVID1

GND SDA OUT1

BUS_SELVCC

LOW FOR SVID

R582 X_27R0402 R583 X_27R0402 6262_VCCNB D D UPI6262_NB R639 G VCORE_EN# Q77 Q79 7,11,20,33 SDA0 R637 X_0R0402 X_0R0402 6262_VCCNB_R

3 4 8

OUT2 OUT3 SCL

7 6 5

6262_VCCP_R R635

X_0R0402 6262_VCCP 75N02 75N02 C1000p50X0402 PHASE_NB_A ISEN_NB_A

SCL0

7,11,20,33

2

BUS_SEL=100%VCC

X_UP6262M8_SOT23-8-RH R636 X_10KR0402 VCC5

A

A

G R584 10 CPU_CORE_TYPE B X_4.7KR0402 E X_N-2N7002_SOT23 300R0402 C S S Q78

R638 X_N-2N7002_SOT23 X_1KR0402

I2C address:0X60 R643=10K;R644=OPEN

R570

MICRO-START INT'L CO.,LTD.

Title

X_N-MMBT3904_NL_SOT23 Size Document Number Custom Date:

5 4 3 2

STL6740 3+1PHASE

Rev

MS-7549

Sheet 6 of 38

1

1.1

Wednesday, November 12, 2008

5

4

3

2

1

VCC3

CP7 X_Copper

CLK_VDD

L11

X_30L3A-15_0805-RH C347 C10u10Y0805

C338 C0.1u16X0402-2

C342 X_C0.1u16X0402-2

C325 C0.1u16X0402-2

C339 X_C0.1u16X0402-2

C320 X_C0.1u16X0402-2

C281 X_C0.1u16X0402-2

C272 X_C0.1u16X0402-2

1- PLACE ALL THE SERIES TERMINATION RESISTORS AS CLOSE AS U41 AS POSSIBLE

D D

2- ROUTE ALL CPUCLK/#, NBSRCCLK/#, GPPCLK/# AS DIFFERENT PAIR RULE 3- PUT DECOUPLING CAPS CLOSE TO U41 POWER PIN

CP9 X_Copper L12 X_30L3A-15_0805-RH CLK_VDD C287 X_C10u10Y0805 C299 C0.1u16X0402-2 CLK_VDDA U16A

VCC3

44 43 60 61

VDDA GNDA VDDREF GNDREF VDDSATA GNDSATA VDD48 GND48 VDDCPU GNDCPU VDDHTT GNDHTT VDDATIG VDDSRC VDDSRC VDDSB_SRC GNDATIG GNDATIG GNDSRC GNDSRC GNDSB_SRC X1 X2 RESTORE# SMBCLK SMBDAT PD#

CPUKG0T_LPRS CPUKG0C_LPRS CPUKG1T_LPRS/SRC7T_LPRS CPUKG1C_LPRS/SRC7C_LPRS ATIG0T_LPRS ATIG0C_LPRS ATIG1T_LPRS ATIG1C_LPRS ATIG2T_LPRS ATIG2C_LPRS ATIG3T_LPRS ATIG3C_LPRS SB_SRC0T_LPRS SB_SRC0C_LPRS SB_SRC1T_LPRS SB_SRC1C_LPRS SRC0T_LPRS SRC0C_LPRS SRC1T_LPRS SRC1C_LPRS SRC2T_LPRS SRC2C_LPRS SRC3T_LPRS SRC3C_LPRS SRC4T_LPRS SRC4C_LPRS **DOC_1/SRC5T_LPRS **DOC_0/SRC5C_LPRS SRC6T/SATAT_LPRS SRC6C/SATAC_LPRS HTT0T_LPRS/66M HTT0C_LPRS/66M **SEL_CPU1#/48MHz_0 **SEL_DOC/48MHz_1

50 49 46 45 38 37 36 35 32 31 30 29 27 26 23 22 21 20 19 18 15 14 13 12 9 8 7 6 41 40 55 54 2 1

CPU_CLK CPU_CLK# RN22 NBGFX_SRCCLK_R NBGFX_SRCCLK#_R GFX_CLKP_R GFX_CLKN_R

CPU_CLK CPU_CLK#

8 8

VCC3 CP6 L10 X_30L3A-15_0805-RH C275 C1u6.3Y0402-RH X_Copper VDD48

39 42 64 3 48 47 56 53 34 11 16 25

1 3 5 7

2 4 6 8

8P4R-0R0402

NBGFX_SRCCLK 15 NBGFX_SRCCLK# 15 GFX_CLKP 23 GFX_CLKN 23

C

C

GPPCLK0 GPPCLK0# CK_PE_100M_LAN CK_PE_100M_LAN# NBLINKCLK NBLINKCLK# DOC1# DOC0# SBSRCCLK SBSRCCLK# HTREFCLK HTREFCLK# SIO_CLK_R USBCLK_EXT_R R227 33R0402 R228 0R0402

GPPCLK0 GPPCLK0#

23 23

C256 C22p50N C255 C22p50N CLK_VDD 20,30,33,34 FP_RST# 6,11,20,33 SCL0 6,11,20,33 SDA0 CLK_VDD

14.318MHZ16P_D-RH

28 33 10 17 24

TXC1 TXC2 RST#_CLK

Y2

1

R202 X_1MR

CK_PE_100M_LAN 27 CK_PE_100M_LAN# 27 NBLINKCLK 15 NBLINKCLK# 15 SBSRCCLK SBSRCCLK# HTREFCLK HTREFCLK# SIO_CLK USBCLK_EXT 18 18 15 15 30 20

2

CLK_VDD

U16B

4 5

PD#

DOC

R225 10KR0402 USBCLK_EXT_R

R217

1KR0402 CLK_VDD

51 59 58

REF0/SEL_HTT66 REF1/SEL_SATA REF2/SEL_OC_MODE**

ICS9LPRS477BKLFT_MLF64-RH

B

C306 C10p50N0402

C311 C10p50N0402

ICS9LPRS477BKLFT_MLF64-RH

THERMPAD

R216 X_4.7KR0402 R206 0R0402 R235 0R0402 R239 0R0402

52

65

62 63

B

NB RS740 RX780 RS780 15 NB_OSC_14M

NB_OSC_14M R214 3.3V 33R serial 1.8V 75R/100R 1.1V 150R/75R R213 R215 X_10KR0402 SEL_HTT66 SEL_SATA SEL_OC_MODE

57

EMI suggest

X_10KR0402 X_10KR0402 R205 150R1%0402

SEL_SATA R212 10KR0402 R204 10KR0402

R663

X_0R0402

25M_48M_66M_OSC C835 X_10p/50v/N/4

25M_48M_66M_OSC 18

VCC3

R200 75R1%0402

C249 X_C10p50N0402

Reserved for EMI 0906

EXT CLK FREQUENCY SELECT TABLE(MHZ)

REF0/SEL_HTT66 0

A

R245 4.7KR0402 DOC0# R243 X_4.7KR0402 DOC1#

HTT CLOCK 100.00 DIFFERENTIAL 66.66 SINGLE END

FS2 FS1 FS0 0 0 0 0 1 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 1

CPU Hi-Z X

SRCCLK HTT [2:1] 100.00 Hi-Z 100.00 X/3

PCI Hi-Z X/6 30.00 73.12 33.33 33.33 33.33

USB 48.00 48.00 48.00 48.00 48.00 48.00 48.00

COMMENT Reserved Reserved Reserved Reserved Reserved Reserved Normal HAMMER operation

1

A

180.00 100.00 60.00 220.00 100.00 36.56 100.00 100.00 66.66 133.33 100.00 66.66 200.00 100.00 66.66

Micro Star Restricted Secret

Title

Rev

Clock-Gen ICS9LPRS477

MS-7549

MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan https://www.doczj.com/doc/3e247924.html,

Document Number

1.1

Last Revision Date: Tuesday, November 11, 2008 Sheet of 7 38

1

5

4

3

2

5

4

3

2

1

VCC_DDR 300R/4 300R/4 CPU_THRIP#

D

20 19,30 R184 18

TALERT# CPU_HOT CPU_HOT

R185

2 4 6 8

D

RN18 8P4R-4.7KR0402 1 3 5 7 Q37

13 HT_CADIN_H[15..0] 13 HT_CADIN_L[15..0] 13 HT_CADOUT_H[15..0] 13 HT_CADOUT_L[15..0]

HT_CADIN_H[15..0] HT_CADIN_L[15..0] HT_CADOUT_H[15..0] HT_CADOUT_L[15..0] L2 80/2A/B8 C84 C77 4.7u/16v/Y5/1206 R116 169R/6/1% CPUCLKIN CPUCLKIN# 18 LDT_PWRGD 15,18 LDT_STOP# 15,18 LDT_RST# C74 X_1000p/50v/X7/6 R176 R177 1K/4/5% 1K/4/5% THERM_SIC THERM_SID TP21 TP17 TP16 TP23 CPU_TDI CPU_TRST_L CPU_TCK CPU_TMS CPU_DBREQ_L VCC_DDR 6 6 COREFB_H COREFB_L TP10 R183 39.2R/6/1% CPU_STRAP_HI_E11 CPU_STRAP_LO_F11 R180 39.2R/6/1% CPU_TEST25_H CPU_TEST25_L 300R/4 300R/4 CPU_VTT_SENSE CPU_M_VREF 0.22u/16v/X7/6 3300p/50v/X7/4 VDDA25 VDDA_25 VDDA25

CPU_HOT TALERT# CPU_THRIP_L# CPU_THRIP#

4 3 1 6

5 2

VCCA_1V2

VCCA_1V2

VCC_DDR place near the PWM IC 7 CPU_CLK 3900p/50vX7/6 X_0.22u/16v/X7/6 C83 3900p/50vX7/6 7 CPU_CLK# C85 C89 C10 D10 A8 B8 C9 D8 C7 AL3 AL6 AK6 AL10 AJ10 AH10 AL9 A5 G2 G1 E12 F12 AH11 AJ11 A10 B10 F10 E9 AJ7 F6 D6 E7 F8 C5 AH9 E5 AJ5 AG9 AG8 AH7 AJ6 VDDA1 VDDA2 CLKIN_H CLKIN_L PWROK LDTSTOP_L RESET_L CPU_PRESENT_L SIC SID TDI TRST_L TCK TMS DBREQ_L VDD_FB_H VDD_FB_L VTT_SENSE M_VREF M_ZN M_ZP TEST25_H TEST25_L TEST19 TEST18 TEST13 TEST9 TEST17 TEST16 TEST15 TEST14 TEST12 TEST7 TEST6 TEST5 TEST4 TEST3 TEST2 ZIF-SOCK940-RH-1 VID(5) VID(4) VID(3) VID(2) VID(1) VID(0) D2 D1 C1 E3 E2 E1 AK7 AL7 AK10 CPUVID5 CPUVID4 CPUVID3 CPUVID2 CPUVID1 CPUVID0 CPU_THRIP_L# CPU_HOT CPU_TDO TP19 6 6 6 6 6 6 CPUVID5 CPUVID4 CPUVID3 CPUVID2 CPUVID1 CPUVID0 R143 R141 1K/4/5% 1K/4/5% CPU1D

C94

C187

C97

C95

C230 C234 4.7u/16v/Y5/1206

C236

C253

C210

C213

0.22u/16v/X7/6 X_0.22u/16v/X7/6 0.22u/16v/X7/6 X_0.22u/16v/X7/6

X_4.7u/16v/Y5/1206 X_0.22u/16v/X7/6 X_4.7u/16v/Y5/1206 0.22u/16v/X7/6

C

CPU1A 13 13 13 13 13 13 13 13 HT_CLKIN_H1 HT_CLKIN_L1 HT_CLKIN_H0 HT_CLKIN_L0 HT_CTLIN_H1 HT_CTLIN_L1 HT_CTLIN_H0 HT_CTLIN_L0 HT_CADIN_H15 HT_CADIN_L15 HT_CADIN_H14 HT_CADIN_L14 HT_CADIN_H13 HT_CADIN_L13 HT_CADIN_H12 HT_CADIN_L12 HT_CADIN_H11 HT_CADIN_L11 HT_CADIN_H10 HT_CADIN_L10 HT_CADIN_H9 HT_CADIN_L9 HT_CADIN_H8 HT_CADIN_L8

B

VCC_DDR L0_CLKOUT_H(1) L0_CLKOUT_L(1) L0_CLKOUT_H(0) L0_CLKOUT_L(0) L0_CTLOUT_H(1) L0_CTLOUT_L(1) L0_CTLOUT_H(0) L0_CTLOUT_L(0) L0_CADOUT_H(15) L0_CADOUT_L(15) L0_CADOUT_H(14) L0_CADOUT_L(14) L0_CADOUT_H(13) L0_CADOUT_L(13) L0_CADOUT_H(12) L0_CADOUT_L(12) L0_CADOUT_H(11) L0_CADOUT_L(11) L0_CADOUT_H(10) L0_CADOUT_L(10) L0_CADOUT_H(9) L0_CADOUT_L(9) L0_CADOUT_H(8) L0_CADOUT_L(8) L0_CADOUT_H(7) L0_CADOUT_L(7) L0_CADOUT_H(6) L0_CADOUT_L(6) L0_CADOUT_H(5) L0_CADOUT_L(5) L0_CADOUT_H(4) L0_CADOUT_L(4) L0_CADOUT_H(3) L0_CADOUT_L(3) L0_CADOUT_H(2) L0_CADOUT_L(2) L0_CADOUT_H(1) L0_CADOUT_L(1) L0_CADOUT_H(0) L0_CADOUT_L(0) AD5 AD4 AD1 AC1 Y6 W6 W2 W3 Y5 Y4 AB6 AA6 AB5 AB4 AD6 AC6 AF6 AE6 AF5 AF4 AH6 AG6 AH5 AH4 Y1 W1 AA2 AA3 AB1 AA1 AC2 AC3 AE2 AE3 AF1 AE1 AG2 AG3 AH1 AG1 HT_CLKOUT_H1 HT_CLKOUT_L1 HT_CLKOUT_H0 HT_CLKOUT_L0 HT_CTLOUT_H1 HT_CTLOUT_L1 HT_CTLOUT_H0 HT_CTLOUT_L0 HT_CADOUT_H15 HT_CADOUT_L15 HT_CADOUT_H14 HT_CADOUT_L14 HT_CADOUT_H13 HT_CADOUT_L13 HT_CADOUT_H12 HT_CADOUT_L12 HT_CADOUT_H11 HT_CADOUT_L11 HT_CADOUT_H10 HT_CADOUT_L10 HT_CADOUT_H9 HT_CADOUT_L9 HT_CADOUT_H8 HT_CADOUT_L8 HT_CADOUT_H7 HT_CADOUT_L7 HT_CADOUT_H6 HT_CADOUT_L6 HT_CADOUT_H5 HT_CADOUT_L5 HT_CADOUT_H4 HT_CADOUT_L4 HT_CADOUT_H3 HT_CADOUT_L3 HT_CADOUT_H2 HT_CADOUT_L2 HT_CADOUT_H1 HT_CADOUT_L1 HT_CADOUT_H0 HT_CADOUT_L0 13 13 13 13 13 13 13 13

LDT_PWRGD LDT_STOP# LDT_RST# TP20 CPU_PRESENT_L

C

N6 P6 N3 N2 V4 V5 U1 V1 U6 V6 T4 T5 R6 T6 P4 P5 M4 M5 L6 M6 K4 K5 J6 K6 U3 U2 R1 T1 R3 R2 N1 P1 L1 M1 L3 L2 J1 K1 J3 J2

L0_CLKIN_H(1) L0_CLKIN_L(1) L0_CLKIN_H(0) L0_CLKIN_L(0) L0_CTLIN_H(1) L0_CTLIN_L(1) L0_CTLIN_H(0) L0_CTLIN_L(0) L0_CADIN_H(15) L0_CADIN_L(15) L0_CADIN_H(14) L0_CADIN_L(14) L0_CADIN_H(13) L0_CADIN_L(13) L0_CADIN_H(12) L0_CADIN_L(12) L0_CADIN_H(11) L0_CADIN_L(11) L0_CADIN_H(10) L0_CADIN_L(10) L0_CADIN_H(9) L0_CADIN_L(9) L0_CADIN_H(8) L0_CADIN_L(8) L0_CADIN_H(7) L0_CADIN_L(7) L0_CADIN_H(6) L0_CADIN_L(6) L0_CADIN_H(5) L0_CADIN_L(5) L0_CADIN_H(4) L0_CADIN_L(4) L0_CADIN_H(3) L0_CADIN_L(3) L0_CADIN_H(2) L0_CADIN_L(2) L0_CADIN_H(1) L0_CADIN_L(1) L0_CADIN_H(0) L0_CADIN_L(0) ZIF-SOCK940-RH-1

THERMTRIP_L PROCHOT_L TDO

TP5 DBRDY VDDIO_FB_H VDDIO_FB_L PSI_L HTREF1 HTREF0 TEST29_H TEST29_L B6 AK11 AL11 F1 V8 V7 C11 D11 CPU_PSI_L HTREF1 HTREF0 CPU_DBRDY

VCC_DDR

TP9 VCCA_1V2 R181 R182 C180 1000p/50v/X7/4 R115 80.6R/6/1%

B

44.2R/6/1% 44.2R/6/1%

R112 R113

C181 1000p/50v/X7/4

HT_CADIN_H7 HT_CADIN_L7 HT_CADIN_H6 HT_CADIN_L6 HT_CADIN_H5 HT_CADIN_L5 HT_CADIN_H4 HT_CADIN_L4 HT_CADIN_H3 HT_CADIN_L3 HT_CADIN_H2 HT_CADIN_L2 HT_CADIN_H1 HT_CADIN_L1 HT_CADIN_H0 HT_CADIN_L0

TP18 VCC_DDR TP24 300R/4 R179 300R/4

30 THERMDC_CPU 30 THERMDA_CPU

TEST28_H TEST28_L TEST27 TEST26 TEST10 TEST8

J10 H9 AK9 AK5 G7 D4

R178 300R0402

TP8 TP11 TP13 TP6 TP15

TEST24 TEST23 TEST22 TEST21 TEST20

AK8 AH8 AJ9 AL8 AJ8

TP22 TP14 CPU_TEST22 CPU_TEST21

VCC_DDR

R175

R101 15R/6/1% CPU_M_VREF R108 15R/6/1% C88 TP1 C82 1000p/50v/X7/6

CPU_DBREQ_L C66 X_C0.1u25Y

0.1u/25v/Y5/4 VCC_DDR RN5

VCC_DDR

VCC3 VCC_DDR

1 3 5 7

2 4 6 8 8P4R/300R/6

CPU_DBREQ_L LDT_RST# LDT_STOP# LDT_PWRGD

R132 4.7K/4

A

R68 10K/4

CPU_PRESENT_L R172 CPU_TEST25_H R110 CPU_TEST25_L R114

1K/4/5% 510R/0402 510R/0402

B

LDT_PWRGD

E

Q22 2N3904_SOT23 C

A

Micro Star Restricted Secret

PWROK_PWM 6

Title

Rev

K9 M2 HT I/F,CTRL&DEBUG

MS-7549

1.1

Document Number

MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan https://www.doczj.com/doc/3e247924.html,

Last Revision Date: Sunday, November 09, 2008 Sheet 8 38 of

5

4

3

2

1

5

4

3

2

1

11 MEM_MA_DQS_L[7..0] 11 MEM_MA_DQS_H[7..0] 11 MEM_MA_DM[7..0]

D

MEM_MA_DQS_L[7..0] MEM_MA_DQS_H[7..0] MEM_MA_DM[7..0] MEM_MA_ADD[15..0] MEM_MA_DATA[63..0] CPU1B

11 MEM_MB_DQS_L[7..0] 11 MEM_MB_DQS_H[7..0] 11 MEM_MB_DM[7..0] 11,12 MEM_MB_ADD[15..0] 11 MEM_MB_DATA[63..0]

MEM_MB_DQS_L[7..0] MEM_MB_DQS_H[7..0] MEM_MB_DM[7..0] MEM_MB_ADD[15..0] MEM_MB_DATA[63..0]

D

11,12 MEM_MA_ADD[15..0] 11 MEM_MA_DATA[63..0]

CPU1C 11,12 11,12 11,12 11,12 11,12 11,12 MEM_MA0_CLK_H2 MEM_MA0_CLK_L2 MEM_MA0_CLK_H1 MEM_MA0_CLK_L1 MEM_MA0_CLK_H0 MEM_MA0_CLK_L0 MEM_MA0_CLK_H2 MEM_MA0_CLK_L2 MEM_MA0_CLK_H1 MEM_MA0_CLK_L1 MEM_MA0_CLK_H0 MEM_MA0_CLK_L0 MEM_MA0_CS_L1 MEM_MA0_CS_L0 MEM_MA0_ODT0 AG21 AG20 G19 H19 U27 U26 AC25 AA24 AC28 AE20 AE19 G20 G21 V27 W27 AD27 AA25 AC27

C

MA0_CLK_H(2) MA0_CLK_L(2) MA0_CLK_H(1) MA0_CLK_L(1) MA0_CLK_H(0) MA0_CLK_L(0) MA0_CS_L(1) MA0_CS_L(0) MA0_ODT(0) MA1_CLK_H(2) MA1_CLK_L(2) MA1_CLK_H(1) MA1_CLK_L(1) MA1_CLK_H(0) MA1_CLK_L(0) MA1_CS_L(1) MA1_CS_L(0) MA1_ODT(0) MA_CAS_L MA_WE_L MA_RAS_L MA_BANK(2) MA_BANK(1) MA_BANK(0) MA_CKE(1) MA_CKE(0) MA_ADD(15) MA_ADD(14) MA_ADD(13) MA_ADD(12) MA_ADD(11) MA_ADD(10) MA_ADD(9) MA_ADD(8) MA_ADD(7) MA_ADD(6) MA_ADD(5) MA_ADD(4) MA_ADD(3) MA_ADD(2) MA_ADD(1) MA_ADD(0) MA_DQS_H(7) MA_DQS_L(7) MA_DQS_H(6) MA_DQS_L(6) MA_DQS_H(5) MA_DQS_L(5) MA_DQS_H(4) MA_DQS_L(4) MA_DQS_H(3) MA_DQS_L(3) MA_DQS_H(2) MA_DQS_L(2) MA_DQS_H(1) MA_DQS_L(1) MA_DQS_H(0) MA_DQS_L(0) MA_DM(7) MA_DM(6) MA_DM(5) MA_DM(4) MA_DM(3) MA_DM(2) MA_DM(1) MA_DM(0) ZIF-SOCK940-RH-1

11,12 MEM_MA0_CS_L1 11,12 MEM_MA0_CS_L0 11,12 MEM_MA0_ODT0

11,12 MEM_MA_CAS_L 11,12 MEM_MA_WE_L 11,12 MEM_MA_RAS_L 11,12 MEM_MA_BANK2 11,12 MEM_MA_BANK1 11,12 MEM_MA_BANK0 12 MEM_MA_CKE1 11,12 MEM_MA_CKE0

MEM_MA_CAS_L MEM_MA_WE_L MEM_MA_RAS_L MEM_MA_BANK2 MEM_MA_BANK1 MEM_MA_BANK0 MEM_MA_CKE1 MEM_MA_CKE0 MEM_MA_ADD15 MEM_MA_ADD14 MEM_MA_ADD13 MEM_MA_ADD12 MEM_MA_ADD11 MEM_MA_ADD10 MEM_MA_ADD9 MEM_MA_ADD8 MEM_MA_ADD7 MEM_MA_ADD6 MEM_MA_ADD5 MEM_MA_ADD4 MEM_MA_ADD3 MEM_MA_ADD2 MEM_MA_ADD1 MEM_MA_ADD0 MEM_MA_DQS_H7 MEM_MA_DQS_L7 MEM_MA_DQS_H6 MEM_MA_DQS_L6 MEM_MA_DQS_H5 MEM_MA_DQS_L5 MEM_MA_DQS_H4 MEM_MA_DQS_L4 MEM_MA_DQS_H3 MEM_MA_DQS_L3 MEM_MA_DQS_H2 MEM_MA_DQS_L2 MEM_MA_DQS_H1 MEM_MA_DQS_L1 MEM_MA_DQS_H0 MEM_MA_DQS_L0 MEM_MA_DM7 MEM_MA_DM6 MEM_MA_DM5 MEM_MA_DM4 MEM_MA_DM3 MEM_MA_DM2 MEM_MA_DM1 MEM_MA_DM0

AB25 AB27 AA26 N25 Y27 AA27 L27 M25 M27 N24 AC26 N26 P25 Y25 N27 R24 P27 R25 R26 R27 T25 U25 T27 W24 AD15 AE15 AG18 AG19 AG24 AG25 AG27 AG28 D29 C29 C25 D25 E19 F19 F15 G15 AF15 AF19 AJ25 AH29 B29 E24 E18 H15

B

MA_DATA(63) MA_DATA(62) MA_DATA(61) MA_DATA(60) MA_DATA(59) MA_DATA(58) MA_DATA(57) MA_DATA(56) MA_DATA(55) MA_DATA(54) MA_DATA(53) MA_DATA(52) MA_DATA(51) MA_DATA(50) MA_DATA(49) MA_DATA(48) MA_DATA(47) MA_DATA(46) MA_DATA(45) MA_DATA(44) MA_DATA(43) MA_DATA(42) MA_DATA(41) MA_DATA(40) MA_DATA(39) MA_DATA(38) MA_DATA(37) MA_DATA(36) MA_DATA(35) MA_DATA(34) MA_DATA(33) MA_DATA(32) MA_DATA(31) MA_DATA(30) MA_DATA(29) MA_DATA(28) MA_DATA(27) MA_DATA(26) MA_DATA(25) MA_DATA(24) MA_DATA(23) MA_DATA(22) MA_DATA(21) MA_DATA(20) MA_DATA(19) MA_DATA(18) MA_DATA(17) MA_DATA(16) MA_DATA(15) MA_DATA(14) MA_DATA(13) MA_DATA(12) MA_DATA(11) MA_DATA(10) MA_DATA(9) MA_DATA(8) MA_DATA(7) MA_DATA(6) MA_DATA(5) MA_DATA(4) MA_DATA(3) MA_DATA(2) MA_DATA(1) MA_DATA(0) MA_DQS_H(8) MA_DQS_L(8) MA_DM(8) MA_CHECK(7) MA_CHECK(6) MA_CHECK(5) MA_CHECK(4) MA_CHECK(3) MA_CHECK(2) MA_CHECK(1) MA_CHECK(0)

AE14 AG14 AG16 AD17 AD13 AE13 AG15 AE16 AG17 AE18 AD21 AG22 AE17 AF17 AF21 AE21 AF23 AE23 AJ26 AG26 AE22 AG23 AH25 AF25 AJ28 AJ29 AF29 AE26 AJ27 AH27 AG29 AF27 E29 E28 D27 C27 G26 F27 C28 E27 F25 E25 E23 D23 E26 C26 G23 F23 E22 E21 F17 G17 G22 F21 G18 E17 G16 E15 G13 H13 H17 E16 E14 G14 J28 J27 J25 K25 J26 G28 G27 L24 K27 H29 H27

MEM_MA_DATA63 MEM_MA_DATA62 MEM_MA_DATA61 MEM_MA_DATA60 MEM_MA_DATA59 MEM_MA_DATA58 MEM_MA_DATA57 MEM_MA_DATA56 MEM_MA_DATA55 MEM_MA_DATA54 MEM_MA_DATA53 MEM_MA_DATA52 MEM_MA_DATA51 MEM_MA_DATA50 MEM_MA_DATA49 MEM_MA_DATA48 MEM_MA_DATA47 MEM_MA_DATA46 MEM_MA_DATA45 MEM_MA_DATA44 MEM_MA_DATA43 MEM_MA_DATA42 MEM_MA_DATA41 MEM_MA_DATA40 MEM_MA_DATA39 MEM_MA_DATA38 MEM_MA_DATA37 MEM_MA_DATA36 MEM_MA_DATA35 MEM_MA_DATA34 MEM_MA_DATA33 MEM_MA_DATA32 MEM_MA_DATA31 MEM_MA_DATA30 MEM_MA_DATA29 MEM_MA_DATA28 MEM_MA_DATA27 MEM_MA_DATA26 MEM_MA_DATA25 MEM_MA_DATA24 MEM_MA_DATA23 MEM_MA_DATA22 MEM_MA_DATA21 MEM_MA_DATA20 MEM_MA_DATA19 MEM_MA_DATA18 MEM_MA_DATA17 MEM_MA_DATA16 MEM_MA_DATA15 MEM_MA_DATA14 MEM_MA_DATA13 MEM_MA_DATA12 MEM_MA_DATA11 MEM_MA_DATA10 MEM_MA_DATA9 MEM_MA_DATA8 MEM_MA_DATA7 MEM_MA_DATA6 MEM_MA_DATA5 MEM_MA_DATA4 MEM_MA_DATA3 MEM_MA_DATA2 MEM_MA_DATA1 MEM_MA_DATA0

11,12 11,12 11,12 11,12 11,12 11,12

MEM_MB0_CLK_H2 MEM_MB0_CLK_L2 MEM_MB0_CLK_H1 MEM_MB0_CLK_L1 MEM_MB0_CLK_H0 MEM_MB0_CLK_L0

MEM_MB0_CLK_H2 MEM_MB0_CLK_L2 MEM_MB0_CLK_H1 MEM_MB0_CLK_L1 MEM_MB0_CLK_H0 MEM_MB0_CLK_L0 MEM_MB0_CS_L1 MEM_MB0_CS_L0 MEM_MB0_ODT0

AJ19 AK19 A18 A19 U31 U30 AE30 AC31 AD29 AL19 AL18 C19 D19 W29 W28 AE29 AB31 AD31

MB0_CLK_H(2) MB0_CLK_L(2) MB0_CLK_H(1) MB0_CLK_L(1) MB0_CLK_H(0) MB0_CLK_L(0) MB0_CS_L(1) MB0_CS_L(0) MB0_ODT(0) MB1_CLK_H(2) MB1_CLK_L(2) MB1_CLK_H(1) MB1_CLK_L(1) MB1_CLK_H(0) MB1_CLK_L(0) MB1_CS_L(1) MB1_CS_L(0) MB1_ODT(0) MB_CAS_L MB_WE_L MB_RAS_L MB_BANK(2) MB_BANK(1) MB_BANK(0) MB_CKE(1) MB_CKE(0) MB_ADD(15) MB_ADD(14) MB_ADD(13) MB_ADD(12) MB_ADD(11) MB_ADD(10) MB_ADD(9) MB_ADD(8) MB_ADD(7) MB_ADD(6) MB_ADD(5) MB_ADD(4) MB_ADD(3) MB_ADD(2) MB_ADD(1) MB_ADD(0) MB_DQS_H(7) MB_DQS_L(7) MB_DQS_H(6) MB_DQS_L(6) MB_DQS_H(5) MB_DQS_L(5) MB_DQS_H(4) MB_DQS_L(4) MB_DQS_H(3) MB_DQS_L(3) MB_DQS_H(2) MB_DQS_L(2) MB_DQS_H(1) MB_DQS_L(1) MB_DQS_H(0) MB_DQS_L(0) MB_DM(7) MB_DM(6) MB_DM(5) MB_DM(4) MB_DM(3) MB_DM(2) MB_DM(1) MB_DM(0) ZIF-SOCK940-RH-1

11,12 MEM_MB0_CS_L1 11,12 MEM_MB0_CS_L0 11,12 MEM_MB0_ODT0

11,12 MEM_MB_CAS_L 11,12 MEM_MB_WE_L 11,12 MEM_MB_RAS_L 11,12 MEM_MB_BANK2 11,12 MEM_MB_BANK1 11,12 MEM_MB_BANK0 12 MEM_MB_CKE1 11,12 MEM_MB_CKE0

MEM_MB_CAS_L MEM_MB_WE_L MEM_MB_RAS_L MEM_MB_BANK2 MEM_MB_BANK1 MEM_MB_BANK0 MEM_MB_CKE1 MEM_MB_CKE0 MEM_MB_ADD15 MEM_MB_ADD14 MEM_MB_ADD13 MEM_MB_ADD12 MEM_MB_ADD11 MEM_MB_ADD10 MEM_MB_ADD9 MEM_MB_ADD8 MEM_MB_ADD7 MEM_MB_ADD6 MEM_MB_ADD5 MEM_MB_ADD4 MEM_MB_ADD3 MEM_MB_ADD2 MEM_MB_ADD1 MEM_MB_ADD0 MEM_MB_DQS_H7 MEM_MB_DQS_L7 MEM_MB_DQS_H6 MEM_MB_DQS_L6 MEM_MB_DQS_H5 MEM_MB_DQS_L5 MEM_MB_DQS_H4 MEM_MB_DQS_L4 MEM_MB_DQS_H3 MEM_MB_DQS_L3 MEM_MB_DQS_H2 MEM_MB_DQS_L2 MEM_MB_DQS_H1 MEM_MB_DQS_L1 MEM_MB_DQS_H0 MEM_MB_DQS_L0 MEM_MB_DM7 MEM_MB_DM6 MEM_MB_DM5 MEM_MB_DM4 MEM_MB_DM3 MEM_MB_DM2 MEM_MB_DM1 MEM_MB_DM0

AC29 AC30 AB29 N31 AA31 AA28 M31 M29 N28 N29 AE31 N30 P29 AA29 P31 R29 R28 R31 R30 T31 T29 U29 U28 AA30 AK13 AJ13 AK17 AJ17 AK23 AL23 AL28 AL29 D31 C31 C24 C23 D17 C17 C14 C13 AJ14 AH17 AJ23 AK29 C30 A23 B17 B13

MB_DATA(63) MB_DATA(62) MB_DATA(61) MB_DATA(60) MB_DATA(59) MB_DATA(58) MB_DATA(57) MB_DATA(56) MB_DATA(55) MB_DATA(54) MB_DATA(53) MB_DATA(52) MB_DATA(51) MB_DATA(50) MB_DATA(49) MB_DATA(48) MB_DATA(47) MB_DATA(46) MB_DATA(45) MB_DATA(44) MB_DATA(43) MB_DATA(42) MB_DATA(41) MB_DATA(40) MB_DATA(39) MB_DATA(38) MB_DATA(37) MB_DATA(36) MB_DATA(35) MB_DATA(34) MB_DATA(33) MB_DATA(32) MB_DATA(31) MB_DATA(30) MB_DATA(29) MB_DATA(28) MB_DATA(27) MB_DATA(26) MB_DATA(25) MB_DATA(24) MB_DATA(23) MB_DATA(22) MB_DATA(21) MB_DATA(20) MB_DATA(19) MB_DATA(18) MB_DATA(17) MB_DATA(16) MB_DATA(15) MB_DATA(14) MB_DATA(13) MB_DATA(12) MB_DATA(11) MB_DATA(10) MB_DATA(9) MB_DATA(8) MB_DATA(7) MB_DATA(6) MB_DATA(5) MB_DATA(4) MB_DATA(3) MB_DATA(2) MB_DATA(1) MB_DATA(0) MB_DQS_H(8) MB_DQS_L(8) MB_DM(8) MB_CHECK(7) MB_CHECK(6) MB_CHECK(5) MB_CHECK(4) MB_CHECK(3) MB_CHECK(2) MB_CHECK(1) MB_CHECK(0)

AH13 AL13 AL15 AJ15 AF13 AG13 AL14 AK15 AL16 AL17 AK21 AL21 AH15 AJ16 AH19 AL20 AJ22 AL22 AL24 AK25 AJ21 AH21 AH23 AJ24 AL27 AK27 AH31 AG30 AL25 AL26 AJ30 AJ31 E31 E30 B27 A27 F29 F31 A29 A28 A25 A24 C22 D21 A26 B25 B23 A22 B21 A20 C16 D15 C21 A21 A17 A16 B15 A14 E13 F13 C15 A15 A13 D13 J31 J30 J29 K29 K31 G30 G29 L29 L28 H31 G31

MEM_MB_DATA63 MEM_MB_DATA62 MEM_MB_DATA61 MEM_MB_DATA60 MEM_MB_DATA59 MEM_MB_DATA58 MEM_MB_DATA57 MEM_MB_DATA56 MEM_MB_DATA55 MEM_MB_DATA54 MEM_MB_DATA53 MEM_MB_DATA52 MEM_MB_DATA51 MEM_MB_DATA50 MEM_MB_DATA49 MEM_MB_DATA48 MEM_MB_DATA47 MEM_MB_DATA46 MEM_MB_DATA45 MEM_MB_DATA44 MEM_MB_DATA43 MEM_MB_DATA42 MEM_MB_DATA41 MEM_MB_DATA40 MEM_MB_DATA39 MEM_MB_DATA38 MEM_MB_DATA37 MEM_MB_DATA36 MEM_MB_DATA35 MEM_MB_DATA34 MEM_MB_DATA33 MEM_MB_DATA32 MEM_MB_DATA31 MEM_MB_DATA30 MEM_MB_DATA29 MEM_MB_DATA28 MEM_MB_DATA27 MEM_MB_DATA26 MEM_MB_DATA25 MEM_MB_DATA24 MEM_MB_DATA23 MEM_MB_DATA22 MEM_MB_DATA21 MEM_MB_DATA20 MEM_MB_DATA19 MEM_MB_DATA18 MEM_MB_DATA17 MEM_MB_DATA16 MEM_MB_DATA15 MEM_MB_DATA14 MEM_MB_DATA13 MEM_MB_DATA12 MEM_MB_DATA11 MEM_MB_DATA10 MEM_MB_DATA9 MEM_MB_DATA8 MEM_MB_DATA7 MEM_MB_DATA6 MEM_MB_DATA5 MEM_MB_DATA4 MEM_MB_DATA3 MEM_MB_DATA2 MEM_MB_DATA1 MEM_MB_DATA0

C

B

A

A

Micro Star Restricted Secret

Title

Rev

K9 M2 DDR MEMORY I/F

MS-7549

Last Revision Date: Friday, November 07, 2008 Sheet of 9 38

1.1

Document Number

MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan https://www.doczj.com/doc/3e247924.html,

5 4 3 2 1

5

4

3

2

1

D

D

VCCP_NB VCCP CPU1F A4 A6 AA8 AA10 AA12 AA14 AA16 AA18 AB7 AB9 AB11 AC4 AC5 AC8 AC10 AD2 AD3 AD7 AD9 AE10 AF7 AF9 AG4 AG5 AG7 AH2 AH3 B3 B5 B7 C2 C4 C6 C8 D3 D5 D7 D9 E4 E6 E8 E10 F5 F7 F9 F11 G6 G8 G10 G12 H7 H11 H23 J8 J12 J14 J16 J18 J20 J22 J24 K7 K9 K11 K13 K15 K17 K19 K21 K23 L4 L5 L8 L10 L12 Y17 Y19 VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD ZIF-SOCK940-RH-1 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS A3 A7 A9 A11 AA4 AA5 AA7 AA9 AA11 AA13 AA15 AA17 AA19 AA21 AA23 AB2 AB3 AB8 AB10 AB12 AB14 AB16 AB18 AB20 AB22 AC7 AC9 AC11 AC13 AC15 AC17 AC19 AC21 AC23 AD8 AD10 AD12 AD14 AD16 AD20 AD22 AD24 AE4 AE5 AE9 AE11 AF2 AF3 AF8 AF10 AF12 AF14 AF16 AF18 AF20 AF22 AF24 AF26 AF28 AG10 AG11 AH14 AH16 AH18 AH20 AH22 AH24 AH26 AH28 AH30 AK2 AK14 AK16 AK18 Y14 Y16 VCCP L14 L16 L18 M2 M3 M7 M9 M11 M13 M15 M17 M19 N8 N10 N12 N14 N16 N18 P7 P9 P11 P13 P15 P17 P19 R4 R5 R8 R10 R12 R14 R16 R18 R20 T2 T3 T7 T9 T11 T13 T15 T17 T19 T21 U8 U10 U12 U14 U16 U18 U20 V9 V11 V13 V15 V17 V19 V21 W4 W5 W8 W10 W12 W14 W16 W18 W20 Y2 Y3 Y7 Y9 Y11 Y13 Y15 Y21 CPU1G VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD ZIF-SOCK940-RH-1 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS AK20 AK22 AK24 AK26 AK28 AK30 AL5 B4 B9 B11 B14 B16 B18 B20 B22 B24 B26 B28 B30 C3 D14 D16 D18 D20 D22 D24 D26 D28 D30 E11 F4 F14 F16 F18 F20 F22 F24 F26 F28 F30 G9 G11 H8 H10 H12 H14 H16 H18 H22 H24 H26 H28 H30 J4 J5 J7 J9 J11 J13 J15 J17 J19 J21 J23 K2 K3 K8 K10 K12 K14 K16 K18 K20 K22 Y18 AA20 AA22 AB13 AB15 AB17 AB19 AB21 AB23 AC12 AC14 AC16 AC18 AC20 AC22 AD11 AD23 AE12 AF11 L20 L22 M21 M23 N20 N22 P21 P23 R22 T23 U22 V23 W22 Y23 1 2 3 4 5 6 7 8 VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD 1 2 3 4 5 6 7 8 VCCP CPU1H VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS N17 N19 N21 N23 P2 P3 P8 P10 P12 P14 P16 P18 P20 P22 R7 R9 R11 R13 R15 R17 R19 R21 R23 T8 T10 T12 T14 T16 T18 T20 T22 U4 U5 U7 U9 U11 U13 U15 U17 U19 U21 U23 V2 V3 V10 V12 V14 V16 V18 V20 V22 W9 W11 W13 W15 W17 W19 W21 W23 Y8 Y10 Y12 W7 Y20 Y22 VCCA_1V2 AJ4 AJ3 AJ2 AJ1 D12 C12 B12 A12 AB24 AB26 AB28 AB30 AC24 AD26 AD28 AD30 AF30 M24 M26 M28 M30 P24 P26 P28 P30 T24 T26 T28 T30 V25 V26 V28 V30 Y24 Y26 Y28 Y29 CPU1I VLDT_A1 VLDT_A2 VLDT_A3 VLDT_A4 VTT VTT VTT VTT VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO VDDIO ZIF-SOCK940-RH-1 VLDT_B1 VLDT_B2 VLDT_B3 VLDT_B4 VTT VTT VTT VTT VTT VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS H6 H5 H2 H1 AK12 AJ12 AH12 AG12 AL12 K24 K26 K28 K30 L7 L9 L11 L13 L15 L17 L19 L21 L23 M8 M10 M12 M14 M16 M18 M20 M22 N4 N5 N7 N9 N11 N13 N15 VLDT_RUN_B VTT_DDR R174 C102 C101 C99 C100 X_0.01u/50v/Y5/6 L25 L26 L31 L30 W26 W25 AE27 U24 V24 AE28 Y31 Y30 AG31 V31 W31 AF31 CPU1E RSVD1 RSVD2 RSVD3 RSVD4 RSVD5 RSVD6 RSVD7 RSVD8 RSVD9 RSVD10 RSVD11 RSVD12 RSVD13 RSVD14 RSVD15 RSVD16 RSVD17 RSVD18 RSVD19 RSVD20 RSVD21 RSVD22 RSVD23 RSVD24 RSVD25 RSVD26 RSVD27 RSVD28 RSVD29 RSVD30 RSVD31 RSVD32 RSVD33 RSVD34 RSVD35 RSVD36 RSVD37 RSVD38 E20 B19 AL4 AK4 AK3 F2 F3 G4 G3 G5 AD25 AE24 AE25 AJ18 AJ20 C18 C20 G24 G25 H25 V29 W30 ALERT_L CPU_SA0 X_1KR0402 VCC_DDR

VTT_DDR

VCC_DDR

0.01u/50v/Y5/6 X_0.01u/50v/Y5/6 4.7u/10v/Y5/8

R173

0R0402

VCCP_NB

TP12

NB_VSEN NB_VSEN 6 NB_GND NB_GND 6 CPU_CORE_TYPE CPU_CORE_TYPE R122 300R0402VCC_DDR

6

C628 10p/16v/X7/6

C630

C639

C636 0.01u/50v/X7/6_B

VCCP_NB

10p/16v/X7/6 10p/16v/X7/6

C

C

VCCP_NB

C611

C618

C623 X_10u/10v/X5/8_B

C629 X_10u/10v/X5/8_B

ZIF-SOCK940-RH-1

X_22u/6.3v/X5/8 22u/6.3v/X5/8 VCCP

C109 22u/6.3v/X5/8_B

For EMI

VCC_DDR

C165 1000p/50v/N/4

C110

C179 1000p/50v/N/4

C107

C192 1000p/50v/N/4

C108

C117 1000p/50v/N/4

1000p/50v/N/4 VCCP

0.1u/25v/Y5/4

1000p/50v/N/4

BOTTOM

C614 0.22u/16v/X7/6_B C616 C619 C610 10p/16v/X7/6 C622

VCC_DDR VCCP

BOTTOM

C646 C625 X_2.2u/6.3v/X5/6_B

VCCP_NB

VCCP

B

ZIF-SOCK940-RH-1 C155 X_2.2u/6.3v/X5/6

B

10p/16v/X7/6 0.22u/16v/X7/6_B VCCP

180p/50v/N/4_B X_2.2u/6.3v/X5/6_B

BOTTOM

C612 C617 C624 C632 C634 C641 C613 C620 C626

N12-9400050-L06

10u/6.3/X5/0805 VTT_DDR VCC_DDR

C633

C10u6.3X50805-1 10u/10v/X5/8_B X_22u/6.3v/X5/8_B 22u/6.3v/X5/8_B VCC_DDR

X_10u/10v/X5/8_B X_10u/10v/X5/8_B 10u/10v/X5/8_B 10u/10v/X5/8_B 10u/10v/X5/8_B

BOTTOM

C199 C202 C186 C631 4.7u/10v/Y5/8_B C640 X_4.7u/10v/Y5/8_B 1 +

C194

C87

C183

C76

C188

C178

C47 C205 C635 C206 0.22u/16v/X7/6 X_220p/50v/N/4 1000p/50v/X7/6 X_1000p/50v/X7/6 1000p/50v/N/4 4.7u/10v/Y5/8 1000p/50v/N/4

X_0.22u/16v/X7/6 4.7u/10v/Y5/8 220p/50v/N/4 X_0.22u/16v/X7/6 220p/50v/N/4 X_4.7u/10v/Y5/8

2

EC13 X_1000u/6.3v/8x11.5/3.5mm

C621

C184

C615

C176

C627

C123

C124

C191

C207

10u/10v/X5/8_B X_4.7u/10v/Y5/8 0.22u/16v/X7/6 X_0.01u/50v/X7/6 1000p/50v/N/4 10u/10v/X5/8_B 4.7u/10v/Y5/8 1000p/50v/X7/6 X_10u/10v/X5/8_B

VTT_DDR

A

VCC_DDR C318

VCC3

A

X_0.01u/16v/X7/4 C219 X_0.22u/16v/X7/6 C91 C81 0.22u/16v/X7/6 4.7u/10v/Y5/8 C48 X_1000p/50v/X7/6

Micro Star Restricted Secret

Title

K9 M2 PWR & GND

MS-7549

Rev 1.1

Document Number

MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan https://www.doczj.com/doc/3e247924.html,

Last Revision Date: Tuesday, November 11, 2008 Sheet of 10 38

5

4

3

2

1

5

4

3

2

1

9 MEM_MA_DQS_H[7..0] 9 MEM_MA_DQS_L[7..0] 9 MEM_MA_DM[7..0] 9,12 MEM_MA_ADD[15..0] 9 MEM_MA_DATA[63..0]

MEM_MA_DQS_H[7..0] MEM_MA_DQS_L[7..0] MEM_MA_DM[7..0] MEM_MA_ADD[15..0] VCC3 MEM_MA_DATA[63..0]

9 MEM_MB_DQS_H[7..0] 9 MEM_MB_DQS_L[7..0] 9 MEM_MB_DM[7..0] 9,12 MEM_MB_ADD[15..0] 9 MEM_MB_DATA[63..0]

MEM_MB_DQS_H[7..0] MEM_MB_DQS_L[7..0] MEM_MB_DM[7..0] VCC3 MEM_MB_ADD[15..0] MEM_MB_DATA[63..0] VCC_DDR

VCC_DDR

D

C451 X_C0.1u16Y0402

C337 C0.1u16Y0402

D

55 18 19 102 68

51 56 62 72 75 78 191 194 181 175 170 53 59 64 197 69 172 187 184 178 189 67

238 VDDSPD

DIMM1

55 18 19 102 68

51 56 62 72 75 78 191 194 181 175 170 53 59 64 197 69 172 187 184 178 189 67

238

RC0 RC1 NC1 NC/TEST NC2

Y

C

MEM_MA_DATA0 MEM_MA_DATA1 MEM_MA_DATA2 MEM_MA_DATA3 MEM_MA_DATA4 MEM_MA_DATA5 MEM_MA_DATA6 MEM_MA_DATA7 MEM_MA_DATA8 MEM_MA_DATA9 MEM_MA_DATA10 MEM_MA_DATA11 MEM_MA_DATA12 MEM_MA_DATA13 MEM_MA_DATA14 MEM_MA_DATA15 MEM_MA_DATA16 MEM_MA_DATA17 MEM_MA_DATA18 MEM_MA_DATA19 MEM_MA_DATA20 MEM_MA_DATA21 MEM_MA_DATA22 MEM_MA_DATA23 MEM_MA_DATA24 MEM_MA_DATA25 MEM_MA_DATA26 MEM_MA_DATA27 MEM_MA_DATA28 MEM_MA_DATA29 MEM_MA_DATA30 MEM_MA_DATA31 MEM_MA_DATA32 MEM_MA_DATA33 MEM_MA_DATA34 MEM_MA_DATA35 MEM_MA_DATA36 MEM_MA_DATA37 MEM_MA_DATA38 MEM_MA_DATA39 MEM_MA_DATA40 MEM_MA_DATA41 MEM_MA_DATA42 MEM_MA_DATA43 MEM_MA_DATA44 MEM_MA_DATA45 MEM_MA_DATA46 MEM_MA_DATA47 MEM_MA_DATA48 MEM_MA_DATA49 MEM_MA_DATA50 MEM_MA_DATA51 MEM_MA_DATA52 MEM_MA_DATA53 MEM_MA_DATA54 MEM_MA_DATA55 MEM_MA_DATA56 MEM_MA_DATA57 MEM_MA_DATA58 MEM_MA_DATA59 MEM_MA_DATA60 MEM_MA_DATA61 MEM_MA_DATA62 MEM_MA_DATA63

3 4 9 10 122 123 128 129 12 13 21 22 131 132 140 141 24 25 30 31 143 144 149 150 33 34 39 40 152 153 158 159 80 81 86 87 199 200 205 206 89 90 95 96 208 209 214 215 98 99 107 108 217 218 226 227 110 111 116 117 229 230 235 236 2 5 8 11 14 17 20 23 26 29 32 35 38 41 44 47 50 65 66 79 82 85 88 91 94 97

DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 DQ16 DQ17 DQ18 DQ19 DQ20 DQ21 DQ22 DQ23 DQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31 DQ32 DQ33 DQ34 DQ35 DQ36 DQ37 DQ38 DQ39 DQ40 DQ41 DQ42 DQ43 DQ44 DQ45 DQ46 DQ47 DQ48 DQ49 DQ50 DQ51 DQ52 DQ53 DQ54 DQ55 DQ56 DQ57 DQ58 DQ59 DQ60 DQ61 DQ62 DQ63 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

DQS0 DQS0# DQS1 DQS1# DQS2 DQS2# DQS3 DQS3# DQS4 DQS4# DQS5 DQS5# DQS6 DQS6# DQS7 DQS7# DQS8 DQS8# A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10_AP A11 A12 A13 A14 A15 A16/BA2 BA1 BA0 WE# CAS# RAS# DM0/DQS9 NC/DQS9# DM1/DQS10 NC/DQS10# DM2/DQS11 NC/DQS11# DM3/DQS12 NC/DQS12# DM4/DQS13 NC/DQS13# DM5/DQS14 NC/DQS14# DM6/DQS15 NC/DQS15# DM7/DQS16 NC/DQS16# DM8/DQS17 NC/DQS17# ODT0 ODT1 CKE0 CKE1 CS0# CS1# CK0(DU) CK0#(DU) CK1(CK0) CK1#(CK0#) CK2(DU) CK2#(DU) SCL SDA VREF X1 SA0 SA1 SA2 X2 X3

7 6 16 15 28 27 37 36 84 83 93 92 105 104 114 113 46 45 188 183 63 182 61 60 180 58 179 177 70 57 176 196 174 173 54 190 71 73 74 192 125 126 134 135 146 147 155 156 202 203 211 212 223 224 232 233 164 165 195 77 52 171 193 76 185 186 137 138 220 221 120 119 1 X1 239 240 101 X2 X3

MEM_MA_DQS_H0 MEM_MA_DQS_L0 MEM_MA_DQS_H1 MEM_MA_DQS_L1 MEM_MA_DQS_H2 MEM_MA_DQS_L2 MEM_MA_DQS_H3 MEM_MA_DQS_L3 MEM_MA_DQS_H4 MEM_MA_DQS_L4 MEM_MA_DQS_H5 MEM_MA_DQS_L5 MEM_MA_DQS_H6 MEM_MA_DQS_L6 MEM_MA_DQS_H7 MEM_MA_DQS_L7 SCL0 MEM_MA_ADD0 MEM_MA_ADD1 MEM_MA_ADD2 MEM_MA_ADD3 MEM_MA_ADD4 MEM_MA_ADD5 MEM_MA_ADD6 MEM_MA_ADD7 MEM_MA_ADD8 MEM_MA_ADD9 MEM_MA_ADD10 MEM_MA_ADD11 MEM_MA_ADD12 MEM_MA_ADD13 MEM_MA_ADD14 MEM_MA_ADD15 MEM_MA_BANK2 MEM_MA_BANK1 MEM_MA_BANK0 MEM_MA_WE_L MEM_MA_CAS_L MEM_MA_RAS_L MEM_MA_BANK2 9,12 MEM_MA_BANK1 9,12 MEM_MA_BANK0 9,12 MEM_MA_WE_L 9,12 MEM_MA_CAS_L 9,12 MEM_MA_RAS_L 9,12 VCC_DDR

VCC3

Z

D18 X_1PS226_SOT23

VCC3

SDA0

Z

D17 X_1PS226_SOT23

VDDR_VREF

MEM_MA_DM0 MEM_MA_DM1 MEM_MA_DM2 MEM_MA_DM3 MEM_MA_DM4 MEM_MA_DM5 MEM_MA_DM6 MEM_MA_DM7 R86 15R1% VDDR_VREF X_0.1u/25v/Y5/4 C44 0.1u/25v/Y5/4 R84 15R1% C53

MEM_MB_DATA0 MEM_MB_DATA1 MEM_MB_DATA2 MEM_MB_DATA3 MEM_MB_DATA4 MEM_MB_DATA5 MEM_MB_DATA6 MEM_MB_DATA7 MEM_MB_DATA8 MEM_MB_DATA9 MEM_MB_DATA10 MEM_MB_DATA11 MEM_MB_DATA12 MEM_MB_DATA13 MEM_MB_DATA14 MEM_MB_DATA15 MEM_MB_DATA16 MEM_MB_DATA17 MEM_MB_DATA18 MEM_MB_DATA19 MEM_MB_DATA20 MEM_MB_DATA21 MEM_MB_DATA22 MEM_MB_DATA23 MEM_MB_DATA24 MEM_MB_DATA25 MEM_MB_DATA26 MEM_MB_DATA27 MEM_MB_DATA28 MEM_MB_DATA29 MEM_MB_DATA30 MEM_MB_DATA31 MEM_MB_DATA32 MEM_MB_DATA33 MEM_MB_DATA34 MEM_MB_DATA35 MEM_MB_DATA36 MEM_MB_DATA37 MEM_MB_DATA38 MEM_MB_DATA39 MEM_MB_DATA40 MEM_MB_DATA41 MEM_MB_DATA42 MEM_MB_DATA43 MEM_MB_DATA44 MEM_MB_DATA45 MEM_MB_DATA46 MEM_MB_DATA47 MEM_MB_DATA48 MEM_MB_DATA49 MEM_MB_DATA50 MEM_MB_DATA51 MEM_MB_DATA52 MEM_MB_DATA53 MEM_MB_DATA54 MEM_MB_DATA55 MEM_MB_DATA56 MEM_MB_DATA57 MEM_MB_DATA58 MEM_MB_DATA59 MEM_MB_DATA60 MEM_MB_DATA61 MEM_MB_DATA62 MEM_MB_DATA63

3 4 9 10 122 123 128 129 12 13 21 22 131 132 140 141 24 25 30 31 143 144 149 150 33 34 39 40 152 153 158 159 80 81 86 87 199 200 205 206 89 90 95 96 208 209 214 215 98 99 107 108 217 218 226 227 110 111 116 117 229 230 235 236 2 5 8 11 14 17 20 23 26 29 32 35 38 41 44 47 50 65 66 79 82 85 88 91 94 97

DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 DQ16 DQ17 DQ18 DQ19 DQ20 DQ21 DQ22 DQ23 DQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31 DQ32 DQ33 DQ34 DQ35 DQ36 DQ37 DQ38 DQ39 DQ40 DQ41 DQ42 DQ43 DQ44 DQ45 DQ46 DQ47 DQ48 DQ49 DQ50 DQ51 DQ52 DQ53 DQ54 DQ55 DQ56 DQ57 DQ58 DQ59 DQ60 DQ61 DQ62 DQ63 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ

CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7

DIMM2

42 43 48 49 161 162 167 168

42 43 48 49 161 162 167 168

DQS0 DQS0# DQS1 DQS1# DQS2 DQS2# DQS3 DQS3# DQS4 DQS4# DQS5 DQS5# DQS6 DQS6# DQS7 DQS7# DQS8 DQS8# A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10_AP A11 A12 A13 A14 A15 A16/BA2 BA1 BA0 WE# CAS# RAS# DM0/DQS9 NC/DQS9# DM1/DQS10 NC/DQS10# DM2/DQS11 NC/DQS11# DM3/DQS12 NC/DQS12# DM4/DQS13 NC/DQS13# DM5/DQS14 NC/DQS14# DM6/DQS15 NC/DQS15# DM7/DQS16 NC/DQS16# DM8/DQS17 NC/DQS17# ODT0 ODT1 CKE0 CKE1 CS0# CS1# CK0(DU) CK0#(DU) CK1(CK0) CK1#(CK0#) CK2(DU) CK2#(DU) SCL SDA VREF X1 SA0 SA1 SA2 X2 X3

7 6 16 15 28 27 37 36 84 83 93 92 105 104 114 113 46 45 188 183 63 182 61 60 180 58 179 177 70 57 176 196 174 173 54 190 71 73 74 192 125 126 134 135 146 147 155 156 202 203 211 212 223 224 232 233 164 165 195 77 52 171 193 76 185 186 137 138 220 221 120 119 1 X1 239 240 101 X2 X3

Y

MEM_MB_DQS_H0 MEM_MB_DQS_L0 MEM_MB_DQS_H1 MEM_MB_DQS_L1 MEM_MB_DQS_H2 MEM_MB_DQS_L2 MEM_MB_DQS_H3 MEM_MB_DQS_L3 MEM_MB_DQS_H4 MEM_MB_DQS_L4 MEM_MB_DQS_H5 MEM_MB_DQS_L5 MEM_MB_DQS_H6 MEM_MB_DQS_L6 MEM_MB_DQS_H7 MEM_MB_DQS_L7

RC0 RC1 NC1 NC/TEST NC2

VDD VDD VDD VDD VDD VDD VDD VDD VDD VDD VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ VDDQ

VDDSPD

CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7

MEM_MB_ADD0 MEM_MB_ADD1 MEM_MB_ADD2 MEM_MB_ADD3 MEM_MB_ADD4 MEM_MB_ADD5 MEM_MB_ADD6 MEM_MB_ADD7 MEM_MB_ADD8 MEM_MB_ADD9 MEM_MB_ADD10 MEM_MB_ADD11 MEM_MB_ADD12 MEM_MB_ADD13 MEM_MB_ADD14 MEM_MB_ADD15 MEM_MB_BANK2 MEM_MB_BANK1 MEM_MB_BANK0 MEM_MB_WE_L MEM_MB_CAS_L MEM_MB_RAS_L MEM_MB_BANK2 9,12 MEM_MB_BANK1 9,12 MEM_MB_BANK0 9,12 MEM_MB_WE_L 9,12 MEM_MB_CAS_L 9,12 MEM_MB_RAS_L 9,12

X

C

X

MEM_MB_DM0 MEM_MB_DM1 MEM_MB_DM2 MEM_MB_DM3 MEM_MB_DM4 MEM_MB_DM5 MEM_MB_DM6 MEM_MB_DM7

MEM_MB0_ODT0 MEM_MB_CKE0 MEM_MB0_CS_L0 MEM_MB0_CS_L1 MEM_MB0_CLK_H0 MEM_MB0_CLK_L0 MEM_MB0_CLK_H1 MEM_MB0_CLK_L1 MEM_MB0_CLK_H2 MEM_MB0_CLK_L2 SCL0 SDA0

MEM_MB0_ODT0 9,12 MEM_MB_CKE0 9,12 MEM_MB0_CS_L0 9,12 MEM_MB0_CS_L1 9,12 MEM_MB0_CLK_H0 MEM_MB0_CLK_L0 MEM_MB0_CLK_H1 MEM_MB0_CLK_L1 MEM_MB0_CLK_H2 MEM_MB0_CLK_L2 SCL0 SDA0 VDDR_VREF 9,12 9,12 9,12 9,12 9,12 9,12 6,7,20,33 6,7,20,33

B

MEM_MA0_ODT0 MEM_MA_CKE0 MEM_MA0_CS_L0 MEM_MA0_CS_L1 MEM_MA0_CLK_H0 MEM_MA0_CLK_L0 MEM_MA0_CLK_H1 MEM_MA0_CLK_L1 MEM_MA0_CLK_H2 MEM_MA0_CLK_L2 SCL0 SDA0 VDDR_VREF

MEM_MA0_ODT0 9,12 MEM_MA_CKE0 9,12 MEM_MA0_CS_L0 9,12 MEM_MA0_CS_L1 9,12 MEM_MA0_CLK_H0 MEM_MA0_CLK_L0 MEM_MA0_CLK_H1 MEM_MA0_CLK_L1 MEM_MA0_CLK_H2 MEM_MA0_CLK_L2 9,12 9,12 9,12 9,12 9,12 9,12

B

SCL0 6,7,20,33 SDA0 VDDR_VREF 6,7,20,33

VDDR_VREF VCC3 C45 C0.1u16Y0402

VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS 100 103 106 109 112 115 118 121 124 127 130 133 136 139 142 145 148 151 154 157 160 163 166 169 198 201 204 207 210 213 216 219 222 225 228 231 234 237

C54 C0.1u16Y0402

DDRII-240_ORANGE-RH

100 103 106 109 112 115 118 121 124 127 130 133 136 139 142 145 148 151 154 157 160 163 166 169 198 201 204 207 210 213 216 219 222 225 228 231 234 237

DDRII-240_ORANG-RH

A

ADDRESS

A0

ADDRESS

A2

Micro Star Restricted Secret

Title

Rev

FIRST LOGICAL DDR DIMM

MS-7549

Last Revision Date: Friday, November 07, 2008 Sheet of 11 38

1.1

A

Document Number

MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan https://www.doczj.com/doc/3e247924.html,

5

4

3

2

1

5

4

3

2

1

VCC_DDR VTT_DDR 9,11 MEM_MA0_CLK_H2 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 9,11 MEM_MB_ADD11 MEM_MA_ADD12 MEM_MA_ADD11 MEM_MA_ADD9 MEM_MA_ADD14 MEM_MA_ADD15 MEM_MB_ADD12 MEM_MB_ADD9 MEM_MA_ADD7 MEM_MB_ADD7 MEM_MB_ADD8 MEM_MA_ADD8 MEM_MB_ADD0 MEM_MB_BANK1 MEM_MB_ADD10 MEM_MB_BANK0 MEM_MB_ADD3 MEM_MA_ADD2 MEM_MB_ADD1 MEM_MB_ADD2 MEM_MA0_CS_L0 MEM_MA_CAS_L MEM_MB_WE_L MEM_MA0_ODT0 MEM_MB_ADD11 MEM_MA_ADD12 MEM_MA_ADD11 MEM_MA_ADD9 MEM_MA_ADD14 MEM_MA_ADD15 MEM_MB_ADD12 MEM_MB_ADD9 MEM_MA_ADD7 MEM_MB_ADD7 MEM_MB_ADD8 MEM_MA_ADD8 MEM_MB_ADD0 MEM_MB_BANK1 MEM_MB_ADD10 MEM_MB_BANK0 MEM_MB_ADD3 MEM_MA_ADD2 MEM_MB_ADD1 MEM_MB_ADD2 RN10 1 3 5 7 RN9 1 3 5 7 RN11 1 3 5 7 RN15 1 3 5 7 RN14 1 3 5 7 MEM_MA0_CLK_H2 C193 C1.5p50N0402 MEM_MA_ADD15 MEM_MA_ADD14 MEM_MA_ADD13 MEM_MA_ADD12 MEM_MA_ADD11 MEM_MA_ADD10 MEM_MA_ADD9 MEM_MA_ADD8 MEM_MA_ADD7 MEM_MA_ADD6 MEM_MA_ADD5 MEM_MA_ADD4 MEM_MA_ADD3 MEM_MA_ADD2 MEM_MA_ADD1 MEM_MA_ADD0 C638 C637 C662 C642 C644 C656 C645 C647 C648 C650 C649 C652 C651 C653 C654 C655 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 MEM_MB_ADD15 MEM_MB_ADD14 MEM_MB_ADD13 MEM_MB_ADD12 MEM_MB_ADD11 MEM_MB_ADD10 MEM_MB_ADD9 MEM_MB_ADD8 MEM_MB_ADD7 MEM_MB_ADD6 MEM_MB_ADD5 MEM_MB_ADD4 MEM_MB_ADD3 MEM_MB_ADD2 MEM_MB_ADD1 MEM_MB_ADD0 MEM_MB_CAS_L MEM_MB_WE_L MEM_MB_RAS_L MEM_MB_BANK2 MEM_MB_BANK1 MEM_MB_BANK0 C121 C122 C174 C126 C131 C159 C130 C137 C136 C141 C142 C148 C149 C151 C150 C156 C169 C168 C163 C125 C158 C162

VCC_DDR X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402 X_C22p50N0402

D

2 4 6 8 2 4 6 8 2 4 6 8 2 4 6 8

8P4R-47R0402 MEM_MA0_CLK_L2 MEM_MA0_CLK_H1 C86 C1.5p50N0402

8P4R-47R0402

9,11 MEM_MA0_CLK_L2 9,11 MEM_MA0_CLK_H1

8P4R-47R0402 MEM_MA0_CLK_L1 MEM_MA0_CLK_H0 C140 C1.5p50N0402

D

8P4R-47R0402

9,11 MEM_MA0_CLK_L1 9,11 MEM_MA0_CLK_H0

2 8P4R-47R0402 4 6 8 2 8P4R-47R0402 4 6 8 2 8P4R-47R0402 4 6 8

MEM_MA_CAS_L C660 MEM_MA_WE_L C661 MEM_MA_RAS_L C658 MEM_MA_BANK2 C643 MEM_MA_BANK1 C657 MEM_MA_BANK0 C659

9,11 MEM_MA0_CLK_L0 9,11 MEM_MB0_CLK_H2

MEM_MA0_CLK_L0 MEM_MB0_CLK_H2

MEM_MA0_CS_L0 RN19 MEM_MA_CAS_L MEM_MB_WE_L MEM_MA0_ODT0

1 3 5 7

9,11 MEM_MB0_ODT0 9,11 MEM_MB_ADD13 9,11 MEM_MB0_CS_L1

RN21 1 MEM_MB0_ODT0 3 MEM_MB_ADD13 5 MEM_MB0_CS_L1 7

9,11 MEM_MB0_CLK_L2 9,11 MEM_MB0_CLK_H1

MEM_MB0_CLK_L2 MEM_MB0_CLK_H1

C190 C1.5p50N0402

Decoupling Between Processor and DIMMs

C

9,11 MEM_MB0_CLK_L1 9,11 MEM_MB0_CLK_H0

MEM_MB0_CLK_L1 MEM_MB0_CLK_H0

C80 C1.5p50N0402

C

9,11 MEM_MB0_CLK_L0

MEM_MB0_CLK_L0

C133 C1.5p50N0402 VTT_DDR

Layout: Spread out on VTT pour

EMI

C0.1u25Y0402-RH C135 C212 C201 C132 C228 C227 C0.1u25Y0402-RH C203 C196 C215 C22P50Y0402-RH C233 C225 C224 X_C0.1u25Y0402-RH X_C0.1u25Y0402-RH C164 C211 C229

X_C0.1u25Y0402-RH 220p50Y0402-RH C22P50Y0402-RH

220p50Y0402-RH C0.1u25Y0402-RH

C22P50Y0402-RH X_C0.1u25Y0402-RH

X_C0.1u25Y0402-RH C0.1u25Y0402-RH

C0.1u25Y0402-RH

VTT_DDR VTT_DDR 9 MEM_MB_CKE1 9,11 MEM_MB_CKE0 9,11 MEM_MB_ADD15 9,11 MEM_MB_ADD14 9,11 MEM_MA_ADD5 9,11 MEM_MB_ADD6 9,11 MEM_MA_ADD6 9,11 MEM_MB_ADD5 9,11 MEM_MA_ADD4 9,11 MEM_MA_ADD3 9,11 MEM_MA_ADD1 9,11 MEM_MB_ADD4 9,11 MEM_MA_ADD0 9,11 MEM_MA_ADD10 9,11 MEM_MA_BANK0 9,11 MEM_MA_BANK1 9,11 9,11 9,11 9,11 MEM_MB_RAS_L MEM_MB0_CS_L0 MEM_MA_RAS_L MEM_MA_WE_L MEM_MB_CKE1 MEM_MB_CKE0 MEM_MB_ADD15 MEM_MB_ADD14 MEM_MA_ADD5 MEM_MB_ADD6 MEM_MA_ADD6 MEM_MB_ADD5 MEM_MA_ADD4 MEM_MA_ADD3 MEM_MA_ADD1 MEM_MB_ADD4 MEM_MA_ADD0 MEM_MA_ADD10 MEM_MA_BANK0 MEM_MA_BANK1 MEM_MB_RAS_L MEM_MB0_CS_L0 MEM_MA_RAS_L MEM_MA_WE_L MEM_MB_BANK2 MEM_MA_CKE1 MEM_MA_CKE0 MEM_MA_BANK2 MEM_MB_CAS_L MEM_MA_ADD13 MEM_MA0_CS_L1 RN7

B

1 3 5 7 RN12 1 3 5 7 RN13 1 3 5 7 RN16 1 3 5 7

RN17 1 3 5 7 RN8

2 4 6 8 2 4 6 8 2 4 6 8 2 4 6 8

8P4R-47R0402

8P4R-47R0402

C175

C171

C182

C217

C143

C208

C197

C221 X_C0.1u25Y0402-RH

B

8P4R-47R0402

X_C0.1u25Y0402-RH C0.1u25Y0402-RH C0.1u25Y0402-RH X_C0.1u25Y0402-RH C0.1u25Y0402-RH C0.1u25Y0402-RH X_C0.1u25Y0402-RH

8P4R-47R0402 VTT_DDR VCC_DDR

2 8P4R-47R0402 4 6 8 2 8P4R-47R0402 4 6 8 2 8P4R-47R0402 4 6 8

C216

C139

C127

C167

C200

C209

C177

C223

FOR EMI 07/17

X_C0.1u25Y0402-RH X_C0.1u25Y0402-RH X_C0.1u25Y0402-RH X_C0.1u25Y0402-RH C0.1u25Y0402-RH X_C0.1u25Y0402-RH C0.1u25Y0402-RH X_C0.1u25Y0402-RH VCC_DDR

9,11 MEM_MB_BANK2 9 MEM_MA_CKE1 9,11 MEM_MA_CKE0 9,11 MEM_MA_BANK2

1 3 5 7

9,11 MEM_MB_CAS_L 9,11 MEM_MA_ADD13

A

9,11 MEM_MA0_CS_L1

RN20 1 3 5 7

C680

C681

C682

C683

C684

C685

C686

C687

C688

C689

C690

C691

C693

C692

C694

C695

A

X_C0.1u25Y0402-RH 220p50Y0402-RH 220p50Y0402-RH X_C0.1u25Y0402-RH X_C0.1u25Y0402-RH X_C0.1u25Y0402-RH X_C0.1u25Y0402-RH 220p50Y0402-RH X_C0.1u25Y0402-RH 220p50Y0402-RH X_C0.1u25Y0402-RH 220p50Y0402-RH 220p50Y0402-RH X_C0.1u25Y0402-RH X_C0.1u25Y0402-RH 220p50Y0402-RH

Micro Star Restricted Secret

Title

Rev

DDR Terminatior

MS-7549

1.1

Document Number

MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan https://www.doczj.com/doc/3e247924.html,

5 4 3 2 1

Last Revision Date: Tuesday, November 11, 2008 Sheet of 12 38

5

4

3

2

1

D

D

8 HT_CADOUT_H[15..0] 8 HT_CADOUT_L[15..0]

HT_CADOUT_H[15..0] HT_CADOUT_L[15..0]

8 HT_CADIN_H[15..0] 8 HT_CADIN_L[15..0]

HT_CADIN_H[15..0] HT_CADIN_L[15..0]

20 / 5 / 5 / 5 / 20

HT_CADOUT_H0 HT_CADOUT_L0 HT_CADOUT_H1 HT_CADOUT_L1 HT_CADOUT_H2 HT_CADOUT_L2 HT_CADOUT_H3 HT_CADOUT_L3 HT_CADOUT_H4 HT_CADOUT_L4 HT_CADOUT_H5 HT_CADOUT_L5 HT_CADOUT_H6 HT_CADOUT_L6 HT_CADOUT_H7 HT_CADOUT_L7 HT_CADOUT_H8 HT_CADOUT_L8 HT_CADOUT_H9 HT_CADOUT_L9 HT_CADOUT_H10 HT_CADOUT_L10 HT_CADOUT_H11 HT_CADOUT_L11 HT_CADOUT_H12 HT_CADOUT_L12 HT_CADOUT_H13 HT_CADOUT_L13 HT_CADOUT_H14 HT_CADOUT_L14 HT_CADOUT_H15 HT_CADOUT_L15 8 8 8 8 8 8 8 8 HT_CLKOUT_H0 HT_CLKOUT_L0 HT_CLKOUT_H1 HT_CLKOUT_L1 HT_CTLOUT_H0 HT_CTLOUT_L0 HT_CTLOUT_H1 HT_CTLOUT_L1 301R1%0402 R197 HT_RXCALP HT_RXCALN

U15A

20 / 5 / 5 / 5 / 20

HS_NB

HYPER TRANSPORT CPU I/F

2

MSI DDR

NB_HEATSINK

1

C

Y25 Y24 V22 V23 V25 V24 U24 U25 T25 T24 P22 P23 P25 P24 N24 N25 AC24 AC25 AB25 AB24 AA24 AA25 Y22 Y23 W21 W20 V21 V20 U20 U21 U19 U18 T22 T23 AB23 AA22 M22 M23 R21 R20 C23 A24

HT_RXCAD0P HT_RXCAD0N HT_RXCAD1P HT_RXCAD1N HT_RXCAD2P HT_RXCAD2N HT_RXCAD3P HT_RXCAD3N HT_RXCAD4P HT_RXCAD4N HT_RXCAD5P HT_RXCAD5N HT_RXCAD6P HT_RXCAD6N HT_RXCAD7P HT_RXCAD7N

PART 1 OF 6

HT_TXCAD0P HT_TXCAD0N HT_TXCAD1P HT_TXCAD1N HT_TXCAD2P HT_TXCAD2N HT_TXCAD3P HT_TXCAD3N HT_TXCAD4P HT_TXCAD4N HT_TXCAD5P HT_TXCAD5N HT_TXCAD6P HT_TXCAD6N HT_TXCAD7P HT_TXCAD7N HT_TXCAD8P HT_TXCAD8N HT_TXCAD9P HT_TXCAD9N HT_TXCAD10P HT_TXCAD10N HT_TXCAD11P HT_TXCAD11N HT_TXCAD12P HT_TXCAD12N HT_TXCAD13P HT_TXCAD13N HT_TXCAD14P HT_TXCAD14N HT_TXCAD15P HT_TXCAD15N HT_TXCLK0P HT_TXCLK0N HT_TXCLK1P HT_TXCLK1N HT_TXCTL0P HT_TXCTL0N HT_TXCTL1P HT_TXCTL1N HT_TXCALP HT_TXCALN

D24 D25 E24 E25 F24 F25 F23 F22 H23 H22 J25 J24 K24 K25 K23 K22 F21 G21 G20 H21 J20 J21 J18 K17 L19 J19 M19 L18 M21 P21 P18 M18 H24 H25 L21 L20 M24 M25 P19 R18 B24 B25

HT_CADIN_H0 HT_CADIN_L0 HT_CADIN_H1 HT_CADIN_L1 HT_CADIN_H2 HT_CADIN_L2 HT_CADIN_H3 HT_CADIN_L3 HT_CADIN_H4 HT_CADIN_L4 HT_CADIN_H5 HT_CADIN_L5 HT_CADIN_H6 HT_CADIN_L6 HT_CADIN_H7 HT_CADIN_L7 HT_CADIN_H8 HT_CADIN_L8 HT_CADIN_H9 HT_CADIN_L9 HT_CADIN_H10 HT_CADIN_L10 HT_CADIN_H11 HT_CADIN_L11 HT_CADIN_H12 HT_CADIN_L12 HT_CADIN_H13 HT_CADIN_L13 HT_CADIN_H14 HT_CADIN_L14 HT_CADIN_H15 HT_CADIN_L15 HT_CLKIN_H0 HT_CLKIN_L0 HT_CLKIN_H1 HT_CLKIN_L1 HT_CTLIN_H0 HT_CTLIN_L0 HT_CTLIN_H1 HT_CTLIN_L1 HT_TXCALP HT_TXCALN 301R1%0402 R198 8 8 8 8 8 8 8 8

RS780V

OPT

X_RS780V

RS760G

OPT

X_RS760G

C

HT_RXCAD8P HT_RXCAD8N HT_RXCAD9P HT_RXCAD9N HT_RXCAD10P HT_RXCAD10N HT_RXCAD11P HT_RXCAD11N HT_RXCAD12P HT_RXCAD12N HT_RXCAD13P HT_RXCAD13N HT_RXCAD14P HT_RXCAD14N HT_RXCAD15P HT_RXCAD15N HT_RXCLK0P HT_RXCLK0N HT_RXCLK1P HT_RXCLK1N HT_RXCTL0P HT_RXCTL0N HT_RXCTL1P HT_RXCTL1N HT_RXCALP HT_RXCALN

B

B

5 / 10

AMD-215-0674007-00-A01-RH

5 / 10

Check U10 New Version : Port Number

RX780/RS740/RS780 difference table (HT LINK)

SIGNALS VCCP HT_RXCALP HT_RXCALN HT_TXCALP 100R C96 X_C0.01u16X0402 C93 X_C0.01u16X0402 HT_TXCALN 1.21K 301R RS740 49.9R (GND) 1.21K 49.9R (VDDHT) 301R RX780 RS780

A

Adding some 0.01僴uF stitching capacitors for crossing a split when these signals change different reference layer.

Title

A

MICRO-STAR INt'L CO., LTD. RS780-HT L

Size Date: Document Number

MS-7549

Tuesday, November 11, 2008

1

Rev 1.1 13 of 38

Sheet

5

4

3

2

5

4

3

2

1

20 / 5.5 / 4.5 / 5.5 / 20

23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 27 27 GFX_RX0P GFX_RX0N GFX_RX1P GFX_RX1N GFX_RX2P GFX_RX2N GFX_RX3P GFX_RX3N GFX_RX4P GFX_RX4N GFX_RX5P GFX_RX5N GFX_RX6P GFX_RX6N GFX_RX7P GFX_RX7N GFX_RX8P GFX_RX8N GFX_RX9P GFX_RX9N GFX_RX10P GFX_RX10N GFX_RX11P GFX_RX11N GFX_RX12P GFX_RX12N GFX_RX13P GFX_RX13N GFX_RX14P GFX_RX14N GFX_RX15P GFX_RX15N PE0_RX PE0_RX# RX_LANP1 RX_LANN1 D4 C4 A3 B3 C2 C1 E5 F5 G5 G6 H5 H6 J6 J5 J7 J8 L5 L6 M8 L8 P7 M7 P5 M5 R8 P8 R6 R5 P4 P3 T4 T3 AE3 AD4 AE2 AD3 AD1 AD2 V5 W6 U5 U6 U8 U7 A_RX0P A_RX0N A_RX1P A_RX1N A_RX2P A_RX2N A_RX3P A_RX3N AA8 Y8 AA7 Y7 AA5 AA6 W5 Y5

U15B GFX_RX0P GFX_RX0N GFX_RX1P GFX_RX1N GFX_RX2P GFX_RX2N GFX_RX3P GFX_RX3N GFX_RX4P GFX_RX4N GFX_RX5P GFX_RX5N GFX_RX6P GFX_RX6N GFX_RX7P GFX_RX7N GFX_RX8P GFX_RX8N GFX_RX9P GFX_RX9N GFX_RX10P GFX_RX10N GFX_RX11P GFX_RX11N GFX_RX12P GFX_RX12N GFX_RX13P GFX_RX13N GFX_RX14P GFX_RX14N GFX_RX15P GFX_RX15N GPP_RX0P GPP_RX0N GPP_RX1P GPP_RX1N GPP_RX2P GPP_RX2N GPP_RX3P GPP_RX3N GPP_RX4P GPP_RX4N GPP_RX5P GPP_RX5N SB_RX0P SB_RX0N SB_RX1P SB_RX1N SB_RX2P SB_RX2N SB_RX3P SB_RX3N

20 / 5.5 / 4.5 / 5.5 / 20 PART 2 OF 6

GFX_TX0P GFX_TX0N GFX_TX1P GFX_TX1N GFX_TX2P GFX_TX2N GFX_TX3P GFX_TX3N GFX_TX4P GFX_TX4N GFX_TX5P GFX_TX5N GFX_TX6P GFX_TX6N GFX_TX7P GFX_TX7N GFX_TX8P GFX_TX8N GFX_TX9P GFX_TX9N GFX_TX10P GFX_TX10N GFX_TX11P GFX_TX11N GFX_TX12P GFX_TX12N GFX_TX13P GFX_TX13N GFX_TX14P GFX_TX14N GFX_TX15P GFX_TX15N GPP_TX0P GPP_TX0N GPP_TX1P GPP_TX1N GPP_TX2P GPP_TX2N GPP_TX3P GPP_TX3N GPP_TX4P GPP_TX4N GPP_TX5P GPP_TX5N SB_TX0P SB_TX0N SB_TX1P SB_TX1N SB_TX2P SB_TX2N SB_TX3P SB_TX3N PCE_CALRP PCE_CALRN A5 B5 A4 B4 C3 B2 D1 D2 E2 E1 F4 F3 F1 F2 H4 H3 H1 H2 J2 J1 K4 K3 K1 K2 M4 M3 M1 M2 N2 N1 P1 P2 AC1 AC2 AB4 AB3 AA2 AA1 Y1 Y2 Y4 Y3 V1 V2 AD7 AE7 AE6 AD6 AB6 AC6 AD5 AE5 AC8 AB8 PE0_TXP PE0_TXN TX_LANP1 TX_LANN1 GFX_TX0P GFX_TX0N GFX_TX1P GFX_TX1N GFX_TX2P GFX_TX2N GFX_TX3P GFX_TX3N GFX_TX4P GFX_TX4N GFX_TX5P GFX_TX5N GFX_TX6P GFX_TX6N GFX_TX7P GFX_TX7N GFX_TX8P GFX_TX8N GFX_TX9P GFX_TX9N GFX_TX10P GFX_TX10N GFX_TX11P GFX_TX11N GFX_TX12P GFX_TX12N GFX_TX13P GFX_TX13N GFX_TX14P GFX_TX14N GFX_TX15P GFX_TX15N 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 23 PE0_TX PE0_TX# TXLANP1 TXLANN1 23 23 27 27

D

D

C

PCIE I/F GFX

C

C379 C378

C0.1u10x0402 C0.1u10x0402

PCIE I/F GPP

18 18 18 18 18 18 18 18

A_RX0P A_RX0N A_RX1P A_RX1N A_RX2P A_RX2N A_RX3P A_RX3N

PCIE I/F SB

A_TX0P_C A_TX0N_C A_TX1P_C A_TX1N_C A_TX2P_C A_TX2N_C A_TX3P_C A_TX3N_C R258 R252

C328 C326 C370 C372 C336 C345 C375 C376

X7R

C0.1u10X0402 C0.1u10X0402 C0.1u10X0402 C0.1u10X0402 C0.1u10X0402 C0.1u10X0402 C0.1u10X0402 C0.1u10X0402 VCC1_1

A_TX0P A_TX0N A_TX1P A_TX1N A_TX2P A_TX2N A_TX3P A_TX3N

18 18 18 18 18 18 18 18

1.27KR1%0402 2KR1%0402

B

AMD-215-0674007-00-A01-RH

B

1.2V (RS740) 1.1V(RS780)

RX780/RS740/RS780 GPP difference table

RS740 PCE_CALRP GPP4 GPP5 562R (GND) NC NC RX780/RS780 1.27K (GND) GPP4 GPP5 GPP X4 CONNECTOR GPP X1 CONNECTOR GIGABIT ETHERNET GPP3

RX780/RS740/RS780 GPP Routing table

RS740 GPP[2:0] RX780/RS780 GPP[3:0] GPP4 GPP5

RS780 Display Port Support (muxed on GFX)

GFX_TX0,TX1,TX2 and TX3 DP0 AUX0 and HPD0 GFX_TX4,TX5,TX6 and TX7 DP1 AUX1 and HPD1

A A

MICRO-STAR INt'L CO., LTD.

Title

RS780-PCIE I/F

Size Date:

5 4 3 2

Document Number

MS-7549

Tuesday, November 11, 2008 Sheet

1

Rev 1.1 14 of 38

5

4

3

2

1

+1.8V_S0

SPEC. HI:0.7VCC LOW:0.3VCC

3VDUAL VCC3 R265 4.7KR0402 Y1 VCC Y2 6 5 4 NB_PWRGD_IN NB_PWRGD_IN must have a pull-up resister to +1.8V_S0 due to NC7W207 output pin is op-drain 3VDUAL +1.8V_S0 FB9 220L2A-50

ANALOG POWER X5R

AVDD C283 C4.7u6.3X5 C289 C698 C0.1u16Y0402 C1u16Y0402 AVDDI

U17 33 SYS_PWRGD 1 2 3 A1 GND A2

15 MILS WIDTH

R208 For meet power sequence +1.8V_S0 FB8 SB_PWRGD 20

0R

15 MILS WIDTH

U15C C696 C0.1u25Y5 F12 E12 F14 G15 H15 H14 E17 F17 F15 G18 G17 E18 F18 E19 F19 A11 B11 F8 E8 715R1%0402 R221 DAC_RSET G14 RS780 PLLVDD A12 PLLVDD18 D14 B12 VDDA18HTPLL VDDA18PCIEPLL SYSRESET# NB_PWRGD_IN LDT_STOP#_NB ALLOW_LDTSTOP HTREFCLK HTREFCLK# H17 D7 E7 D8 A10 C10 C12 C25 C24 E11 F11 T2 T1 A22 B22 A21 B21 B20 A20 A19 B19 B18 A18 A17 B17 D20 D21 D18 D19 B16 A16 D16 D17 VDDLTP18 VDDLTP18 VSSLTP18 A13 B13 A15 B15 A14 B14 C14 D15 C16 C18 C20 E20 C22 TXD00P TXD00N TXD01P TXD01N TXD02P TXD02N TXD10P_R TXD10N_R TXD11P_R TXD11N_R TXD12P_R TXD12N_R

X_NC7WZ07P6X_SC70-6

C268 C2.2u6.3X5 AVDDQ C273 C276 C0.1u16Y0402

D

33 SYS_PWRGD

R287

0R0402

SB_PWRGD R291 X_4.7KR0402

15 MILS WIDTH

C697 C1u16Y0402

20 WD_PWRGD

R264

0R0402

NB_PWRGD_IN

220L2A-50

AVDD AVDD AVDDDI AVSSDI AVDDQ AVSSQ C Y COMP RED RED# GREEN GREEN# BLUE BLUE# DAC_HSYNC DAC_VSYNC DAC_SCL DAC_SDA DAC_RSET PLLVDD PLLVDD18 PLLVSS VDDA18HTPLL VDDA18PCIEPLL VDDA18PCIEPLL SYSRESET# POWERGOOD LDTSTOP# ALLOW_LDTSTOP HT_REFCLKP HT_REFCLKN REFCLK_P REFCLK_N GFX_REFCLKP GFX_REFCLKN GPP_REFCLKP GPP_REFCLKN GPPSB_REFCLKP GPPSB_REFCLKN I2C_CLK I2C_DATA DDC_DATA DDC_CLK AUX1P AUX1N STRP_DATA VSS AUX_CAL

PART 3 OF 6

CRT/TVOUT

C2.2u6.3X5

TXOUT_L0P TXOUT_L0N TXOUT_L1P TXOUT_L1N TXOUT_L2P TXOUT_L2N TXOUT_L3P TXOUT_L3N TXOUT_U0P TXOUT_U0N TXOUT_U1P TXOUT_U1N TXOUT_U2P TXOUT_U2N TXOUT_U3P TXOUT_U3N TXCLK_LP TXCLK_LN TXCLK_UP TXCLK_UN

TXD00P TXD00N TXD01P TXD01N TXD02P TXD02N

29 29 29 29 29 29

D

TXD10P_R TXD10N_R TXD11N_R TXD11P_R TXD12N_R TXD12P_R

R732 R731 R733 R734 R735 R736

X_0R0402 X_0R0402 X_0R0402 X_0R0402 X_0R0402 X_0R0402

TXD10P TXD10N TXD11N TXD11P TXD12N TXD12P

TXD10P TXD10N TXD11N TXD11P TXD12N TXD12P

29 29 29 29 29 29

26 26 26

R G B if chipset version is A13 ,then R pull down resistor should change to 140 ohm 16,26 HSYNC# 16,26 VSYNC# 26 DDC_CLK 26 DDC_DATA FB11220L2A-50 HSYNC# VSYNC#

10 MILS WIDTH

R478 R480 R479 140R1%0402

10 MILS WIDTH

150R1%0402

10 MILS WIDTH

150R1%0402

RS780

TXC0P TXC0N 29 29 2 +1.8V_S0 CP38 1 X_30L3A-15_0805-RH C307 0.1u/16v/Y5/4 VDDLT18 VDDLT33

TP25

Q40 N-P8503BMG_SOT23-3-RH

D G S

+1.8V_S0

1.1V

VCC1_1

PLL X5R

C274 C2.2u6.3X5

15 MILS WIDTH

L32 R211 L31 X_30L3A-15_0805-RH 2 CP37 1 +12V 4.7KR0402

PLL PWR LVTM

+1.8V_S0

15 MILS WIDTH 15 MILS WIDTH

FB7 220L200mA 0402 C313 C2.2u6.3X5 FB6 220L2A-50 FB10 220L2A-50 C250 C2.2u6.3X5 C254 C0.1u16Y0402 C305 C2.2u6.3X5 C279 C0.1u16Y0402

C301 C2.2u6.3X5

15 MILS WIDTH 15 MILS WIDTH

C312 C0.1u16Y0402

VDDLT18 VDDLT18 VDDLT33 VDDLT33 VSSLT VSSLT VSSLT VSSLT VSSLT VSSLT VSSLT

15 MILS WIDTH

C288 C296 1u/6.3v/Y5/4

RS780

C10u6.3X50603-RH

C

C

PM

CLOCKs

Stuff : RX780 Nc : RS780 RX740/RS740/RS780 difference table

RS740 NB_PWRGD IN ALLOW_LDTSTOP OUT(default)/IN LDT_STOP# IN(default)/IN 3.3V IN OC 3.3V IN RX780 1.8V IN OC 1.8V IN RS780 1.8V IN OC/3.3V IN * 3.3V IN/OC * R257 *, CLMC mode: NB send LDT_STOP#, ALLOW_LDTSTOP will become input X_4.7KR0402 VCC3 VCC3 R236 4.7KR0402

7 7

HTREFCLK HTREFCLK# 7 NB_OSC_14M VCC1_1 R483 NB_OSC_14M

ANALOG POWER X5R

E9 F7 G12 RX780 RX780 R485 R484 R155 X_4.7KR0402 VCC3

R481 NB_OSC_14M_R R482 150R1%0402 150R1%0402

7 NBGFX_SRCCLK 7 NBGFX_SRCCLK# B9,A9 pulling up resistors are stuffed for not working and hardware reseting issue.B8,A8 pulling up resistors are reserved. VCC3 7 7 NBLINKCLK NBLINKCLK# 29 29 23 23 DVI_DDC_CLK DVI_DDC_DATA SDA0_AUX0N SCL0_AUX0P DVI_DDC_CLK DVI_DDC_DATA SDA0_AUX0N SCL0_AUX0P DP_AUX1P DP_AUX1N R248 TP26 R259 RS740_DFT_GPIO1 150R0402 R262 X_4.7KR0402 R268 X_4.7KR0402 SDA0_AUX0N SCL0_AUX0P

GPIO3 GPIO2 GPIO4

U1 U2 V4 V3 B9 A9 B8 A8 B7 A7

X_1.27KR1%0402 X_1.27KR1%0402 TMDS_HPD2 29

DVI/HDMI hot plug

TMDS_HPD0 23 VCC3

MIS.

R250 X_4.7KR0402 DVI_DDC_DATA DVI_DDC_CLK

TMDS_HPD HPD TVCLKIN THERMALDIODE_P THERMALDIODE_N TESTMODE

D9 D10 D12 AE8 AD8 D13 TEST_EN R233 1.8KR0402 R247

TMDS_HPD1

R260

X_4.7KR0402

10KR0402 RS780

VCC3

X_2KR0402 STRP_DATA B10 G11 C8

SUSE_STAT#, RS780C doesn't support sideport. So SUSE_STAT# of SB700,just let it NC

AMD-215-0674007-00-A01-RH

18 ALLOW_LDTSTOP

B

ALLOW_LDTSTOP

RS740/RX780/RS780 STRAPS Note: for RS780, change 150R as AUX_CAL,

place close to pin C8

RS740/RX780/RS780: STRAP_DEBUG_BUS_GPIO_ENABLE

RS780

RS740/RX780/RS780: LOAD_EEPROM_STRAPS

+1.8V_S0 VCC3

Enables the Test Debug Bus using GPIO and/or memory IO 1 : Disable (RS740); Enable (RX780/RS780) 0 : Enable (RS740); Disable(RX780/RS780) RX780: pin DFT_GPIO5 RS780: pin VSYNC

B

R229 X_4.7KR0402 B

R238 X_4.7KR0402

Selects Loading of STRAPS from EPROM 1 : Bypass the loading of EEPROM straps and use Hardware Default Values 0 : I2C Master can load strap values from EEPROM if connected, or use default values if not connected RS740: pin DFT_GPIO1 RS780: pin SUS_STAT#

RX780/RS740/RS780 DEBUG PIN MAPPING

RX780 RS740 LVDS_DIGON LVDS_ENA_BL LVDS_BLON TMDS_HPD X X X X RS780 LVDS_DIGON LVDS_ENA_BL LVDS_BLON TMDS_HPD AUX1N AUX1P HPD AUX_CAL DEBUG_OUT0 DEBUG_OUT1 DEBUG_OUT2 DEBUG_OUT3 DEBUG_OUT4 DEBUG_OUT5 DEBUG_OUT6 DEBUG_OUT7 RED(DFT_GPIO0) GREEN(DFT_GPIO1) Y(DFT_GPIO2) BLUE(DFT_GPIO3) TXOUT_L2N(DBG_GPIO0) TXCLK_LP(DBG_GPIO1) TXOUT_L3N(DBG_GPIO2) TXCLK_LN(DBG_GPIO3)

RS740

C 0R0402 LDT_STOP#_NB

8,18

LDT_STOP#

X_N-MMBT3904_NL_SOT23 Q42 E R251

DFT_GPIO[4:2]: STRAP_PCIE_GPP_CFG[2:0] These pin straps are used to configure PCI-E GPP mode. 111: register defined (register default to Config E) default 110: 4-0-0-0-0 Config A 101: 4-4-0-0-0 Config B 100: 4-2-2-0-0 Config C 011: 4-2-1-1-0 Config D 010: 4-1-1-1-1 Config E others: register defined (default to Config E)

RS780

+1.8V_S0 VCC3

DP_AUX1P DP_AUX1N

R269 R263

X_3K/4 X_3K/4

RS780

X_N-MMBT3904_NL_SOT23 Q43 8,18 LDT_RST# E B

R255 X_4.7KR0402

R267 X_4.7KR0402

RS780 RS780

C SYSRESET#

SDA0_AUX0P SDA0_AUX0N DP_AUX1P DP_AUX1N Route AUX differentially

RS740/RX780/RS780: LOAD_EEPROM_STRAPS

18,23,30

A_RST# RS740

R270

0R0402

Selects Loading of STRAPS from EPROM 1 : Bypass the loading of EEPROM straps and use Hardware Default Values 0 : I2C Master can load strap values from EEPROM if connected, or use default values if not connected

RS780

RX740/RS740/RS780 JTAG PIN MAPPING

RX780 TRST TMS(TP220) TEST_EN PCIE_RST3(TP222) I2C_DATA I2C_CLK PWM_GPIO6(TP219) RS740/RS780 TEST_EN DDC_DATA(TP223) I2C_DATA I2C_CLK TMDS_HPD(TP221)

A

RS780

RX780 100M DIFF 100M DIFF 14M SE (1.8V) NC 100M DIFF 100M DIFF 100M DIFF 100M DIFF 100M DIFF

NB CLOCK INPUT TABLE

RX780: pin DFT_GPIO1 RS780: pin SUS_STAT#

NB CLOCKS

A

TDI TCK TDO(TP218)

HT_REFCLKP

66M SE(SE)

HT_REFCLKN REFCLK_P REFCLK_N GFX_REFCLK GPP_REFCLK GPPSB_REFCLK

NC 14M SE (3.3V) NC 100M DIFF NC 100M DIFF

14M SE (1.1V) vref 100M DIFF(IN/OUT)* 100M DIFF(OUT) 100M DIFF

100M DIFF 100M DIFF

RS740/RX780/RS780: SIDE-PORT MEMORY ENABLE

Enables Side port memory 1. Disable (RS740/RS780) 0 : Enable (RS740/RS780) RS780: pin HSYNC RX780: Not Appicable

MICRO-STAR INt'L CO., LTD.

Title

RS780-SYSTEM I/F

Size Document Number

* RS780 can be used as clock buffer to output two PCIE referecence clocks By deault, chip will configured as input mode, BIOS can program it to output mode.

5

RS740

Date:

4 3 2

MS-7549

Tuesday, November 11, 2008

1

Rev 1.1 15 of 38

Sheet

5

4

3

2

1

U15D

PAR 4 OF 6

AB12 AE16 V11 AE15 AA12 AB16 AB14 AD14 AD13 AD15 AC16 AE13 AC14 Y14 AD16 AE17 AD17 W12 Y12 AD18 AB13 AB18 V14 V15 W14 AE12 AD12 MEM_A0 MEM_A1 MEM_A2 MEM_A3 MEM_A4 MEM_A5 MEM_A6 MEM_A7 MEM_A8 MEM_A9 MEM_A10 MEM_A11 MEM_A12 MEM_A13 MEM_BA0 MEM_BA1 MEM_BA2 MEM_RAS# MEM_CAS# MEM_WE# MEM_CS# MEM_CKE MEM_ODT MEM_CKP MEM_CKN MEM_COMPP MEM_COMPN MEM_DQ0 MEM_DQ1 MEM_DQ2 MEM_DQ3 MEM_DQ4 MEM_DQ5 MEM_DQ6 MEM_DQ7 MEM_DQ8 MEM_DQ9 MEM_DQ10 MEM_DQ11 MEM_DQ12 MEM_DQ13 MEM_DQ14 MEM_DQ15 MEM_DQS0P MEM_DQS0N MEM_DQS1P MEM_DQS1N MEM_DM0 MEM_DM1 IOPLLVDD18 IOPLLVDD IOPLLVSS MEM_VREF AA18 AA20 AA19 Y19 V17 AA17 AA15 Y15 AC20 AD19 AE22 AC18 AB20 AD22 AC22 AD21 Y17 W18 AD20 AE21 W17 AE19 AE23 AE24 AD23 AE18

MEM_VREF1 IOPLLVDD18 IOPLLVDD +1.8V_S0 VCC1_1 15,26 VSYNC#

D

D

SBD_MEM/DVO_I/F

RS740/RX780/RS780: STRAP_DEBUG_BUS_GPIO_ENABLE

VCC3 R240 3KR0402 R244 X_3KR0402

Enables the Test Debug Bus using GPIO and/or memory IO 1 : Disable (RS740/RS780); Enable (RX780) 0 : Enable (RS740/RS780); Disable(RX780) RS740: pin DFT_GPIO5 RS780: pin VSYNC

15 MILS WIDTH 15 MILS WIDTH

1.2V(RS740) C251 X_C2.2u6.3X5 X_C2.2u6.3X5 R237 X_3KR0402 C266

RS740/RX780/RS780: SIDE-PORT MEMORY ENABLE

AMD-215-0674007-00-A01-RH 15,26 VCC_DDR HSYNC# R232 3KR0402 VCC3 Have not side port memory,AMD suggest HSYNC pull hign

Enables Side port memory 1. Disable (RS740/RS780) 0 : Enable (RS740/RS780) RS740: pin DFT_GPIO0 RS780: pin HSYNC

FOR RS780,R148,R162,C203 and C202 will be populated.

R224

C

RX780/RS780: STRAP_DEBUG_BUS_PCIE_ENABLE

X_1KR1%0402 MEM_VREF1 R222 C285 0R X_C0.1u10X0402

Enables Test debug bus using PCIE bus 1. Disable (can be enabled thru nbcfg register) 0 : Enable RS780: configurable thru register setting only RS740: Not supported

C

AMD: Please let MEM_VREF short to GND when Sideport is not used.

B

B

A

A

MICRO-STAR INt'L CO., LTD.

Title

RS780-SPMEM/STRAPS

Size Date:

5 4 3 2

Document Number