Jitter and Phase Noise in Ring Oscillators Ali Hajimiri,Sotirios Limotyrakis,and Thomas H.Lee,Member,IEEE

Abstract—A companion analysis of clock jitter and phase noise of single-ended and differential ring oscillators is presented.The impulse sensitivity functions are used to derive expressions for the jitter and phase noise of ring oscillators.The effect of the number of stages,power dissipation,frequency of oscillation,and short-channel effects on the jitter and phase noise of ring oscillators is analyzed.Jitter and phase noise due to substrate and supply noise is discussed,and the effect of symmetry on the upconversion of 1/f noise is demonstrated.Several new design insights are given for low jitter/phase-noise design.Good agreement between theory and measurements is observed.

Index Terms—Design methodology,jitter,noise measurement, oscillator noise,oscillator stability,phase jitter,phase-locked loops,phase noise,ring oscillators,voltage-controlled oscillators.

I.I NTRODUCTION

D U

E to their integrated nature,ring oscillators have be-

come an essential building block in many digital and communication systems.They are used as voltage-controlled oscillators(VCO’s)in applications such as clock recovery circuits for serial data communications[1]–[4],disk-drive read channels[5],[6],on-chip clock distribution[7]–[10],and integrated frequency synthesizers[10],[11].Although they have not found many applications in radio frequency(RF), they can be used for some low-tier RF systems. Recently,there has been some work on modeling jitter and phase noise in ring oscillators.References[12]and[13] develop models for the clock jitter based on time-domain treatments for MOS and bipolar differential ring oscillators, respectively.Reference[14]proposes a frequency-domain approach to?nd the phase noise based on an linear time-invariant model for differential ring oscillators with a small number of stages.

In this paper,we develop a parallel treatment of frequency-domain phase noise[15]and time-domain clock jitter for ring oscillators.We apply the phase-noise model presented in[16] to obtain general expressions for jitter and phase noise of the ring oscillators.

The next section brie?y reviews the phase-noise model presented in[16].In Section III,we apply the model to timing jitter and develop an expression for the timing jitter of oscilla-tors,while Section IV provides the derivation of a closed-form expression to calculate the rms value of the impulse sensitivity function(ISF).Section V introduces expressions for jitter and phase noise in single-ended and differential ring oscillators Manuscript received April8,1998;revised November2,1998.

A.Hajimiri is with the California Institute of Technology,Pasadena,CA 91125USA.

S.Limotyrakis and T.H.Lee are with the Center for Integrated Systems, Stanford University,Stanford,CA94305USA.

Publisher Item Identi?er S0018-9200(99)04200-6.in long-and short-channel regimes of operation.Section VI describes the effect of substrate and supply noise as well as the noise due to the tail-current source in differential struc-tures.Section VII explains the design insights obtained from this treatment for low jitter/phase-noise design.Section VIII summarizes the measurement results.

II.P HASE N OISE

The output of a practical oscillator can be written

as

is periodic in

2

model?uctuations in amplitude and phase due to internal and external noise sources.The amplitude?uctuations are signi?cantly attenuated by the amplitude limiting mechanism, which is present in any practical stable oscillator and is particularly strong in ring oscillators.Therefore,we will focus on phase variations,which are not quenched by such a restoring mechanism.

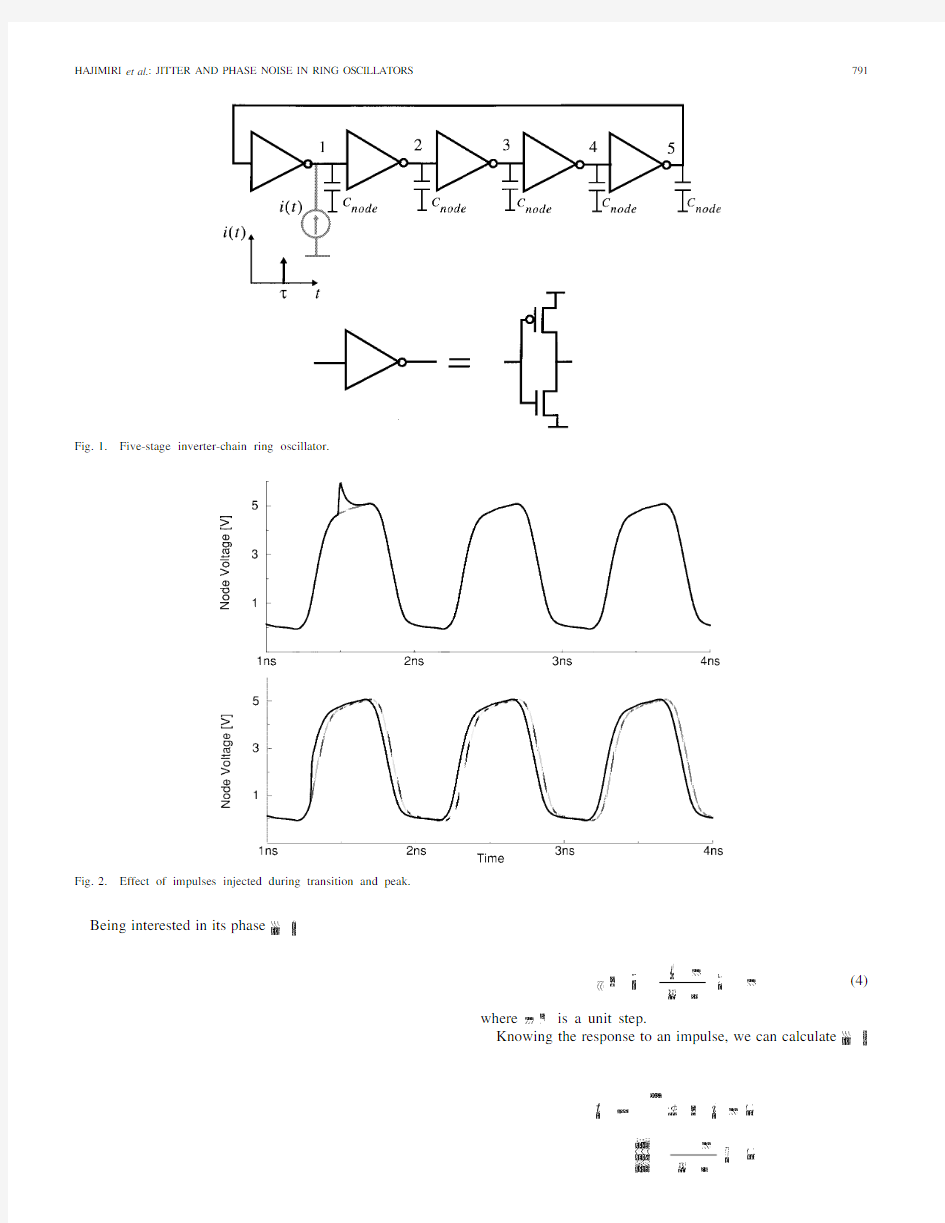

As an example,consider the single-ended ring oscillator with a single current source on one of the nodes shown in Fig.1.Suppose that the current source consists of an impulse of current with

area

is proportional to the injected

charge

(3)

where is the voltage swing across the capacitor

and

thus represents the sensitivity of every point of the waveform to a

perturbation,

Fig.1.Five-stage inverter-chain ring oscillator.

Being interested in its phase

(4)

where is a unit step.

Knowing the response to an impulse,we can calculate

where represents the noise current injected into the node of interest.Note that the integration arises from the closed-loop nature of the oscillator.The single-sideband phase-noise spectrum due to a white-noise current source is given by[16]

1

(6)

where is the single-

sideband power spectral density of the noise current source,

and is the frequency offset from the carrier.In the case

of multiple noise sources injecting into the same

node,

noise sources

is

times for a differential ring

oscillator).

From(5),it follows that the upconversion of low-frequency

noise,such as

1

(7)

where is the dc value of the ISF.Since the height of the

positive and negative lobes of the ISF is determined by the

slope of the rising and falling edges of the output waveform,

respectively,symmetry of the rising and falling edges can

reduce and hence the upconversion of

1

where

is the variance of the uncertainty introduced by one stage

during one transition.Noting

that

is a proportionality constant determined by circuit

parameters.

Another instructive special case that is not usually consid-

ered is when the noise sources are totally correlated with one

another.Substrate and supply noise are examples of such noise

sources.Low-frequency noise sources,such as

1

is another proportionality constant.Noise sources

such as thermal noise of devices are usually modeled as

uncorrelated,while substrate and supply-noise sources,as

well as low-frequency noise,are approximated as partially

or fully correlated sources.In practice,both correlated and

uncorrelated sources exist in a circuit,and hence a log–log

plot of the timing

jitter

In most digital applications,it is desirable for

or where

calculated to be

becomes

larger,since each transition occupies a smaller fraction of the

period.Based on these observations,we approximate the ISF

as triangular in shape and with symmetric rising and falling

edges,as shown in Fig.6.The case of nonsymmetric rising

and falling edges is considered in Appendix B.

The ISF has a maximum of1where is the

maximum slope of the normalized waveform

,and hence the

slopes of the sides of the triangles are

Fig.8.RMS values of the ISF’s for various single-ended ring oscillators versus number of stages.

On the other hand,stage delay is proportional to the rise

time

(14)

where

is a proportion-ality constant,which is typically close to one,as can be seen in Fig.7.

The period is

2

(16)

Note that the

1

dependence

of

because the effect of variations in other parameters,such

as

,and thus the ISF is a unitless,frequency-and

amplitude-independent function.

Equation (16)is valid for differential ring oscillators as well,since in its derivation no assumption speci?c to single-ended oscillators was made.Fig.9shows

the

changes.Members of the

second set of oscillators have a ?xed total power dissipation and ?xed load resistors,which result in variable swings and for whom data are shown with circles.The third case is that of a ?xed tail current for each stage and constant load resistors,whose data are illustrated using crosses.Again,in spite of the diverse variations of the frequency and other

circuit parameters,the

1

dependency

of This is shown with the solid line in Fig.9.A similar result

can be obtained for bipolar differential ring oscillators.

Although

Fig.9.RMS values of the ISF’s for various differential ring oscillators versus number of stages.

V.E XPRESSIONS FOR J ITTER AND P HASE N OISE IN R ING O SCILLATORS

In this section,we derive expressions for the phase noise and jitter of different types of ring oscillators.Throughout this section,we assume that the symmetry criteria required to

minimize

(and hence the upconversion of

1(17)

where

is the zero-bias drain source

conductance,

is the gate-oxide capacitance per unit

area,

is 2/3for long-channel devices in the saturation

region and typically two to three times greater for short-channel devices [18].Equation (17)is valid in both short-and long-channel regimes as long as an appropriate value

for

is given

by

(18)

where

-stage single-ended ring

oscillator,the power dissipation associated with this process

is

(22)

where

is the delay of each stage and and are the rise and fall time,respectively,associated with the maximum slope during a transition.

Assuming that the thermal noise sources of the different devices are uncorrelated,and assuming that the waveforms (and hence the ISF)of all the nodes are the same except for a phase shift,the total phase noise due to

all

(23)

is the characteristic voltage of the device.For

long-channel mode of operation,it is de?ned

as

(25)

increases,leading to no net dependence of phase noise

on

,since there is not a strong

dependence on the number of stages for single-ended CMOS

ring oscillators.Note that(25)and(26)establish the lower

bound and therefore should not be used to calculate the phase

noise and jitter of an arbitrary oscillator,for which(6)and

(12)should be used,respectively.

We may carry out a similar calculation for the short-channel

case.For such devices,the drain current may be expressed

as

is the number of

stages,is the tail bias current

of the differential pair,

and

(32)

Surprisingly,tail-current source noise in the vicinity

of

noise sources is

2

degrading as the number of stages increases for a given fre-

quency and power dissipation.This result may be understood

as a consequence of the necessary reduction in the charge

swing that is required to accommodate a constant frequency

of oscillation at a?xed power level as

i.e.,

th Fourier coef?cient of the ISF.Equation(38)

means that for identical sources,only noise in the vicinity of

integer multiples of affects the phase.

To verify this effect,sinusoidal currents with an amplitude

of10

20dB/dec slope.The effect of injection in the vicinity

of harmonics that are not integer multiples of

;however,as can be seen

in Fig.11,there is some sideband power due to the amplitude

response.

Low-frequency noise can also result in correlation between

uncertainties introduced during different cycles,as its value

does not change signi?cantly over a small number of periods.

Therefore,the uncertainties add up in amplitude rather than power,resulting in a region with a slope of one in the log–log plot of jitter even in the absence of external noise sources such as substrate and supply noise.

VII.D ESIGN I MPLICATIONS

One can use (23)and (34)to compare the phase-noise performance of single-ended and differential MOS ring os-cillators.As can be seen

for

for a regular ring oscillator is three,even a properly designed differential CMOS ring oscillator underperforms its single-ended counterpart,especially for a larger number of stages.This difference is even more pronounced if proper precautions to reduce the noise of the tail current are not taken.However,the differential ring oscillator may still be preferred in IC’s because of the lower sensitivity to substrate and supply noise,as well as lower noise injection into other circuits on the same chip.The decision to use differential versus single-ended ring oscillators should be based on both of these considerations.

The common-mode sensitivity problem in a single-ended ring oscillator can be mitigated to some extent by using two identical ring oscillators laid out close to each other that oscillate out of phase because of small coupling inverters [19].Single-ended con?gurations may be used in a less noisy environment to achieve better phase-noise performance for a given power dissipation.

As shown in Appendix B,asymmetry of the rising and falling edges degrades phase noise and jitter by increasing

the

1

corner frequency.Thus,every effort should be taken to make the rising and falling edges symmetric.By properly adjusting the symmetry properties,one can suppress or even eliminate low-frequency-noise upconversion [16].As shown in [16],differential symmetry is insuf?cient,and the symmetry of each half circuit is important.One practical method to achieve this symmetry is to use more linear loads,such as resistors or linearized MOS devices.This method reduces the

1

increases.Hence for a

process with large

1

will reduce the jitter.In general,the choice of the number of stages must be made on the basis of several design criteria,such as

1

Second,in a ring

oscillator,the device noise is maximum during the transitions,which is the time where the sensitivity,and hence the ISF,is the largest [16].

VIII.E XPERIMENTAL R ESULTS

The phase-noise measurements in this section were per-formed using three different systems:an HP 8563E spectrum analyzer with phase-noise measurement capability,an RDL NTS-1000A phase-noise measurement system,and an HP E5500phase-noise measurement system.The jitter measure-ments were performed using a Tektronix CSA 803A commu-nication signal analyzer.

Tables I–III summarize the phase-noise measurements.All the reported phase-noise values are at a 1-MHz offset from the carrier,chosen to achieve the largest dynamic range in the measurement.Table I shows the measurement results for three different inverter-chain ring oscillators.These oscillators are made of the CMOS inverters shown in Fig.12(a),with no frequency tuning mechanism.The output is taken from one node of the ring through a few stages of tapered inverters.Oscillators number 1and 2are fabricated in a

2-

m

TABLE I

I NVERTER -C HAIN R ING O

SCILLATORS

TABLE II

C URRENT -S TARVE

D I NVERTER -C HAIN R ING O

SCILLATORS

As an illustrative example,we will show the details of phase-noise calculations for oscillator number https://www.doczj.com/doc/2412985662.html,ing (16)to

calculate

the phase noise can be obtained from (6).We calculate the noise power when the stage is halfway through a transition.At this point,the drain current is simulated to be

3.47mA.

An

10of 2.5is used in (28)to obtain a noise power

of

fC.There is one such noise source on

each node;therefore,the phase noise

is

dBc/Hz.

Table II summarizes the data obtained for current-starved ring oscillators with the cell structure shown in Fig.12(b),all implemented in the same

0.25-

).

Table III summarizes the results obtained for differential ring oscillators of various sizes and lengths with the inverter topology shown in Fig.12(c),covering a large span of frequen-cies up to 5.5GHz.All these ring oscillators are implemented in the same

0.25-

TABLE III

D IFFERENTIAL R ING O

SCILLATORS

(a)

(b)(c)

Fig.12.

Inverter stages for (a)inverter-chain ring oscillators,(b)current-starved inverter-chain ring oscillators,and (c)differential ring oscillators.

calculations for oscillator number 12.The noise current due to one of differential pair NMOS devices is given by (28).The total capacitance on each node in the balanced case

is

fF,and the simulated voltage swing is 1.208V;

therefore,

mA,and therefore

the noise current of the NMOS device has a single-sideband spectral density

of

stages,there is one such noise source on each node;therefore,the phase noise is

2

of 0.9,(34)predicts a phase noise

of

MHz

dBc/Hz

Fig.13.Die photograph of the current-starved single-ended

oscillators.

Fig.14.Die photograph of the 12-stage differential ring

oscillator.

Fig.15.

Timing jitter measurement setup using CSA803A.

distinguished from the device under test (DUT)’s jitter.This extra jitter can be directly measured by looking at the jitter on the triggering edge.This edge can be readily identi?ed since it has lower rms jitter than the transitions before and after it.

The effect of this excess jitter should be subtracted from the jitter due to the DUT.Assuming no correlation between the jitter of the DUT and the sampling head,the equivalent jitter due to the DUT can be estimated

by

(39)

where

is the measured rms jitter at a

delay

is the jitter on the triggering edge.

Fig.16shows the rms jitter versus the measurement delay for oscillator number 12on a log–log plot.The best

?t

Fig.16.RMS jitter versus measurement interval for the four-stage,2.8-GHz differential ring oscillator(oscillator number12).

Fig.17.Phase noise versus symmetry voltage for oscillator number7.

(41)

Therefore

Analog and digital designers prefer using phase noise and timing jitter,respectively.The relationship between these two parameters can be obtained by noting that timing jitter is the standard deviation of the timing

uncertainty

(45)

where represents the expected value.Since the autocor-

relation function

of

(46)

the timing jitter in(45)can be written

as

(47)

The relation between the autocorrelation and the power spec-

trum is given by the Khinchin theorem[21],

i.e.,

can be expressed in terms of phase noise in the

1region

as

(50)

where

(52)

where

and

represents the asymmetry

of the waveform and is de?ned

as

(54)

Combining(52)and(54)results in the

following:

can be calculated from Fig.18in a similar manner and

is given

by

,and the

1corner approaches zero.

A CKNOWLEDGMENT

The authors would like to thank M.A.Horowitz,G.Nasser-bakht,A.Ong,C.K.Yang,B.A.Wooley,and M.Zargari for helpful discussions and support.They would further like to thank Texas Instruments,Inc.,and Stanford Nano-Fabrication facilities for fabrication of the oscillators.

R EFERENCES

[1]L.DeVito,J.Newton,R.Croughwell,J.Bulzacchelli,and F.Benkley,

“A52and155MHz clock-recovery PLL,”in ISSCC Dig.Tech.Papers, Feb.1991,pp.142–143.

[2] A.W.Buchwald,K.W.Martin,A.K.Oki,and K.W.Kobayashi,“A6-

GHz integrated phase-locked loop using AlCaAs/Ga/As heterojunction bipolar transistors,”IEEE J.Solid-State Circuits,vol.27,pp.1752–1762, Dec.1992.

[3] https://www.doczj.com/doc/2412985662.html,i and R.C.Walker,“A monolithic622Mb/s clock extraction data

retiming circuit,”in ISSCC Dig.Tech.Papers,Feb.1993,pp.144–144.

[4]R.Farjad-Rad,C.K.Yang,M.Horowitz,and T.H.Lee,“A0.4mm

CMOS10Gb/s4-PAM pre-emphasis serial link transmitter,”in Symp.

VLSI Circuits Dig.Tech Papers,June1998,pp.198–199.

[5]W.D.Llewellyn,M.M.H.Wong,G.W.Tietz,and P.A.Tucci,“A

33Mbi/s data synchronizing phase-locked loop circuit,”in ISSCC Dig.

Tech.Papers,Feb.1988,pp.12–13.

[6]M.Negahban,R.Behrasi,G.Tsang,H.Abouhossein,and G.Bouchaya,

“A two-chip CMOS read channel for hard-disk drives,”in ISSCC Dig.

Tech.Papers,Feb.1993,pp.216–217.

[7]M.G.Johnson and E.L.Hudson,“A variable delay line PLL for CPU-

coprocessor synchronization,”IEEE J.Solid-State Circuits,vol.23,pp.

1218–1223,Oct.1988.

[8]I.A.Young,J.K.Greason,and K.L.Wong,“A PLL clock generator

with5–110MHz of lock range for microprocessors,”IEEE J.Solid-State Circuits,vol.27,pp.1599–1607,Nov.1992.

[9]J.Alvarez,H.Sanchez,G.Gerosa,and R.Countryman,“A wide-

bandwidth low-voltage PLL for PowerPC TM microprocessors,”IEEE J.Solid-State Circuits,vol.30,pp.383–391,Apr.1995.

[10]I.A.Young,J.K.Greason,J.E.Smith,and K.L.Wong,“A PLL clock

generator with5–110MHz lock range for microprocessors,”in ISSCC Dig.Tech.Papers,Feb.1992,pp.50–51.

[11]M.Horowitz,A.Chen,J.Cobrunson,J.Gasbarro,T.Lee,W.Leung,

W.Richardson,T.Thrush,and Y.Fujii,“PLL design for a500Mb/s interface,”in ISSCC Dig.Tech.Papers,Feb.1993,pp.160–161. [12]T.C.Weigandt,B.Kim,and P.R.Gray,“Analysis of timing jitter in

CMOS ring oscillators,”in Proc.ISCAS,June1994.

[13]J.McNeill,“Jitter in ring oscillators,”IEEE J.Solid-State Circuits,vol.

32,pp.870–879,June1997.

[14] B.Razavi,“A study of phase noise in CMOS oscillators,”IEEE J.

Solid-State Circuits,vol.31,pp.331–343,Mar.1996.

[15] A.Hajimiri,S.Limotyrakis,and T.H.Lee,“Phase noise in multi-

gigahertz CMOS ring oscillators,”in Proc.Custom Integrated Circuits Conf.,May1998,pp.49–52.

[16] A.Hajimiri and T.H.Lee,“A general theory of phase noise in electrical

oscillators,”IEEE J.Solid-State Circuits,vol.33,pp.179–194,Feb.

1998.

[17],The Design of Low Noise Oscillators.Boston,MA:Kluwer

Academic,1999.

[18] A.A.Abidi,“High-frequency noise measurements of FET’s with small

dimensions,”IEEE Trans.Electron Devices,vol.ED-33,pp.1801–1805, Nov.1986.[19]T.Kwasniewski,M.Abou-Seido,A.Bouchet,F.Gaussorgues,and J.

Zimmerman,“Inductorless oscillator design for personal communica-tions devices—A1.2 m CMOS process case study,”in Proc.CICC, May1995,pp.327–330.

[20]J.G.Maneatis and M.A.Horowitz,“Precise delay generation using cou-

pled oscillators,”IEEE J.Solid-State Circuits,vol.28,pp.1273–1282, Dec.1993.

[21]W. A.Gardner,Introduction to Random Processes.New York:

McGraw-Hill,1990.

[22]W.F.Egan,Frequency Synthesis by Phase Lock.New York:Wiley,

1981.

Ali Hajimiri received the B.S.degree in electronics

engineering from Sharif University of Technology,

Tehran,Iran,in1994and the M.S.and Ph.D.

degrees in electrical engineering from Stanford Uni-

versity,Stanford,CA,in1996and1998,respec-

tively.

He was a Design Engineer with Philips,where

he worked on a BiCMOS chipset for GSM cellular

units from1993to1994.During the summer of

1995,he was with Sun Microsystems,where he

worked on the UltraSparc microprocessor’s cache RAM design methodology.During the summer of1997,he was with Lucent Technologies(Bell Labs),where he investigated low-phase-noise integrated oscillators.In1998,he joined the Faculty of the California Institute of Technology,Pasadena,as an Assistant Professor.His research interests are high-speed and RF integrated circuits.He is coauthor of The Design of Low Noise Oscillators(Boston,MA:Kluwer Academic,1999).

Dr.Hajimiri was the Bronze Medal Winner of the21st International Physics Olympiad,Groningen,the Netherlands.He was a corecipient of the International Solid-State Circuits Conference1998Jack Kilby Outstanding Paper

Award.

Sotirios Limotyrakis was born in Athens,Greece,

in1971.He received the B.S.degree in electrical

engineering from the National Technical University

of Athens in1995and the M.S.degree in electri-

cal engineering from Stanford University,Stanford,

CA,in1997,where he currently is pursuing the

Ph.D.degree.

In the summer of1993,he was with K.D.D.

Corp.,Saitama R&D Labs,Japan,where he worked

on the design of communication protocols.During

the summers of1996and1997,he was with the Texas Instruments Inc.R&D Center,Dallas,TX,where he focused on LNA,low-phase-noise oscillator design,and GSM mobile unit transmit path architectures.His current research interests include the design of mixed-signal circuits for high-speed data conversion and broad-band communications. Mr.Limotyrakis received the W.Burgess Dempster Memorial Fellowship from the School of Engineering,Stanford University,in1995.

Thomas H.Lee(S’87–M’87),for a photograph and biography,see p.585of the May1999issue of this J OURNAL.

1石英晶体及其特性 (1) 1.1 石英晶体简介............................................... . ... 1.2石英晶体的阻抗频率特性...................................... 1 ... 2晶体管的部工作原理 (3) 3.晶体振荡器电路的类型及其工作原理 (4) 3.1串联型谐振晶体振荡器........................................ 4…??… 3.2并联谐振型晶体振荡器........................................ 6…??… 3.3泛音晶体振荡器................................................ 8 .. 4 确定工作点和回路参数(以皮尔斯电路为例) (10) 4.1主要技术指标 (10) 4.2确定工作点 (10) 4.3交流参数的确定 (11) 5提高振荡器的频率稳定度........................................... 1 2 6.总结 (13) 参考文献:........................................................ 1.4

Word 文档

1石英晶体及其特性 1.1石英晶体简介 石英是矿物质硅石的一种,化学成分是Sio2,形状是呈角锥形的六棱结晶体,具有各向异性的物理特性。按其自然形状有三个对称轴,电轴X,机械轴丫光轴Z。石英谐振器中的各种晶片,就是按与各轴不同角度,切割成正方形、长方形、圆形、或棒型的薄片,如图1的AT、BT、CT、DT 等切型。不同切型的晶片振动型式不,性能不同 1.2石英晶体的阻抗频率特性 石英谐振器的电路符号和等效电路如图121。C0称为静态电容,即晶体不振动时两极板间的等效电容,与晶片尺寸有关,一般约为几到几十pF。晶体作机械振动时的惯性以Lq、弹性用Cq振动时因磨擦造成的损耗用Rq来等效,它们的数值与晶片切割方位、形状和大小有关, 一般Lq为10 3102H,Cq为10 410 1pF,Rq 在几一几百欧之间。它

SDH抖动测试 一、抖动特性 1、抖动的概念 在理想情况下,数字信号在时间域上的位置是确定的,即在预定的时间位置上将回出现数字脉冲(1或0)。然而由于种种非理想的因素会导致数字信号偏离它的理想时间位置。我们将数字信号的特定时刻(例如最佳抽样时刻)相对其理想时间位置的短时间偏离称为定时抖动,简称抖动。这里所谓短时间偏离是指变化频率高于10H的相位变化,而将低于的相位变化称为漂移。事实上,两者的区分不仅在相位变化的频率不同,而且在产生机理、特性和对网络的影响方面也不尽相同。 定时抖动对网络的性能损伤表现在下面几个方面: *对数字编码的模拟信号,解码后数字流的随机相位抖动使恢复后的样值具有不规则的相位,从而造成输出模拟信号的失真,形成所谓抖动噪声,影响业务信号质量,特别是图像信号质量。 *在再生器中,定时的不规则性使有效判决点偏离接收眼图的中心,从而降低了再生器的信噪比余度,直至发生误码。 *对于需要缓存器和相位比较器的数字设备,过大的抖动会造成缓存器的溢出或取空,从而导致不可控滑动损伤。 2、抖动机理 (1)、PDH与SDH共有的抖动源 A、随机性抖动源 * 各类噪声源 * 定时滤波器失谐 * 完全不相关的图案抖动 B、系统性抖动源 * 码间干扰 * 有限脉宽作用 * 限幅器的门限漂移 * 激光器的图案效应 (2)、SDH设备特有的抖动机理 A、指针调整抖动 SDH设备的支路信号的同步机理采用所谓的指针调整,即利用指针值的增减调整来补偿低速支路信号的相位变化和频率变化,由于指针调整是按字节为单位进行的,调整时将带来很大的相位跃变。带有这些相位跃变的数字信号通过带限电路时将会产生很长的相位过滤过程。处于正常同步工作的SDH网中的指针调整主要是由于同步分配过程中的随机噪声引起的,因而由之引起

摘要 自激式振荡器是在无需外加激励信号的情况下,能将直流电能转换成具有一定波形、一定频率和一定幅值的交变能量电路。正弦波振荡器的作用是产生频率稳定、幅度不变的正弦波输出。基于频率稳定、反馈系数、输出波形、起振等因素的综合考虑,本次课程设计采用电容三点式振荡器,运用multisim软件进行仿真。根据静态工作点计算出回路的电容电感取值,得出输出频率与输出幅度有效值以达到任务书的要求。 关键词:电容三点式;振荡器;multisim;

目录 1、绪论 (1) 2、方案的确定 (2) 3、工作原理、硬件电路的设计和参数的计算 (3) 3.1 反馈振荡器的原理和分析 (3) 3.2. 电容三点式振荡单元 (4) 3.3 电路连接及其参数计算 (5) 4、总体电路设计和仿真分析 (6) 4.1组建仿真电路 (6) 4.2仿真的振荡频率和幅度 (7) 4.3误差分析 (8) 5、心得体会 (9) 参考文献 (10) 附录 (10) 附录Ⅰ元器件清单 (10) 附录Ⅱ电路总图 (11)

1、绪论 振荡器是不需外信号激励、自身将直流电能转换为交流电能的装置。凡是可以完成这一目的的装置都可以作为振荡器。一个振荡器必须包括三部分:放大器、正反馈电路和选频网络。放大器能对振荡器输入端所加的输入信号予以放大使输出信号保持恒定的数值。正反馈电路保证向振荡器输入端提供的反馈信号是相位相同的,只有这样才能使振荡维持 下去。选频网络则只允许某个特定频率0f能通过,使振荡器产生单一频率的输出。 振荡器能不能振荡起来并维持稳定的输出是由以下两个条件决定的;一个是反馈电压 U和输入电压i U要相等,这是振幅平衡条件。二是f U和i U必须相位相同,这是相位f 平衡条件,也就是说必须保证是正反馈。一般情况下,振幅平衡条件往往容易做到,所以在判断一个振荡电路能否振荡,主要是看它的相位平衡条件是否成立。 本次课程设计我设计的是电容反馈三点式振荡器,电容三点式振荡器,也叫考毕兹振荡器,是自激振荡器的一种,这种电路的优点是输出波形好。电容三点式振荡器是由串联电容与电感回路及正反馈放大器组成。因振荡回路两串联电容的三个端点与振荡管三个管脚分别相接而得名。 本课题旨在根据已有的知识及搜集资料设计一个正弦波振荡器,要求根据给定参数设计电路,并利用multisim仿真软件进行仿真验证,达到任务书的指标要求,最后撰写课设报告。报告内容按照课设报告文档模版的要求进行,主要包括有关理论知识介绍,电路设计过程,仿真及结果分析等。 主要技术指标:输出频率9 MHz,输出幅度(有效值)≥5V。

实验二:LC与晶体振荡器 一.实验目的 1.熟悉电子元器件和高频电子线路实验系统。 2.掌握电容三点式LC振荡电路的基本原理,熟悉其各元件功能。 3.熟悉静态工作点IEQ对振荡器振荡幅度和频率的影响。 4.熟悉LC谐振回路的电容变化对振荡器振荡频率的影响。 二.实验预习要求 1.做本实验时应具备的知识点: * 三点式LC振荡器 * 克拉泼电路 * 静态工作点值对振荡器工作的影响 2.做本实验时所用到的仪器: * LC与晶体振荡模块实验板 * 双踪示波器 * 频率计 * 万用表 三.实验电路原理 1.概述 LC振荡器实质上是满足振荡条件的正反馈放大器。LC振荡器是指振荡回路是由LC元件组成的。从交流等效电路可知:由LC振荡回路引出三个端子,分别接振荡管的三个电极,而构成反馈式自激振荡器,因而又称为三点式振荡器。如果反馈电压取自分压电感,则称为电感反馈LC振荡器或电感三点式振荡器;如果反馈电压取自分压电容,则称为电容反馈LC振荡器或电容三点式振荡器。 在几种基本高频振荡回路中,电容反馈LC振荡器具有较好的振荡波形和稳定度,电路形式简单,适于在较高的频段工作,尤其是以晶体管极间分布电容构成反馈支路时其振荡频率可高达几百MHZ~GHZ。 2.LC振荡器的起振条件 一个振荡器能否起振,主要取决于振荡电路自激振荡的两个基本条件,即:振幅起振、平衡条件和相位平衡条件。 3.C振荡器的频率稳定度 频率稳定度表示:在一定时间、或一定温度、电压等变化范围内振荡频率的相对变化程度,常用表达式:Δf0/f0来表示(f0为所选择的测试频率;Δf0为振荡频率的频率误差,Δf0=f02-f01;f02和f01为不同时刻的f0),频率相对变化量越小,表明振荡频率的稳定度越高。由于振荡回路的元件是决定频率的主要因素,所以要提高频率稳定度,就要设法提高振荡回路的标准性,除了采用高稳定和高Q值的回路电容和电感外,其振荡管可以采用部分接入,以减小晶体管极间电容和分布电容对振荡回路的影响,还可采用负温度系数元件实现温度补偿。 4、LC振荡器的调整和参数选择 以实验采用的改进型电容三点振荡电路(西勃电路)为例 (1)静态工作点的调整 合理选择振荡管的静态工作点,对振荡器工作的稳定性及波形的好坏,有一定的影响,偏置电路一般采用分压式电路,如实验电路图12-1所示。

晶体振荡器工作原理 石英晶体振荡器是高精度和高稳定度的振荡器,被广泛应用于彩电、计算机、遥控器等各类振荡电路中,以及通信系统中用于频率发生器、为数据处理设备产生时钟信号和为特定系统提供基准信号。 石英晶体振荡器的基本原理 石英晶体振荡器的结构 石英晶体振荡器是利用石英晶体(二氧化硅的结晶体)的压电效应制成的一种谐振器件,它的基本构成大致是:从一块石英晶体上按一定方位角切下薄片(简称为晶片,它可以是正方形、矩形或圆形等),在它的两个对应面上涂敷银层作为电极,在每个电极上各焊一根引线接到管脚上,再加上封装外壳就构成了石英晶体谐振器,简称为石英晶体或晶体、晶振。其产品一般用金属外壳封装,也有用玻璃壳、陶瓷或塑料封装的。 压电效应 若在石英晶体的两个电极上加一电场,晶片就会产生机械变形。反之,若在晶片的两侧施加机械压力,则在晶片相应的方向上将产生电场,这种物理现象称为压电效应。如果在晶片的两极上加交变电压,晶片就会产生机械振动,同时晶片的机械振动又会产生交变电场。在一般情况下,晶片机械振动的振幅和交变电场的振幅非常微小,但当外加交变电压的频率为某一特定值时,振幅明显加大,比其他频率下的振幅大得多,这种现象称为压电谐振,它与LC回路的谐振现象十分相似。它的谐振频率与晶片的切割方式、几何形状、尺寸等有关。 符号和等效电路 当晶体不振动时,可把它看成一个平板电容器称为静电电容C,它的大小与晶片的几何尺寸、电极面积有关,一般约几个PF到几十PF。当晶体振荡时,机械振动的惯性可用电感L来等效。一般L的值为几十mH 到几百mH。晶片的弹性可用电容C来等效,C的值很小,一般只有0.0002~0.1pF。晶片振动时因摩擦而造成的损耗用R来等效,它的数值约为100Ω。由于晶片的等效电感很大,而C很小,R也小,因此回路的品质因数Q很大,可达1000~10000。加上晶片本身的谐振频率基本上只与晶片的切割方式、几何形状、尺寸有关,而且可以做得精确,因此利用石英谐振器组成的振荡电路可获得很高的频率稳定度。 谐振频率 从石英晶体谐振器的等效电路可知,它有两个谐振频率,即(1)当L、C、R支路发生串联谐振时,它的等效阻抗最小(等于R)。串联揩振频率用fs表示,石英晶体对于串联揩振频率fs呈纯阻性,(2)当频率高于fs时L、C、R支路呈感性,可与电容C。发生并联谐振,其并联频率用fd表示。根据石英晶体的等效电路,可定性画出它的电抗—频率特性曲线。可见当频率低于串联谐振频率fs 或者频率高于并联揩振频率fd时,石英晶体呈容性。仅在fs<f<fd极窄的范围内,石英晶体呈感性。 石英晶体振荡器类型特点 石英晶体振荡器是由品质因素极高的石英晶体振子(即谐振器和振荡电路组成。晶体的品质、切割取向、晶体振子的结构及电路形式等,共同决定振荡器的性能。国际电工委员会(IEC)将石英晶体振荡器分为4类:普通晶体振荡(TCXO),电压控制式晶体振荡器(VCXO),温度补偿式晶体振荡(TCXO),恒温控制式

石英晶体振荡器 第一章研究意义 金融危机以来,国家围绕“保增长、调结构”采取了一系列调控政策,为我国石英晶体振荡器行业提供了较为宽松的国内发展环境,使石英晶体振荡器行业从2008年下半年以来的困境中得到了缓解和恢复。我国石英晶体振荡器行业也在加快产业结构调整、转变发展方式,为行业持续发展提供了动力和支撑。在全球经济不景气、国际市场持续低迷的情况下,我国石英晶体振荡器行业仍然呈现出了企稳回升、发展逐渐向好的良好局面。 虽然石英晶体振荡器行业发展很快,但是市场存在的一些问题不容忽视,如市场无序竞争、产品质量下降、创新乏力等。石英晶体振荡器行业的规划和发展需要建立在充分市场调研的基础之上,石英晶体振荡器市场管理需要认清市场经济条件下政府和企业的角色定位,石英晶体振荡器市场有序运行需要完善市场交易规则和各项制度。 第二章发展现状 石英的化学成分为SiO2,晶体属三方晶系的氧化物矿物,即低温石英(a-石英),是石英族矿物中分布最广的一个矿物种。广义的石英还包括高温石英(b-石英)。 低温石英常呈带尖顶的六方柱状晶体产出,柱面有横纹,类似于六方双锥状的尖顶实际上是由两个菱面体单形所形成的。石英集合体通常呈粒状、块状或晶簇、晶腺等。纯净的石英无色透明,玻璃光泽,贝壳状断口上具油脂光泽,无解理。受压或受热能产生电效应。 发展趋势 1、小型化、薄片化和片式化:为满足移动电话为代表的便携式产品轻、薄、短小的要求,石英晶体振荡器的封装由传统的裸金属外壳覆塑料金属向陶瓷封装转变。例如TCXO这类器件的体积缩小了30~100倍。采用SMD 封装的TCXO厚度不足2mm,目前5×3mm尺寸的器件已经上市石英晶体振荡器。 2、高精度与高稳定度,无补偿式晶体振荡器总精度也能达到±25ppm,VCXO的频率稳定度在10~7℃范围内一般可达±20~100ppm,而OCXO在同一温度范围内频率稳定度一般为±0.0001~5ppm,VCXO控制在±25ppm以下。

一种低噪声交叉耦合结构集成石英晶体振荡器的研究 摘要通过改进电路结构,采用CMOS交叉耦合结构提供负阻,设计一种20 MHz的集成石英晶体振荡器.在该振荡器中,采用共模反馈使其输出稳定的直流电平,并增加RC高通滤波器和预抑制电路降低其相位噪声.基于NUVOTON 0.35 μm CMOS工艺,利用Cadence Spectre对电路进行仿真,结果表明,在电源电压为3.3 V,偏置电流约400 μA时,该振荡器的起振时间约为1.5 ms,输出波形峰峰值为1.08 V,输出直流电平约为801.6 mV.输出信号频率为19.95 MHz,相位噪声分别可以达到-155 dBc/Hz@1 kHz,-164 dBc/Hz@10 kHz. 关键词晶体振荡器;相位噪声;交叉耦合;RC高通滤波 1 低噪声交叉耦合结构振荡电路 本文设计的交叉耦合结构的石英晶体振荡器及其等效电路,其主要由预抑制电路、CMOS交叉耦合电路、RC滤波电路、偏置电路和谐振网络等5部分组成. 偏置电压经过预抑制电路后通过电流镜给交叉耦合振荡电路提供一个稳定的偏置电流Ib.石英晶体在稳定振荡时工作在感性区间,因此,本文将石英晶体等效为一个电感来代替传统的CMOS交叉耦合VCO结构中的电感.同时在保证电路对称的情况下,改进电路结构,只需接一个石英晶体.输出端OSC1和OSC2分别接石英晶体的两端,在PMOS对和NMOS对的栅极与输出端之间加入RC 滤波电路。石英晶体两端各接一个负载电容CL,而R1和R2给振荡电路提供静态工作点。尾电流源给振荡电路提供偏置电流,同时考虑到电流源也会给振荡电路带来噪声,以噪声系数相对较小的PMOS电流镜作为尾电流源,能有效隔离电源噪声,并提供稳定的基准电流[1]。 1.1 CMOS交叉耦合结构 本文采用CMOS交叉耦合结构产生负阻补偿振荡电路振荡时的能量消耗,其工作在饱和区时的阻值为: R=-2/geff (5) 式中:geff为交叉耦合振荡器的等效跨导.对于单个的交叉耦合对: geff=gmn=gmp (6) 对于CMOS交叉耦合对: geff=gmn+gmp (7) 由式(6)和式(7)可知,相对于单个的耦合对,CMOS交叉耦合对能提供

燕山大学石英晶体振荡器设计报告 题目: 专业:电子信息工程 姓名:李飞虎 指导教师:李英伟 院系站点:信息科学与工程学院 2014年11 月17 日 高频石英晶体振荡器仿真报告

1.振荡器电路属于一种信号发生器类型,即表现为没有外加信号的情况下能自动生成具有一定频率、一定波形、一定振幅的周期性交变振荡信号的电子线路。振荡器起振时是将电路自身噪声或电源跳变中频谱很广的信号进行放大选频。此时振荡器的输出幅值是不断增长的,随着振幅的增大,放大器逐渐由放大区进入饱和区或者截止区,其增益逐渐下降,当放大器增益下降而导致环路增益下降到1时,振幅的增长过程将停止,振荡器达到平衡,进入等幅振荡状态。振荡器进入平衡状态后,直流电源补充的能量刚好抵消整个环路消耗的能量。 2,串联晶体振荡器 在串联型晶体振荡器中,晶体接在振荡器要求低阻抗的两点之间,通常接在反馈电路中。图1-1和图1-2显示出了一串联型振荡器的实际路线和等效电路。可以看出,如果将石英晶体短路,该电路即为电容反馈的振荡器。电路的实际工作原理为:当回路的谐振频率等于晶体的串联谐振频率时,晶体的阻抗最小,近似为一短路线,电路满足相位条件和振幅条件,故能正常工作;当回路的谐振频率距串联谐振频率较远时,晶体阻抗增大,是反馈减弱,从而使电路不能满足振幅条件,电路不能正常工作。串联型晶体振荡器只能适应高

次泛音工作,这是由于晶体只起到控制频率的作用,对回路没有影响,只要电路能正常工作,输出幅度就不受晶体控制。 图1-1 图1-2 设计参数在仿真图上,首先进行静态分析,根据仿真,各元件参数符合要求。对于振荡器,当该电路接为串联型振荡器时,晶体起到选频短路线的作用,(与三端电容振荡器相同)输出频率应为3MHZ. L1,C1,C2组成谐振回路,参数符合要求,即f0=3MHZ。 3.并联晶体振荡器 并联振荡器分为c-b型和b-e型。前者相对稳定。所以我设计的是c-b型。 参数分析与前者类似。交流参数确定时,并联振荡电路中晶振接在谐振回

泰克MSO6的低噪声设计及降低显示信号上噪声的几种常用方法 噪声是一种无处不在的常见问题。几乎处理电路的每个人都要用一定的时间处理噪声,要么找到噪声来源修复它,要么减少噪声对测量的影响。噪声来自于各种各样的地方,包括设计内部来源或外部来源,噪声可能会淹没感兴趣的信号。您可能在测量低压(mV)信号方面正碰到麻烦,如在雷达传输或心脏监测仪中,噪声会使您很难找到信号的实际电压。噪声可能使抖动增加,从而很难进行精确分析。因此,要对低电压信号进行准确测量,不仅要保证示波器本身的低噪声,而且还需要简单精确的测量手段。 而示波器的低噪声设计也一直被追捧,不仅因为低噪声的重要性,同时还包含其技术挑战的难度。示波器设计中要考虑到许多因素,只有方方面面都做到精益求精,才能把产品做得像一件精美的艺术品。泰克示波器提供了相应的功能和工具,帮助您处理噪声。 本篇内容分为两部分,将首次披露泰克示波器低噪声设计细节,以及示波器中常用的测量工具。 低噪声设计 一、低噪声前置放大器的设计 众所周知,示波器的模拟前端,包含衰减电路、缓冲电路和放大器电路都会引入噪声。这也是示波器的本底噪声的重要来源。通常都会将模拟前端的设计作为评价示波器噪声的表现的重要指标。泰克MSO6采用了全新设计的前端放大器Tek061,在较小的伏特/格设置上实现了非常好的噪声性能。因此在放大小信号观察细节时,Tek061的优秀表现让脱颖而出,在1mv/div(1GHz带宽)时,示波器本底噪声实测值(RMS)只有54.8uV。

二、A DC模数转换的设计 当前使用的数字示波器中,ADC的量化噪声是示波器噪声另一来源。MSO6采用了世界上速度最快的新型12位ADC转换器,内部运行速率达25GS/s,每通道采样率要比以前的同类示波器高出25%。12位实现了4096种垂直模数转换电平,分辨率比采用8位ADC的示波器高出16 倍。每条ADC 通道基于交织连续接近寄存器(SAR)结构,基于该ADC的TEK049平台性能可以最高实现了100 GS/s 的总吞吐量。这样就把通道中大量的后端噪声分散到更大的带宽上,采用合适的滤波器滤除噪声。实现精确测量。 三、晶体振荡器的选择 MSO6采用的恒温晶体振荡器实现了一流的锁相环ASIC,时钟路径的噪声非常低。采用的时基精度为±20ppb(在校准时, 25℃环境温度, 在任意≥1 ms 间隔上)。实现了产生的时钟精度非常高,相位噪声非常低。这么低的相位噪声,使我们的客户能够更准确地进行时间测量。 四、信号通路的设计 差分路径设计不易受来自其他内部源的串扰影响。信号通常以单端方式进入示波器。所有单端信号都在RF屏蔽之下,使用共面波导传送,使其与其他外部噪声源隔开。而一旦信号经过前置放大器,那么它会很快变成差分信号,然后才能脱离屏蔽区域。接地的共面波导是RF设计常用的一种路径选择技术。选择一条路径,然后在该路径的两侧放上接地层,从电路板到接地将过孔缝合,这可以防止信号受到任何其他外部噪声源的耦合影响。 另外,MSO6还特别注意内部屏蔽,尤其是前端,因为这才是真正的焦点。因此,Tek061前端放大器实现全包围的屏蔽层覆盖,这样既有助于实现优异的噪声性能,又有助于实现通道隔离,这也是这一代产品优于上一代产品的地方。实际上,与其他竞争对手的任何其他产品相比,我们的通道间隔离度都是非常好的。从低噪声Tek061前置放大器入手,然后防止内部的所有其他噪声源。我们研制出这种RF屏蔽,并特别注意其他通道的串扰,仪器内部其他噪声源,比如采集内存,噪声可能会很大,因此我们必须把它与采集内存屏蔽开。电源的距离要尽可能远,确保电源的噪声非常低。 五、电源的设计 干净的电源是数字电路稳定工作的前提,电源的纹波和噪声都会影响电源供应的质量,MSO6特别注重低噪声电源的设计,对电源信号进行了包含频谱分析在内的大量分析,对不同的杂散信号进行了详细的频域分析,然后着力解决掉这些问题。

AN2867 应用笔记 ST微控制器振荡器电路 设计指南 前言 大多数设计者都熟悉基于Pierce(皮尔斯)栅拓扑结构的振荡器,但很少有人真正了解它是如何工 作的,更遑论如何正确的设计。我们经常看到,在振荡器工作不正常之前,多数人是不愿付出 太多精力来关注振荡器的设计的,而此时产品通常已经量产;许多系统或项目因为它们的晶振 无法正常工作而被推迟部署或运行。情况不应该是如此。在设计阶段,以及产品量产前的阶 段,振荡器应该得到适当的关注。设计者应当避免一场恶梦般的情景:发往外地的产品被大批 量地送回来。 本应用指南介绍了Pierce振荡器的基本知识,并提供一些指导作法来帮助用户如何规划一个好的 振荡器设计,如何确定不同的外部器件的具体参数以及如何为振荡器设计一个良好的印刷电路 板。 在本应用指南的结尾处,有一个简易的晶振及外围器件选型指南,其中为STM32推荐了一些晶 振型号(针对HSE及LSE),可以帮助用户快速上手。

目录ST微控制器振荡器电路设计指南目录 1石英晶振的特性及模型3 2振荡器原理5 3Pierce振荡器6 4Pierce振荡器设计7 4.1反馈电阻R F7 4.2负载电容C L7 4.3振荡器的增益裕量8 4.4驱动级别DL外部电阻R Ext计算8 4.4.1驱动级别DL计算8 4.4.2另一个驱动级别测量方法9 4.4.3外部电阻R Ext计算 10 4.5启动时间10 4.6晶振的牵引度(Pullability) 10 5挑选晶振及外部器件的简易指南 11 6针对STM32?微控制器的一些推荐晶振 12 6.1HSE部分12 6.1.1推荐的8MHz晶振型号 12 6.1.2推荐的8MHz陶瓷振荡器型号 12 6.2LSE部分12 7关于PCB的提示 13 8结论14

辽宁工业大学 高频电子线路课程设计(论文)题目:石英晶体振荡器电路设计 院(系):电子与信息工程学院 专业班级: 学号: 学生姓名: 指导教师: 起止时间: 2014.6.16-2014.6.27

课程设计(论文)任务及评语 院(系):电子与信息工程学院 教研室: 电子信息工程 注:成绩:平时20% 论文质量50% 答辩30% 以百分制计算 学 号 学生姓名 专业班级 课程设计(论文)题目 石英晶体振荡器电路设计 课 程设计(论文)任务 要求:1.设计一个石英晶体振荡器 2.能够观察输入输出波形。 3.观察振荡频率。 参数:振荡频率10000HZ 左右。 设计要求: 1 .分析设计要求,明确性能指标。必须仔细分析课题要求、性能、指标及应用环境等,广开思路,构思出各种总体方案,绘制结构框图。 2 .确定合理的总体方案。对各种方案进行比较,以电路的先进性、结构的繁简、成本的高低及制作的难易等方面作综合比较,并考虑器件的来源,敲定可行方案。 3 .设计各单元电路。总体方案化整为零,分解成若干子系统或单元电路,逐个设计。 4 .组成系统。在一定幅面的图纸上合理布局,通常是按信号的流向,采用左进右出的规律摆放各电路,并标出必要的说明。 指导教师评语及成绩 平时成绩(20%): 论文成绩(50%): 答辩成绩(30%): 总成绩: 学生签字: 年 月 日

目录 第1章绪论 (1) 1.1石英晶体振荡器 (1) 1.2设计要求 (1) 第2章石英晶体振荡器设计电路 (2) 2.1石英晶体振荡器总体设计方案 (2) 2.2具体电路设计 (2) 2.2.1串联型晶体振荡器 (2) 2.2.2并联型晶体振荡器 (4) 2.2.3输出缓冲级设计 (5) 2.3元件参数的计算 (5) 2.4Multisim软件仿真 (6) 2.4.1串联型振荡器输出测试 (6) 2.4.2并联型振荡器输出测试 (7) 第3章课程设计总结 (9) 参考文献 (10) 附录Ⅰ总体电路图 (11) 附录Ⅱ元器件清单 (12)

一种低相噪恒温晶体振荡器的研制 【摘要】为了满足恒温晶体振荡器小型化的市场需求,应用低噪声电路设计原理和高精密控温技术,研制了一种小体积、低噪声、单层恒温晶体振荡器。产品的性能达到国内先进水平。 【关键词】相位噪声;热敏电阻;恒温晶体振荡器 恒温控制石英晶体振荡器(简称恒温晶振)的频率温度稳定度一般在±0.5ppm ~±0.005ppm的范围。它是各领域的中高端电子设备的频率源,它的技术水平和质量水平决定了电子设备的技术质量水平。 随着科学技术的发展,恒温晶振在民用和军用各领域的中、高端电子设备中获得了广泛应用。同时各领域的中、高端电子设备对其频率源恒温晶振的电性能和可靠性的要求越来越高,功耗和体积要求越来越小,这推动了恒温晶振设计技术的发展。恒温晶振用途不同,技术要求不同,设计也不同。该晶振难点是老化小,相噪低,主要技术指标如下:电源电压:12V,标称频率:10MHz,工作温度:-40~70℃,频率-温度稳定性:±1×10-8,老化率:≤±5×10-10/day,输出幅度:≥9dBm,单边带相位噪声:≤-150dBc/Hz@1kHz≤-160dBc/Hz@10kHz。 1.电路噪声分析 随着无线电技术的飞跃发展,雷达和通讯设备越来越先进,为了准确无误,对其核心元件晶体振荡器指标提出了更高的要求,特别是相位噪声要求更严。因此,国内外的专家在这方面做了大量工作。噪声主要有闪变噪声、白噪声和随机噪声。考虑到闪变过程依赖频率fγ,此处β限制在0>γ>-4,公式(1)给出了实际振荡器的相位噪声功率谱密度的模型为: Sφ(f)=k-3f-3+k-2f-2+k-1f-1+k0 (1) 式中系数kγ定义不同成分的噪声水平,其值决定单边带相位噪声?(f)=10log[0.5 SΦ(f)]的斜率。γ=0,-1,-2,-3,-4分别表示白噪声调相、闪变噪声调相、白噪声调频、闪变噪声调频和随机游动噪声。随机游动噪声主要与环境条件的影响有关。通常γ值如表1所示。 表1 γ值一览表 噪声类型γN Sφ(f)噪声系数 闪频噪声γ-3 k-3f-3 k-3=2α(f0/2Qe)2 白频噪声γ-2 k-2f-2 k-2=(4FNKT/PS)(f0/2Qe)

抖动分类与测量 李惠民力科公司华南区应用工程师 在现在的协议一致性测试中,“抖动”似乎已经成为了一个绕不开的名词,它是评估信号质量的一个关键指标。然而,各个通信协议对抖动似乎有着不同的要求,到底抖动的各个分量有什么意义呢?它们又是如何测量得到准确的结果呢?在系统设计中又该如何改善抖动指标呢?希望看完本文之后您能够得到一些帮助。 抖动的定义 过去,时钟频率只有10MHz。电路板或者封装设计的主要挑战就是如何自双层板上布通所有的信号线以及如何在组装时不破坏封装,在那个时代,数字信号基本上不需要考虑“信号质量”的;然而随着时钟频率的提高,信号周期和上升沿也已经普遍变短,这个时候,信号完整性就变得十分重要。特别的,当时钟频率超过1GHz时,由于时钟周期变短,“抖动”这个指标在信号质量也变得十分重要。 抖动是指信号与理想时钟之间的偏差[1]。如下面图1和图2两个时序中,可以明显看出,图2中信号与理想时钟之间偏差相对较图1比更大,若两个信号时钟频率相同,我们就可以说图2中的抖动比图1中大。 图1信号和理想时钟之间的偏差 图2更“大”的抖动 需要注意的是,抖动和频偏并不是不是相同的概念,一般讨论抖动是要在一段时间内实际信号和理想时钟之间速率相同或者相差很小的情况。图3中,这段

时间内,实际信号和理想时钟之间的频率偏差约为7%,一般来说我们讨论抖动的时候频偏不会超过5000ppm(即0.5%),图3这种情况不再我们的讨论范围之内。 图3“频偏”并不是我们所讨论的抖动 另外,抖动的绝对值在有些情况下参考意义并不太大。假若是10MHz的时钟频率,每个周期为100ns,1ns的抖动似乎对信号没有太大的影响。然而当频率为500MHz时,1ns的抖动就很的能会影响信号信号质量,使得信号在传输过程在出现误码。所以我们在很多情况下会用UI这个相对单位;1UI即为1个时钟周期所花费的时间。若信号的时钟周期为10MHz时,1UI对应为100ns。相应的还有mUI,1mUI即0.001UI。相对单位比绝对时间单位更能看出抖动对信号质量的影响。 抖动的分类 在说抖动分类之前,首先我想说一下源同步与时钟恢复技术。想必大家在学习和使用单片机的时候应该对同步通信和异步通信有比较深刻的认识;同步通信的典型代表就是SPI,特点就是同时传送时钟和数据;异步通信的经典代表是UART,只需要两根线就可以实现全双工。源同步和SPI类似,在通信的时候同时传输时钟和数据,但是高速的时钟信号在传输过程中衰减很大,而且容易引起EMI,所以一般会对同步时钟进行分频,源同步的代表有HDMI,其时钟频率是信号速率的1/10。时钟恢复技术可以在串行数据中提取出时钟,然后用恢复出来的时钟对信号进行采样,克服异步通信中由于不同源带来的的频偏和抖动,时钟恢复的代表有USB,万兆以太网等。 首先,我们需要明确的一点就是——抖动是时间的函数,确切的来说,抖动是和时钟周期相关的。 在讨论抖动分类的时候,我们一般会从三个维度去讨论。 从关注抖动参数的类型,可以分成TIE(Time interval error),Period

1.课程设计的目的 (3) 2.课程设计的内容 (3) 3.课程设计原理 (3) 4.课程设计的步骤或计算 (5) 5.课程设计的结果与结论 (11) 6.参考文献 (16)

一、设计的目的 设计一个晶振频率为20MHz,输出信号幅度≥5V(峰-峰值),可调的晶体振荡器 二、设计的内容 本次课程设计要求振荡器的输出频率为20Mhz,属于高频范围。所以选择LC振荡器作为参考对象,再考虑输出频率和振幅的稳定性,最终选择了克拉泼振荡器。通过ORCAD 的设计与仿真,Protel绘制PCB版图,得到了与理论值比较相近的结果,这表明电路的原理设计是比较成功的,本次课程设计也是比较成功的。 三、设计原理 1.振荡器的概述 在电子线路中,除了要有对各种电信号进行放大的电子线路外,还需要有在没有激励信号的情况下产生周期性振荡信号的电子线路,这种电子线路就是振荡器。 振荡器是一种能量转换器,它不需要外部激励就能自动地将直流电源共给的功率转换为制定频率和振幅的交流信号功率输出。振荡器一般由晶体管等有源器件和某种具有选频能力的无源网络组成。 振荡器的种类很多,根据工作原理可分为反馈型振荡器和负阻型振荡器,根据所产生的波形可分为正弦波振荡器和非正弦波振荡器;根据选频网络可分为LC振荡器﹑晶体振荡器﹑RC振荡器等。 2.振荡器的振荡条件 反馈型振荡器的原理框图如下:

图1.1 反馈型振荡器的原理框图 如图1,放大器的电压放大倍数为K(s),反馈网络的电压反馈系数为F(s),则闭环电压放大倍数Ku(s)的表达式为[1]: K u (s)= ) () (s Us s Uo ( 1—1) 由 K(s)= ) () (s Ui s Uo (1—2) F(s)=) ()(s Uo s i U ' (1—3) U i(s)=U s (s)+)(s i U ' (1—4) 得 K u (s)= )()(1)(s F s K s K -=) (1) (s T s K - (1—5) 其中T(s)=K(s)F(s)= ) () (s Ui s i U ' (1—6) 称为反馈系统的环路增益。用s=j ω带入就得到稳态下的传输系数和环路增益。由式(1—5)可知,若在某一频率ω=ω1上T(j ω),Ku (j ω)将趋近于无穷大,这表明即使没有外加信号,也可以维持振荡输出。因此自激振荡的条件就是环路增益为1,即 T(j ω)=K(j ω)F((j ω)=1 (1—7) 通常称为振荡器的平衡条件。 由式(1—6)还可知|T(j ω)|>1,|)(ωj i U '|>|Ui (j ω)|,形成增幅振荡。 |T(j ω)|<1, |)(ωj i U '|<|Ui (j ω)|,形成减幅振荡。 综上,正弦波振荡器的平衡条件为: T(j ω)=K(j ω)F((j ω)=1 也可表示为|T(j ω)|=KF=1 (1—8a)

晶体振荡器的工作原理 上网时间:2008-11-04 中心论题: ?石英晶体振荡器基本原理 ?石英晶体振荡器类型特点 ?石英晶体振荡器主要参数 ?石英晶体振荡器发展趋势及其应用 解决方案: ?石英晶体振荡器有小型化、薄片化、片式化、高精度、高稳定度、低噪声、高频化趋势 ?广泛应用于石英钟、电视行业、通信系统产品 石英晶体振荡器是高精度和高稳定度的振荡器,被广泛应用于彩电、计算机、遥控器等各类振荡电路中,以及通信系统中用于频率发生器、为数据处理设备产生时钟信号和为特定系统提供基准信号。 石英晶体振荡器的基本原理 石英晶体振荡器的结构 石英晶体振荡器是利用石英晶体(二氧化硅的结晶体)的压电效应制成的一种谐振器件,它的基本构成大致是:从一块石英晶体上按一定方位角切下薄片(简称为晶片,它可以是正方形、矩形或圆形等),在它的两个对应面上涂敷银层作为电极,在每个电极上各焊一根引线接到管脚上,再加上封装外壳就构成了石英晶体谐振器,简称为石英晶体或晶体、晶振。其产品一般用金属外壳封装,也有用玻璃壳、陶瓷或塑料封装的。 压电效应 若在石英晶体的两个电极上加一电场,晶片就会产生机械变形。反之,若在晶片的两侧施加机械压力,则在晶片相应的方向上将产生电场,这种物理现象称为压电效应。如果在晶片的两极上加交变电压,晶片就会产生机械振动,同时晶片的机械振动又会产生交变电场。在一般情况下,晶片机械振动的振幅和交变电场的振幅非常微小,但当外加交变电压的频率为某一特定值时,振幅明显加大,比其他频率下的振幅大得多,这种现象称为压电谐振,它与LC回路的谐振现象十分相似。它的谐振频率与晶片的切割方式、几何形状、尺寸等有关。 符号和等效电路 当晶体不振动时,可把它看成一个平板电容器称为静电电容C,它的大小与晶片的几何尺寸、电极面积有关,一般约几个PF到几十PF。当晶体振荡时,机械振动的惯性可用电感L 来等效。一般L的值为几十mH 到几百mH。晶片的弹性可用电容C来等效,C的值很小,一般只有0.0002~0.1pF。晶片振动时因摩擦而造成的损耗用R来等效,它的数值约为100Ω。由于晶片的等效电感很大,而C很小,R也小,因此回路的品质因数Q很大,可达1000~10000。加上晶片本身的谐振频率基本上只与晶片的切割方式、几何形状、尺寸有关,而且可以做得精确,因此利用石英谐振器组成的振荡电路可获得很高的频率稳定度。 谐振频率 从石英晶体谐振器的等效电路可知,它有两个谐振频率,即(1)当L、C、R支路发生串联谐振时,它的等效阻抗最小(等于R)。串联揩振频率用fs表示,石英晶体对于串联揩振频率fs呈纯阻性,(2)当频率高于fs时L、C、R支路呈感性,可与电容C。发生并联谐振,

**科技大学 课程设计报告 课程名称:高频电路课程设计 设计名称:晶体振荡器的设计与制作 姓名: 学号: 班级:电子1002班 指导教师: 起止日期:2012.12.24-2013.1.6 西南科技大学信息工程学院制

课程设计任务书 学生班级:电子1002班学生姓名:学号: 设计名称:晶体振荡器的设计与制作 起止日期:2012.12.24-2013.1.6指导教师: 课程设计学生日志

课程设计评语表

晶体振荡器的设计与制作 一、设计目的和意义 振荡器是一种能量转换器,它不需要外部激励就能自动地将直流电源共给的功率转换为制定频率和振幅的交流信号功率输出,凡是能完成这一功能的装置都可以作为振荡器。振荡器一般由晶体管等有源器件和某种具有选频能力的无源网络组成。 石英晶体振荡器(quatrz oscillator),是利用具有压电效应的石英晶体片制成的。这种石英晶体薄片受到外加交变电场的作用时会产生机械振动,当交变电场的频率与石英晶体的固有频率相同时,振动便变得很强烈,这就是晶体谐振特性的反应。利用这种特性,就可以取代LC(线圈和电容)谐振回路、滤波器等。石英谐振器具有体积小、重量轻、可靠性高、频率稳定度高等优点,被应用于家用电器和通信设备中。石英谐振器因具有极高的频率稳定性,故主要用在要求频率十分稳定的振荡电路中作谐振元件。 本设计对利用石英晶体构成振荡器的方法做了较深入的研究,对振荡器的原理及石英晶体振荡器原理做了详细的介绍并通过Multisim 11.0软件设计、仿真出并联的石英晶体振荡器,最后按照原理图进行调试和参数的计算。 二、设计原理 1、反馈振荡器振荡的基本原理 2、振荡器的条件 a)、起振条件——保证接通电源后能逐步建立起振荡 反馈电压幅度必须大于输入电压幅度,即: T(ω0)>1 反馈电压相位必须与放大器输入相位相同——正反馈。 φT=2n∏ b)、平衡条件——保证进入维持等幅持续振荡的平衡状态 T(ω0)=1 φT=2n∏ c)、稳定条件——保证平衡状态不因外界不稳定因素影响而受到破坏 在ω0附近T(ω0)的变化率为负值 在ω0附近相位的变化率为负值

第二章石英晶体振荡器 晶体振荡器 上图是经过简化的电路图并表明了石英晶体振荡器的基本组成元件。石英晶体振荡器中的放大器由至少一个驱动设备,偏压电阻并且可能包含其他用来限制带宽,阻抗匹配和增益控制的元件组成。反馈网络由石英晶体谐振器,和其他元件比如用来协调的可变电容等组成。 晶体振荡器特点 z在振荡频率上,闭合回路的相移为2nπ。 z当开始加电时,电路中唯一的信号是噪声。满足振荡相位条件的频率噪声分量以增大的幅度在回路中传输,增大的速率由附加分量,即小信号,回路益增和晶体网络 的带宽决定。 z幅度继续增大,直到放大器增益因有源器件(自限幅)的非线性而减小或者由于某一自动电平控制而被减小。 z在稳定状态下,闭合回路的增益为1。

振荡与稳定度 z 如果产生相位波动?Δ,频率必然产生偏移f Δ,以维持πn 2的相位条件。对于串 联谐振振荡器,L Q f f 2//?Δ?=Δ,是网络中晶体的负载值Q 值。 “相位斜率”L Q df d /?是与靠近串联谐振频率的成正比的(见第三部分“等效电路”和“频率与电抗的关系”)。 L Q z 大多数振荡器均工作在“并联谐振”上,电抗与频率斜率的关系,即“逆 电容”是与晶体器件的动态电容C1成反比的。 df dx /z 相对于振荡回路中的相位(电抗)波动的最高频率稳定度来说,相位斜率(或电抗 斜率)必须最大,即C1应当最小,而应当最大。石英晶体器件的高值和高的逆电容,决定振荡器元件的基本频率(或频率稳定度)。 L Q Q 可调性和稳定度 要使振荡器谐调在宽的频率范围内,就会降低其稳定度,因为要使振荡器按要求进行调谐,同时也会使振荡器容易受不合要求的调谐因素影响。调谐范围越宽,就越难以保持高的稳定度。例如,如果设计OCXO 的短期稳定度在某一平均时间为1×10-12,而可调性为1×10-7,则晶体的负载电抗在上述平均时间必须稳定在上1×10-5。要获得这样的稳定度使困难的,因为影响负载电抗的因素有:寄生电容和电感、变容二极管的电容与电压特性的稳定度,以及加在变容二极管上的电压的稳定度。此外,1×10-5的负载电抗稳定度不仅必须在开始条件下保持,而且在环境条件(温度、振动、辐射等)变化时,也必须保持。 同时,高稳定度10 MHz 的恒温压控晶振的频率调整范围为5×10-7,老化率为2×10-8/y ,而宽调谐范围的10 MHz 压控晶振的调谐范围为50 ppm ,老化率为2 ppm/y 。 振荡器的缩写 经常使用的 其他 XO ………… 晶体振荡器 VCXO ………压控晶体振荡器 OCXO ………恒温控制晶体振荡器 TCXO ………温度压控晶体振荡器 TCVCXO ……温度补偿压控晶体振荡器OCVCXO ……恒温控制压控晶体振荡器MCXO ………微机补偿晶体振荡器 RbXO ………铷晶体振荡器 从历史上来说,在美国,军事上的需求已成为研究石英振荡器的主要推动力。特别是在早期美国军方资助大部分的研究。按照民间说法,缩写XO 代替CO 的主要原因是,在美国军队里,CO 是“指挥官”的缩写而且由于“crystal ”听起来有点象“xtal ”。(随后,有人指

高级抖动溯源分析方法 安捷伦科技(中国)有限公司孙灯亮 抖动的定义及和相位噪声和频率噪声的关系 抖动是数字系统的信号完整性测试的核心内容之一,是时钟和串行信号的最重要测量参数(注:并行总线的最重要测量参数是建立时间和保持时间)。 一般这样定义抖动:“信号的某特定时刻相对于其理想时间位置上的短期偏离为抖动”(参考:Bell Communications Research,Inc(Bellcore),"Synchrous Optical Network(SONET) Transport Systems:Common Generic Criteria, TR-253-CORE",Issue 2, Rev No.1, December 1997".如图1所示。其中快过10HZ的偏离定义为抖动(Jitter),漫过10Hz的偏离定义为漂 移(Wander)。 图1. 时钟和数据抖动的定义 抖动和相位噪声和频率噪声有什么关系呢? 图2.抖动和相位噪声和频率噪声的关系

抖动成分的分解及各个抖动成分的特征及产生原因 随着信号速率的不断提高和对精度的越来越高要求,需要进行抖动成分的分离以更深入表征抖动特征和查找问题根源。一般按图3进行抖动成分的分离。 图3.抖动成分分离图 各个英文的中文翻译如下。 Total Jitter(TJ):总体抖动; Random Jitter(RJ):随机抖动; Deterministic Jitter(DJ):确定性抖动; Data Dependent Jitter(DDJ):数据相关抖动; Periodic Jitter(PJ):周期性抖动; Inter-symbol Interference(ISI):码间干扰 Duty Cycle Distortion(DCD):占空比失真; Sub Rate Jitter(SRJ):子速率抖动。 下面分别讨论每种抖动成分的特征和产生原因。 1、随机抖动RJ 随机抖动是不能预测的定时噪声,因为它没有可以识别的模式。典型的随机噪声实例是在无线电接收机调谐到没有活动的载频时听到的声音。尽管在理论上随机过程具有任意概率分布,但我们假设随机抖动呈现高斯分布,以建立抖动模型。这种假设的原因之一是,在许多电路中,随机噪声的主要来源是热噪声(也称为Johnson 噪声或散粒噪声),而热噪声呈现高斯分布。另一个比较基础的原因是,根据中心极限定理,不管各个噪声源采用什么分布,许多不相关的噪声源的合成效应该接近高斯分布。高斯分布也称为正态分布,但它的一个最重要的特点是:对高斯变量,它可以达到的峰值是无穷大。尽管这种随机变量的大多数样本将会聚集在中间值的周围,但在理论上,任何单一的样本,它可以偏离中间值任意大的量。所以,高斯分布都没有峰到峰边界值,从这种分布中的样本数越多,所测得的峰到峰值将越大。所以,我们用stdev或RMS(均方差)值来衡量随机抖动RJ。 2、确定性抖动DJ 确定抖动是可以重复的、可以预测的定时抖动。正因如此,这个抖动的峰到峰值具有上下限,在数量相对较少的观察基础上,通常可以以高置信度观察或预测其边界。DDJ和PJ 根据抖动特点和根本成因进一步细分了这类抖动。确定性抖动和随机抖动在统计图上可以用图4形象化表示。