7.软件初始化和配置

PCIE 配置模型支持两种配置空间访问机制:

1.PCI兼容配置访问机制(CAM)

2.PCIE 增强的配置访问机制(ECAM)

7.1.配置拓扑结构

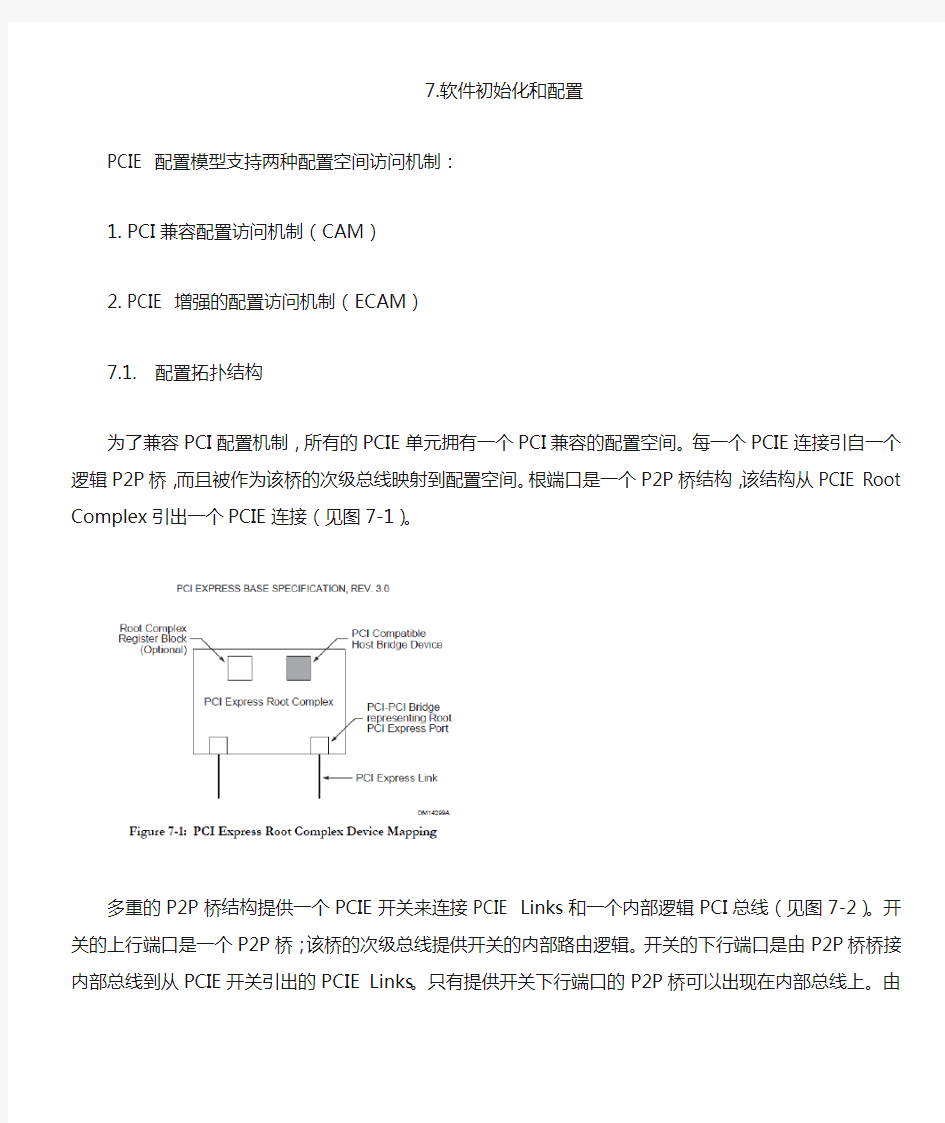

为了兼容PCI配置机制,所有的PCIE单元拥有一个PCI兼容的配置空间。每一个PCIE连接引自一个逻辑P2P 桥,而且被作为该桥的次级总线映射到配置空间。根端口是一个P2P桥结构,该结构从PCIE Root Complex引出一个PCIE连接(见图7-1)。

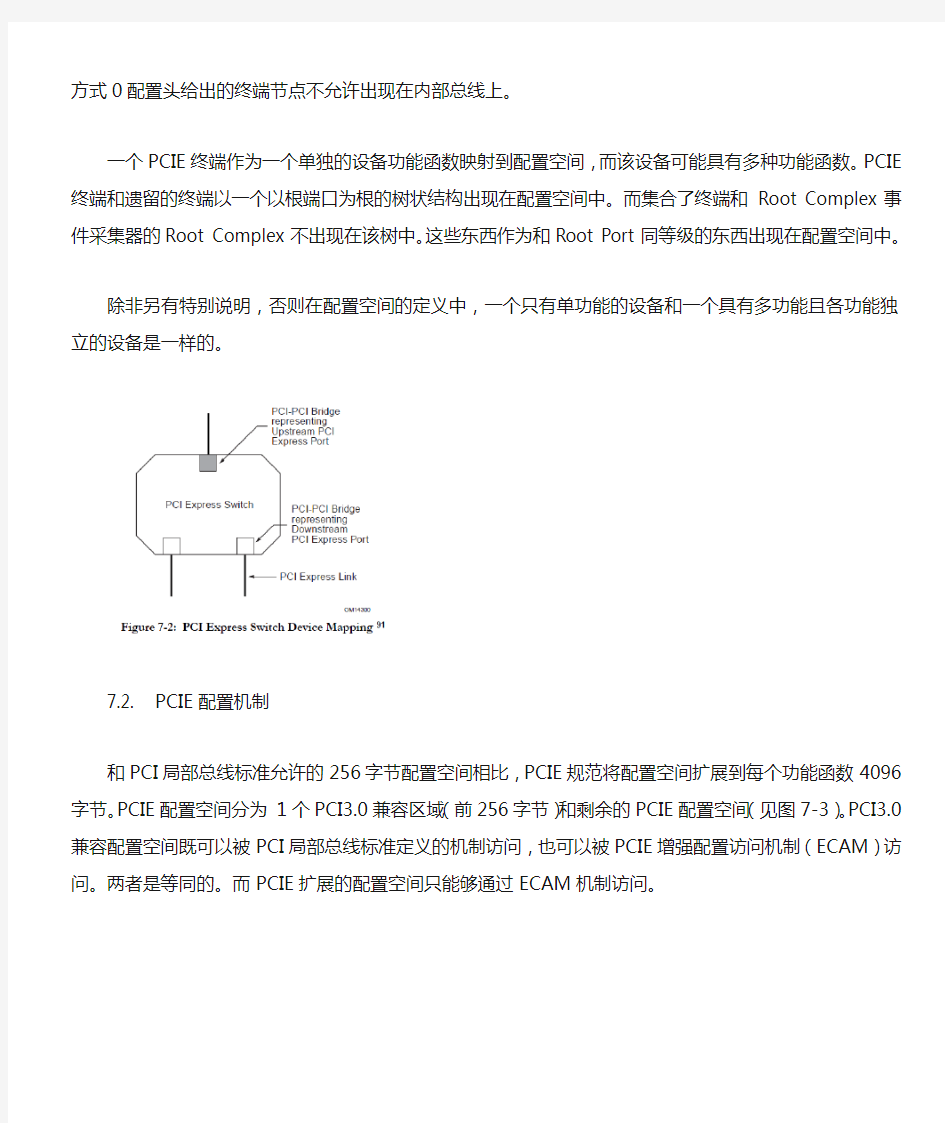

多重的P2P桥结构提供一个PCIE开关来连接PCIE Links和一个内部逻辑PCI总线(见图7-2)。开关的上行端口是一个P2P桥;该桥的次级总线提供开关的内部路由逻辑。开关的下行端口是由P2P桥桥接内部总线到从PCIE 开关引出的PCIE Links。只有提供开关下行端口的P2P桥可以出现在内部总线上。由方式0配置头给出的终端节点不允许出现在内部总线上。

一个PCIE终端作为一个单独的设备功能函数映射到配置空间,而该设备可能具有多种功能函数。PCIE终端和遗留的终端以一个以根端口为根的树状结构出现在配置空间中。而集合了终端和Root Complex事件采集器的Root Complex不出现在该树中。这些东西作为和Root Port同等级的东西出现在配置空间中。

除非另有特别说明,否则在配置空间的定义中,一个只有单功能的设备和一个具有多功能且各功能独立的设备是一样的。

7.2. PCIE配置机制

和PCI局部总线标准允许的256字节配置空间相比,PCIE规范将配置空间扩展到每个功能函数4096字节。PCIE 配置空间分为1个PCI3.0兼容区域(前256字节)和剩余的PCIE配置空间(见图7-3)。PCI3.0兼容配置空间既可以被PCI局部总线标准定义的机制访问,也可以被PCIE增强配置访问机制(ECAM)访问。两者是等同的。而PCIE扩展的配置空间只能够通过ECAM机制访问。

7.2.1.PCI3.0 兼容配置机制

PCI3.0兼容PCIE配置机制支持在PCI局部总线规范中定义的PCI配置空间编程模型。通过依附于这个模型,系统纳入支持传统PCI总线枚举和配置软件的PCIE接口。

和PCI3.0一样,PCIE设备功能函数也被要求提供一个用于驱动软件初始化和配置的配置空间。

PCI3.0兼容配置访问机制使用和ECAM相同的“请求”格式。对于PCI兼容配置请求,扩展的寄存器地址区域必须为0。.

7.2.2.PCIE 增强的配置访问机制(ECAM)

ECAM使用一个平坦内存映射的地址空间来访问设备配置寄存器。在这种情况下,配置寄存器的访问、内存数据刷新、返回寄存器的内容等操作都是在内存中完成的。PCIE配置空间在内存中的映射地址在表7-1中定义。

映射空间的大小和基址由host桥和固件决定。由硬件在“应用规范”行为中向操作系统汇报。总线范围的大小由host桥映射到Bus Number field在配置地址空间中的二进制位数决定的。在表7-1中,二进制位数表示为n,n 取值1~8。一个映射了n个内存地址位的host桥支持0~2n-1个总线,除此之外,范围的基址要和2(n+20)-byte memory address bounary。任何在Bus Number field中没有映射到内存地址的位必须被清零。

例如,如果一个系统映射了3个内存地址位到Bus Number field,如下可得:

1.n = 3;

2.地址位A[63:23]被用作基地址,和223-byte(8-MB)对齐;

3.地址位A[22:20]被映射到Bus Number field的[2:0];

4.Bus Number field 的[7:3]位被清零;

5.除此之外,系统可以寻址的总线号在0~7之间。

内存地址位至少要为1(n=1)。一个4GB的内存最好映射8位内存地址(n = 8)。

7.3.配置处理规则

7.3.1.设备号

对于非ARI设备,PCIE部件被约束在它们的接口(上行端口)上使用单一的设备号,但是被允许使用高达8个独立的功能函数。每一个内部的功能通过译码地址信息(配置请求包的一部分)选中。

没有ARI Forwarding使能的下行端口必须只能关联局部总线的0号设备。目标为0号设备的配置请求包将被送往该设备;而其他设备(1-31)必须被开关的下行端口或者由一个“不支持的请求状态”信号(等同于PCI的Master Abort)激发根端口终结。

想要在它们的上行端口并入超过8个功能函数的开关和部件,被允许使用一个或多个“虚拟开关”,这种开关由P2P桥方式1配置头提供。这些虚拟开关允许超过8个功能。鉴于开关下行端口被允许出现在任何设备号上,在这种情况下,所有的地址信息区域(Bus,Device,Function Numbers)必须完全译码为正确的寄存器地址。任何命中一个未使用的地址的配置请求,都会产生一个“不支持的请求完成状态”。

7.3.2.配置处理寻址

PCIE配置请求使用如下寻址区域:

1.Bus Number ——PCIE 将局部PCI总线号映射到PCIE Links,从而PCI3.0兼容配置软件视PCIE配置树等

同于PCI配置树。

2.Device Number ——当一个ARI设备被命中时,它之上的下行端口将ARI Forwarding使能,设备号被设置

为0,传统的设备号区域被用来代替8位的功能号区域。

3.Function Number ——PCIE和PCE3.0一样支持使用相同的发现机制发现多功能设备。而ARI设备,发现

和枚举其扩展功能需要ARI-aware软件。

4.Extended Register Number and Register Number ——指明了配置空间寄存器的访问地址。

7.3.3.配置请求路由规则

对于终端来说,应用下面的规则:

1.如果配置请求类型为1,遵从“控制不支持的请求”规则;

2.如果配置请求类型为0,判断请求的地址空间是否有效?如果有效,则处理请求;否则遵从“控制不支持的

请求”规则。

对于根端口,开关和PCIE-PCI桥,应用如下规则:

1.如果peer-to-peer的从下行到上行的配置请求不被支持,则配置请求只能由Host桥初始化。

2.如果配置请求类型为0,判断请求地址是否有效?如果有效,处理请求;否则遵从“控制不支持的请求”规

则。

3.如果配置请求类型为1,按顺序执行如下对Bus Number和Device Number 区域的测试:

(1)此处省略几百字。。。。。

7.3.4.PCI 特别循环

PCIE不直接支持PCI Special Cycle。PCI Special Cycle 可以在PCIE-PCI桥使用方式1配置循环的情况下被导向PCI总线段。

7.4.配置寄存器类型

配置寄存器区域被分配了不同的属性,如表7-2所示。所有的PCIE部件,除了Root Complexes和系统集成的设备,都将寄存器区域初始化为特定的值。Root Complexes和系统集成设备按照硬件的要求初始化寄存器。

7.5.PCI兼容配置寄存器

PCIE配置空间的前256字节是PCI3.0的兼容区域。遗留的PCI设备也可以被ECAM访问,而不用去改变设备硬件或驱动程序。

7.5.1.类型0和类型1普通配置空间

图7-4详细展示了PCI3.0类型0和类型1配置头的普通寄存器区域,这些同样用在PCIE设备功能。

这些寄存器被类型0和类型1配置头定义。

https://www.doczj.com/doc/266861108.html,mand Register (Offset 04h)