1、IEEE标准的硬件描述语言是Verilog HDL和VHDL共同点是:能够形式化地抽象表示电路的行为和结构;支持逻辑设计中层次与范围的描述:可借用高级语言的精巧结构来简化电路行为的描述:具有电路仿真与验证机制以保证设计的正确性;支持电路描述由高层到低层的综合转换;硬件描述与实现工艺无关;便于文档管理;易于理解和设计重用。

不同点:Verilog HDL是一种非常容易掌握的硬件描述语言,而VHDL掌握起来就比较困难。

2、把功能经过验证的、可综合的、实现后电路结构总门数在5000门以上的Verilog HDL模型称之为“软核”。把在某一种现场可编程门阵列(FPGA)器件上实现的、经验证是正确的、总门数在5000门以上电路结构编码文件称为“固核”。把在某一种专用集成电路工艺的(ASIC)器件上实现的、经验证是正确的、总门数在5000门以上电路结构版图掩膜称为“硬核”。

3、什么叫综合?通过综合产生的是什么?通过综合工具把行为级描述的模块通过逻辑网表自动转化为门级形式的模块叫综合。综合由EDA工具来完成。产生的是由与门,或门和非门组成的加法器,比较器等组合逻辑。产生的模块很容易与某种工艺的基本元件逐一对应起来,再通过布局布线工具自动地转变为某种工具工艺的电路布线结构。

4、仿真可以在几层面上进行?每个层面的仿真有什么意义?

分别为:前仿真,逻辑网表仿真,门级仿真和布线后仿真。

前仿真,逻辑网表仿真,门级仿真:可以调试和验证逻辑系统的设计和结构准确与否,并发现问题及时修改。布线后仿真:分析设计的电路模块的运行是否正常。

5、模块由描述接口和描述逻辑功能两部分组成。

6、端口分为三种:输入口、输出口、输入/输出口。

7、reg型和wire型变量的差别是什么?reg型变量是寄存器型变量,wire型变量是连线型变量。两者根本性的差别在于reg型变过量有个寄存器来存放变量,这个值只有变量发生改变时才会改变否则保证原来的值不变,wire型变量的值不是确定的值。

8、由连续赋值语句assign赋值的变量能否是reg类型的?可以是reg类型的变量。

9、在always模块中被赋值的变量能否是wire类型的?如果不能,那么必须是什么类型的?它们表示的一定是实际的寄存器吗?

不能。必须是reg类型的变量。他们表示的不一定是实际的寄存器。

10、参数类型的变量有什么用处?好处是可以提高程序的可读性和可维护性。

11、逻辑运算符与按位逻辑运算符有什么不同?用逻辑运算符时是两个操作数进行逻辑运算,而按位逻辑运算符运算时是两个操作数对应的每一位进行逻辑运算。逻辑运算符多用于条件的判断,按位逻辑运算符用于信号的运算和检测。

12、拼接符的作用是什么?为什么说合理地使用拼接符可以提高程序的可读性和可维护性?拼接符的作用是把两个或多个信号的某些位拼接起来进行运算操作。因为借助拼接符可以用一个符号名来表示由多位信号组成的复杂信号。其物理意义是将多个信号结合成一个信号。

13、如果都不带时间延迟,阻塞和非阻塞赋值有什么不同?

阻塞和非阻塞赋值的区别在阻塞时顺序执行而非阻塞时并行执行。举例:

非阻塞赋值:always@(posedge clk) begin b<=a; c<=b; end

阻塞赋值:always@(posedge clk) begin b=a; c=b; end

两种不同的赋值方式结果是不同的。非阻塞赋值中两条语句同时执行,结果是b=a,c=b。而阻塞赋值两条语句是逐条执行的,先执行b=a后执行c=b,结果是c=b=a。

14、不断活动与不断执行有什么不同?

不断活动是always语句不断活动检查是否满足条件(如某个信号发生改变),不断执行时always语句引导的过程中的语句不断的执行着。

15、简单叙述任务和函数的不同点。

(1)函数只能与主模块共用同一个仿真时间单元,而任务可以定义自己的仿真时间单位;

(2)函数不能启动任务,而任务能启动其它任务和函数;

(3)函数至少要有一个输入变量,而任务可以没有或有多个任何类型的变量;

(4)函数返回一个值,而任务则不返回值。

16、什么是综合?是否任何符合语法的Verilog HDL程序都可以综合?

通过综合器把HDL程序转化成标准的门级结构网表。不是。

17、有限状态机分为哪两类?有何区别?分为Moore型和Mealy型两类。Moore型其时序逻辑输出仅与当前状态有关;Mealy型其时序逻辑输出不但取决于状态还取决于输入。18、什么是同步复位,什么是异步复位,两者的区别是什么?

同步复位只有在时钟沿到来时复位信号才起作用。异步复位只要有复位信号系统马上复位。同步复位的复位信号持续的时间应该超过一个时钟周期才能保证系统复位。异步复位抗干扰能力差,有些噪声也能使系统复位,因此有时候显得不够稳定,要想设计一个好的复位最好使用异步复位同步释放,而且复位信号低电平有效。

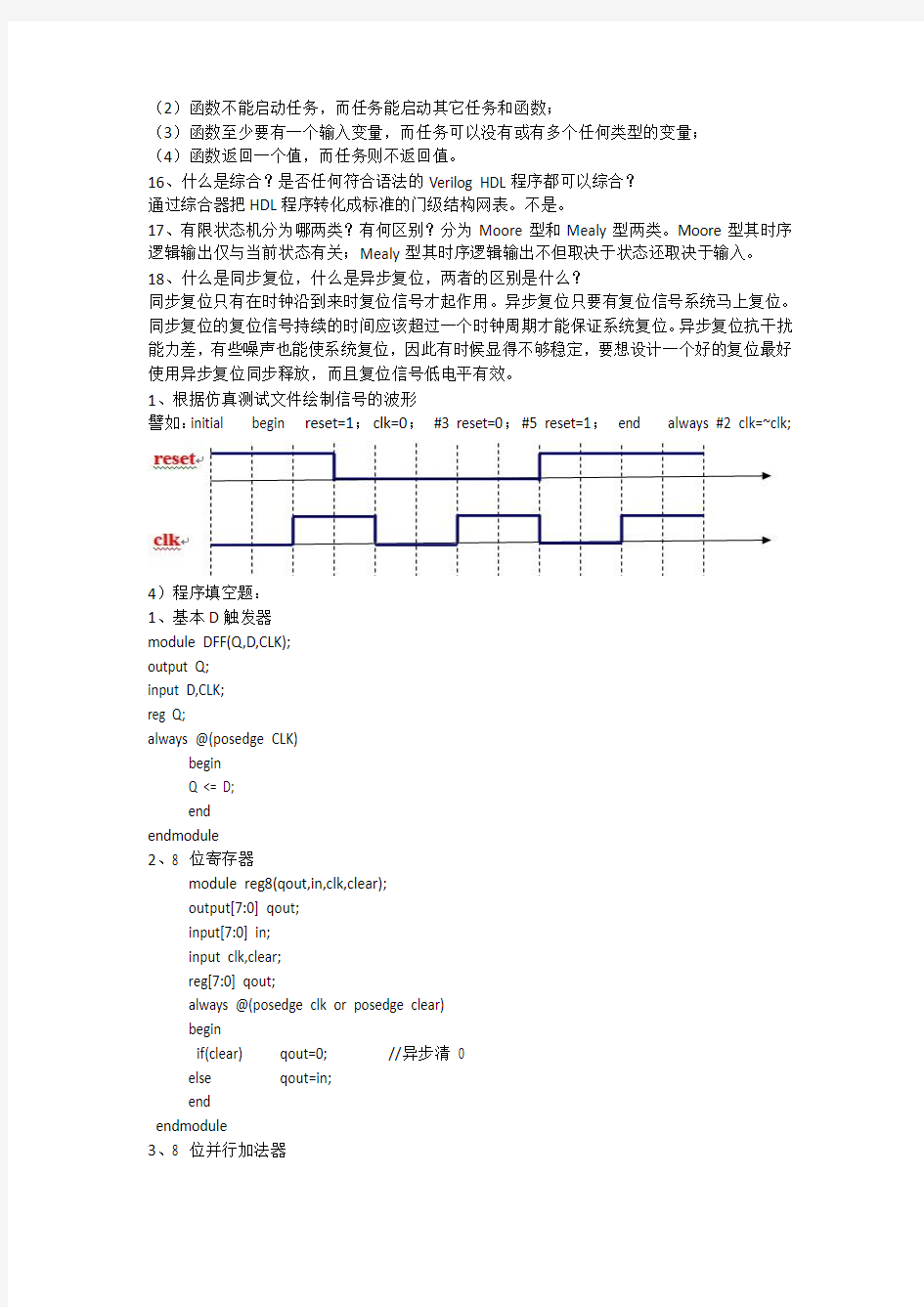

1、根据仿真测试文件绘制信号的波形

譬如:initial begin reset=1;clk=0;#3 reset=0;#5 reset=1;end always #2 clk=~clk;

4)程序填空题:

1、基本D触发器

module DFF(Q,D,CLK);

output Q;

input D,CLK;

reg Q;

always @(posedge CLK)

begin

Q <= D;

end

endmodule

2、8 位寄存器

module reg8(qout,in,clk,clear);

output[7:0] qout;

input[7:0] in;

input clk,clear;

reg[7:0] qout;

always @(posedge clk or posedge clear)

begin

if(clear) qout=0; //异步清0

else qout=in;

end

endmodule

3、8 位并行加法器

module add_bx(cout,sum,a,b,cin);

output[7:0] sum;

output cout;

input[7:0] a,b;

input cin;

assign {cout,sum}=a+b+cin;

endmodule

4、8 位并行乘法器

module mult(outcome,a,b);

parameter size=8;

input[size:1] a,b; //两个操作数

output[2*size:1] outcome; //结果

assign outcome=a*b; //乘法运算符

endmodule

5、多路器

①持续赋值方式定义的2 选 1 多路选择器

module MUX21_1(out,a,b,sel);

input a,b,sel;

output out;

assign out=(sel==0)?a:b; //持续赋值,如果sel为0,则out=a ;否则out=b endmodule

②阻塞赋值方式定义的2 选 1 多路选择器

module MUX21_2(out,a,b,sel);

input a,b,sel;

output out;

reg out;

always@(a or b or sel)

begin

if(sel==0) out=a; //阻塞赋值

else out=b;

end

endmodule

③module mux(out,a,b,sel)

output out;

input a,b,sel;

assign out=sel?a:b;

endmodule

④行为级描述的四选一多路选择器

module mux4_to_1(out,i0,i1,i2,i3,s1,s0);

input i0,i1,i2,i3,s1,s0;

output out;

reg out;

always @(s1 or s0 or i0 or i1 or i2 or i3)

begin

case({s1,s0})

2’b00:out=i0;

2’b01:out=i1;

2’b10:out=i2;

2’b11:ou t=i3;

default:out=1’bx;

endcase

end

endmodule

6、比较器

①module compare_n(X,Y,XGY,XSY,XEY); input [width-1:0] X,Y;

output XGY,XSY,XEY;

reg XGY,XSY,XEY;

parameter width=8;

always@(X or Y)

begin

if(X==Y)

XEY=1;

else XEY=0;

if(X>Y)

XGY=1;

else XGY=0;

if(X XSY=1; else XSY=0; end endmodule ②module compare(equal,a,b); Parameter size=1; output equal; input [size-1:0]a,b; assign aqual=(a==b)?1:0; endmodule 7、3-8译码器 ①module decoder_38(out,in); output[7:0] out; input[2:0] in; reg[7:0] out; always @(in) begin case(in) 3'd0: out=8'b11111110; 3'd1: out=8'b11111101; 3'd2: out=8'b11111011; 3'd3: out=8'b11110111; 3'd4: out=8'b11101111; 3'd5: out=8'b11011111; 3'd6: out=8'b10111111; 3'd7: out=8'b01111111; endcase end endmodule ②module decoder(out,in); output[7:0]out; input [2:0]in; assign out=1’b1< endmodule 8、8-3编码器 module encoder8_3(none_on,outcode,a,b,c,d,e,f,g,h); output none_on; output[2:0] outcode; input a,b,c,d,e,f,g,h; reg[3:0] outtemp; assign {none_on,outcode}=outtemp; always @(a or b or c or d or e or f or g or h) begin if(h) outtemp=4'b0111; else if(g) outtemp=4'b0110; else if(f) outtemp=4'b0101; else if(e) outtemp=4'b0100; else if(d) outtemp=4'b0011; else if(c) outtemp=4'b0010; else if(b) outtemp=4'b0001; else if(a) outtemp=4'b0000; else outtemp=4'b1000; end endmodule 9、8位数据锁存器 module latch_8(qout,data,clk); output[7:0] qout; input[7:0] data; input clk; reg[7:0] qout; always @(clk or data) begin if (clk) qout<=data; end endmodule 10、奇偶检验位生成器 module parity(even_bit,odd_bit,input_bus); output even_bit,odd_bit; input[7:0] input_bus; assign odd_bit = ^ input_bus; //产生奇校验位 assign even_bit = ~odd_bit; //产生偶校验位 endmodule 11、三态输出驱动器 ①module trist(out,in,enable); output out; input in,enable; assign out=enable?in:’bz; endmodule ②module trist(out,in,enable); output out; input in,enable; bufifl mybufl(out,in,enable); endmodule 12、8位移位寄存器 module shifter(din,clk,clr,dout); input din,clk,clr; output[7:0] dout; reg[7:0] dout; always @(posedge clk) begin if (clr) dout<= 8'b0; //同步清0,高电平有效 else begin dout <= dout << 1; //输出信号左移一位 dout[0] <= din; //输入信号补充到输出信号的最低位 end end endmodule 13、四位计数器 module counter(Q,clock,clear); output[3:0]Q; input clock,clear; reg[3:0]Q; always@(posedge clear or negedge clock) begin if(clear) Q<=4’d0; else end endmodule 5)程序设计题: 1.五人表决器的设计 module vote5(a,b,c,d,e,f); input a,b,c,d,e; output f; reg f; reg[2:0] count1; initial count1=0; always@(a,b,c,d,e) begin count1<=a+b+c+d+e; f=count1<3?0:1; end endmodule 2.分频器的设计 module adder(clk,z); output z; reg q; reg z; always@(posedge clk) begin if(q%9==0) z<=q; else q=q+1; end endmodule module counter9(clk,datein,z); output z; input clk; input datein; reg z; reg[3:0] q; always@(posedge clk) begin q<=q+1; if (q==4'b1001) begin q<=4'b0000; z<=datein; end end 3.7段数码管的译码器设计 module SEG7_LUT ( input [3:0] iDIG, output reg [6:0] oSEG ); always@(iDIG) begin case(iDIG) 4'h1: oSEG = 7'b1111001; // ---t---- 4'h2: oSEG = 7'b0100100; // | | 4'h3: oSEG = 7'b0110000; // lt rt 4'h4: oSEG = 7'b0011001; // | | 4'h5: oSEG = 7'b0010010; // ---m---- 4'h6: oSEG = 7'b0000010; // | | 4'h7: oSEG = 7'b1111000; // lb rb 4'h8: oSEG = 7'b0000000; // | | 4'h9: oSEG = 7'b0011000; // ---b---- 4'ha: oSEG = 7'b0001000; 4'hb: oSEG = 7'b0000011; 4'hc: oSEG = 7'b1000110; 4'hd: oSEG = 7'b0100001; 4'he: oSEG = 7'b0000110; 4'hf: oSEG = 7'b0001110; default: oSEG = 7'b1000000; endcase end endmodule 4.计数器的设计 module counter(input bn, output reg[7:0] segcode, output [3:0] an ); reg[3:0] count; assign an=4'b0111; initial begin count=0; end always @(posedge bn) count<=count+1; always @(count) case(count) 0:segcode=8'b11000000;//0 1:segcode=8'b11111001;//1 2:segcode=8'b10100100;//2 3:segcode=8'b10110000;//3 4:segcode=8'b10011001;//4 5:segcode=8'b10010010;//5 6:segcode=8'b10000010;//6 7:segcode=8'b11111000;//7 8:segcode=8'b10000000;//8 9:segcode=8'b10010000;//9 'ha:segcode=8'b10001000;//a 'hb:segcode=8'b10000011;//b 'hc:segcode=8'b11000110;//c 'hd:segcode=8'b10100001;//d 'he:segcode=8'b10000110;//e 'hf:segcode=8'b10001110;//f default:segcode=8'b11111111; endcase endmodule 5.流水灯的设计 module ledflash( output [7:0] ld, input clk ); reg clk1s; reg[7:0] tmp; reg[31:0] count; assign ld=tmp; initial begin clk1s=0; tmp=8'b00000001; count=0; end always@(posedge clk) begin count<=count+1; if (count==25000000) begin count<=0; clk1s<=~clk1s; end end always@(posedge clk1s) begin if (clk1s==1) tmp={tmp[6:0],tmp[7]}; end endmodule 6.移位寄存器(略) 7.根据状态转移图写Verilog模块(4状态模型如下) Module fsm(clock,reset,a,k2,k1); input clock,reset,a; output k2,k1; output[1 :0]state ; reg k2,k1 ; reg[1 :0]state ; paremeter Idle=2’b00 ; Start=2’b01 ; Stop=2’b10 ; Clear=2’b11 ; always@(posedge clock) if( !reset) begin state<=Idle ; k2<=0 ; k1<=0 ; end else case(state) Idle :if(a) begin state<=Start ; K1<=0 ; end Else begin state<=Idle ; k2<=0 ; k1<=0 ; end Start :if( !a)state<=Stop ; else state<=Start ; end Stop :if(a)begin state<=Clear ; k2<=1 ; end else begin start<=Stop ; k2<=0 ; k1<=0 ; end Clear :if( !a)begin State<=Idle ; K2<=0 ; K1<=1 ; End Else begin State<=Clear : K2<=0 ; K1<=1 ; End Default :state<=2’bxx ; Endcase Endmodule 8.运算器的设计(加、减、乘、按位与等)module jsq(a,b,c,out); input[7:0]a,b; input[1:0]c; otput[15:0]out; reg [15:0]out reg[7:0]out1,out2; always@(a,b,c,out) case(c) 2'b00:out=a+b; 2'b01:out=a-b; 2'b10:out=a*b; 2'b11: begin out1=a/b; out2=a%b; out={out1,out2}; end default:; endcase endmodule 武汉理工大学考试试题纸 课程名称:知识产权法学专业班级:级法学 题号一二三四五六七八九十总分 题分 第一部分选择题(共分) 一、单项选择题(本大题共小题,每小题1分,共分)在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内。错选、多选或未选均无分。 .下列选项,哪项中含有保护期限不受时间限制的知识产权?() .著作权、外观设计专利权、植物新品种权 .商标权、商业秘密权、集成电路布图设计权 .计算机软件著作权、邻接权、实用新型专利权 .发明专利权、商标权、植物新品种权 .甲在创作武侠小说《神腿》的过程中,乙提供了辅助活动。小说创作完成后,由出版社丙出版。该书的著作权应归属于() .甲.甲和乙.丙.甲和丙 .以下诸权利中,保护期受限制的有() .署名权.修改权 .发表权.保护作品完整权 .张某经过努力创作出一篇学术论文,依我国著作权法的规定() . 张某只有在其论文发表后才能享有著作权 . 张某的论文不论是否发表都能享有著作权 . 张某的论文须经登记后才能享有著作权 . 张某的论文须加注版权标记后才能享有著作权 .下列各项作品中,其著作权由法人或其他组织享有的是() .记者为所在报社采编的人物专访 .设计人员利用单位物质技术条件创作的工程设计图 .教师为完成教学任务编写的教案 .专业作家创作的报告文学 .小说《师长》的作者甲授权乙将该小说改编成电影剧本,制片人丙委托导演丁将该剧本拍摄成电影。该片拍摄完成后,其著作权归属于() .甲.乙.丙.丁 .图书出版者对其出版的图书的版式设计所享有的权利的保护期为() .5年.10年.25年.50年 .甲为做博士学位论文,在图书馆复印了乙的两篇论文,根据我国著作权法,甲的这一行为属于().侵权行为.法定许可使用 简答题 1、金属材料的机械性能主要包括哪几个方面? ○1)强度、塑性、 2)弹性、韧性和硬度等。 2、钢铁材料的性能,可以通过什么途径加以改变? ○热处理、形变强化等手段。 3、常见的金属晶体结构有哪几种?它们的原子排列有何特点? ○1)体心立方、面心立方和密排六方晶格; 2)原子排列都趋于紧密堆垛。 4、常见的金属晶体结构有哪几种?它们的晶格常数有何特点? ○1)体心立方、面心立方和密排六方晶格; 2)体心立方、面心立方的晶格常数是a=b=c,而密排六方晶格的晶格常数是c/a>1。 5、在体心立方晶格中,哪个晶面和晶向的原子密度最大? ○(110);[111] 6、在面心立方晶格中,哪个晶面和晶向的原子密度最大? ○(111);[110] 7、为何单晶体具有各向异性? ○1)单晶体中各原子面和各原子列上的原子排列的紧密程度不同; 2)因此在各个不同的方向上性能不同。 8、多晶体在一般的情况下为何不显示出各向异性? ○1)多晶体受到不同方位晶体相互的影响; 2)只能反映出其统计平均性能,所以不象单晶体那样呈各向异性。 9、过冷度与冷却速度有何关系?它对金属的结晶过程有何影响? ○1)冷却速度越大,过冷度越大; 2)在一般情况下过冷度越大,结晶的推动力越大,有利于结晶过程的进行。 10、过冷度对铸件晶粒大小有何影响? ○1)在一般的工业冷却条件下,过冷度越大,形核率越大; 2)铸件晶粒越小。 11、在铸造生产中,采用哪些措施控制晶粒的大小? ○冷却速度、变质处理、振动等等。 12、如果其它条件相同,试比较在下列铸造条件下,铸件晶粒的大小: 1)金属模浇注与砂模浇注; 2)铸成薄件与铸成厚件; ○金属模浇注;铸成薄件。 13、影响固溶体的结构形式和溶解度的因素有哪些? ○主要有四个方面: 1)尺寸因素;2)结构因素; 3)负电性因素;4)电子浓度因素。 14、置换原子与间隙原子的固溶强化效果哪个大些?为什么? ○1)间隙原子; 2)因为间隙原子引起的晶格畸变度大于置换原子,强化效果优于后者。 15、金属间化合物在结构和性能方面与固溶体有何不同? ○1)金属间化合物具有独特的晶格形式,而固溶体保持溶剂的晶格形式; 2)固溶体有良好的综合机械性能,金属间化合物高硬度、高脆性、高熔点。 16、何谓固溶强化? ○1)溶质原子的作用; 2)造成溶剂晶格发生不同程度地畸变,引起固溶体强度、硬度升高的现象。 17、何谓共晶反应? ○一定成分的液相在一定的温度条件下同时结晶出来两种成分、结构均不相同的固相的反应。 18、何谓共析反应? ○一定成分的固相在一定的温度条件下同时析出来两种成分、结构均不同的固相的反应。19、试比较共晶反应和共析反应的异同点。 ○1)不同点:一个是从液相中结晶出来,而另一个是从固相中析出来; 2)相同点:都同时生成两种成分、结构均不同的固相。 20、形状、尺寸相同的两个Cu-Ni合金铸件,一个含90%Ni,另一个含50%Ni,铸后自然冷却, 第一章 1-1 EDA技术与ASIC设计和FPGA开发有什么关系?FPGA/CPLD在ASIC设计中有什么用途? 答:利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现;FPGA和CPLD是实现这一途径的主流器件。FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。FPGA/CPLD在ASIC设计中,属于可编程ASIC的逻辑器件;使设计效率大为提高,上市的时间大为缩短。 1-2与软件描述语言相比,VHDL有什么特点? P6 答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。 l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么? P5 什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。 有哪些类型?答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。(3)从RTL级表示转换到逻辑门(包括触发器)的表示,即逻辑综合。(4)从逻辑门表示转换到版图表示(ASIC设计),或转换到FPGA的配置网表文件,可称为版图综合或结构综合。 综合在电子设计自动化中的地位是什么?答:是核心地位(见图1-3)。综合器具有更复杂的工作环境,综合器在接受VHDL程序并准备对其综合前,必须获得与最终实现设计电路硬件特征相关的工艺库信息,以及获得优化综合的诸多约束条件信息;根据工艺库和约束条件信息,将VHDL程序转化成电路实现的相关信息。 1-4在EDA技术中,自顶向下的设计方法的重要意义是什么? P7~10 答:在EDA技术应用中,自顶向下的设计方法,就是在整个设计流程中各设计环节逐步求精的过程。 1-5 IP在EDA技术的应用和发展中的意义是什么? P11~12 答:IP核具有规范的接口协议,良好的可移植与可测试性,为系统开发提供了可靠的保证。 1-6 叙述EDA的FPGA/CPLD设计流程。P13~16 答:1.设计输入(原理图/HDL文本编辑);2.综合;3.适配;4.时序仿真与功能仿真;5.编程下载;6.硬件测试。 (A卷) 赣南师范学院 2010—2011学年第一学期期末考试试卷(A卷)(闭卷)年级 2008 专业电子科学与技术(本)课程名称 EDA技术基础 2、学生答题前将密封线外的内容填写清楚,答题不得超出密封线; 3、答题请用蓝、黑钢笔或圆珠笔。 一、单项选择题(30分,每题2分) 1.以下关于适配描述错误的是 B A.适配器的功能是将综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件 B.适配所选定的目标器件可以不属于原综合器指定的目标器件系列 C.适配完成后可以利用适配所产生的仿真文件作精确的时序仿真 D.通常,EDAL软件中的综合器可由专业的第三方EDA公司提供,而适配器则需由FPGA/CPLD供应商提供 2.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。 A.器件外部特性B.器件的综合约束 C.器件外部特性与内部功能D.器件的内部功能 3.下列标识符中, B 是不合法的标识符。 A.State0 B.9moon C.Not_Ack_0 D.signall 4.以下工具中属于FPGA/CPLD集成化开发工具的是 D A.ModelSim B.Synplify Pro C.MATLAB D.QuartusII 5.进程中的变量赋值语句,其变量更新是 A 。 A.立即完成B.按顺序完成 C.在进程的最后完成D.都不对 6.以下关于CASE语句描述中错误的是 A A.CASE语句执行中可以不必选中所列条件名的一条 B.除非所有条件句的选择值能完整覆盖CASE语句中表达式的取值,否则最末一个条件句的选择必须加上最后一句“WHEN OTHERS=><顺序语句>” C.CASE语句中的选择值只能出现一次 D.WHEN条件句中的选择值或标识符所代表的值必须在表达式的取值范围 7.以下哪个程序包是数字系统设计中最重要最常用的程序包 B A.STD_LOGIC_ARITH B.STD_LOGIC_1164 C.STD_LOGIC_UNSIGNED D.STD_LOGIC_SIGNED 8.基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→A →综合→适配→时序仿真→编程下载→硬件测试。 A.功能仿真B.逻辑综合C.配置D.引脚锁定 9.不完整的IF语句,其综合结果可实现 D A.三态控制电路B.条件相或的逻辑电路 C.双向控制电路D.时序逻辑电路 10.下列语句中,属于并行语句的是A A.进程语句B.IF语句C.CASE语句D.FOR语句11.综合是EDA设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;在下面对综合的描述中, C 是错误的。 A.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件 B.综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系不是唯一的 C.综合是纯软件的转换过程,与器件硬件结构无关 D.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束 12.CPLD的可编程是主要基于什么结构 D 。 A.查找表(LUT)B.ROM可编程 C.PAL可编程D.与或阵列可编程 13.以下器件中属于Altera 公司生产的是 B A.ispLSI系列器件B.MAX系列器件 C.XC9500系列器件D.Virtex系列器件 14.在VHDL语言中,下列对时钟边沿检测描述中,错误的是 D A.if clk'event and clk = '1' then B.if clk'stable and not clk = '1' then C.if rising_edge(clk) then D.if not clk'stable and clk = '1' then 15.以下关于状态机的描述中正确的是 B A.Moore型状态机其输出是当前状态和所有输入的函数 B.与Moore型状态机相比,Mealy型的输出变化要领先一个时钟周期C.Mealy型状态机其输出是当前状态的函数 2016年武汉理工材料科学基础真题(回忆版) 第一题:晶体结构 1.简述石墨,滑石,高岭石的结构特点及性质。 2.在面心立方晶胞中画出(0,-1,2)(上划线不好打出来,只能不规范的写了)的晶面,计算面心立方(110)晶面密度 3.画出钙钛矿的晶胞结构图,解释自发极化和温度的关系 4.NiCo2O4是反尖晶石结构,说明什么阳离子填充什么位置,计算氧离子电价是否饱和。第二题:缺陷 1.写出MgO生成肖特基缺陷的缺陷反应方程式。计算273K和2273K下的肖特基缺陷浓度,题目给出了每mol的缺陷形成能,好像是230KJ/mol.记不清了 2.1%LiO2(质量分数)掺入到MgO中,问杂质缺陷浓度是多少? 3.比较在273K和2273K时,纯净的MgO和掺杂的MgO哪个的电导率高,并解释原因。 第三题:玻璃这章 1.请问用什么方法鉴别透明陶瓷和玻璃?简述陶瓷和玻璃的结构特点。 第四题:表面这章 推倒浸湿的G与表面张力的关系式,利用杨式方程推倒浸湿的接触角条件。这就是书上原封不动的推倒。 第五题:扩散这章 今年考得不是很常见 给出4个NaCl型的晶体:NaCl、MgO、CaO、Fe3+在FeO中的扩散激活能的数值表。问你这几个数值的大小的内在原因,为什么哪个大,哪个小?(大概就是这么问的吧) 2.升高50℃,问那个的扩散系数增长最大。 第六题:相变 推倒相变的温度条件,具体说明凝固和熔融的温度条件。 第七题:固态反应 1.题目背景:两种物质的固态反应,加入少量的NaCl促进了反应的进行。给的是一个表格,反应物粒度与反应速度,相同时间反应进度的表 问反应物粒度和反应速度的关系,解释为什么? 2.给出加入矿化剂后,加速固态反应的四个可能的原因。 第八题 烧结的推动力是什么?烧结传质的四种机理?(当然题目肯定不会提示说四种机理的) 第九题 相图。今年格外简单,但加了一点点二元相图的知识,就是问三元相图三角形边上的e1,e2,e3点是什么点,写出这些点的平衡关系。 EDA期末试卷 一、填空题 1.一般把EDA技术的发展分为MOS时代、CMOS 代和ASIC 三个阶段。 2.EDA设计流程包括设计输入、设计实现、实际设计检验和下载编程四个步骤。 3.EDA设计输入主要包括图形输入、HDL文本输入和状态机输入。 4.时序仿真是在设计输入完成之后,选择具体器件并完成布局、布线之后进行的时序关系仿真,因此又称为功能仿真。5.VHDL的数据对象包括变量、常量和信号,它们是用来存放各种类型数据的容器。 6.图形文件设计结束后一定要通过仿真,检查设计文件是否正确。 7.以EDA方式设计实现的电路设计文件,最终可以编程下载 到FPGA 和CPLD 芯片中,完成硬件设计和验证。 8.MAX+PLUS的文本文件类型是(后缀名).VHD 。9.在PC上利用VHDL进行项目设计,不允许在根目 录下进行,必须在根目录为设计建立一个工程目录(即文件夹)。 10.VHDL源程序的文件名应与实体名相同,否则无法通过编译。 二、选择题:。 11.在EDA工具中,能完成在目标系统器件上布局布线软件称为(C )A.仿真器 B.综合 器 C.适配器 D.下载器12.在执行MAX+PLUSⅡ的(D )命令,可以精确分析设计电路输入与输出波形间的延时量。 A .Create default symbol B. Simulator C. Compiler D. Timing Analyzer 13.VHDL常用的库是(A ) A. IEEE B.STD C. WORK D. PACKAGE 14.下面既是并行语句又是串行语句的是( C ) A.变量赋值 B.信号赋值 C.PROCESS语 句 D.WHEN…ELSE语句 15.在VHDL中,用语句(D )表示clock的下降沿。 武汉理工大学考试试题(A 卷) 课程名称:高等数学A (下) 专业班级:2009级理工科专业 题号 一 二 三 四 五 六 七 总分 题分 15 15 24 16 16 8 6 100 备注:学生不得在试题纸上答题(含填空题、选择题等客观题)应按顺序答在答题纸上。 一、单项选择题(35?=15分) 1. 设线性无关的函数123(),(),()y x y x y x 均是二阶非齐次线性微分方程 ()()()y p x y q x y f x '''++=的解,12,c c 是任意常数,则该方程的通解是( ). A .1122123(1)y c y c y c c y =++-- B .11223y c y c y y =++ C .1122123(1)y c y c y c c y =+--- D .1122123()y c y c y c c y =+-+ 2. 曲线23,,x t y t z t ===在点(1,1,1)处的法平面方程为( ). A .236x y z +-= B .236x y z ++= C .236x y z --= D .236x y z -+= 3.设有三元方程ln 1xz xy z y e -+=,根据隐函数存在定理,存在点()0,1,1的一个邻域,在该邻域内该方程只能确定( ). A .一个具有连续偏导数的隐函数(,)z z x y = B .两个具有连续偏导数的隐函数(,)x x y z =和(,)z z x y = C .两个具有连续偏导数的隐函数(,)x x y z =和(,)y y x z = D .两个具有连续偏导数的隐函数(,)y y x z =和(,)z z x y = 4. 设(,)f x y 为连续函数,则二次积分1 40 (cos ,sin )d f r r rdr πθθθ??=( ). A .2 212 (,)x x dx f x y dy -? ? B .2 212 (,)x dx f x y dy -?? C .2 212 (,)y dy f x y dx -? ? D . 2 212 (,)y y dy f x y dx -? ? 5. 级数3 1 sin n n n α ∞ =∑ 的收敛情况是( ). A .绝对收敛 B .收敛性与α有关 C .发散 D .条件收敛 一、填空题 1.铁碳合金在平衡状态下的三个固态单相是( )、( )和 ( );两个机械混合物是( )和( )。 2.实际晶体中的缺陷按几何特征可分为( )、( )、( ),位错是属于其中的( )。 3.钢的淬硬性主要取决于( ),钢的淬透性主要取决于( )。 4.钢的过冷奥氏体等温转变有( )体转变、( )体转变和( )体转变三个类型。5.把钢经过淬火,再经高温回火的热处理称为( )处理。6.材料力学性能指标 k a ,2.0σ,b σ, s σ,δ中,属于强度指标的是( ),属于塑性指标的是( ),属于韧性指标的是( )。 7.常见的金属晶格类型有( )、( )和( )等三种。8.固态合金的基本相可分为 和 。9.钢的热处理工艺由( )、( )和( )三个阶段组成,一般说来,它不改变被处理工件的( ),而改变其( )。10.金属结晶的过程是一个( )和( )的过程。 二、判断题(10分) 1、单晶体金属具有各向异性,而多晶体金属一般不显示各向异性。( ) 2、同素异晶转变和纯金属的结晶一样,也具有形核和长大的特征。( ) 3、物质从液态转变成固态的过程叫结晶。( ) 4、结晶时形核速率愈小,生长速率愈大,则结晶后合金的力学性能愈好。( ) 5、共析反应是在恒温下从液相中同时结晶出两种新固相的反应。( ) 6、与灰口铸铁相比,可锻铸铁具有较高的强度和韧性,故可以用来生产锻件。( ) 7、本质细晶粒钢加热后的实际晶粒度一定比本质粗晶粒钢的细。( ) 8、铁碳相图中的PSK 线称为共晶线,用A 1表示。( ) 9、奥氏体不锈钢不能通过热处理强化。( ) 10、按金相组织分类,退火状态钢分为亚共析钢,共析钢和过共析钢三种类型。( )三、简答题(30分) 1、在立方晶系中,一晶面在x 轴的截距为1,在y 轴的截距为1/2,且平行于z 轴;一晶向上某点坐标为x=1/2,y=0,z=1,求出其晶面指数和晶向指数,并绘图示之。 2、有一块含碳量为1.2%的碳钢,若将它加热至Accm 以上温度保温,出炉后用风扇吹风对它冷却至室温,金相显微镜下观察到的组织如图所示。试问: 1)组织的名称? 2)这种组织的形成机理? 3、甲、乙两厂生产同一种零件,均选用45钢,硬度要求220~250HBS 。甲厂采用正火,乙厂采用调质处理,均能达到硬度要求,但是塑性和韧性有差异。试分析:1)甲、乙两厂产品的组织状态; 精品文档 一、单项选择题(30分)9.嵌套使用IF语句,其综合结果可实现 A 。A.带优先级且条件相与的逻辑电路1.以下描述错误的是 C B.条 件相或的逻辑电路 C.三态控制电路是A.QuartusIIAltera提供的FPGA/CPLD集成开发环境D.双向控制电路 10.在VHDLAlteraB.是世界上最大的可编程逻辑器件供应商之一语言中,下列对时钟边沿检测描述中,错误的是 D 。 A.if clk'event and clk = ‘1' then B.if falling_edge(clk) then 前一代C.MAX+plusII是AlteraFPGA/CPLD集成开发环境QuartusII的更 C.if clk'event and clk = ‘0' then 新换代新产品D.if clk'stable and not clk = ‘1' then 11.下列那个流程是正确的基于.DQuartusII完全支持VHDL、Verilog的设计流程EDA软件的FPGA / CPLD设计流程 B A.原理图/HDL文本输入→适配→综合→功能仿真→编程下载→硬件测试开发工具中的专用综合器的是2.以下工具中属于FPGA/CPLD B B.原理图/HDL文本输入→功能仿真→综合→适配→编程下载→硬件测试 C .Active HDL D.QuartusII Leonardo Spectrum .AModelSim B.C.原理图/HDL文本输入→功能仿真→综合→编程下载→→适配硬件测试;.3以下器件中属于Xilinx 公司生产的是 C /HDL文本输入→功能仿真→适配→编程下载→综合→硬件测试 D.BMAX系列器件.原理图A.ispLSI系列器件 )语句的语句结构及语法规则语言中,下列对进程(PROCESS系列器件 C.XC9500系列器件D.FLEX 12.在VHDL 。A 的描述中,正确的是以下关于信号和变量的描述中错误的是4. B 为一无限循环语句;敏感信号发生更新时启动进程,执行完..信号是描述硬件系统的基本数据对象,它的性质类似于连接线PROCESSAA .信号的定义范围是结构体、进程B 成后,等待下一次进程启动C.除了没有方向说明以外,信号与实体的端口概念是一致的B.敏感信号参数表中,应列出进程中使用的所有输入信号CD.在进程中不能将变量列入敏感信号列表中.进程由说明部分、结构体部分、和敏感信号参数表三部分组成D.当前进程中声明的变量也可用于其他进程以下关于状态机的描述中正确的是5. B B MooreA.型状态机其输出是当前状态和所有输入的函数13.下列语句中,不属于并行语句的是 语句B.CASE 型的输出变化要领先一个时钟周期型状态机相比,.与BMooreMealy A.进程语句 …语句…ELSE D.WHEN .元件例化语句MealyC.型状态机其输出是当前状态的函数 C 设计现行工作VHDL语言共支持四种常用库,其中哪种库是用户的14.以上都不对D .VHDL B 下列标识符中,.库是不合法的标识符。6 END BPP0 A...D .CNot_Ack sig D 班级 学号 姓名 密 封 线 内 不 得 答 题 一、单项选择题(30分) 1.以下描述错误的是 C A .QuartusII 是Altera 提供的FPGA/CPLD 集成开发环境 B .Altera 是世界上最大的可编程逻辑器件供应商之一 C .MAX+plusII 是Altera 前一代FPGA/CPL D 集成开发环境QuartusII 的更新换代新产品 D .QuartusII 完全支持VHDL 、Verilog 的设计流程 2.以下工具中属于FPGA/CPLD 开发工具中的专用综合器的是 B A .ModelSim B .Leonardo Spectrum C .Active HDL D .QuartusII 3.以下器件中属于Xilinx 公司生产的是 C A .ispLSI 系列器件 B .MAX 系列器件 C .XC9500系列器件 D .FLEX 系列器件 4.以下关于信号和变量的描述中错误的是 B A .信号是描述硬件系统的基本数据对象,它的性质类似于连接线 B .信号的定义范围是结构体、进程 C .除了没有方向说明以外,信号与实体的端口概念是一致的 D .在进程中不能将变量列入敏感信号列表中 5.以下关于状态机的描述中正确的是 B A .Moore 型状态机其输出是当前状态和所有输入的函数 B .与Moore 型状态机相比,Mealy 型的输出变化要领先一个时钟周期 C .Mealy 型状态机其输出是当前状态的函数 D .以上都不对 6.下列标识符中, B 是不合法的标识符。 A .PP0 B .END C .Not_Ack D .sig 7.大规模可编程器件主要有FPGA 、CPLD 两类,下列对CPLD 结构与工作原理的描述中,正确的是 C 。 A .CPLD 即是现场可编程逻辑器件的英文简称 B .CPLD 是基于查找表结构的可编程逻辑器件 C .早期的CPL D 是从GAL 的结构扩展而来 D .在Altera 公司生产的器件中,FLEX10K 系列属CPLD 结构 8.综合是EDA 设计流程的关键步骤,在下面对综合的描述中, D 是错误的。 A .综合就是把抽象设计层次中的一种表示转化成另一种表示的过程 B .综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD 的基本结构相映射的网表文件 C .为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束 D .综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的(即综合结果是唯一的) 9.嵌套使用IF 语句,其综合结果可实现 A 。 A .带优先级且条件相与的逻辑电路 B .条件相或的逻辑电路 C .三态控制电路 D .双向控制电路 10.在VHDL 语言中,下列对时钟边沿检测描述中,错误的是 D 。 A .if clk'event and clk = ‘1’ then B .if falling_edge(clk) then C .if clk’event and clk = ‘0’ then D .if clk’stable and not clk = ‘1’ then 11.下列那个流程是正确的基于EDA 软件的FPGA / CPLD 设计流程 B A .原理图/HDL 文本输入→适配→综合→功能仿真→编程下载→硬件测试 B .原理图/HDL 文本输入→功能仿真→综合→适配→编程下载→硬件测试 C .原理图/HDL 文本输入→功能仿真→综合→编程下载→→适配硬件测试; D .原理图/HDL 文本输入→功能仿真→适配→编程下载→综合→硬件测试 12.在VHDL 语言中,下列对进程(PROCESS )语句的语句结构及语法规则的描述中,正确的是 A 。 A .PROCESS 为一无限循环语句;敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动 B .敏感信号参数表中,应列出进程中使用的所有输入信号 C .进程由说明部分、结构体部分、和敏感信号参数表三部分组成 D .当前进程中声明的变量也可用于其他进程 13.下列语句中,不属于并行语句的是 B A .进程语句 B .CAS E 语句 C .元件例化语句 D .WHEN …ELSE …语句 14.VHDL 语言共支持四种常用库,其中哪种库是用户的VHDL 设计现行工作 库 D A .IEEE 库 B .VITAL 库 C .STD 库 D .WORK 库 15.VHDL 语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。 A .器件外部特性 B .器件的综合约束 C .器件外部特性与内部功能 D .器件的内部功能 二、EDA 名词解释,写出下列缩写的中文含义(10分) 1.CPLD :复杂可编程逻辑器件 2.ASIC :专用集成电路 3.LUT :查找表 4.EDA :电子设计自动化 5.ROM :只读存储器 三、程序填空题(20分) 以下是一个模为24(0~23)的8421BCD 码加法计数器VHDL 描述,请补充完整 武汉理工大学 武汉理工大学2010年研究生入学考试试题 课程名称材料科学基础 一、基本概念(30分) 空间利用率和空隙填充率;位错滑移和位错爬移;玻璃网络形成体和玻璃网络外体;穿晶断裂和蠕变断裂;应力腐蚀和晶间腐蚀;初次在结晶和二次在结晶;均态核化和非均态核化;矿化剂。 二、作图题(10分) 1. 在面心立方晶胞中标示出质点以ABCABC。。。规律重复的堆积方式。(5分) 2.画出面心立方晶胞中质点在(111)晶面上的投影图。(5分) 三、绿宝石Be3Al2[Si6O18]上半个晶胞在(0001)面上的投影图如图1所示,整个晶胞的结构按照标高50处的镜面经反映即可得到。根据图1回答下列问题:(20分) 1.绿宝石的硅氧比为多少?硅氧四面体组成的是什么结构?(4分) 2.Be和Al分别与周边什么标高的几个氧配位?构成的配位多面体是什么?它们之间又是如何连接的?(8分) 3.用Pauling的连接规则说明标高65的氧电价是否平衡?(4分) 4.根据结构说明绿宝石热膨胀系数不高、当半径小的Na+存在时,在直流电场下具有显著离子电导的原因。(4分) 图1 绿宝石晶胞 四、A-B-C三元系统相图如图1所示。根据相图回答下列问题:(25分) 1.在图上划分副三角形、用剪头表示界线上温度下降方向方向及界线的性质;(8分) 2.判断化合物S1S2的性质;(2分) 3.写出各三元无变量点的性质及其对应的平衡关系式;(5分) 4.写出熔体1、2在完全平衡冷却下的冷却结晶过程;(10分) 第4题图 五、假设自组成为18Na2O10CaO72SiO2(wt%)和8Na2O4CaO88SiO2(wt%)两种熔体中,均态成核析出石英相。(15分) 1.设形成晶核为球形,两者相变时除去界面能外单位体积自由焓ΔGv的变化相同,请推导熔体结晶时的核化势垒和临界晶核半径;(5分) 2.考虑到两熔体组成及表面张力的差异,试比较两者的临界晶核半径的大小并解释其原因;(5分) 3.假设新相的晶核形成后,新相长大的速率均取决于溶质原子在熔体中的扩散,在外界条件均相同的情况下,试比较两种熔体石英相的长大速率,并解释其原因;(5分) 六、晶体结构缺陷(15分) 1.CaO形成肖特基缺陷,写出其缺陷反应方程式,并计算单位晶胞CaO的肖特基缺陷数(已知CaO的密度是3.0克/厘米3,其晶格参数是0.481nm);(4分) 2.CsCl溶入MgCl2中形成空位固溶体,并写出固溶体的化学式;(3分) 3.Al2O3掺入到MgO中,写出二个合理的方程,并判断可能成立的方程是哪一个?写出其固溶体的化学式;(5分) 4.根据2和3总结杂质缺陷形成规律。(3分) 2007 至2008学年度第二学期期末考核 《EDA》试题(开卷) 卷号:B 时间:120 分钟 2008 年6 月 专业:电子信息工程学号:姓名: 一填空题(20分) 1、VHDL 2、DEVICE.LIB SYMBOLS.LIB 3、实际零件焊接到电路板时所指示的外观和焊点的位置 4、电子设计自动化电子CAD技术 5、A L T E R A,X I L I N X 6、WAIT 7、电路连接 8、SRAM-BASE 9、2.54mm 300mil 10、元件外观和元件引线端子的图形 二名词解释(20分) 1 PLD/FPGA PLD是可编程逻辑器件(Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field Programable Gate Array)的简称,两者的功能基本相同,只是实现原理略有不同,所以我们有时可以忽略这两者的区别,统称为可编程逻辑器件或PLD/FPGA。 2.过孔 当需要连接两个层面上的铜膜走线时就需要过孔(Via),过孔 又称为贯孔、沉铜孔和金属化孔。 过孔分为穿透式(Through)、半隐藏式(Blind)和隐藏式(Buried) 3.铜膜线 就是连接两个焊盘的导线,称为Track,一般铜膜线走线在不 同层面取不同的走向,例如顶层走水平线,则底层走垂直线。顶 层和底层走线之间的连接采用过孔(Via)连接。 4 PROM、PAL和PLA PROM:与阵列固定,或阵列可编程,一般用作存储器,其输入为存储器的地址,输出为存储器单元的内容。但输入的数目太大时,器件功耗增加,其局限性大。 PLA:与或阵列均可编程,但是其慢速特性和相对PAL、PROM而高得多的价格妨碍了它被广泛使用。PAL:或阵列固定,与阵列可编程,其第二代产品GAL具有了可电擦写、可重复编程、可设置加密的功能。 5 自顶向下的/自下而上的设计方法 自下而上的设计方法,使用该方法进行硬件设计是从选择具体元器件开始,并用这些元器件进行逻辑电路设计,从而完成系统的硬件设计,然后再将各功能模块连接起来,完成整个系统的硬件设计,自顶向下的设计方法就是从系统的总体要求出发,自顶向下分三个层次对系统硬件进行设计。 第一个层次是行为描述第二个层次是数据流描述第三个层次为逻辑综合 1.一个项目的输入输出端口是定义在( A )1-5 ACDCD 6-10 CCACA A. 实体中;. B. 结构体中; C. 任何位置; D. 进程中。 2. MAXPLUS2中编译VHDL源程序时要求( C ) A. 文件名和实体可以不同名; B. 文件名和实体名无关; C. 文件名和实体名要相同; D. 不确定。 3. VHDL语言中变量定义的位置是(D ) A. 实体中中任何位置; B. 实体中特定位置; C. 结构体中任何位置; D. 结构体中特定位置。 4.可以不必声明而直接引用的数据类型是(C ) A. STD_LOGIC ; B. STD_LOGIC_VECTOR; C. BIT; D. ARRAY。 5. MAXPLUS2不支持的输入方式是(D ) A 文本输入;.B. 原理图输入;C. 波形输入;D. 矢量输入。 6.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是( C ) A. FPGA全称为复杂可编程逻辑器件; B. FPGA是基于乘积项结构的可编程逻辑器件; C. 基于SRAM的FPGA器件,在每次上电后必须进行一次配置; D. 在Altera公司生产的器件中,MAX7000系列属FPGA结构。 7.下面不属于顺序语句的是( C ) A. IF语句; B. LOOP语句; C. PROCESS语句; D. CASE语句。 8. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,实体体描述的是( A ) A. 器件外部特性; B. 器件的内部功能; C. 器件的综合约束; D. 器件外部特性与内部功能。 9. 进程中的信号赋值语句,其信号更新是( C ) A. 按顺序完成; B. 比变量更快完成; C. 在进程的最后完成; D. 都不对。 10. 嵌套使用IF语句,其综合结果可实现:(A ) A. 带优先级且条件相与的逻辑电路; B. 条件相或的逻辑电路; C. 三态控制电路; D. 双向控制电路。 一、单项选择题:(20分) 1. IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述 武汉理工大学考试试题 课程:知识产权B卷 班级姓名 一、简述题(每小题8分,共计24分) 1、简述著作权的内容。 2、简述知识产权的范围。 3、简述商业秘密的构成要件。 二、论述题(16分) 4、论述获得专利权的实质条件。 三、案例分析题(5小题,20分;6小题,30分,共计60分) 5、原告广州冲击波音像实业有限公司,住所地广东省广州市天河区体育东路羊城国际贸易中心西塔1101室。 被告河北纪元光电有限公司,住所地河北省石家庄市高新区海河道29号。 被告山东文化音像出版社,住所地山东省济南市历城区山大北路27号。 被告湖南王一实业集团精彩生活超市有限公司,住所地湖南省长沙市晚报大道218号。 原告冲击波公司诉称,原告系《神秘园》(《Secret Garden》)系列曲目的著作权人环球唱片有限公司授权在中国大陆的唯一合法版权享有者,享有《神秘园》(《Secret Garden》)系列曲目在中国大陆的独家复制、出版、发行权,该权利已经国家版权局审核登记,并获得文化部批准。2006年10月16日,原告在被告精彩生活超市发现并购买一套音像制品,外包装盒面标有“神秘园”、“山东文化音像出版社”、“ISRC CN-E26-05-377-00/A.J6”字样,该音像制品的SID码为ifpiG420。经查,该侵权光碟由被告纪元光电公司接受被告山东文化音像出版社委托复制。原告认为上述三被告的行为侵犯了原告的合法权益,给原告造成了巨大的经济损失,特诉至人民法院,请求依法判令:1、三被告立即停止侵权行为;2、被告纪元光电公司、山东文化音像出版社连带赔偿原告经 济损失50万元;3、被告纪元光电公司、山东文化音像出版社连带赔偿原告为制止侵权行为发生的合理费用5000元;4、被告纪元光电公司、山东文化音像出版社承担本案的诉讼费用。 被告纪元光电公司辩称:1、原告对《神秘园》作品没有合法授权,无权主张任何权利,原告提交的证据,无法证明其有《神秘园》的著作权,反而证明《神秘园》作品的合法权利人是辽宁文化艺术音像出版社,而不是原告;2、我公司不侵权,亦没有任何过错,不应承担任何责任。我公司是根据山东文化音像出版社的委托制作《神秘园》光碟,不负责该光碟的出版、销售,即使侵权,也应该由委托方山东文化音像出版社承担责任。故请求人民法院依法驳回原告的诉讼请求。 被告精彩生活超市辩称,我公司出售的是经合法授权的《神秘园》光碟,不侵权。我公司的供货商是长沙振雄音像公司,该公司得到了原告冲击波公司的授权。 被告精彩生活超市以三份证据证明其购进和经营《神秘园》音像制品的渠道是合法的。 2005年6月,被告山东文化音像出版社作为委托方,被告纪元光电公司作为受托方,共同签订了《录音录像制品复制委托书》(No.0522918),其主要内容为:山东文化音像出版社委托纪元光电公司复制《神秘园》CD两万张。 2006年10月16日,原告工作人员在被告精彩生活超市购得被控侵权CD《神秘园》,一套三张,共计54首乐曲,其中包含了原告请求保护的51首曲目,并取得销售发票(发票号:143010520431)。该CD外包装盒上标有“神秘园Secret Garden、山东文化音像出版社、ISRC CN-E26-05-377-00/A.J6”字样,其中A、B、C三张光盘均刻有激光数码储存片来源识别码(SID码)“ifpiG420”。经查,该SID码属于河北纪元光电有限公司。此外,原告工作人员还在北京、衡阳等地发现并购买了被控侵权CD《神秘园》。 另查明,原告冲击波公司为调查、制止涉案三被告的侵权行为所发生的合理费用为2504元。 问题: 武汉理工历年复试真题 2003年材料学院复试笔试题目 适用专业:材料学、材料物理与化学、材料加工工程 1、简述材料科学与工程的定义、材料的分类以及材料在国民经济建设中的地位和作用。 2、结合自己所学专业,叙述二个本专业的研究热点问题。 3、简述你所熟悉的几种有关材料的测试技术,并写出其中一种测试技术的原理及解析方法。 4、针对你拟选报的研究方向,做一个三年的研究计划。 5、目前,用于材料的合成与制备有许多新方法,请你列举二种方法并加以较详细说明。 2004年材料学院复试笔试题目 第一题: 计算机基础30分,今年考了很多计算机基础知识,总之要看书,难度相当于计算机基础的难度。 第二题: 1.简述材料科学与工程的定义,材料的分类以及材料在国民经意建设中的地位和作用。(15 分) 2.简述两种现代测试分析方法,并举例说明每种方法可分析的内容。(20分) 3.结合自己所学专业,叙述两个本专业的研究热点问题。(15分) 4.目前,用于材料的合成与制备有许多新方法,请你列举其中一种方法并加以说明。(10 分) 5.根据你拟选报的研究方向,写一份课题研究计划。(10分) 第一题: 听力20分(有选择有填空) 第二题: 计算机基础(20分) (一).填空题 1.一个完整的计算机系统包括( )和( ). 2.微型计算机系统的总线包括( )总线、( )总线和( )总线. 3. ( 内存)中保存的数据,一经切断电源,其中的数据将完全消失. 4.WINDOWS98中进入中文输入法按( )键,改变中文输入法按( )键. 5.Excel中的基本数据文件是( ). 6.Internet是全球最大的计算机网络,它的基础协议是( ). (二).单选题 1.内存中每个基本单位都被赋予一个唯一的序号,称为: A.地址 B.字节 C.编号 D.代码 2.计算机的存储容量以KB为单位时,这里1KB表示: A.1000个字节 B.1024个字节 C.1000个2进制位 D.1024个2进制位 3.把计算机的数据存到磁盘上,这种操作叫做: A.输出 B.读盘 C.写盘 D.输入 4.操作系统是_______的接口: A.软件和硬件 B.计算机和外设 C.用户和计算机 D.高级语言和机器语言 5.下面全是高级语言的一组是: A.汇编语言,C,PASCAL B.汇编语言,C,BASIC C.机器语言,C,BASIC D.BASIC,C,PASCAL 6.Word的默认文档扩展名是___ ___;Excel的默认文档扩展名是_____. A.IDX B.DOC C.TXT D.DBF E.XLS 7.一个IP地址由网络地址和___ __两部分构成. A.广播地址 B.多址地址 C.主机地址 D.子网掩码 8.E-MAIL的地址格式是: A. 用户名@邮件主机域名 B. @用户名邮件主机域名 C. 用户名@域名邮件主机 9.一张干净的软盘带上写保护后: A.只能预防已知病毒 B.可以预防所有病毒 C.不能预防病毒 第三题: 专业基础(60分) (任选四题回答) 1.结合你对材料科学与工程的认识与理解,谈谈报考材料类研究生的理由?(15分) 2.介绍一种现代测试技术方法,并举例说明其可分析的内容?(15分) 3.结合自己所学专业,叙述二个本专业的研究热点问题.(15分) 4.结合可持续发展的角度,谈谈产业与能源,环境之间的关系.(15分) 5.目前,用于材料的合成与制备有许多新方法,请你列举二种方法并加以较详细说明.(15分) 6.结合你拟报的研究方向,提出一个研究课题并列出主要研究内容?(15分)武汉理工大学考试试题纸

工程材料简答题,武汉理工大学,考试试题(含原题),2014年总结

EDA技术试验问答题答案(基本包含)

EDA期末考试考卷及答案

2016武汉理工大学考研材料科学基础真题

EDA期末试卷及答案(2020年九月整理).doc

【2017年最新】武汉理工大学考试试题

工程材料 测试题武汉理工大学 考试试题 含原题

EDA技术期末试卷含答案资料

EDA技术期末试卷(含答案)

武汉理工大学材料科学基础历年考研真题

《EDA》试题B答案

(完整版)EDA期末考试题1

武汉理工大学考试试题

武汉理工历年复试真题