Dedicated Pin 144-Pin TQFP 256-Pin FBGA 256-Pin MBGA IO/GCLK0

18H5K1IO/GCLK1

20J5L1IO/GCLK2

89J12M20IO/GCLK3

91H12L20IO/DEV_OE

60M8W12IO/DEV_CLRn

61M9Y13TDI

34L6U2TMS

33N4T3TCK

35P3W2TDO

36M5V2GNDINT

17, 54, 92, 128H7, H9, J8, J10J4, U12, M17, D12GNDIO 10, 26, 47, 65, 83, 99, 115, 135A1, A16, B2, B15, G7, G8, G9,

G10, K7, K8, K9, K10, R2, R15,

T1, T16

H3, J3, M4, N3, U9, V8, V9, V13, H18, J17, N18, C8, D9, C12, C13, M18VCCINT (1)19, 56, 90, 126H8, H10, J7, J9

K4, U11, L17, D11VCCIO1 (2)9, 25C1, H6, J6, P1

K3, L3, L4, M3VCCIO2 (2)116, 136A3, A14, F8, F9

C9, C10, D10, C11VCCIO3 (2) 82, 100 C16, H11, J11, P16

J18, K17, K18, L18VCCIO4 (2) 46, 64 L8, L9, T3, T14

U10, V10, V11, V12No Connect (N.C.)--

-Total User I/O Pins 116

212212Notes:

1. For EPM1270 devices, all VCCINT pins must be connected to either 3.3 V or

2.5 V, but not a combination of both. For EPM1270G devices, all VCCINT pins must be connected to 1.8 V.

2. Each set of VCCIO pins (VCCIO1, VCCIO2, etc.) can be connected to

3.3 V, 2.5 V, 1.8 V, or 1.5 V.

Dedicated Pin Information for the MAX ?II

EPM1270 / EPM1270G Devices

Version 1.5

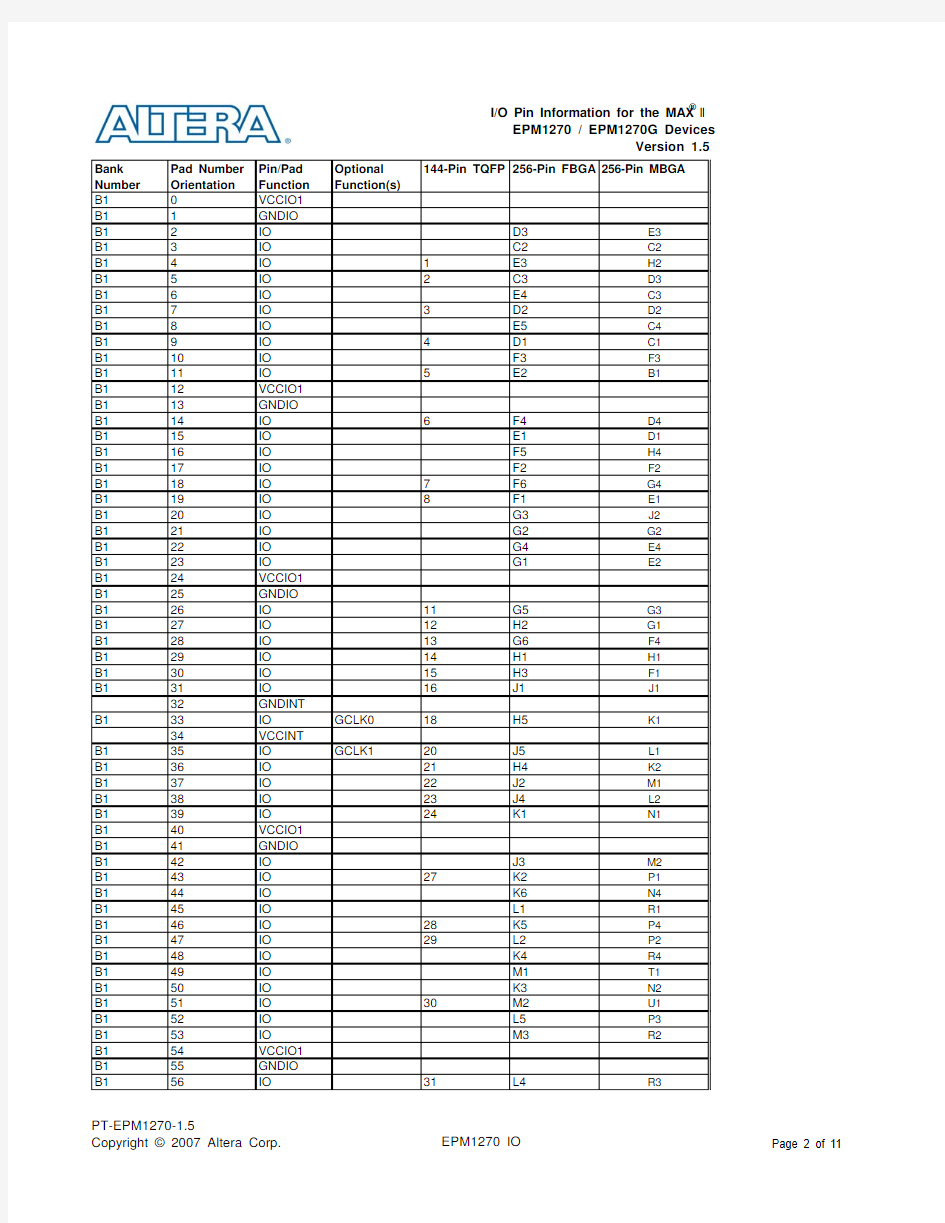

Bank Number Pad Number Orientation Pin/Pad Function Optional Function(s)

144-Pin TQFP 256-Pin FBGA 256-Pin MBGA

B10VCCIO1

B11GNDIO

B12IO D3E3

B13IO C2C2

B14IO 1E3H2

B15IO 2C3D3

B16IO E4C3

B17IO 3D2D2

B18IO E5C4

B19IO 4D1C1

B110IO F3F3

B111IO 5E2B1

B112VCCIO1

B113GNDIO

B114IO 6F4D4

B115IO E1D1

B116IO F5H4

B117IO F2F2

B118IO 7F6G4

B119IO 8F1E1

B120IO G3J2

B121IO G2G2

B122IO G4E4

B123IO G1E2

B124VCCIO1

B125GNDIO

B126IO 11G5G3

B127IO 12H2G1

B128IO 13G6F4

B129IO 14H1H1

B130IO 15H3F1

B131IO 16J1J1

32GNDINT

B133IO GCLK018H5K1

34VCCINT

B135IO GCLK120J5L1

B136IO 21H4K2

B137IO 22J2M1

B138IO 23J4L2

B139IO 24K1N1

B140VCCIO1

B141GNDIO

B142IO J3M2

B143IO 27K2P1

B144IO K6N4

B145IO L1R1

B146IO 28K5P4

B147IO 29L2P2

B148IO K4R4

B149IO M1T1

B150IO K3N2

B151IO 30M2U1

B152IO L5P3

B153IO M3R2

B154VCCIO1

B155GNDIO

B156IO 31L4R3

EPM1270 / EPM1270G Devices

Version 1.5

Bank Number Pad Number Orientation Pin/Pad Function Optional Function(s)

144-Pin TQFP 256-Pin FBGA 256-Pin MBGA

EPM1270 / EPM1270G Devices

Version 1.5

B157IO N1V1

B158IO L3T4

B159IO 32N2W1

B160IO M4V3

B161IO N3T2

B162TMS 33N4T3

B163TDI 34L6U2

B164TCK 35P3W2

B165TDO 36M5V2

B166IO P2U3

B167VCCIO1

B168GNDIO

B169N.C. (1)

B470VCCIO4

B471GNDIO

B472IO P4V4

B473IO 37R1W3

B474IO 38P5V5

B475IO T2Y1

B476IO N5W5

B477IO 39R3W4

B478IO P6U4

B479GNDIO

B480VCCIO4

B481IO 40R4Y2

B482IO 41N6U5

B483IO T4W6

B484IO M6U6

B485IO R5Y3

B486IO 42P7V6

B487IO 43T5Y4

B488IO 44N7V7

B489IO R6W7

B490IO M7U7

B491IO T6Y5

B492IO L7U8

B493IO 45R7Y6

B494VCCIO4

B495GNDIO

B496IO 48P8W8

B497IO 49T7Y7

B498IO 50N8W9

B499IO 51R8Y8

B4100IO 52N9W10

B4101IO 53T8Y9

102GNDINT

B4103IO 55T9Y10

104VCCINT

B4105IO 57R9Y11

B4106IO 58P9W11

B4107IO 59T10Y12

B4108IO DEV_OE 60M8W12

B4109IO DEV_CLRn 61M9Y13

B4110IO 62L10U16

B4111IO 63R10Y14

B4112VCCIO4

B4113GNDIO

Bank Number Pad Number Orientation Pin/Pad Function Optional Function(s)

144-Pin TQFP 256-Pin FBGA 256-Pin MBGA

EPM1270 / EPM1270G Devices

Version 1.5

B4114IO M10U13

B4115IO T11Y15

B4116IO 66N10V15

B4117IO 67R11Y16

B4118IO P10W14

B4119IO T12W15

B4120IO 68M11U14

B4121IO R12W16

B4122IO N11V14

B4123IO 69T13Y17

B4124IO P11W13

B4125IO R13Y18

B4126VCCIO4

B4127GNDIO

B4128IO 70M12U15

B4129IO R14Y19

B4130IO N12V16

B4131IO 71T15W17

B4132IO P12V17

B4133IO R16W18

B4134IO 72P13V18

B4135VCCIO4

B4136GNDIO

B3137VCCIO3

B3138GNDIO

B3139IO P14W19

B3140IO N13U18

B3141IO P15V19

B3142IO 73M14T18

B3143IO 74N14U19

B3144IO 75M13R18

B3145IO N15Y20

B3146IO 76L14W20

B3147IO N16T19

B3148VCCIO3

B3149GNDIO

B3150IO L13U17

B3151IO 77M15V20

B3152IO L12P17

B3153IO M16R19

B3154IO L11T17

B3155IO 78L15U20

B3156IO 79K14N19

B3157IO 80L16T20

B3158IO K13R17

B3159IO K15P19

B3160IO 81K12P18

B3161IO K16R20

B3162VCCIO3

B3163GNDIO

B3164IO 84K11N17

B3165IO 85J15P20

B3166IO 86J14M19

B3167IO 87J16N20

B3168IO 88J13L19

B3169IO GCLK289J12M20

170VCCINT

Bank Number Pad Number Orientation Pin/Pad Function Optional Function(s)

144-Pin TQFP 256-Pin FBGA 256-Pin MBGA

EPM1270 / EPM1270G Devices

Version 1.5

B3171IO GCLK391H12L20

172GNDINT

B3173IO 93H16K20

B3174IO 94H13K19

B3175IO 95H15J20

B3176IO 96H14J19

B3177IO 97G16H20

B3178IO 98G12G18

B3179GNDIO

B3180VCCIO3

B3181IO 101G15G20

B3182IO G11H17

B3183IO F16G19

B3184IO G13F17

B3185IO 102F15F20

B3186IO 103G14E17

B3187IO E16E20

B3188IO F11G17

B3189IO E15F19

B3190IO 104F12D17

B3191IO 105D16D20

B3192IO F13C18

B3193GNDIO

B3194VCCIO3

B3195IO 106D15C20

B3196IO F14H19

B3197IO 107D14B20

B3198IO E12F18

B3199IO 108C15E19

B3200IO E13E18

B3201IO C14D19

B3202IO E14D18

B3203IO D13C19

B3204N.C. (1)

B3205VCCIO3

B3206GNDIO

B2207VCCIO2

B2208GNDIO

B2209IO C13C16

B2210IO 109B16A20

B2211IO 110C12B16

B2212IO 111A15B17

B2213IO D12C15

B2214GNDIO

B2215VCCIO2

B2216IO B14A19

B2217IO C11B18

B2218IO B13A18

B2219IO 112D11B19

B2220IO A13A17

B2221IO E11D15

B2222IO 113B12B15

B2223IO C10C17

B2224IO A12B14

B2225IO 114D10C14

B2226IO B11A16

B2227IO E10D16

Bank Number Pad Number Orientation Pin/Pad Function Optional Function(s)

144-Pin TQFP 256-Pin FBGA 256-Pin MBGA

EPM1270 / EPM1270G Devices

Version 1.5

B2228GNDIO

B2229VCCIO2

B2230IO 117A11B13

B2231IO 118F10D13

B2232IO 119B10A15

B2233IO 120C9B12

B2234IO 121A10A14

B2235IO 122D9D14

B2236IO 123B9A13

B2237IO 124E9B11

B2238IO 125A9A12

239VCCINT

B2240IO 127A8A11

241GNDINT

B2242IO 129B8A10

B2243IO 130E8B10

B2244IO 131A7A9

B2245IO 132D8D8

B2246IO 133B7A8

B2247IO 134C8B9

B2248GNDIO

B2249VCCIO2

B2250IO A6A7

B2251IO F7D7

B2252IO B6B7

B2253IO 137E7C6

B2254IO 138A5A6

B2255IO 139D7C7

B2256IO B5A5

B2257IO C7B8

B2258IO 140A4A4

B2259IO 141E6D6

B2260IO B4B6

B2261IO D6D5

B2262IO 142C4A3

B2263IO C6B2

B2264GNDIO

B2265VCCIO2

B2266IO B3A2

B2267IO C5B3

B2268IO 143A2B5

B2269IO D5C5

B2270IO B1A1

B2271IO 144D4B4

B2272VCCIO2

B2273GNDIO

Note:

1. No Connect

Pin Name

Pin Type Pin Description

VCCIO[1..4]Power I/O supply voltage pins for banks 1 through 4. Each VCCIO bank supports a different

voltage level with the VCCIO pins providing power for the input and output buffers within

that particular I/O bank. Each VCCIO bank can be powered with either 3.3 V, 2.5 V, 1.8 V,

or 1.5 V.

GNDIO Ground Ground pins for all the I/O banks.

VCCINT Power Voltage supply pins for the device.

GNDINT Ground Ground pins for the internal supply.

NC No Connect Do not drive signals into these pins.

DEV_CLRn I/O Dual-purpose pin that can override all clears on all device registers. All registers are

cleared when the pin is driven low and all registers behave as defined in the design when

this pin is driven high. If not used for its dual-purpose function, this pin is a regular I/O.

DEV_OE I/O Dual-purpose pin that can override all tri-states on the device. All output pins are tri-stated

when the pin is driven low and all output pins behave as defined in the design when this

pin is driven high. If not used for its dual-purpose function, this pin is a regular I/O.

TCK Input Dedicated JTAG input pin.

TDI Input Dedicated JTAG input pin.

TMS Input Dedicated JTAG input pin.

TDO Output Dedicated JTAG output pin.

GCLK [0..3]I/O

Dual-purpose clock pins that connect to the global clock network. If not used for

its dual-purpose function, this pin is a regular I/O.Programming and JTAG pins

Clock Pins

Pin Definitions for the MAX ?II

EPM1270 / EPM1270G Devices

Version 1.5

Supply and Reference pins

Figure 1. MAX II EPM1270 / EPM1270G T144 Device Top View Package Diagram and Bank Information Package Diagram and Bank Information for the MAX ? II

EPM1270 / EPM1270G Devices

Version 1.5

Figure 2. MAX II EPM1270 / EPM1270G F256 Device Top View Package Diagram and Bank Information Package Diagram and Bank Information for the MAX ? II

EPM1270 / EPM1270G Devices

Version 1.5

Figure 3. MAX II EPM1270 / EPM1270G M256 Device Top View Package Diagram and Bank Information Package Diagram and Bank Information for the MAX ? II EPM1270 / EPM1270G Devices

Version 1.5

Date

Version Changes Made Sep-07

1.5Added support for M256 package in the EPM1270G device May-07

1.4Changed the VCCIO2 and VCCIO4 pins for EPM1270 (256-Pin MBGA package) to match Quartus II pin-out Apr-06

1.3Added M256 package Jan-05

1.2Added MAX IIG device naming to titles, notes, and figures Jul-04

1.1Added package diagram and bank information figures for each package May-04 1.0

Initial release Revision History for the MAX ? II EPM1270 / EPM1270G Devices

Version 1.5

74LS373 引脚图、内部结构、参数、典型应用电路 【功能简介】 74LS373是一款常用的地址锁存器芯片,由八个并行的、带三态缓冲输出的D触发器构成。在单片机系统中为了扩展外部存储器,通常需要一块74LS373芯片。本文将介绍74LS373的工作原理,内容涵盖引脚图、内部结构、主要参数以及在单片机扩展系统中的典型应用电路。 【内部逻辑结构图】 74LS373地址锁存器的内部逻辑结构如图一所示。 图1

【74LS373的真值表(功能表)】 G—与8031/8051的ALE相连,控制八个D型锁存器的导通与截止:高电平时,八个D型锁存器正常运行(导通),即锁存器的输出端 与输入端D的反相信号始终同步;低电平时锁存器截止,D锁存器输出 端的状态保持不变。 OE(Output Enable = Output Control)—使能端,接地时锁存 【74LS373引脚排列图】

【74LS373电气参数】 拖动图片放大! 74ls373推荐工作条件 【74LS373在单片机扩展系统中的典型应用电路】 当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端G为高电平时,输出Q0-Q7的状态与输入端D1-D7状态相同;当G发生负的跳变时,输入端D0-D7 数据锁入Q0-Q7。51单片机的ALE信号可以直接与74LS373的G 连接。在MCS-51单片机系统中,其连接方法如下图所示。其中输入端1D-8D接

至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允 许信号ALE。输出允许端OE接地,表示三态输出门一直导通,可以送出地址信 号。 1D-8D为8个输入端。 1Q-8Q为8个输出端。 【说明】基础比较好的同学请直接忽略。 G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。 OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。 (1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态); (2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态. 锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。

8255A的内部结构,由三部分电路组成:与CPU的接口电路、内部控制逻辑电路和与外设连接的输入/输出接口电路。 D7~D0(data bus):三态、双向数据线,与CPU数据总线连接,用来传送数据。 (chip select):片选信号线,低电平有效时,芯片被选中。 A1, A0(port address):地址线,用来选择内部端口。 (read):读出信号线,低电平有效时,允许数据读出。 (write):写入信号线,低电平有效时,允许数据写入。 RESET(reset):复位信号线,高电平有效时,将所有内部寄存器(包括控制寄存器)清0。 PA7~PA0(port A):A口输入/输出信号线。

PB7~PB0(port B):B口输入/输出信号线。 PC7~PC0(port C):C口输入/输出信号线。 VCC:+5V电源。GND:电源地线。 8255A的工作方式 方式0:基本输入输出方式 适用于无条件传送和查询方式的接口电路 方式1:选通输入输出方式 适用于查询和中断方式的接口电路 方式2:双向选通传送方式 适用于与双向传送数据的外设 适用于查询和中断方式的接口电路 8255A初始化编程 8255A的A,B,C三个端口的工作方式是在初始化编程时,通过向8255A的控制端口写入控制字来设定的。 8255A由编程写入的控制字有两个:方式控制字和置位/复位控制字。方式控制字用于设置端口A, B, C的工作方式和数据传送方向;置位/复位控制字用于设置C口的PC7~PC0中某一条口线PC i(i=0~7)的电平。两个控制字公用一个端口地址,由控制字的最高位作为区分这两个控制字的标志位。 (1)方式控制字的格式 8255A工作方式控制字的格式如图7.11所示。 D0:设置PC3~PC0的数据传送方向。D0=1为输入;D0=0为输出。 D1:设置B口的数据传送方向。D1=1为输入;D1=0为输出. D2:设置B口的工作方式。D2=1为方式1;D2=0为方式0。 D3:设置PC7~PC4的数据传送方向。D3=1为输入;D3=0为输出。 D4:设置A口的数据传送方向。D4=1为输入;D4=0为输出。 D6D5:设置A口的工作方式。D6D5=00为方式0,D6D5=01为方式1,D6D5=10或11为方式2。 D7:方式控制字的标志位,恒为1。 例如,将8255A的A口设定为工作方式0输入,B口设定为工作方式1输出,C口没有定义,

74系列芯片引脚图资料大全 作者:佚名来源:本站原创点击数:57276 更新时间:2007年07月26日【字体:大中小】 为了方便大家我收集了下列74系列芯片的引脚图资料,如还有需要请上电子论坛https://www.doczj.com/doc/1b13856107.html,/b bs/ 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373

反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND

74系列芯片引脚图、功能、名称、资料大全(含74LS、74HC等),特别推荐为了方便大家,我收集了下列74系列芯片的引脚图资料。 说明:本资料分3部分:(一)、TXT文档,(二)、图片,(三)、功能、名称、资料。 (一)、TXT文档 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门 LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373

反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘

1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门 74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器 74LS245 │20 19 18 17 16 15 14 13 12 11│ )│ DIR=1 A=>B │ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND

河北大学工商学院计算机接口课程结课作业 题目:可编程并行接口芯片8255A的功能及应用 姓名学号:XXXXXX 2011XXXXXX 自动化X班 XXXXXX 2011XXXXXX 自动化X班 XXXXXX 2011XXXXXX 自动化X班 XXXXXX 2011XXXXXX 通信工程X班 组别:第XXX组 指导教师:王竹毅 20XX年 XX月XX日

摘要:8255A是Intel公司为其80系列微处理器生产的通用可编程并行输入输出接口芯片,也可以与其他系列的微处理器配套使用。由于其通用性强,与微机接口连接方便,且可通过程序指定完成各种输入输出操作,因此在中小系统中有着广泛的应用。本文主要介绍了可编程并行接口芯片8255A的主要特点及其在工业控制中的应用。 关键词:微机系统;并行接口;8255A;工作方式; 并行输入/输出就是把若干个二进制位信息同时进行传送的数据传输方式,它具有传输速度快、效率高的优点。并行数据传输需用的信号线较多,不适合长距离传输,所以并行数据传输适用于数据传输率要求较高,且传输距离相对较短的场合。所谓可编程实际就是具有可选择性,并且是用编程的方法进行选择。选择端口与CPU之间采用哪种方式传送数据等,均可由用户在程序中写入方式字或控制字进行指定。Intel 8255A是一个通用的可编程的并行接口芯片,它有三个并行I/O口,又可通过编程设置多种工作方式,价格低廉、使用方便,可以直接与Intel系列的芯片连接使用,其具有广泛的适应性及很高的灵活性,在微机系统中的应用十分广泛。 一、8255A的基本特性 1.1 三个数据端口A,B,C 这三个端口均可看作是I/O口,但它们的结构和功能也稍有不同。 ·A口:是一个独立的8位I/O口,内部有对数据输入输出的锁存功能。 ·B口:也是一个独立的8位I/O口,仅有对输出数据的锁存功能。 ·C口:可以看作是一个独立的8位I/O口;也可以看作是两个独立的4位I/O口,仅有对输出数据的锁存功能。 1.2 A组和B组的控制电路 这是两组根据CPU命令控制8255A工作方式的电路,这些控制电路内部设有控制寄存器,可以根据CPU送来的编程命令来控制8255A的工作方式,也可以根据编程命令来对C口的指定位进行置位/复位的操作。 A组控制电路用来控制A口及C口的高4位(PC4-PC7); B组控制电路用来控制B口及C口的低4位(PC0-PC3);

74ls373引脚图管脚功能表 74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片, (1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态); (2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态. 锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7 数据锁入Q0~Q7。51单片机的ALE信号可以直接与74LS373的C连接。74ls373与单片机接口:

1D~8D为8个输入端。1Q~8Q为8个输出端。 G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。 OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。 在MCS-51单片机系统中,常采用74LS373作为地址锁存器使用,其连接方法如上图所示。其中输入端1D~8D接至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允许信号ALE。输出允许端OE接地,表示输出三态门一直打开

您的数字ID 是:463099 您的密码是:1.8667 附录三 常用芯片引脚图 一、单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O 接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时的地址/数据复用口。P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为通用I/O 接口,第二功能作为为单片机的控制信号。 ALE/PROG :地址锁存允许/编程脉冲输入信号线(输出信号) PSEN :片外程序存储器开发信号引脚(输出信号) EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD :复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc :主电源引脚(+5V ) Vss :数字电路地引脚(0V ) Vpd :内部RAM 备用电源引脚(+5V ) V REF :A/D 转换器基准电源引脚(+5V ) AGND :A/D 转换器参考地引脚 XTAL1、XTAL2:内部振荡器反相器输 P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS

反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS24 5 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373 反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│

Y =A+C )│四总线三态门74LS125 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器74LS245 │20 19 18 17 16 15 14 13 12 11│ )│ DIR=1 A=>B │1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND 页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器 正逻辑与门,与非门: Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与门74LS08 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ __ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与非门74LS00 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND Vcc 1C 1Y 3C 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ ___ │14 13 12 11 10 9 8│ Y = ABC )│ 3输入三正与非门74LS10 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 2A 2B 2C 2Y GND

8255芯片 8255是Intel公司生产的可编程并行I/O接口芯片,有3个8位并行I/O口。具有3个通道3种工作方式的可编程并行接口芯片(40引脚)。其各口功能可由软件选择,使用灵活,通用性强。8255可作为单片机与多种外设连接时的中间接口电路。 8255作为主机与外设的连接芯片,必须提供与主机相连的3个总线接口,即数据线、地址线、控制线接口。同时必须具有与外设连接的接口A、B、C口。由于8255可编程,所以必须具有逻辑控制部分,因而8255内部结构分为3个部分:与CPU连接部分、与外设连接部分、控制部分。 8255管脚 编辑本段特性 (1)一个并行输入/输出的LSI芯片,多功能的I/O器件,可作为CPU总线与外围的接口. (2)具有24个可编程设置的I/O口,即3组8位的I/O口为PA口,PB口和PC口.它们又可分为两组12位的I/O口,A组包括A口及C口(高4位,PC4~PC7),B组包括B口及C口(低4位,PC0~PC3).A组可设置为基本的I/O口,闪控(STROBE)的I/O闪控式,双向I/O3种模式;B组只能设置为基本I/O或闪控式I/O两种模式,而这些操作模式完全由控制寄存器的控制字决

定. 编辑本段引脚功能 RESET:复位输入线,当该输入端处于高电平时,所有内部寄存器(包括控制寄存器)均被清除,所有I/O口均被置成输入方式。 CS:芯片选择信号线,当这个输入引脚为低电平时,即/CS=0时,表示芯片被选中,允许8255与CPU进行通讯;/CS=1时,8255无法与CPU做数据传输. RD:读信号线,当这个输入引脚为低电平时,即/RD=0且/CS=0时,允许8255通过数据总线向CPU发送数据或状态信息,即CPU从8255读取信息或数据。 WR:写入信号,当这个输入引脚为低电平时,即/WR=0且/CS=0时,允许CPU将数据或控制字写入8255。 D0~D7:三态双向数据总线,8255与CPU数据传送的通道,当CPU 执行输入输出指令时,通过它实现8位数据的读/写操作,控制字和状态信息也通过数据总线传送。 PA0~PA7:端口A输入输出线,一个8位的数据输出锁存器/缓冲器,一个8位的数据输入锁存器。 PB0~PB7:端口B输入输出线,一个8位的I/O锁存器,一个8位的输入输出缓冲器。 PC0~PC7:端口C输入输出线,一个8位的数据输出锁存器/缓冲器,一个8位的数据输入缓冲器。端口C可以通过工作方式设定而分成2个4位的端口,每个4位的端口包含一个4位的锁存器,分别与端口A和端口B配合使用,可作为控制信号输出或状态信号输入端口。' A1,A0:地址选择线,用来选择8255的PA口,PB口,PC口和控制寄存器. 当A1=0,A0=0时,PA口被选择; 当A1=0,A0=1时,PB口被选择; 当A1=1,A0=0时,PC口被选择; 当A1=1.A0=1时,控制寄存器被选择. 编辑本段编程模型

附录三 常用芯片引脚图 一、 单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O 接口引脚、4条控制引脚、2条电源引 脚、2条时钟引脚。 引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时 的地址/数据复用口。 P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。 P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为 通用I/O 接口,第二功能作为为单片机的控 制信号。 ALE/ PROG :地址锁存允许/编程脉冲输入信号线(输出信号) PSEN :片外程序存储器开发信号引脚(输出信号) EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD :复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1 TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc :主电源引脚(+5V ) Vss :数字电路地引脚(0V ) Vpd :内部RAM 备用电源引脚(+5V ) V REF :A/D 转换器基准电源引脚(+5V ) AGND :A/D 转换器参考地引脚 12345678910111213141516171819204039383736353433323130292827262524232221P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS V CC P0.0/AD 0P0.1/AD 1 P0.2/AD 2P0.3/AD 3P0.4/AD 4P0.5/AD 5P0.6/AD 6P0.7/AD 7 EA/V PP ALE/PROG PSEN P2.7/A 15P2.6/A 14P2.5/A 13 P2.4/A 12P2.3/A 11P2.2/A 10P2.1/A 9P2.0/A 8803180518751

. 附录6 器件管脚图及功能表 74LS74双D 正沿触发器 74LS273八D 触发器 74LS377八D 触发器 74LS374八D 触发器 (三态输出) 74LS175双输出四D 触发器 74LS245 74LS161四位二进制同步计数器 74LS139双2:4译码器

74LS151 八选一选择器 74LS157 四个二选一选择器 74LS257 四个二选一选择器 (非反相三态输出) 注:i等于d2d1d0对应的十进制数 6116 2K*8 RAM 2716 2K*8 ROM2732 4K*8 ROM 74LS148 8:3八进制优先编码器 74LS85 四位幅度比较器 .

附录9微指令寄存器的各字段微操作信号输出去向及功能 指令字段IR7~0 .

附录10 联机通讯指南 一、准备 1、准备一台PC机。 2、把TEC-2机在实验台上放好打开,将TEC-2的随机电源放在TEC-2的左侧,并确认电源开关处在关断的位置。 二、连接电源线 1、将TEC-2机电源的直流输出插头P8插在TEC-2机垂直板左侧的插座P8上; 将TEC-2机电源的直流输出插头P9插在TEC-2水平板左侧的插座P9上。 特别提醒注意:不要接反P8和P9,否则会烧机器或电源。 2、将TEC-2电源的电源线一端接电源的交流输入插孔,另一端接220V交流电源接线盒。 注意:TEC-2电源的交流电源线必须和计算机的电源线接在同一个有地线的电源接线盒上,以保证两设备共地,否则可能烧毁电源或机器。 三、连接TEC-2和PC 1、准备好随机提供的TEC-2和PC的串口通讯电缆。该电缆一端是9孔的插头,另一端是25孔的插头。 注意:TEC-2随机提供多条通讯电缆,请务必正确选用,以免错误连接造成联机失败。 2、把串口通讯电缆的9孔插头接在TEC-2机的上板左下角V70插座上,25孔插头插在计算机的串口上(COM1或COM2)。 如果PC上没有25针的串口或者25针的串口已被其它设备占用,TEC-2 随机提供一个9转25的转换器可以把25孔的插头转换成9孔的插头,接在9针的串口上。 四、TEC-2的初始设置 将TEC-2大板下方钮子开关S2~S0拨成100(向上为“1”,向下为“0”); FS1~FS4拨成1010(向上为“1”,向下为“0”); 将CONT/STEP钮子开关拨到CONT位置。 五、开机 1、打开计算机电源开关,使计算机正常启动。 2、打开TEC-2电源开关,TEC-2大板左上角一排指示灯亮。 六、加载通讯软件 .

74 系列芯片的引脚图 [日期:2008-12-29 ] [来源:net 作者:佚名] [字体:大中小] (投递新闻) 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373 反相器: Vcc 6A6Y5A5Y4A4Y六非门74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A)│ │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A1Y2A2Y3A3Y GND 驱动器: Vcc 6A6Y5A5Y4A4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A)│六驱动器(OC高压输出) 74LS07 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A1Y2A2Y3A3Y GND Vcc -4C 4A4Y -3C 3A3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门74LS125 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘

-1C 1A1Y -2C 2A2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐8位总线驱动器74LS245 │20 19 18 17 16 15 14 13 12 11│ )│DIR=1 A=>B │ 1 2 3 4 5 6 7 8 9 10│DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND 页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器 正逻辑与门,与非门: Vcc 4B 4A4Y3B 3A3Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = AB )│2输入四正与门74LS08 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A1B 1Y2A2B 2Y GND Vcc 4B 4A4Y3B 3A3Y ┌┴—┴—┴—┴—┴—┴—┴┐ __ │14 13 12 11 10 9 8│ Y = AB )│2输入四正与非门74LS00 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A1B 1Y2A2B 2Y GND Vcc 1C 1Y3C 3B 3A3Y ┌┴—┴—┴—┴—┴—┴—┴┐ ___ │14 13 12 11 10 9 8│ Y = ABC )│3输入三正与非门74LS10 │1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A1B 2A2B 2C 2Y GND Vcc H G Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ )│8输入与非门74LS30 │1 2 3 4 5 6 7│________

74LS273与74LS373的区别 发表于2006-12-28 23:47:08 一位网友在中华工控网上问的问题,我看没什么人回答,就整理了一下,给他回答了,并发到我的blog上 74LS273 是带公共时钟复位八D触发器 74LS373 是三态同相八D锁存器 273与373的引脚排列是相同的,唯一的差别是两者1、11脚的功能不同. 对273 (1).1脚是复位CLR,低电平有效,当1脚是低电平时,输出脚2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部输出0,即全部复位; (2).当1脚为高电平时,11(CLK)脚是锁存控制端,并且是上升沿触发锁存,当11脚有一个上升沿,立即锁存输入脚3、4、7、8、13、14、17、18的电平状态,并且立即呈现在在输出脚2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)上. 对373: (1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态); (2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态. 所以,如果分别用273和373来作为单片机的地址锁存器的话, 对273来说,1(CLR)脚必须接高电平,ALE信号经过反相后接11脚(因为单片机的ALE信号是以下降沿方式出现) 对373来说,1脚接低电平,保证使能,11脚直接接单片机的ALE信号.

8255引脚图及引脚功能 单片机系统中常用的地址锁存器芯片74LS373以及coms的 74hc373。是带三态缓冲输出的8D触发器,其引脚图与结构原理图、电路连接图如下: <74LS373引脚图内部结构原理图电路连接图> E G 功 能 0 0 直通Qi = Di 0 1 保持(Qi保持不变) 1 X 输出高阻 <74LS373功能表> E G D Q

L H H H L H L L L L X Q 上表是74LS373的真值表,表中: L——低电平; H——高电平; X——不定态; Q0——建立稳态前Q的电平; G——输入端,与8031ALE连高电平:畅通无阻低电平:关门锁存。图中OE——使能端,接地。 当G=“1”时,74LS373输出端1Q—8Q与输入端1D—8D相同; 当G为下降沿时,将输入数据锁存。 8255A(2) 7.2 可编程并行接口 由于我们现在常用的微机系统均以并行方式处理数据,所以,

并行接口也是最常用的接口电路。并行接口有以下几方面的特点:(1)并行接口是在多根数据线上,以数据字节(字)为单位与输入/输出设备或被控对象传送信息的,如打印机接口、A/D、D /A转换器接口、IEEE-488接口、开关量接口、控制设备接口等。在实际应用中,凡在CPU与外设之间同时需要两位以上信息传送时,就要采用并行口。 并行口适用于近距离传送的场合。由于各种I/O设备和被控对象多为并行数据线连接,CPU用并行口来组成应用系统很方便,故使用十分普遍。 (2)并行传送的信息,不要求固定的格式,这与串行传送的信息有数据格式的要求不同。例如,异步串行通信的格式是一个数据,它包括起始位、数据位、校验位和停止位。 (3)从并行接口的电路结构来看,并行口有硬线连接接口和可编程接口之分。硬线连接接口的工作方式及功能用硬线连接来设定,用软件编程序的方法不能加以改变;如果接口的工作方式及功能可以用软件编程序的方法加以改变,则就叫可编程接口。 7.2.1 可编程并行接口芯片8255A 所谓可编程,实际上就是具有可选择性。例如,选择芯片中的哪一个或哪几个数据端口与外设连接;选择端口中的哪一位或哪几位作输入,哪一位或哪几位作输出;选择端口与CPU之间采用哪种方式传送数据等,均可由用户在程序中写入方式字或控制字来进行指定。

附录三 常用芯片引脚图 一、单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O接口引脚、4条控制引脚、2条电源引 脚、2条时钟引脚。 引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为 通用I/O接口,第二功能作为存储器扩展时 的地址/数据复用口。 P1.0~P1.7:P1口8位口线,通用I/O接口 无第二功能。 P2.0~P2.7:P2口8位口线,第一功能作为 通用I/O接口,第二功能作为存储器扩展时 传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为 通用I/O接口,第二功能作为为单片机的控 制信号。 ALE/ PROG:地址锁存允许/编程脉冲输入信号线(输出信号) PSEN:片外程序存储器开发信号引脚(输出信号) EA/Vpp:片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD:复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1 TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc:主电源引脚(+5V) Vss:数字电路地引脚(0V) Vpd:内部RAM备用电源引脚(+5V) V REF:A/D转换器基准电源引脚(+5V)P1.0 P1.1 P1.2 P1.3 P1.4 P1.5 P1.6 P1.7 RST INT0/P3.2 INT1/P3.3 WR/P3.6 RD/P3.7 XTAL2 XTAL1 V SS

74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片.本文将介绍74ls373的工作原理,引脚图(管脚图),内结构图、主要参数及在单片机系统中的典型应用电路. 74ls373工作原理简述: (1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态); (2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态. 锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。 74ls373内部逻辑结构图

74LS373的真值表(功能表),表中: L——低电平; H——高电平; X——不定态; Q0——建立稳态前Q的电平;

G——输入端,与8031ALE连高电平:畅通无阻低电平:关门锁存。图中OE——使能端,接地。 当G=“1”时,74LS373输出端1Q—8Q与输入端1D—8D相同; 当G为下降沿时,将输入数据锁存。 E G 功能 0 0 直通Qi = Di 0 1 保持(Qi保持不变) 1 X 输出高阻 74ls373引脚(管脚)排列图:

8253引脚图及引脚定义 作者:来源:本站原创点击数:更新时间:2007年07月24日 8253是在单片机系统常用的定时/计数器接口芯片,他能扩展几个定时/计数器,而不占用单片机的cpu时间,而且在pc机的应用很很广。 下面介绍8253引脚图和内部结构及引脚定义等。 8253由以下几个部分组成: (1) 数据总线缓冲器(8位、三态、双向); (2) 读/写控制逻辑; CS:片选信号,低电平有效; RD:读信号,低电平有效; WR:写信号,低电平有效 A1A0:端口选择信号 (3) 三个通道( 0 ~ 2); (4) 一个控制寄存器; 《8253引脚图》

当A1A0分别为00 01 10 11时分别选中三个通道和控制字寄存器在8088系统中,8088的A1A0分别与8253的A1A0相连在8086系统中,通常将8253的8位数据线与8086的低8位相连,即使用偶地址,所以8086的A2A1分别与8253的A1A0相连 Intel 8253是一片具有三个独立的16位计数器通道的可编程定时器/计数器芯片。每个通道都可以编程设定6种工作方式之一种; 由于8253的读/写操作对系统时钟没有特殊的要求,因此它几乎可以应用与由任何一种微处理器组成的系统中,可作为可编程的方波频率发生器、分频器、实时时钟、事件计数器和单脉冲发生器等。 表8-4 控制功能表

16位计数初值寄存器、减一计数器和输出锁存器。作定时器用:其CLK端上的输入脉冲应是标准的、精确的;作计数器用:对其CLK端上的脉冲计数,脉冲宽度可以不等。采用减一计数器,为0时,从OUT端上输出一个脉冲定时时间 = 8253在 PC机中的应用 例8.5.2: 设计一个程序,使扬声器发出600Hz频率的声音,按下任意键声音停止。PC机的发声系统以计数器2为核心。CLK2的输入频率1.19MHz,改变计数器初值可以由OUT2得到不同频率的方波输出对于600Hz,计数初值1.19MHz/60 0Hz=1938,发声系统受8255芯片B口的两个输出端线PB0、PB1的控制。PB0为1,使GATE2为1,计数器2能正常计数。PB1为1,打开输出控制门。 CODE SEGMENT ASSUME CS:CODE START:IN AL, 61H //8253端口 OR AL, 03H OUT 61H, AL MOV AX, 1983 OUT 42H, AL

74ls373引脚图,内部结构,参数,应用电路(74ls373中文资料) 74ls373功能简介: 74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片.本文将介绍74ls373的工作原理,引脚图(管脚图),内结构图、主要参数及在单片机系统中的典型应用电路. 74ls373工作原理简述: 74ls373内部逻辑结构图 74LS373的真值表(功能表),表中:

L——低电平; H——高电平; X——不定态; Q0——建立稳态前Q的电平; G——输入端,与8031ALE连高电平:畅通无阻低电平:关门锁存。图中OE——使能端,接地。 当G=“1”时,74LS373输出端1Q—8Q与输入端1D—8D相同;

74ls373电气特性 74ls373推荐工作条件 74ls373在单片机系统中的应用电路图: 当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7 数据锁入Q0~Q7。51单片机的ALE信号可以直接与74LS373的C连接。在MCS-51单片机系统中,常采用74LS373作为地址锁存器使用,其连接方法如上图所示。其中输入端1D~8D接至单片机的P0口,输出端提供的是低8位地址,G

端接至单片机的地址锁存允许信号ALE。输出允许端OE接地,表示输出三态门一直打开。 1D~8D为8个输入端。 1Q~8Q为8个输出端。 G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。 OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。 (1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态); (2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出 2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态. 锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。