ATmega128 专用寄存器查询表

一、I/O口寄存器

1、数据方向控制寄存器

数据方向控制寄存器总共有DDRA、DDRB、DDRC、DDRD、DDRE、DDRF、DDRG等7个

D DRx

D7 D6D5D4D3D2D1D0

说明:对应的位置1,定义为输出,对应的位置0,定义为输入

2、输出数据寄存器

数据寄存器总共有PORTA、PORTB、PORTC、PORTD、PORTE、PORTF、PORTG 等7个。

PORTx

D7 D6D5D4D3D2D1D0

说明:对应的位置1,输出为1,对应的位置0,为输出为0。

3、输入数据寄存器

数据寄存器总共有PINA、PINB、PINC、PIND、PINE、PINF、PING等7个。

PINx

D7 D6D5D4D3D2D1D0

说明:如果对应位为1,对应引脚输入高电平,如果对应位为0,对应引脚输入低电平。

二、定时器\计数器寄存器

1、特殊功能寄存器

SFIOR

D7 D6D5D4D3D2D1D0

TSM ACME PUD PSR0 PSR321 说明:Bit 7、T\C同步模式Bit 1 T/C0预分频器复位

Bit 0 T/C1 T/C1 T/C2预分频器复位

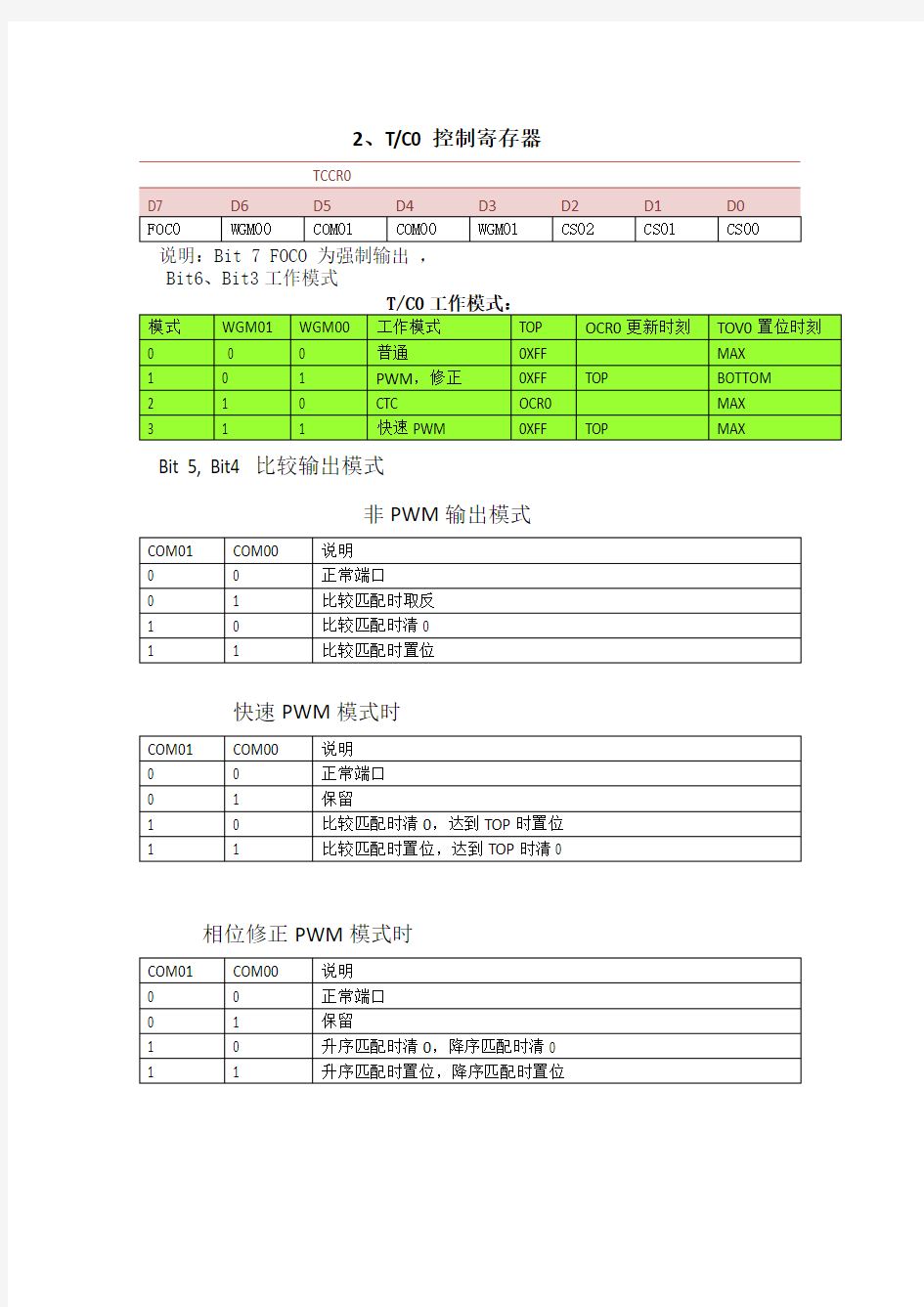

2、T/C0控制寄存器

TCCR0

D7 D6D5D4D3D2D1D0

FOC0 WGM00 COM01 COM00 WGM01 CS02 CS01 CS00

说明:Bit 7 FOCO 为强制输出,

Bit6、Bit3工作模式

T/C0工作模式:

模式WGM01 WGM00 工作模式TOP OCR0更新时刻TOV0置位时刻

0 0 0 普通0XFF MAX

1 0 1 PWM,修正0XFF TOP BOTTOM

2 1 0 CTC OCR0 MAX

3 1 1 快速PWM 0XFF TOP MAX

Bit 5, Bit4 比较输出模式

非PWM输出模式

COM01 COM00 说明

0 0 正常端口

0 1 比较匹配时取反

1 0 比较匹配时清0

1 1 比较匹配时置位

快速PWM模式时

COM01 COM00 说明

0 0 正常端口

0 1 保留

1 0 比较匹配时清0,达到TOP时置位

1 1 比较匹配时置位,达到TOP时清0

相位修正PWM模式时

COM01 COM00 说明

0 0 正常端口

0 1 保留

1 0 升序匹配时清0,降序匹配时清0

1 1 升序匹配时置位,降序匹配时置位

Bit 2 、Bit 1 、Bit0 时钟选择

CS02 CS01 CS00 说明

0 0 0 无时钟,不工作

0 0 1 无分频

0 1 0 1/8分频

0 1 1 1/32

1 0 0 1/64

1 0 1 1/128

1 1 0 1/256

1 1 1 1/1024

T/C0的计数寄存器

TCNT0

7 6543210

输出比较寄存器

OCR0

7 6543210

T/C中断屏蔽寄存器

TIMSK

7 6543210

OCIE0 TOIE0 Bit 1输出比较匹配使能Bit 0 T/C0 溢出使能

T/C中断标志寄存器

TIFR

7 6543210

OCF0 TOV0 Bit 1输出比较匹配标志Bit 0 T/C0 溢出标志

2、定时/计数器2(大多定时/计数器1大多一样,注意区分)

定时/计数器2控制器寄存器

TCCR2

7 6543210

FOC2 WGM20 COM21 COM20 WGM21 CS22 CS21 CS020 说明:Bit 7 强制输出比较Bit6、Bit3波形产生模式

Bit 5, Bit4 比较输出模式Bit 2 、Bit 1 、Bit0 时钟选择

CS22 CS21 CS20 说明

0 0 0 无时钟,不工作

0 0 1 无分频

0 1 0 1/8分频

0 1 1 1/64

1 0 0 1/256

1 0 1 1/1024

1 1 0 从T2引脚外部时钟源。为下降沿1 1 1 从T2引脚外部时钟源。为上升沿

T/C2的计数寄存器

TCNT2

7 6543210

输出比较寄存器

OCR2

7 6543210

T/C中断屏蔽寄存器

TIMSK

7 6543210

OCIE2 TOIE2 OCIE0 TOIE1 Bit 7输出比较匹配使能Bit 6 T/C0 溢出使能

T/C中断标志寄存器

TIFR

7 6543210

OCF2 TOV2 OCF0 TOV0 Bit 7 输出比较匹配标志Bit 6 T/C0 溢出标志

3、16为定时/计数器(注意定时器1和定时器3功能基本一样只是寄存器不同而已)

定时器/计数器1控制寄存器A

TCCR1A

7 6543210

COM1A1 COM1A0 COM1B1 COM1B0 COM1C1 COM1C0 WGM11 WGM10

定时/计数器3控制寄存器A

TCCR3A

7 6543210

COM3A1 COM3A0 COM3B1 COM3B0 COM3C1 COM3C0 WGM31 WGM30

Bit7 Bit 6:通道A比较输出模式Bit 5 Bit 4:通道B比较输出模式

Bit 4 Bit 3:通道C比较输出模式

如果COMnA1:0(COMnB1:0或COMnC1:0)的一位或两位被写入"1”,OCnA(OCnB或OCnC) 输出功能将取代I/O 端口功能

比较输出模式,非PWM

COMnA1/COMnB1/COMnC1 COMnA0/COMnB0/COMnC0 说明

0 0 普通端口

0 1 比较匹配时OCnA/OCnB/0CnC电平取反

1 0 比较匹配时OCnA/OCnB/0CnC清0(低电平)1 1 比较匹配时OCnA/OCnB/0CnC置位(高电平)

比较输出模式,快速PWM

COMnA1/COMnB1/COMnC1 COMnA0/COMnB0/COMnC0 说明

0 0 普通端口

0 1 WGMn3=0: 普通端口

WGMn3=1:比较匹配时OCnA取反

OCnB/0CnC保留

1 0 比较匹配时清零OCnA/OCnB/0CnC

在TOP时OCnA/OCnB/0CnC置位

1 1 比较匹配时置位OCnA/OCnB/0CnC

在TOP时清零OCnA/OCnB/0CnC

比较输出模式,相位修正PWM

COMnA1/COMnB1/COMnC1 COMnA0/COMnB0/COMnC0 说明

0 0 普通端口

0 1 WGMn3=0: 普通端口

WGMn3=1:比较匹配时OCnA取反

OCnB/0CnC保留

1 0 升序匹配时清零OCnA/OCnB/0CnC

降序时OCnA/OCnB/0CnC置位

1 1 升序匹配时置位OCnA/OCnB/0CnC

降序时清零OCnA/OCnB/0CnC

波形发生模式

定时器/计数器1控制寄存器B

TCCR1B

7 6543210

ICNC1 ICES1 -------- WGM13 WGM12 CS12 CS11 CS10

定时器/计数器3控制寄存器B

TCCR3B

7 6543210

ICNC3 ICES3 -------- WGM33 WGM32 CS32 CS31 CS30

Bit 7 : 入捕捉噪声抑制器

Bit 6 : 输入捕捉触发沿选择

Bit 5 –保留位

Bit 4:3: 波形发生模式

Bit 2:0 : 时钟选择具体选择如下

CSn2 CSn1 CSn0 说明

0 0 0 无时钟,不工作

0 0 1 无分频

0 1 0 1/8分频

0 1 1 1/64

1 0 0 1/256

1 0 1 1/1024

1 1 0 从Tn引脚外部时钟源。为下降沿1 1 1 从Tn引脚外部时钟源。为上升沿

定时器/计数器1控制寄存器C

TCCR1C

7 6543210 FOCIA FOC1B FOC1C

定时器/计数器3控制寄存器C

TCCR3C

7 6543210

FOC3A FOC3B FOC3C

Bit7:强制输出比较通道A

Bit6: 强制输出比较通道B

Bit5: 强制输出比较通道C

定时器/计数器1(TCNT1H和TCNT1L)

定时器/计数器3(TCNT3H和TCNT3L)

输出比较寄存器1A(OCR1AH 和OCR1AL)

输出比较寄存器1B(OCR1BH 和OCR1BL)

输出比较寄存器1C(OCR1CH 和OCR1CL)

输出比较寄存器3A(OCR3AH 和OCR3AL)

输出比较寄存器3B(OCR3BH 和OCR3BL)

输出比较寄存器3C(OCR3CH 和OCR3CL)

输入捕捉寄存器1(ICR1H和ICR1L)

输入捕捉寄存器3(ICR3H和ICR3L)

定时器/计数器中断屏蔽寄存器

TIMSK

76543210 OCIE2 OCIE2 TICIE1 OCIE1A OCIE1B TOIE1 OCIE0 OCIE0 ? Bit 5 – ICF1: T/C1 输入捕捉中断使能

? Bit 4 – OCF1A: T/C1 输出比较A 匹配中断使能

Bit 3 – OCF1B: T/C1 输出比较B 匹配中断使能

? Bit 2 – TOV1: T/C1 溢出中断使能

扩展定时器/计数器中断屏蔽寄存器

TETIMSK

7 6543210

TICIE3 OCIE3A OCIE3B TOIE3 OCIE3C OCIE1C ? Bit 5 – : T/C3 输入捕捉中断使能

? Bit 4 –: T/C3输出比较A 匹配中断使能

Bit 3 – : T/C3 输出比较B 匹配中断使能

? Bit 2 – : T/C3 溢出中断使能

Bit1--: T/C3输出比较C匹配中断使能

Bit 0 T/C1输出比较C 匹配中断使能

定时器/计数器中断标志寄存器

TIFR

7 6543210

ICF1 OCF1A OCF1B TOV1

? Bit 5 – ICF1: T/C1 输入捕捉标志位

? Bit 4 – OCF1A: T/C1 输出比较A 匹配标志位

Bit 3 – OCF1B: T/C1 输出比较B 匹配标志位

? Bit 2 – TOV1: T/C1 溢出标志

扩展定时器/计数器中断标志寄存器

ETIFR

7 6543210

ICF3 OCF3A OCF3B TOV3 OCIE3C OCIE1C ? Bit 5 – ICF3: T/C3 输入捕捉标志位

? Bit 4 – OCF3A: T/C3 输出比较A 匹配标志位

Bit 3 – OCF3B: T/C3 输出比较B 匹配标志位

? Bit 2 – TOV3: T/C3 溢出标志

Bit 1:T/C3 输出比较C 匹配标志位

Bit 0:T/C1 输出比较C 匹配标志位

三、同步串行口(SPI)

SPI 控制寄存器- SPCR

SPIC

7 6 5 4 3 2 1 0

SPIE SPE DORD MSTR COPL CPHA SPR1 SPR0

Bit 7 – SPIE: 使能SPI 中断? Bit 6 – SPE: 使能SPI

? Bit 5 – DORD: 数据次序(置位时LSB首发,否则MSB首发)

? Bit 4 – MSTR: 主/ 从选择

? Bit 3 – CPOL: 时钟极性

? Bit 2 – CPHA: 时钟相位

? Bits 1, 0 – SPR1, SPR0: SPI 时钟速率选择1 与0

SPI 状态寄存器

SPSR

7 6 5 4 3 2 1 0

SPIE WCOL SPI2X ? Bit 7 – SPIF: SPI 中断标志? Bit 6 – WCOL: 写碰撞标志

? Bit 0 – SPI2X: SPI 倍速(置位后,若为主机,SCK频率可达CPU频率的一半,若为从机只能保证fosc/4)

SPI 数据寄存器

SPDR

7 6 5 4 3 2 1 0

MSB LSB 四、USART 寄存器

USART数据寄存器

UDR

RXB(7:0)

TXB(7:0)

注意:USART 发送数据缓冲寄存器和USART 接收数据缓冲寄存器共享相同的I/O 地址,称为USART 数据寄存器或UDR。将数据写入UDR 时实际操作的是发送数据缓冲器存器(TXB),读UDR 时实际返回的是接收数据缓冲寄存器(RXB) 的内容。

USART 控制和状态寄存器A

UCSRnA

7 6 5 4 3 2 1 0 RXCn TXCn UDREn FEn DORn UPEn U2Xn MPCMn ? Bit 7 – RXCn: USART 接收结束(不要求写,只能读(R))

? Bit 6 – TXCn: USART 发送结束(发送缓冲器(UDR) 为空时TXC 置位)

? Bit 5 – UDREn: USART 数据寄存器空(R)? Bit 4 – FEn: 帧错误(R)

? Bit 3 – DORn: 数据溢出(R)? Bit 2 –UPEn: 奇偶校验错误(R)

? Bit 1 – U2Xn: 倍速发送? Bit 0 – MPCMn: 多处理器通信模式

USART 控制和状态寄存器B

UCSRnB

7 6 5 4 3 2 1 0 RXCIEn TXCIEn UDRIEn RXENn TXENn UCSZn2 RXB8n TXB8n ? Bit 7 – RXCIEn: 接收结束中断使能? Bit 6 – TXCIEn: 发送结束中断使能? Bit 5 – UDRIEn: USART 数据寄存器空中断使能? Bit 4 – RXENn: 接收使能? Bit 3 – TXENn: 发送使能? Bit 2 – UCSZn2: 字符长度

? Bit 1 – RXB8n: 接收数据位8 ? Bit 0 – TXB8n: 发送数据位8

注意:对9 位串行帧进行操作时,RXB8 是第9 个数据位。读取UDR 包含的低位数据之前首先要读取RXB8。

对9 位串行帧进行操作时,TXB8 是第9 个数据位。写UDR 之前首先要对它进行写操作。

USART 控制和状态寄存器C

UCSRnC

7 6 5 4 3 2 1 0

UMSELn UPMn1 UPMn0 USBSn UCSZn1 UCSZn0 UCPOLn

? Bit 6 – UMSEL: USART 模式选择

? Bit 5:4 – UPM1:0: 奇偶校验模式

? Bit 3 – USBS: 停止位选择

? Bit 2:1 – UCSZ1:0: 字符长度

? Bit 0 – UCPOL: 时钟极性

USART波特率寄存器

UBRRnH UBRRnL

UBRRn[11:8] UBRRnH UBRRn[7:0] UBRRnL

常用波特率表

五、TWI 寄存器

TWI 比特率寄存器

T WBR

7 6 5 4 3 2 1 0 TWBR7 TWBR6 TWBR5 TWBR4 TWBR3 TWBR2 TWBR1 TWBR0

TWI 控制寄存器

T WCR

7 6 5 4 3 2 1 0 TWINT TWEA TWSTA TWSTO TWWC TWEN TWIE ? Bit 7 – TWINT: TWI 中断标志? Bit 6 – TWEA: 使能TWI 应答

? Bit 5 – TWSTA: TWI START 状态标志? Bit 4 – TWSTO: TWI STOP 状态标志? Bit 3 – TWWC: TWI 写碰撞标志? Bit 2 – TWEN: TWI 使能

? B it 0 – TWIE: 使能TWI 中断

T WI 状态寄存器

T WSR

7 6 5 4 3 2 1 0 TWS7 TWS6 TWS5 TWS4 TWS3 TWPS1 TWPS0 ? Bits 7..3 – TWS: TWI 状态

? Bits 1..0 – TWPS: TWI 预分频位

TWI 数据寄存器

T WDR

7 6 5 4 3 2 1 0 TWD7 TWD6 TWD5 TWD4 TWD3 TWD2 TWD1 TWD0

TWI( 从机) 地址寄存器

T WAR

7 6 5 4 3 2 1 0 TWA6 TWA5 TWA4 TWA3 TWA2 TWA1 TWA0 TWGCR ? Bits 7..1 – TWA: TWI 从机地址寄存器其值为从机地址。

? Bit 0 – TWGCE: 使能TWI 广播识别置位后MCU 可以识别TWI 总线广播。

具体使用如下

六、模拟比

特殊功能寄存器

SFIOR

7 6543210

TSM ACME PUD PSR0 PSR321 ? Bit 3 – ACME: 模拟比较器多路复用器使能

当此位为逻辑"1”,且ADC 处于关闭状态(ADCSRA 寄存器的ADEN 为"0”) 时,ADC 多路复用器为模拟比较器选择负极输入。当此位为"0” 时,AIN1 连接到比较器的负极输入端。

模拟比较器控制和状态寄存

ACSR

7 6 5 4 3 2 1 0

ACD ACB ACO ACI ACIE ACIC ACIS1 ACSI0 ? Bit 7 – ACD: 模拟比较器禁用(置位时)

? Bit 6 – ACBG 选择模拟比较器能隙基准源(置位时)

? Bit 5 – ACO: 模拟比较器输出(不要求写)

? Bit 4 – ACI: 模拟比较器中断标志

? Bit 3 – ACIE: 模拟比较器中断使能? Bit 2– ACIC: 模拟比较器输入捕捉使能? Bits 1, 0 – ACIS1, ACIS0: 模拟比较器中断模式选择位

七、A/D转化ADC

ADC多工选择寄存器

ADMUX

7 6 5 4 3 2 1 0 REFS1 REFS0 ADLAR MUX4 MUX3 MUX2 MUX1 MUX0 ? Bit 7:6 – REFS1:0: 参考电压选择

? Bit 5 – ADLAR: ADC 转换结果左对齐。

ADLAR置位时转换结果为左对齐,否则为右对

? Bits 4:0 – MUX4:0: 模拟通道与增益选择位

ADC 控制和状态寄存器A

ADCSRA

7 6 5 4 3 2 1 0 ADEN ADSC ADFR ADIF ADIE ADPS2 ADPS1 ADPS0 ? Bit 7 – ADEN: ADC 使能? Bit 6 – ADSC: ADC 开始转换

? Bit 5 – ADATE: ADC连续转化选择(置位时连续转化,为零停止转化)? Bit 4 – ADIF: ADC 中断标志

? Bit 3 – ADIE: ADC 中断使能? Bits 2:0 – ADPS2:0: ADC 预分频器选择位

ADC 数据寄存器

ADLAR=0

ADCH ADCL

ADCH ADC9 ADC8 ADCL ADC[7:0]

ADLAR=1

ADCH ADCL

ADC9 ADC8 ADC3 ADC2 ADC1 ADC0

STM32库函数操作和寄存器操作 首先,两个都是C语言。从51过渡过来的话,就先说寄存器操作。每个MCU都有自己的寄存器,51是功能比较简单的一种,相应的寄存器也比较少,我们常用的就那么几个,像P0 P1 SMOD TMOD之类的,这些存在于标准头文件reg.h里面,因为少,所以大家就直接这么去操作了,每一位对应的意义随便翻一下手册就看得到,甚至做几个小项目就记的很清楚了。所以做51开发的时候大多数都是直接操作寄存器。 到了STM32,原理一样,也是有自己的寄存器,但是作为一款ARM 内核的芯片,功能多了非常多,寄存器自然也就多了很多,STM32的手册有一千多页,这时候想去像51那样记住每个寄存器已经不现实了,所以ST的工程师就给大家提供了库函数这么一个东西。这是个神器。库函数里面把STM32的所有寄存器用结构体一一对应并且封装起来,而且提供了基本的配置函数。我们要去操作配置某个外设的时候不需要再去翻眼花缭乱的数据手册,直接找到库函数描述拿来就可以用,这样就能把精力放在逻辑代码的开发上,而不是去费力的研究一个芯片的外设要怎么配置寄存器才能驱动起来。简单讲就是这些了,库函数是为了让开发者从大量繁琐的寄存器操作中脱离出来的一个文件包,在使用一个外设的时候让开发者直接去调用相应的驱动函数而不是自己去翻手册一个一个配置寄存器。有人说用库函数掌握不到芯片的精髓,见仁见智了。熟悉一款芯片是在不断的开发使用中逐渐了解并掌握的,调试的过程中会遇到很多问题,会要求我们去跟踪相关寄存器的状态,在整个框架都已经建立起来的基础上再去对照手册做具体到寄存器每一位的分析,代码对照现象,很快就能积累起来经验,祝成功。

第三章习题参考答案 1.画出以1)(2 4 6 +++=x x x x f 为联接多项式的线性移位寄存器逻辑框图,及其对应的状态图。 解:由1)(2 46+++=x x x x f ,得反馈函数为531621),,,(x x x x x x f ++=Λ,故 (1)逻辑框图: (2)状态图: 状态圈-1: 状态圈-2: 状态圈-3: 状态圈-4: 状态圈-5: 状态圈-6: 状态圈-7: 状态圈-8:

状态圈-9: 状态圈-10: 状态圈-11: 状态圈-12: 2.已知图3-2所示的7级线性反馈移位寄存器: 图3-2 (1)绘出该移位寄存器的线性递推式,联接多项式及特征多项式。 (2)给出状态转移矩阵。 (3)设初态为(1 1 1 1 1 1 1),给出输出序列a 。 解:(1)由逻辑框图得,递推式为: k k k k a a a a ++=+++357 ()0≥k 。 联接多项式为:7 4 2 1)(x x x x f +++=。 特征多项式为:7531)(~ x x x x f +++=

(2)状态转移矩阵:? ? ???? ? ?? ? ? ??0100000 101000000010001000100 000001000000011000000。 (3)输出序列:)111111111(ΛΛ=- a 。 3.设5级线性反馈移位寄存器的联接多项式为1)(2 5 ++=x x x f ,初态为(10101)。求输出序列a 。 解:由联接多项式得,反馈函数为:41521),,,(x x x x x f +=Λ。故以)10101(为初态的状态转移图为: 10101 01010001010001000001100000100000100100100100110100110100110100110100111100111100111101111101111001110001110001110000110010110110111110101110101110101110101→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→ 由此可得,输出序列为:=a 44444443444444421一个周期 0110100100000011111001010111011…。 4.证明:n 级线性反馈移位寄存器的状态转移变换是n 维线性空间n F 2上的线性变换。 证明:设f T 为n 级线性移位寄存器的状态转移变换,对n F 2,∈?βα,令),,,(110-=n a a a Λα, ),,,(110-=n b b b Λβ,有: ),,,(),,,()(121110∑=--==n i i n i n f f a c a a a a a T T ΛΛα, ),,,(),,,()(1 21110∑=--==n i i n i n f f b c b b b b b T T ΛΛβ。 ) ()() ,,,(),,,() )(,,,() ,,,()(1 211 2112211111100βαβαf f i n n i i i n n i i n i i n i n i n n f f T T b c b b a c a a b a c b a b a b a b a b a T T +=+=+++=+++=+-=-==----∑∑∑ΛΛΛΛ 对 2F k ∈?, ))((),,,(),,,()(1 21110ααf i n n i i n f f T k a c k ka ka ka ka ka T k T ===-=-∑ΛΛ。 故n 级线性反馈移位寄存器的状态转移变换是n 为线性空间n F 2上的线性变换。

STM32单片机GPIO寄存器的功能解析 1、GPIO的寄存器按照功能可以分为以下几类: A、配置寄存器 B、数据寄存器 C、位寄存器 D、锁定寄存器 2、对于GPIO端口,每个端口有16个引脚,每个引脚的模式由寄存器的四个位控制,每四位又分为两位控制引脚配置(CNFy[1:0]),两位控制引脚的模式及最高速度(MODEy [1:0]),其中y表示第y个引脚。配置GPIO引脚模式的一共有两个寄存器,CRH是高寄存器,用来配置高8位引脚,还有CRL配置低八位引脚。 3、端口位设置\清除寄存器(GPIOx_BSRR) 一个引脚y的输出数据由GPIOx_BSRR寄存器位的2个位来控制分别为BRy (Bit Reset y)和BSy (Bit Set y),BRy位用于写1清零,使引脚输出低电平,BSy位用来写1置1,使引脚输出高电平。而对这两个位进行写零都是无效的。 4、Cortex-M3有32根地址线,所以它的 寻址空间大小为2 bit=4GB。ARM公司设计时,预先把这4GB的寻址空间大致地分配好了。它把地址从0x4000 0000至0x5FFF FFFF(512MB )的地址分配给片上外设。 5、stm32f10x.h这个文件中重要的内容就是把STM32的所有寄存器进行地址映射。如同51单片机的头文件一样,stm32f10x.h像一个大表格,我们在使用的时候就是通过宏定义进行类似查表的操作。 6、STM32总线有AHB总线、APB2总线、APB1总线 7、时钟系统。 A、从时钟频率来说分为告诉时钟和低速时钟,高速时钟是提供给芯片主体时钟,而低速时钟只是提供给芯片中的RTC及独立看门狗使用。 B、从芯片角度来说,时钟源分为内部时钟与外部时钟源,内部时钟是在芯片内部RC振

第10章移位寄存器 本章大纲 10.1 基本移位寄存器功能 10.2 串行进入/串行输出移位寄存器 10.3 串行进入/并行输出移位寄存器 10.4 并行进入/串行输出移位寄存器 10.5 并行进入/ 并行输出移位寄存器 10.6 双向移位寄存器 10.7 移位寄存器计数器 10.8 移位寄存器应用 10.9 故障检测 10.10 关联标注的逻辑符号 10.11 CPLD简介 10.12 数字系统应用 本章学习目标 ?识别移位寄存器中数据运动的基本方式 ?解释串行进入/串行输出、串行进入/并行输出、并行进入/串行输出和并行进入/并 行输出移位寄存器是怎样运行的 ?描述双向移位寄存器怎样运行 ?确定约翰逊计数器的序列 ?设置环形计数器以产生指定序列 ?从移位寄存器中构建环形计数器 ?使用移位寄存器作为时间延迟设备 ?使用移位寄存器来实现串行到并行数据的变换器 ?实现基本移位寄存器控制的键盘译码器 ?通过用已知的测试模式“运行”系统来对数字系统进行故障检测 ?解释关联标注的ANSI/IEEE标准91-1984移位寄存器 ?描述基本的CPLD ?在系统应用中使用移位寄存器 重要术语 ?寄存器 ?级

?移位 ?载入 ?双向 ?CPLD ?逻辑阵列块(LAB) ?宏单元 简介 移位寄存器是紧密关联于数字计数器的序列逻辑电路的一种类型。寄存器主要用来存 储数字数据并且一般不具有特征内部状态序列,而计数器则具有这样的序列。但是也有例外,我们将在10.7节介绍它们。 在本章中,我们将学习移位寄存器的基本类型并展示几个应用。同时,我们还介绍了一种重要的故障检测方法。本章还介绍了复杂可编程逻辑设备(CPLD)。 固定功能逻辑器件 74HC164 74HC165 74HC174 74HC194 74HC195 可编程逻辑器件 MAX 7000 ·数字系统应用概述 数字系统应用阐释了本章中的概念。我们介绍了一个控制建筑物中警报器的安全进入系统。该系统使用两种类型的寄存器以及前几章所介绍的其他类型的设备。该系统同时还含有一个存储器,其将是第12章数字系统应用的重点。 学习本章内容可访问https://www.doczj.com/doc/1113619627.html,/floyd。 10.1 基本移位寄存器功能 移位寄存器由一组触发器组成,在数字系统中涉及数据存储和移位方面的应用中是很 重要的。寄存器和计数器不同,除了一些特别专业的应用之外,都没有特定的状态序列。一般来说,寄存器主要用来存储和移位外部数据源进入其中的数据(1和0),并且一般不具有特征内部状态序列。 学完本节之后,你应当能够 ?解释触发器怎样存储一个数据位 ?定义移位寄存器的存储容量 ?定义寄存器的移位能力 □寄存器可以由一个或者多个用以存储和移位数据的触发器组成。 寄存器是一种具有两种基本功能的数字电路:数据存储和数据移动。寄存器的存储能

CRC寄存器 (一种算法,用以确认发送过程中是否出错)数据寄存器:CRC_DR 可读写,复位值:0xFFFF FFFF; 独立数据寄存器:CRC_IDR 临时存放任何8位数据; 控制寄存器:CRC_CR 只零位可用,用于复位CRC,对其写1复位,由硬件清零; PWR电源控制(控制和管理电源) 电源控制寄存器:PWR_CR 控制选择系统的电源 电源控制/状态寄存器:PWR_CSR 睡眠或待机模式电源控制 BKP备份寄存器(用以控制和管理备份数据) 备份数据寄存器x:BKP_DRx (x = 1 … 10) 10个16位数据寄存器用以存储用户数据 RTC时钟校准寄存器:BKP_RTCCR 控制实时时钟的运行 备份控制寄存器:BKP_CR 控制选择清除备份数据的类型

备份控制/状态寄存器:BKP_CSR 对侵入事件的控制 RCC寄存器(时钟的选择、复位、分频) 时钟控制寄存器(RCC_CR) 各时钟状态显示 时钟配置寄存器(RCC_CFGR) 时钟分频 时钟中断寄存器(RCC_CIR) 控制就绪中断使能与否 APB2外设复位寄存器(RCC_APB2RSTR) APB1外设复位寄存器(RCC_APB1RSTR) 复位APB各功能寄存器 AHB外设时钟使能寄存器(RCC_AHBENR) AHB时钟使能控制 APB2外设时钟使能寄存器(RCC_APB2ENR) APB1外设时钟使能寄存器(RCC_APB1ENR) APB1时钟使能控制 备份域控制寄存器(RCC_BDCR) 备份域时钟控制 控制/状态寄存器(RCC_CSR) 复位标志寄存器 AHB外设时钟复位寄存器(RCC_AHBRSTR) 复位以太网MAC模块 时钟配置寄存器2(RCC_CFGR2) 时钟选择与分频

线性反馈移位寄存器实现产生伪随机数M序列 -----在CN03平台上,主要体现为Random功能的实现。 什么是线性反馈移位寄存器? 数学解释这里就不作介绍了,这里我们主要理解两个词语就行,一个是线性,它是指量与量之间的一种按比例、成直线的关系。这里面有一点点的数学知识,就是说在ai∈(0,1)的存储单元,ai的个数表示为反馈移位寄存器的级,在某一个时刻,这些寄存器会有一个状态,共有2^n个状态,每个状态对应于域GF(2)上的一个N维向量,用(a1,a2,a3,……an)表示。作为某一个时刻的状态,可以用一个函数f(a1,a2,a3…..an)来表示,从而称为该反馈寄存器的反馈函数,因此线性的意思,就是指如果这个反馈函数是a1,a2,a3….an的线性函数,那么这个反馈移位寄存器,就叫做线性反馈移位寄存器,比如f(a1,a2,a3,…an)=kna1⊕kn-1a2⊕….⊕k2an-1⊕k1an,其中系数ki∈{0,1}i=(1,2,3,…,n)。 另外一个词,就是反馈,这个词在我理解,就是说需要获得下一个状态就需要通过获得一个反馈值来实现。这个反馈的值可以在接下来的两种实现LFSR的方式的解释过程中得到更深刻的理解。 为什么要使用线性反馈移位寄存器? 使用线性反馈移位寄存器的作用: 在很多领域上都有使用到LFSR,譬如说密码学、白噪声,还有我们这里的随机功能实现,之所以把它使用到我们的radio的随机功能里面,除了它可以产生伪随机数序列实现随机播放功能之外,更重要的是我们利用了它的两个特点。其

一,只需要在代码中开辟几个byte的位置,就能够实现随机序列的产生,需要的空间很少。其二,是它的记忆功能,我们在随机的功能里面,选择了下一曲,则上一曲可以通过调整抽头数的序列来从新获得,而不需要开辟空间进行存储。怎样产生伪随机数M序列? M序列的意思就是最大序列,专业点来说就是周期,就是这些不同的伪随机数在什么时候才会回到初始的输入状态,M序列的最大值为2^n-1,因为全0的初始状态不起作用,所以不能以全0的状态作为初始输入。 M序列就是我们在随机功能中获得的那个随机播放的序列。 它有些很好的特性: 1、通过反馈抽头数可以获得与之前输出的值的输入值,这也是我们所说的记 忆功能。 2、这些给定的反馈抽头数永远都是偶数的,而且只包括最高位,不包括最低 位。 3、还有另外一些特征,这里就不一一列出(这些规律的东西,我们只需要理解 我们用到的)。 两种LFSR的产生形式 这里有两种LFSR的实现方式,伽罗瓦(Galois)和斐波那契(Fibonacci)两种形式,也有人称为外部(External)执行方式和内部(Internal)执行方式。所以这两种方式也是有着本质的区别的。 1、伽罗瓦方式(Internal)

STM32使用BSRR和BRR寄存器快速操作 GPI0端口STM32的每个GPIO端口都有两个特别的寄存器,GPIOx_BSR和GPIOx_BRF寄存器,通过这两个寄存器可以直接对对应的GPIOx端口置“或置“ 0。“ GPIOx_BSRR勺高16位中每一位对应端口x的每个位,对高16位中的某位置“狈『端口x的对应位被清“0;“寄存器中的位置“0, “则对它对应的位不起作 用。 GPIOx_BSRR的氐16位中每一位也对应端口x的每个位,对低16位中的某位置“1则“它对应的端口位被置“1;“寄存器中的位置“0,“则对它对应的端口不起作用。 简单地说GPIOx_BSR的高16位称作清除寄存器,而GPIOx_BSR的低氐16 位称作设置寄存器。另一个寄存器GPIOx_BRfl只有低16位有用,与GPIOx_BSR 的高16位具有相同功能。 举个例子说明如何使用这两个寄存器和所体现的优势。例如GPIOE的16个IO都被设置成输出,而每次操作仅需要改变低8位的数据而保持高8位不变,假设新的8 位数据在变量Newdata 中, 这个要求可以通过操作这两个寄存器实现,STM32的固件库中有两个函数GPIO_SetBits和GPIO_ResetBits使用了这两个寄存器操作端口。 上述要求可以这样实现: GPI0_SetBits(GPI0E, Newdata & 0xff); GPI0_ResetBits(GPI0E, (~Newdata & 0xff)); 也可以直接操作这两个寄存器: GPI0E->BSRR = Newdata & 0xff; GPI0E->BRR = ~Newdata & 0xff; 当然还可以一次完成对8位的操作:

stm32 BKP 寄存器操作操作寄存器+库函数 BKP 是BACKUP 的缩写,stm32f103RCTE 的内部配备了10 个16 位宽度 的BKP 寄存器。在主电源切断或系统产生复位时间时,BKP 寄存器仍然可以 在备用电源的支持下保持其内容。BKP 在实际应用中可以存入重要数据,防止 被恶意查看,或用于断电等。本例实现对BKP 寄存器的读写操作,和入侵检 测和处理。主程序中写入寄存器后,依次打印出10 个BKP 寄存器数据,然后 触发GPIOC13 的入侵中断(输入低电平),在中断中打印出入侵事件发生后的 寄存器内容(复位为0 )。直接操作寄存器用到的寄存器描述如下:备份数据 寄存器x(BKP_DRx) (x = 1 10):低16 位[15:0]有效,用来写入或读出备份数据。备份控制寄存器(BKP_CR):低两位有效。TPAL[1]:侵入检测TAMPER 引脚有效电平(TAMPER pin active level)0:侵入检测TAMPER 引脚上的高电平会清除所有数据备份寄存器(如果TPE 位为1) 1:侵入检测TAMPER 引脚 上的低电平会清除所有数据备份寄存器(如果TPE 位为1)TPE[0]:启动侵入检 测TAMPER 引脚(TAMPER pin enable)0:侵入检测TAMPER 引脚作为通用IO 口使用1:开启侵入检测引脚作为侵入检测使用备份控制/状态寄存器 (BKP_CSR): TIF[9]:侵入中断标志(Tamper interrupt flag) 0:无侵入中断1:产生侵入中断当检测到有侵入事件且TPIE 位为1 时,此位由硬件置1。通过向CTI 位 写1 来清除此标志位(同时也清除了中断)。如果TPIE 位被清除,则此位也会被 清除。TEF[8]:侵入事件标志(Tamper event flag) 0:无侵入事件1:检测到侵入事件当检测到侵入事件时此位由硬件置1。通过向CTE 位写1 可清除此标 志位TPIE[2]:允许侵入TAMPER 引脚中断(TAMPER pin interrupt enable)0:禁止侵入检测中断1:允许侵入检测中断(BKP_CR 寄存器的TPE 位也必须被置1)注

设计内容及要求 基于MATLAB产生m序列 要求: 1.通过matlab编程产生m序列的产生原理及其产生方法。 2.对特定长度的m序列,分析其性质,及其用来构造其它序列的方法。 第二章m序列设计方案的选择 2.1 方案一 MATLAB编程非常简单,无需进行变量声明,可以很方便的实现m序列。 2.2 方案二 图2.1 Simulink实现m序列 Simulink是MATLAB最重要的组件之一,它提供了一个动态系统建模,仿真和综合分析的集成环境。在此环境中无需大量书写程序,而只需通过简单直观的鼠标操作,就可构造出复杂的系统。Simulink具有适应性广,结构及流程清晰及仿真精细等优点,基于以上优点,Simulink已被广泛的运用到控制理论和数字信号处理的复杂仿真和设计。

通过比较方案一和方案二,发现方案一的有点具有通用性而方案二利用MATLAB的Simulink直接搭建模块,在移位寄存器较少的情况下利用此方法比较简单,可是当移位寄存器的个数增多时,要搭建那么多的模块就显的很繁琐了,缺乏通用性,因此本次实验选择方案一。 第三章m序列的产生及性质 3.1 m序列的产生原理、结构及产生 m序列是最长线性反馈移位寄存器序列的简称,m序列是由带线性反馈的移位寄存器产生的。 由n级串联的移位寄存器和反馈逻辑线路可组成动态移位寄存器,如果反馈逻辑线路只由模2和构成,则称为线性反馈移位寄存器。 带线性反馈逻辑的移位寄存器设定初始状态后,在时钟触发下,每次移位后各级寄存器会发生变化,其中任何一级寄存器的输出,随着时钟节拍的推移都会产生一个序列,该序列称为移位寄存器序列。 n级线性移位寄存器的如图3.1所示: 图3.1 n级线性移位寄存器 图中C i表示反馈线的两种可能连接方式,C i=1表示连线接通,第n-i 级输出加入反馈中;C i=0表示连线断开,第n-i级输出未参加反馈。 因此,一般形式的线性反馈逻辑表达式为 ------表达式3.1将等式左边的a n移至右边,并将a n=C0a n(C0=1)带入上式,则上式可以 写成 -------表达式3.2

嵌入式系统》课程报告 基于 STM32的 LCD 操作 组长:曾昭智 组员:邓 宁、张小扬、牛洪澄 光电学院 电信 2班、3 班 2014.05.29 姓名 学院 班级 完成日期

目录 1、原理方案(功能框图介绍) (1) 2、电路连线及资源分配. (2) 3、所用主要器件或模块说明. (3) 4、程序流程图. (4) 5、调试心得. (5) 6、源代码 (6)

1.TFT-LCD 原理 1.1 TFT-LCD 简介 TFT-LCD即薄膜晶体管液晶显示器。其英文全称为:Thin Film Transistor-Liquid Crystal Display 。TFT-LCD与无源TN-LCD、STN-LCD 的简单 矩阵不同,它在液晶显示屏的每一个象素上都设置有一个薄膜晶体管(TFT),可有效地克服非选通时的串扰,使显示液晶屏的静态特性与扫描线数无关,因此大大提高了图像质量。TFT-LCD也被叫做真彩液晶显示器。 上一节介绍了OLED模块,这一节,我们给大家介绍ALIENTEK TFTLC模D 块,该模块有如下特点: 1,2.4 '/2.8 '两种大小的屏幕可选。 2,320×240的分辨率。 3,16位真彩显示。 4,自带触摸屏,可以用来作为控制输入。 5,通用的接口,除了ALIENTEK MiniSTM32开发板,该液晶模块还可以使用在优异特、STMSK、Y 红牛等开发板上。 本节,我们以 2.8 寸的ALIENTEKT FTLCD模块为例介绍,该模块采用的是显尚光电的DST2001PHT FTLCD,DST2001PH的控制器为ILI9320 ,采用26 万色的TFTLCD 屏,分辨率为320×240,采用16 位的80并口。 1.2 80 并口 ALIENTEK TFTLCD 模块采用80并口口方与外部链接,采用16位数据线(低了速度太慢,用彩色就没什么效果了)。该模块的80并口有如下一些信号线:CS:TFTLCD 片选信号。 WR:向TFTLCD 写入数据。 RD:从TFTLCD 读取数据。 D[15:0] :16位双向数据线。 RST:硬复位TFTLCD 。 RS:命令/数据标志(0,读写命令;1,读写数据)。 TFTLCD 模块的RST信号线和OLED 模块一样,也是直接接到STM32 的复位脚上,并 不由软件控制,这样可以省下来一个IO 口。另外我们还需要一个背光控制线来控制TFTLCD 的背光。所以,我们总共需要的IO 口数目为21 个。 1.3 ILI9320 模块的控制器为ILI9320 ,该控制器自带显存,其显存总大小为172820 (240*320*18/8 ),即18位模式(26万色)下的显存量。模块的16位数据线与显寸的对应关系为565 方式,如下图所示: 1.4 GRAM显示方向设置

1、不使用库函数的IO口操作 Systick 部分内容属于NVIC控制部分,一共有4个寄存器 SysTick_CTRL, 0xE000E010 -- 控制寄存器默认值:0x0000 0004 SysTick_LOAD, 0xE000E014 -- 重载寄存器默认值:0x0000 0000 SysTick_VAL, 0xE000E018 -- 当前值寄存器默认值:0x0000 0000 SysTick_CALIB, 0xE000E01C -- 校准值寄存器默认值:0x0002328 SysTick_CTRL 寄存器内有4个bit具有意义 第0位:ENABLE,Systick 使能位(0:关闭Systick功能;1:开启Systick功能) 第1位:TICKINT,Systick 中断使能位(0:关闭Systick中断;1:开启Systick中断) 第2位:CLKSOURCE,Systick时钟源选择(0:使用HCLK/8 作为Systick时钟;1:使用HCLK 作为系统时钟) 第16位:COUNTFLAG,Systick计数比较标志 IO口的位操作实现 该部分代码实现对STM32各个IO口的位操作,包括读入和输出。当然在这些函数调用之前,必须先进行IO口时钟的使能和IO口功能定义。此部分仅仅对IO口进行输入输出读取和控制。代码如下: #define BITBAND(addr,bitnum) ((addr & 0xF0000000)+0x2000000+((addr &0xFFFFF)<<5)+(bitnum<<2)) #define MEM_ADDR(addr) *((volatile unsigned long *)(addr)) #define BIT_ADDR(addr,bitnum) MEM_ADDR(BITBAND(addr,bitnum)) //IO口地址映射 #define GPIOA_ODR_Addr (GPIOA_BASE+12) //0x4001080C #define GPIOB_ODR_Addr (GPIOB_BASE+12) //0x40010C0C #define GPIOC_ODR_Addr (GPIOC_BASE+12) //0x4001100C #define GPIOD_ODR_Addr (GPIOD_BASE+12) //0x4001140C #define GPIOE_ODR_Addr (GPIOE_BASE+12) //0x4001180C #define GPIOF_ODR_Addr (GPIOF_BASE+12) //0x40011A0C #define GPIOG_ODR_Addr (GPIOG_BASE+12) //0x40011E0C #define GPIOA_IDR_Addr (GPIOA_BASE+8) //0x40010808 #define GPIOB_IDR_Addr (GPIOB_BASE+8) //0x40010C08 #define GPIOC_IDR_Addr (GPIOC_BASE+8) //0x40011008 #define GPIOD_IDR_Addr (GPIOD_BASE+8) //0x40011408 #define GPIOE_IDR_Addr (GPIOE_BASE+8) //0x40011808 #define GPIOF_IDR_Addr (GPIOF_BASE+8) //0x40011A08 55

第二章作业参考答案 1.3级线性反馈移位寄存器在c3=1时可有4种线性反馈函数,设其初始状态为(a1,a2,a3)=(1,0,1),求各线性反馈函数的输出序列及周期。 解:此时线性反馈函数可表示为f(a1,a2,a3)=a1⊕c2a2⊕c1a3 当c1=0,c2=0时,f(a1,a2,a3)=a1⊕c2a2⊕c1a3=a1, 输出序列为101101…,周期=3 当c1=0,c2=1时,f(a1,a2,a3)=a1⊕c2a2⊕c1a3=a1⊕a2, 输出序列为10111001011100…,周期=7 当c1=1,c2=0时,f(a1,a2,a3)=a1⊕c2a2⊕c1a3=a1⊕a3, 输出序列为10100111010011…,周期=7 当c1=1,c2=1时,f(a1,a2,a3)=a1⊕c2a2⊕c1a3=a1⊕a2⊕a3, 有输出序列为1010…,周期=2 2.设n级线性反馈移位寄存器的特征多项式为p(x),初始状态为(a1,a2, …,a n-1,a n)=(00…01),证明输出序列的周期等于p(x)的阶 证:设p(x)的阶为p,由定理2-3,由r|p,所以r≤p 设A(x)为序列{a i}的生成函数,并设序列{a i}的周期为r,则显然有A(x)p(x)=φ(x) 又A(x)=a1+a2x+…+a r x r-1+x r(a1+a2x+…+a r x r-1)+(x r)2(a1+a2x+…+a r x r-1)+… =a1+a2x+…+a r x r-1/(1-x r)=a1+a2x+…+a r x r-1/(x r-1) 于是A(x)=(a1+a2x+…+a r x r-1)/(x r-1)=φ(x)/p(x) 又(a1,a2, …,a n-1,a n)=(00…01) 所以p(x)(a n x n-1+…+a r x r-1)=φ(x)(x r-1) 即p(x)x n-1(a n+…+a r x r-n)=φ(x)(x r-1) 由于x n-1不能整除x r-1,所以必有x n-1|φ(x),而φ(x)的次数小于n,所以必有φ(x)=x n-1 所以必有p(x)|(x r-1),由p(x)的阶的定义知,阶p≤r 综上所述:p=r# 3.设n=4,f(a1,a2,a3,a4)=a1⊕a4⊕1⊕a2a3,初始状态为(a1,a2,a3,a4)=(1,1,0,1),求此非线性反馈移位寄存器的输出序列及周期。 解:由反馈函数和初始状态得状态输出表为 (a4 a3 a2 a1) 输出(a4 a3 a2 a1) 输出 1 0 1 1 1 1 1 1 1 1 1 1 0 1 1 0 1 1 1 1 1 1 1 0 0 1 0 1 1 1(回到初始状态) 所以此反馈序列输出为:11011…周期为5 4.设密钥流是由m=2s级LFSR产生,其前m+2个比特是(01)s+1,即s+1个01。问第m+3个比特有无可能是1,为什么? 解:不能是1。 可通过状态考察的方法证明以上结论。 首先m级LFSR的状态是一个m维的向量,则前m个比特构成一个状态S0,可表示为(01)s, 第m+1个比特是0,所以S0的下一个状态是S1=(10)s, 第m+2个比特是1,所以S1的下一个状态是S2=(01)s=S0,回到状态S0, 所以下一个状态应是S3=S1=(10)s,也即第m+3个比特应该为0。 5.设密钥流是由n级LFSR产生,其周期为2n-1,i是任一正整数,在密钥流中考虑以下比特对(S i, S i+1), (S i+1, S i+2), …, (S i+2n-3, S i+2n-2), (S i+2n-2, S i+2n-1), 问有多少形如(S j, S j+1)=(1,1)的比特对?证明你的结论。

STM32 GPIO使用 操作步骤: 使能GPIO对应的外设时钟 例如://使能GPIOA、GPIOB、GPIOC对应的外设时钟 RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA | RCC_APB2Periph_GPIOB| RCC_APB2Periph_GPIOC , ENABLE); 声明一个GPIO_InitStructure结构体 例如: GPIO_InitTypeDef GPIO_InitStructure; 选择待设置的GPIO管脚 例如:/* 选择待设置的GPIO 7、8、9管脚位,中间加“|”符号*/ GPIO_InitStructure.GPIO_Pin = GPIO_Pin_7 | GPIO_Pin_8 | GPIO_Pin_9; 4. 设置选中GPIO管脚的速率 例如:/* 设置选中GPIO管脚的速率为最高速率2MHz */ GPIO_InitStructure.GPIO_Speed = GPIO_Speed_2MHz; //最高速率2MHz GPIO5. 设置选中管脚的模式*/ 设置选中GPIO管脚的模式为开漏输出模式/* 例如://开漏输出模式GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_OD; GPIOX

中指定的参数初始化外设6. 根据GPIO_InitStructureGPIOC */ GPIO_InitStructure中指定的参数初始化外设根据例如:/* 1 / 16 GPIO_Init(GPIOC, &GPIO_InitStructure); 7.其他应用 例:将端口GPIOA的 10、15脚置1(高电平) GPIO_SetBits(GPIOA, GPIO_Pin_10 | GPIO_Pin_15); 例:将端口GPIOA的 10、15脚置0(低电平) GPIO_ResetBits(GPIOA, GPIO_Pin_10 | GPIO_Pin_15); GPIO寄存器: 寄存器描述 端口配置低寄存器CRL 端口配置高寄存器CRH 端口输入数据寄存器IDR 端口输出数据寄存器ODR 端口位设置BSRR /复位寄存器 端口位复位寄存器BRR 端口配置锁定寄存器LCKR 事件控制寄存器EVCR

STM32的寄存器操作和C51的操作有很大的不同。 要操作STM32可以通过库函数操作,也可直接操作寄存器。 下面分析一下寄存器的操作,以控制PE4脚输出高低电平为例: 首先找到GPIOE的寄存器基地址,如下图:(STM32F4xx中文参考手册.pdf) 找到GPIOE的基地址为:0x4002 1000 我们要操作PE4脚,首先找到BSRR位操作寄存器,如下图 BSRR寄存器偏移地址为:0x18 由于我我们要操作PE4,即操作BSRR寄存器的第4位。 下面编写代码: 首先定义一个指向uint32_t型的指针,之后将该指针指向BSRR寄存器地址:

0x4002 1018 = 0x4002 1000 + 0x0000 00018 此时要操作BSRR寄存器,直接向*p赋值就可以了,如下图: 该代码即可实现PE4脚的高低电平输出。 假如不加延时,如下图: 系统也可正常运行,但在这两行处打断点调试,会发现无法进入,分析原因是两行代码中间无延时,实际运行时几乎可以忽略该代码的操作,所以编译器在编译时自动优化了,此时我们只需要在声明变量的时候为其指明__IO类型变量(volatile)即可,如下图: 上面的例子从最基本的寄存器分析操作STM32的,下面来分析下官方库函数是如何操作寄存器的。 首先定义GPIO寄存器组,通过结构体将寄存器组封包,如下图:

由于以上寄存器地址是连续的,所以可以分在一个结构体中 然后定义GPIOE寄存器组 这里的GPIOE_BASE为GPIOE寄存器的基地址:0x4002 1000 定义了GPIO_TypeDef类型指针GPIOE,并指向了GPIOE寄存器的基地址。此时我们要操作PE4脚状态只需要操作GPIOE->BSRR就可以了, 其它寄存器的操作参考上面的分析即可实现。

学习STM32,官方提供一个库,但如果刚入手的话,肯定连功能都不太清楚,所以用不太习觉得还是操作寄存器来的直接,所以就整理了STM32的大部分寄存器共大家参考。版权归 基本上都是103的,其中107的RCC,USB,和以太网等一些不太重要的没有,但大部分都有我只是把数据手册中的寄存器整理了一下方便大家看。如果有什么不对的,请通知我,也好联系方式:qq 526083029 小树 PWR电源相关寄存器 PWR_CR(电源控制寄存器) 31302928272625242322212019181716 保留 1514131211109876543210保留DBP PLS[2:0]PVDE CSBF CWUF PDDS LPDS 8位:DBP取消后备区域写保护。复位值为0。定义:0为禁止写入,1为允许写入。注:如果rtc时钟是HSE/128,必须保持为1 7-5位:PVD电源电压检测器的电压阀值。定义:000(2.2v),001(2.3v),010(2.4v),011(2.5v),100(2.6v),101(2.7v),110(2.8v),4位:PVDE电源电压检测器(PVD)使能。定义:0(禁止PVD),1(开启PVD) 3位:CSBF清除待机位(始终输出为0)定义:0(无功效),1(清除SBF待机位(写) 2位:CWUF清除唤醒位(始终输出为0)定义:0(无功效),1(2个系统时钟周期后清除WUF唤醒位(写) 1位:PDDS掉电深睡眠(与LPDS位协同操作)定义:0(当CPU进入深睡眠时进入停机模式,调压器状态由LPDS位控制),1(CPU进入深睡眠时进入待机模0位:LPDS深睡眠下的低功耗(PDDS=0时,与PDDS位协同操作)定义:0(在待机模式下电压调压器开启),1(在待机模式下电压调压器处于低功耗模式 PWR_CSR(电源控制/状态寄存器) 31302928272625242322212019181716 保留 1514131211109876543210保留EWUP保留PVDO SBF WUF 8位:EWUP使能WKUP引脚。定义:0(WKUP为通用IO),1(用于待机唤醒模式,WKUP引脚被强置为输入下拉的配置(WKUP引脚上的上升沿将系统从待机模 注:复位时清除这一位 2位:PVDO-PVD输出(当PVD被PVDE位使能后该位才有效)定义:0(VDD/VDDA高于PLS[2-0]选定的PVD阀值),1(VDD/VDDA低于PLS[2-0]选定的PVD阀值 注:在待机模式下PVD被停止,因此,待机模式后或复位后,直到设置PVDE位之前,该位为0 1位:SBF待机标志位(该位由硬件设置,并只能由POR/PDR(上电/掉电复位)或设置电源控制寄存器(PWR_CR)的CSBUF位清除)定义:0(不在待机 0位:WUF唤醒标志(该位由硬件设置,并只能由POR/PDR(上电/掉电复位)或设置电源控制寄存器(PWR_CR)的CWUF位清除) 定义:0(没有唤醒事件),1(在WKUP引脚上发生唤醒事件或出现RTC脑中事件) 注:当WKUP引脚已经是高电平时,在(通过设置EWUP位)使能WKUP引脚时,会检测到一个额外事件 BKP——DRx(x=1...10)(备份数据寄存器) 1514131211109876543210 15-0位:备份数据由用户来写数据。注:BKP——DRx寄存器不会被系统复位,电源复位,待机唤醒所复位 它可以由备份域复位来复位或(如果入侵检测引脚TAMPER功能被开启时)由浸入引脚事件复位 BKP_RTCCR(RTC时钟校准寄存器) 1514131211109876543210

STM32的每个GPIO端口都有两个特别的寄存器,GPIOx_BSRR和GPIOx_BRR寄存器,通过这两个寄存器可以直接对对应的GPIOx端口置'1'或置'0'。 GPIOx_BSRR的高16位中每一位对应端口x的每个位,对高16位中的某位置'1'则端口x的对应位被清'0';寄存器中的位置'0',则对它对应的位不起作用。 GPIOx_BSRR的低16位中每一位也对应端口x的每个位,对低16位中的某位置'1'则它对应的端口位被置'1';寄存器中的位置'0',则对它对应的端口不起作用。 简单地说GPIOx_BSRR的高16位称作清除寄存器,而GPIOx_BSRR的低16位称作设置寄存器。另一个寄存器GPIOx_BRR只有低16位有效,与GPIOx_BSRR的高16位具有相同功能。 举个例子说明如何使用这两个寄存器和所体现的优势。例如GPIOE的16个IO都被设置成输出,而每次操作仅需要改变低8位的数据而保持高8位不变,假设新的8位数据在变量Newdata 中, 这个要求可以通过操作这两个寄存器实现,STM32的固件库中有两个函数GPIO_SetBits()和GPIO_ResetBits()使用了这两个寄存器操作端口。 上述要求可以这样实现: GPIO_SetBits(GPIOE, Newdata & 0xff); GPIO_ResetBits(GPIOE, (~Newdata & 0xff)); 也可以直接操作这两个寄存器: GPIOE->BSRR = Newdata & 0xff; GPIOE->BRR = ~Newdata & 0xff; 当然还可以一次完成对8位的操作: GPIOE->BSRR = (Newdata & 0xff) | (~Newdata & 0xff)<<16; 从最后这个操作可以看出使用BSRR寄存器,可以实现8个端口位的同时修改操作。 如果不是用BRR和BSRR寄存器,则上述要求就需要这样实现: GPIOE->ODR = GPIOE->ODR & 0xff00 | Newdata; 使用BRR和BSRR寄存器可以方便地快速地实现对端口某些特定位的操作,而不影响其它位的状态。

如何用寄存器的方法操作STM32 这个文章是摘自阿莫论坛,觉得写得很不错,就收藏下来了,整理成文档,希望更多的人能看到 既然我们要操作IO 口,当然就要看IO口相关的知识。打开STM3210x参考手册.pdf ,我的目的只是操作GPIO 所以我只需要将第五章看完就OK了。章节比较多,懒得看,根据一般的经验(楼主,你缺经验了吧?),不说多 就AVR 和PIC 而已。操作IO一般是两个步骤,第一,操作IO控制寄存器,设置IO为输出,第二就是送数据。 那么很明显,只可能是GPIOx_CRL GPIOx_CRH ,GPIOx_ODR 三个寄存器会有想要 仔细阅读这几个寄存器的介绍后知道,GPIOx_CRL 是控制PIN 0-7 的属性的,GPIOx_CRH 控制PIN 8-15,ODR寄存器 当然就是输出数据了,将数据送到这里就行了。 然后,这几个寄存器的地址是多少?首先看stm32f103ve.pdf 这个是官方的datasheet、,看第四章,Mmeory Mapping 为什么看这章?会英文都能猜到吧?,看PORTB 的地址是0x40010C00 - 0x40010FFF ,这个就是基地址了。基地址 加上偏移量就能找到具体的寄存器。 例如我需要操作GPIOB_CRL 的偏移为00H ,(看STM3210x参考手册.pdf)ODR 寄存器的偏移为0CH 那么很自然得出 GPIOB_CRL = 0x40010C00 GPIOB_ODR = 0x40010C0C 怎么验证我的结论正确?先看keil 给的头文件\Keil\ARM\INC\ST\STM32F10x\stm32f10x_map.h #define PERIPH_BASE ((u32)0x40000000) #define APB2PERIPH_BASE (PERIPH_BASE + 0x10000) #define GPIOB_BASE (APB2PERIPH_BASE + 0x0C00) 这样怎么算都能算出0x40010C00 出来吧??ODR 寄存器同理 为了点亮LED ,我需要将PB5 (也就是GPIOB5)设置为输出,并且ODR相应的位写入1 ,看资料得出MODE5 是 bit 20 21 控制的,CNF5 是bit 22,23 MODE5应该设置10(0x2) 选择2MHZ 输出,CNF5 选择00(0x0),通用推挽模式,于是将这个值写入(*volatile unsigned long)0x40010C00 = (2<<20) | (0<<22); // 为简单起见,不管其他位了