异构多核处理器的

编程模型和编译技术

杨灿群 李春江

国防科学技术大学关键词:异构多核 编程编译

引言

目前,芯片集成度的发展继续延续摩尔定律,即每18个月左右晶体管的密度翻一番。照这样的速度,预计到2010年前后,单个芯片能够集成数十亿个晶体管。而且目前来看,这一趋势将持续相当长的时间。因此,如何充分利用芯片上大量的晶体管资源设计高性能的微处理器,是当前产业界和学术界普遍关注的问题。在单芯片上集成多个处理器核构建多核处理器,以便开发更高级别的芯片内部并行性是处理器重要的发展趋势之一。

按照集成方式的不同,多核处理器可以分为同构多核处理器和异构多核处理器。同构多核处理器在一个芯片内集成了多个同构的处理器核,每个处理器核所面向的工作负载完全相同,因此其设计实现相对简单。目前,这一类处理器已经全面推向市场,近期主要以双核为主。

异构多核处理器则在一个芯片内集成了多个异构的处理器核,不同结构的处理器核负责处理工作负载中不同类型的操作。这样,在特定应用领域,异构多核处理器比同构多核处理器能发挥出更高的性能。因此,异构多核处理器是当前产业界和学术界的研究热点。

异构多核处理器对体系结构和软件两个领域都提出了许多新的研究课题。在软件方面的关键问题是支持什么样的编程模型、采用哪些编译优化技术才能充分发挥出处理器的高性能。

可以把异构多核处理器抽象为一个异构并行处理系统,其中存在着多个层次的并行性。面向异构多核处理器的编程模型和编译技术的核心问题是,如何充分开发这个系统中各个层次的并行性。在并行计算几十年的发展过程中,虽然面向并行系统的编程和编译技术已经取得了相当多的成果,但仍是并行计算发展的瓶颈之一。异构多核处理器的异构并行结构,为并行编程和编译优化技术提供了新的研究课题,同时也提出了更大的挑战。

异构多核处理器

异构多核处理器的结构特点

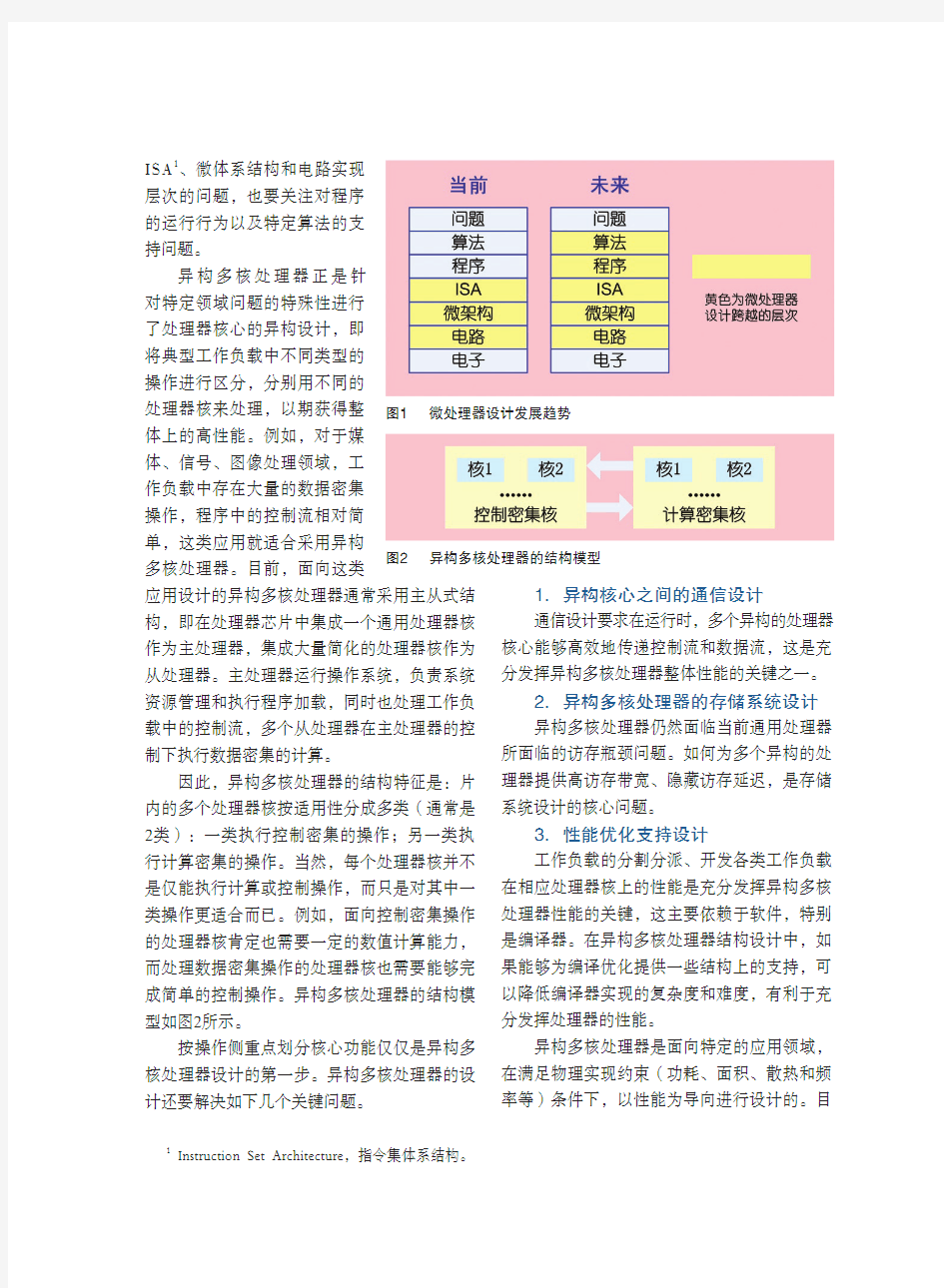

异构多核处理器通常面向特定的应用领域设计,目标是针对特定领域的应用获得高性能。而针对特定应用领域或者面向解决特定问题来设计计算机系统的微处理器,正是微处理器设计的发展方向。未来微处理器在计算机系统设计中所跨越的层次将发生如图1所示的变化[1],即微处理器设计过程中不再仅仅关注

专题报道

ISA1、微体系结构和电路实现

层次的问题,也要关注对程序

的运行行为以及特定算法的支

持问题。

异构多核处理器正是针

对特定领域问题的特殊性进行

了处理器核心的异构设计,即

将典型工作负载中不同类型的

操作进行区分,分别用不同的

处理器核来处理,以期获得整

体上的高性能。例如,对于媒

体、信号、图像处理领域,工

作负载中存在大量的数据密集

操作,程序中的控制流相对简

单,这类应用就适合采用异构

多核处理器。目前,面向这类

应用设计的异构多核处理器通常采用主从式结构,即在处理器芯片中集成一个通用处理器核作为主处理器,集成大量简化的处理器核作为从处理器。主处理器运行操作系统,负责系统资源管理和执行程序加载,同时也处理工作负载中的控制流,多个从处理器在主处理器的控制下执行数据密集的计算。

因此,异构多核处理器的结构特征是:片内的多个处理器核按适用性分成多类(通常是2类):一类执行控制密集的操作;另一类执行计算密集的操作。当然,每个处理器核并不是仅能执行计算或控制操作,而只是对其中一类操作更适合而已。例如,面向控制密集操作的处理器核肯定也需要一定的数值计算能力,而处理数据密集操作的处理器核也需要能够完成简单的控制操作。异构多核处理器的结构模型如图2所示。

按操作侧重点划分核心功能仅仅是异构多核处理器设计的第一步。异构多核处理器的设计还要解决如下几个关键问题。

1.异构核心之间的通信设计

通信设计要求在运行时,多个异构的处理器核心能够高效地传递控制流和数据流,这是充分发挥异构多核处理器整体性能的关键之一。

2.异构多核处理器的存储系统设计

异构多核处理器仍然面临当前通用处理器所面临的访存瓶颈问题。如何为多个异构的处理器提供高访存带宽、隐藏访存延迟,是存储系统设计的核心问题。

3.性能优化支持设计

工作负载的分割分派、开发各类工作负载在相应处理器核上的性能是充分发挥异构多核处理器性能的关键,这主要依赖于软件,特别是编译器。在异构多核处理器结构设计中,如果能够为编译优化提供一些结构上的支持,可以降低编译器实现的复杂度和难度,有利于充分发挥处理器的性能。

异构多核处理器是面向特定的应用领域,在满足物理实现约束(功耗、面积、散热和频率等)条件下,以性能为导向进行设计的。目

1

Instruction Set Architecture,指令集体系结构。

图1 微处理器设计发展趋势

图2 异构多核处理器的结构模型

前,出现了多种异构多核处理器,这方面的软硬件研究处于微处理器体系结构研究的前沿。

典型的异构多核处理器

1.IBM Cell

Cell [2] 高性能处理器由IBM、索尼和东芝三家国际顶尖厂商从2001年起联合研发,2005年初首次公布。Cell最初的研发目标是用于索尼的游戏机PS3,但IBM也宣称Cell是片上超级计算机。第一款Cell芯片性能突出,在4GHz频率下工作时,单精度浮点运算速度可以达到288GFLOPS 2,双精度浮点运算速度也能达到26GFLOPS。

C e l l处理器是典型的异构多核处理器,如图3所示,它由1个64位P o w e r P C处理器核(P P E 3)和8个S I M

D 4 型向量协处理器核(SPE5)构成。片内通信采用总线结构,用高带宽的环状高速总线(EIB 6)将各个处理器

核、存储器接口控制器(MIC 7)、I/O 8 接口控制器(EIB 9)连接起来。

Cell的异构处理器核之间有明确的分工:PPE负责执行操作系统并控制SPE,SPE完成主要的计算任务。SPE内配置了128个128位的寄存器,用256KB的SRAM 10 作为局部存储器。SPE通过消除取/存操作的地址转换、硬件管理的缓存(Cache)、乱序指令发射和分支预测来获得高性能。当然,这就要求在编程和编译过程中尽可能地挖掘向量操作,并且减少分支,以便充分发挥其性能。SPE的流水线调度规则比较简单,这样有利于静态分析其执行代码的性能,也有利于编译器进行高质量的静态指令调度。

虽然C e l l处理器研发的初衷是用于游戏机,但是C e l l处理器的卓越性能也使人们坚信,它在高端计算领域也有出色的表现。IBM 就宣称,Cell是一款片内超级计算机,并研制了采用Cell处理器的刀片服务器。最近有消息称,IBM将利用Cell处理器和AMD公司的皓龙(Opteron)处理器为美国能源部研制世界最快的超级计算机走鹃(Roadrunner),其目标是峰值性能达到千万亿次[3] 量级。

2.Merrimac流处理器

流应用(包括多媒体、信号处理和图像处理)已经成为计算机系统的主要负载。由于这类应用具有数据密集的特点,因此,能够将芯片上大量的计算单元同时利用起来,从而获得高性能。

Merrimac [4,5] 是斯坦福(Stanford)大学的流

2 Giga FLoating-point Operation Per Second,每秒10亿次浮点操作。3

Power Processing Element,Power处理单元。4

Single Instruction Multiple Data,单指令多数据。5

Synergistic Processing Element,附属处理单元。6

Element Interconnect Bus,单元互联总线。7

Memory Interface Controller。8

Input/Output,输入/输出。9

Element Interconnect Bus,单元互联总线。10

Static Random Access Memory,静态随机访问存储器。

图3 Cell处理器结构

专题报道

超级计算机项目,是Imagine[6] 流处理器项目的继承和发展。Merrimac的目标是构建面向流处理的高性能计算机系统。

Merrimac吸收了Imagine流处理器设计的成功经验,并在此基础上重新设计了一款流处理器。Merrimac的流处理器也是典型的异构多核结构,如图4所示。它集成了2个通用处理器核Mips64 20kc(一个用作自校验,2个核在功能上可以看作1个)用于处理标量操作,还集成了16个称为计算簇(Cluster)的处理器。每个计算簇包含4个64位的浮点乘加单元,768个64位寄存器以及8k字的流寄存器文件(SRF11)。芯片中的微控制器以超长指令字指令控制16个计算簇以S I M D方式同时工作。设计预期该流处理器的双精度浮点计算速度可以达到128GFLOPS。

Merrimac项目的目标是,用这款流处理器来研制运算速度可以达到每秒千万亿次量级的流超级计算机。目前,Merrimac项目仍在进行中,其处理器和计算机系统尚未发布。

异构多核处理

器的编程模型

当然,如果编译器

的功能足够强大,采用

任何编程模型编写的程

序就都能够编译成可以

在任何并行系统上高效

运行的可执行程序。但

是,编译器远未达到这

样的水平。因此,将目

标系统的一些特性体现

在编程模型里面,暴露

给程序开发人员,在程

序编写的过程中就充分考虑到目标系统的特性,是目前开发并行软件通常的做法。

异构多核处理器的运行模式取决于多个处理器核的协同方式,这些运行模式也体现到给用户提供的编程模型中。下面分别以IBM的Cell 处理器和Merrimac的流处理器为例,分析异构多核处理器的编程模型。

Cell的编程模型

Cell处理器的运行模式非常灵活,PPE和SPE之间可以通信和协同,SPE之间也可以通信和协同。这一特点在对于编程模型的支持上得到充分体现。Cell处理器支持的编程模型相当丰富,包括远程过程调用(RPC12)模型、设备扩展模型、计算加速模型、流模型、共享存储多处理器模型、非对称线程模型、用户模式线程模型和SPE插件模型。

埃臣伯格(Eichenberger)[7] 等实现了一个OpenMP编译器,用于支持Cell的共享存储编程

模型。使用软件控制的数据缓存(Cache)来图4 Merrimac的流处理器结构

11 Stream Register File

12 Remote Procedure Call

支持Cell的共享存储抽象,当缓存失效时,产生DMA 13 请求传递数据,由于各SPE的局部存储器的容量有限,只有256KB,因此,编译器除使用软件控制的数据缓存外,还使用了代码划分技术来保证OpenMP线程在SPE上的执行。

在流编程模型下,数据以流的模式流经多个SPE,在一个SPE上处理完的数据通过高速EIB总线传递给下一个SPE进行处理。这种模式适合流应用,如信号、图像处理等。

从应用的角度看,每个SPE和PPE可以看作是独立的处理器,有各自独立的存储空间,Cell中的高速DMA传输能有效地在2个SPE的局部存储器之间或者局部存储器与系统存储之间传递消息,因此可以把Cell看作是一个紧耦合的、但节点存储器容量有限的集群(Cluster)系统,消息传递编程模型可以较自然地映射到Cell上去。奥哈拉(M. Ohara)[8] 等实现了针对Cell的MPI microtask编程支持。

Merrimac流处理器的编程模型

和Cell处理器相比,Merrimac的流处理器所支持的编程模型没有那么丰富。其根本原因是,流处理器中的计算簇(Cluster)是非常精简的处理器核,只包含几组功能部件。16个核与一个微控制器组织成SIMD并行多核结构,微

控器用超长指令字(VLIW 14)控制16个核的执行,VLIW中包含了16个核共享的取指段、译码段和控制逻辑。16个核执行相同的指令序列,只是处理的数据不同。每个核之间并不完全独立,各个核可以在程序的控制下进行通信。每个核内

部有多个功能部件,每个功能部件内部都有一条执行流水

线。处理器中有多条流水线同时工作,并且各条流水线的延迟不同。整个流处理器的运行模式单一,由标量处理器核发送流指令来为所有计算簇准备数据、加载驱动计算簇执行的超长指令字代码、启动计算簇执行。

Merrimac流处理器的这种设计面向适用于流应用的流编程模型,目标是面向流计算获得高性能。在流编程模型中,数据按流的方式来组织,数据流经SRF(流寄存器文件)的过程中被多个计算簇并行处理。

为了使用户更好地使用流编程模型,Merrimac设计了专门的流编程语言——Brook。目前提出了BrookC(C语言扩展)和BrookTran (Fortran语言的扩展)的语言规范。用户可利用Brook流编程语言提供的指导命令,在程序中显示指定哪些程序段在哪部分处理器核上执行,编译过程中,对面向不同处理器核的程序段分别编译。

面向异构多核处理器的编译技术

目前,微处理器性能的充分发挥,越来越依赖于编译器,异构多核处理器更是如此。对于异构多核处理器而言,由于不同结构的处理

图5 Cell处理器可执行程序的构建过程

13

Direct Memory Access,直接存储器访问。14

Very Long Instruction Word

专题报道

器核的指令集不同,需要生成在不同处理器核上执行的不同的执行码,因此编译过程更加复杂,同时,为了获得高性能,对编译优化技术的要求也更高。

编译的一般流程

面向异构多核处理器的编译过程,一般要经过如下若干步骤。

1.代码划分

要把用高级语言编写的程序编译成可在异构多核处理器上运行的执行代码,首先要区分哪些代码在哪类处理器上运行。如果这部分工作由编译器自动完成,往往困难较大,并且性能低。解决的办法通常是在源代码中添加指导语句,以便区分哪些源代码所描述的操作在哪类处理器上运行。编译过程中的代码划分工作就是要识别这些指导语句,将在不同目标处理器核上执行的代码分离开,分别进行编译。

2.分别编译

这一步工作就是针对需要在不同类型的处理器核上执行的代码,分别调用面向目标处理器核的编译器,将其编译成执行代码。因此,在这一步可能要调用多个编译器。

3.执行代码的组织

这一步需要解决的问题是,采用什么方式将要在不同处理器核上执行的目标代码组织成一个操作系统环境下的运行实体(可执行程序)。通常的做法是:运行实体在通用的标量处理器上加载执行,而将要在从处理器上执行的目标码作为该执行实体(可执行程序)的数据段中的一部分或者作为该执行实体运行时读取的数据文件。

面向Cell处理器的应用程序编译过程如图5所示[7],该图充分反映了面向异构多核处理器的编译过程的特点。

经过以上3步,就完成了用户代码到执行程序的编译过程。在运行过程中多个处理器核之间的协同常常还需要运行时系统提供支持。

关键编译技术

伴随着计算机系统结构尤其是微处理器系统结构的发展,编译技术也在不断发展,并取得了相当多的成果。编译技术中所涵盖的技术内容非常丰富。异构多核处理器的出现,对编译技术的很多方面都提出了新的研究课题。通过对目前典型的异构多核处理器系统结构及编译过程的分析,我们认为面向异构多核处理器的关键编译技术有以下几个方面。

1.面向SIMD结构的编译

SIMD结构是能充分利用处理器上大量的功能部件进行大规模数据并行计算的典型结构。面向这种结构,通常采用自动向量化编译技术。自动向量化是自动并行化的一种,尽管自动并行化相当困难,但仅仅面向程序中进行数据密集计算的循环来进行自动向量化是可行的。早在向量并行计算机为主流并行计算系统的时代,就已经开始了对自动向量化技术的研究,如今已经有了相当多的积累。采用SIMD结构的异构多核处理器的出现,又进一步推动了自动向量化编译技术研究的发展。

2.通信调度

异构多核处理器芯片内的通信包含多个层次:单个从处理器内多个ALU15之间的数据传递、多个从处理器核之间的数据传递以及整个芯片内多个处理器核之间的数据传递。

为了最大限度地开发异构多核处理器的并行性能,这些通信往往都暴露给编译器,由编译器根据对程序行为的分析来控制这些数据传递。

寄存器是处理器核内ALU之间数据交换的主要实现方式,异构多核处理器可能不采用集中式的寄存器堆。例如,采用共享互联结构的Imagine[9] 处理器,计算簇中每个ALU都有自己

15 Arithmetic and Logic Unit,算术逻辑单元。

局部的寄存器,ALU之间的数据传递通过寄存器之间共享的连线来传递数据,这完全由程序控制。针对这种结构就要求研究相应的寄存器分配技术及指令调度技术。

异构多核处理器中,多个从处理器核之间的通信以及整个芯片内多个处理器核心之间的通信也有多种实现结构,面向特定的通信实现结构在编译时进行优化是异构多核处理器编译优化技术的重要方面。例如,在Cell处理器中,芯片内多个从处理器之间的数据传递采用DMA机制,在各个从处理器的局部存储器之间进行。面向这种结构的通信优化要考虑通信粒度、计算与通信重叠等问题。

3.片上多处理器访存调度

处理器和存储器的速度差距一直是计算机系统的性能瓶颈,异构多核处理器也是如此。进行访存调度来优化存储访问的局部性一直是编译优化研究的重点内容之一。面向通用微处理器的访存调度侧重于开发各个存储层次(特别是缓存)的局部性。由于异构多核处理器面向特定的应用领域进行专门设计,其存储系统结构可以设计得更加灵活多样。

异构多核处理器存储层次设计的趋势是各个存储层次的管理越来越多地暴露给软件(主要是编译器),如软件管理的缓存、软件管理的便签式存储器(Scratch Pad Memory)以及软件可见的存储体分配等等。异构多核处理器的代码必须显式地管理系统存储器和各个协同工作的处理器核的局部存储器之间数据和代码的传递。编译器必须优化这些数据传递,使通信与计算重叠。

4.局部存储器容量成为编译优化要考虑的主要问题之一

在面向协处理器核的编译优化中,原有面向RISC16 体系结构的一般指令级并行优化问题依然存在,但是,其中很多优化都还必须兼顾协处理器核局部存储器容量的限制。例如,指令调度时,为了尽可能地提高每拍流出的指令数,往往通过函数内联、分支转换、循环展开等方法扩大调度区域,从而增加指令的并行度和调度的自由度。但是,这类优化常常也会增大代码的体积。因此,面向协处理器的编译器在进行这类优化时,需要在局部代码大小和总代码大小之间、在关键代码和非关键代码之间进行权衡,并尽可能通过其他优化手段减少总代码的体积。

另一方面,采用Code Overlay17 技术和代码缓冲技术可以允许协处理器的执行代码超过局部存储器的容量。为了利用好这些技术,又要求编译器对采用哪些优化技术进行更精细的权衡。

5.高效运行库的设计和实现处于重要的位置

为了充分发挥协处理器强大的计算能力,并提高异构多核处理器的可编程性,常常需要用内部函数封装对协处理器的控制操作。这样,高效运行库的设计和实现成为开发异构多核处理器性能潜力的关键之一。用户直接利用高效运行库可以大幅度减少开发高性能应用的时间和复杂度。

对面向异构多核处理器的编译技术的一点看法

异构多核处理器是开发芯片内并行的微处理器,这类处理器的出现并不会引起编译技术中重大的技术变革,只是给已有的编译优化技术提出了一些新的约束条件。面向这些新的约束条件,需要对已有的编译优化技术在原有的基础上进行进一步的研究。

编译器是计算机领域中发展比较成熟的系

16 RISC,Reduction Instruction Set Computer,精简指令级计算机。

17 Code Overlay,代码重叠。

专题报道

统软件。面向各种编程模型、编程语言和系统

结构,科研人员已经对编译及优化技术进行了

大量研究实现工作,相当多的技术已经在各种

编译器中有了成熟的实现。目前,编译技术研

究的重点是面向计算机结构特性的优化技术,

而编译优化技术的研究被形容为类似绣花的工

作,就是要通过非常精细的代码优化工作来提

升性能。当然,这种工作是没有止境的。

对于异构多核体系结构,编译系统面临的挑

战仍然围绕着并行这一主题,从核内的指令级和

向量级并行到核之间的线程级和任务级并行,需

要解决的基本问题仍然相同。但是,在高度集成

的过程中,它同时还允许更紧密的协同工作、更

大和更灵活的交互操作。在开发其性能潜力的

过程中,需要多种编译优化技术相互配合。

异构多核体系结构暴露了更多的硬件细节

给软件,应用则希望更抽象的编程层次。底层

硬件与高层软件之间的差异呈剪刀差的发展趋

势。编译系统承担了弥补这个剪刀差的重担。

结语

多核处理器将迅速发展,异构多核处理器

也会大量出现并应用于越来越多的领域。从消

费类电子产品到超级计算机,都可能成为异构

多核处理器大显身手的用武之地。面向异构多

核处理器,如何编程、如何充分发挥其性能是

软件方面必须持续面对的问题。本文针对这些

问题,进行了较为粗浅的分析。我们希望能够

抛砖引玉,引发国内编译技术研究同仁对面向

异构多核处理器的编译技术进行更广泛、深入

的讨论。■

杨灿群

国防科学技术大学计算机学院

支撑软件室主任、副研究员,

主要研究领域为程序设计语言

编译实现与编译优化,曾主持

和参与研制了多款串行、并行

编译器,是GCC开发组成员。

李春江

国防科技大学计算机学院助理

研究员。2004年在国防科技大

学获计算机科学与技术博士学

位。主要研究领域为计算机体

系结构、编译器实现和优化技

术、分布计算。

参考文献

[1] Prof. Dr Marjan Gusev. “Overview of Processor Technology and Trends”, Reports. University Sts Cyril and

Methodius PMF Institute of Informatics

[2] http://www.bsc.es/projects/deepcoumputing/linuxoncell

[3] “Jay Lyman. “Big Blue to Build World’s Fastest Supercomputer” https://www.doczj.com/doc/1912364775.html,/story/52872.

html. TechNewsWorld, September, 2006

[4] William J.Dally, et al. “Merrimac: Supercomputing with Streams”. SC’03, November, 2003, Phoenix, Arizona,

USA

[5] https://www.doczj.com/doc/1912364775.html,/

[6] https://www.doczj.com/doc/1912364775.html,/projects/imagine/

[7] A. E. Eichenberger, et al., “Using Advanced Compiler Technology to Exploit the Performance of the Cell Broadband

Engine Architecture”. IBM Systems Journal, Vol. 45, No. 1, 2006

[8] M. Ohara, et al., “MPI Microtask for Programming the Cell Broadband EngineTM Processor”. IBM Systems

Journal, Vol. 45, No.1, 2006

[9] Peter Mattson, “A Programming System for the Imagine Media Processor”. Stanford University, March 2002

实验一Windows多线程编程 一、实验目的与要求 了解windows多线程编程机制 掌握线程同步的方法 二、实验环境和软件 WindowsXP VC6.0 三、实验内容 创建线程: HANDLECreateThread( LPSECURITY_ATTRIBUTESlpThreadAttributes, SIZE_TdwStackSize, LPTHREAD_START_ROUTINElpStartAddress, LPVOIDlpParameter, DWORDdwCreationFlags, LPDWORDlpThreadId ); 四、实验程序 #include"stdafx.h" #include

while(1) { Sleep(1000); cout<<"ThisisThreadFrunc1"< 异构多核处理器的任务调度算法 蒋建春;汪同庆 【期刊名称】《计算机工程与应用》 【年(卷),期】2009(045)033 【摘要】在研究Min-min、Max-min算法和Sufferage算法基础上,针对异构多核处理器的特点,提出一种任务静态调度算法--自适应分段Sufferage算法(Adaptive Segmented Sufferage,ASS).该算法以最早完成时间和负载均衡为目标进行任务分配,先将任务分配分成两个阶段:在第一个阶段以最少完成时间作为分配原则进行分配,选择单位时间内节省时间最多的任务先分配;在第二个阶段以负载均衡为分配原则进行分配,选择执行时间大的任务先分配.然后选取不同调节参数,对任务进行多次重新分配,以最小的最大完成时间为最后分配结果,实现自适应调节.通过实验验证,该算法在实现最少完成时间的前提下能很好地达到负载均衡.%After studying the Min-min,Max-min and Sufferage algorithms,this paper presents an Adaptive Segmented Sufferage (ASS) algorithm that can be applied to heterogeneous multi-core processors system,and the goal is to assign optimally tasks to different cores to get the minimal Earliest Finish Time(EFT) and optimal load balancing.At first,the algorithm divides the allo-cating process into two phases:The first phase,the tasks whose saving time is maximum have priority to be selected to a core in the minimal execution time tasks set on the principle of the minimal EFT;the second phase,as the principle of load balancing, the tasks,which have the maximum execution time in the (此文档为word格式,下载后您可任意编辑修改!) 多核编程与并行计算实验报告 姓名: 日期:2014年 4月20日 实验一 // exa1.cpp : Defines the entry point for the console application. // #include"stdafx.h" #include 实验二 // exa2.cpp : Defines the entry point for the console application. // #include"stdafx.h" #include 异构多核处理器的 编程模型和编译技术 杨灿群 李春江 国防科学技术大学关键词:异构多核 编程编译 引言 目前,芯片集成度的发展继续延续摩尔定律,即每18个月左右晶体管的密度翻一番。照这样的速度,预计到2010年前后,单个芯片能够集成数十亿个晶体管。而且目前来看,这一趋势将持续相当长的时间。因此,如何充分利用芯片上大量的晶体管资源设计高性能的微处理器,是当前产业界和学术界普遍关注的问题。在单芯片上集成多个处理器核构建多核处理器,以便开发更高级别的芯片内部并行性是处理器重要的发展趋势之一。 按照集成方式的不同,多核处理器可以分为同构多核处理器和异构多核处理器。同构多核处理器在一个芯片内集成了多个同构的处理器核,每个处理器核所面向的工作负载完全相同,因此其设计实现相对简单。目前,这一类处理器已经全面推向市场,近期主要以双核为主。 异构多核处理器则在一个芯片内集成了多个异构的处理器核,不同结构的处理器核负责处理工作负载中不同类型的操作。这样,在特定应用领域,异构多核处理器比同构多核处理器能发挥出更高的性能。因此,异构多核处理器是当前产业界和学术界的研究热点。 异构多核处理器对体系结构和软件两个领域都提出了许多新的研究课题。在软件方面的关键问题是支持什么样的编程模型、采用哪些编译优化技术才能充分发挥出处理器的高性能。 可以把异构多核处理器抽象为一个异构并行处理系统,其中存在着多个层次的并行性。面向异构多核处理器的编程模型和编译技术的核心问题是,如何充分开发这个系统中各个层次的并行性。在并行计算几十年的发展过程中,虽然面向并行系统的编程和编译技术已经取得了相当多的成果,但仍是并行计算发展的瓶颈之一。异构多核处理器的异构并行结构,为并行编程和编译优化技术提供了新的研究课题,同时也提出了更大的挑战。 异构多核处理器 异构多核处理器的结构特点 异构多核处理器通常面向特定的应用领域设计,目标是针对特定领域的应用获得高性能。而针对特定应用领域或者面向解决特定问题来设计计算机系统的微处理器,正是微处理器设计的发展方向。未来微处理器在计算机系统设计中所跨越的层次将发生如图1所示的变化[1],即微处理器设计过程中不再仅仅关注 什么是异构多处理系统,为什么需要异构多处理系统 早期嵌入式处理系统通常由一个微控制器和一系列外设构成。这些系统通常用来完成获取少量数据、处理数据、做出决策、基于决策结果输出信息等工作。在某些情况下会实现简单的人机交互接口如读取键盘并显示结果。处理需求、同时产生需求,以现在的标准来看似乎微不足道。现代嵌入式系统通常需要处理和分析十亿字节级的海量数据,而且常常在确定性和低延时运算上还有一些额外要求。许多应用还要求系统在满足相关行业标准的同时可靠符合可靠性和安全性要求。 目前,似乎还不可能在单一处理器上同时满足处理高带宽数据、执行系统应用程序、响应实时请求并满足行业安全标准。然而,多核异构芯片却可以实现这些功能。这样的设备具有多个处理单元,每一个单元都有能力负责处理一个或多个前述需求,我们称这样的设备为异构处理系统。 1 什么是异构多处理呢? 一个异构多处理系统由不同类型的多个单核心或多核心处理器构成,异构多核处理系统最简单的形式是由一个多核处理器和GPU组成。然而,现代科技让一颗芯片上的异构多处理系统包含以下模块: ①多核应用处理器(MulTIcore ApplicaTIons Processors); ②多核图形处理器(MulTIcore Graphics Processors; ③多核实时处理器(MulTIcore Real-Time Processors); ④平台管理单元(Platform Management Unit); ⑤配置和安全系统(Configuration and Security Unit); ⑥在FPGA可编程逻辑上实现特定多核处理器。 本文所引用的异构多核处理系统包括上述的多个分类。使用FPGA逻辑实现多核处理器的优势是:它可以创建自定义特殊应用处理器,通过并行Pipes和多Pipeline stages来实现二维并行数据处理,使得在一个时钟周期里可以完成大量的计算。 多核处理器可以设计用来执行通用计算或者是专用计算。和通用处理器执行相同功能相比 一、项目背景及必要性 (一)国内外现状和技术发展趋势 大数据是指海量的数据加上复杂的数据类型。从产业的发展角度看,我们对数据的利用经历了传输、传播、处理三个阶段,而今眼目下,对数据的利用正处在处理这个阶段,即如何处理、如何管理、如何应用,如何优化是现阶段的主要工作。 大数据的具体特点主要表现为四个“V”:一是体量浩大(Volume),数据集合的规模已从GB到TB再到PB级,甚至已经开始以EB和ZB来计算。著名咨询公司IDC的研究报告称,未来10年全球大数据将增加50倍,管理数据仓库的服务器的数量将增加10倍。二是类型复杂(Variety),大数据类型包括结构化数据、半结构化数据和非结构化数据。现代互联网应用呈现出非结构化数据大幅增长的特点,到20152年末非结构化数据将达到整个数据量的75%以上。三是生成迅速(Velocity),大数据通常以数据流的形式动态、快速地产生,具有很强的时效性。数据自身的状态与价值也随时空变化而发生演变,数据的涌现特征明显。四是价值巨大但利用密度低(Value),基于传统思维与技术让人们在实际环境中面临信息泛滥而知识匮乏的窘态。 当今社会,新摩尔定律得到验证,大数据以成为各行各业的焦点。数据的来源多样化:以多源异构数据为代表的非结构化数据占世界上信息总量的95%以上,剩下的5%为结构化数据,包括网页、文本、交易数据、邮件、高清视频、3D视频、语音、图片、地质勘测 数据、多源异构数据探测数据等等,这些数亿TB的数据正以超乎人们想象的速度增长,这对数据的存储系统的容量和实时计算速度提出了空前的要求。同时,大到智慧地球,小到智慧城市的数字化建设,使其越来越多的人、设备和传感器通过数字网络连接起来,产生、传送、分享和访问数据的能力也得到彻底变革。这些行业包括:互联网、制造业、医疗行业、媒体行业、零售销售行业、金融业、能源业、航空航天等等。预计2015年,超过40亿人(世界人口的60%)在使用各种智能终端,以全方位的方式与各行各业发生交互融合。其中大约12%拥有智能终端——其渗透率以每年20%以上的速度增长。如今,3000多万联网传感器节点分布在互联网、交通、汽车、工业、公用事业和零售部门,其数量正以每年30%以上的速度增长。预计到2020年,全球数据使用量预计暴增44倍,达到35.2ZB。35.2ZB也就是说全球大概需要376亿个1TB硬盘来存储数据。 人们对数据日益广泛的需求导致存储系统的规模变得越来越庞大,管理越来越复杂,数据的爆炸性增长和管理能力的相对不足之间的矛盾日益尖锐。同时,数据的高速增长也对存储系统的可靠性和扩展性提出了挑战,海量数据的共享、分析、搜索也显得越来越重要,充分挖掘海量数据中的有效价值。这就要求我们得实现一种有别于传统系统而全新的存储管理平台,该平台必须具备高扩展性、高可靠性、高时效性,同时也需要具备高经济性,只有这样才能更好的为国民经济和生活服务。 国外的大数据发展现状,以GOOGLE/FACEBOOK为代表的 计算机的发展按照硬件工艺可以分为 第一代(1946~1958):电子管数字计算机。 第二代(1958~1964):晶体管数字计算机。 第三代(1964~1971):集成电路数字计算机。 第四代(1971年以后):大规模集成电路数字计算机。 现代计算机发展历程可以分为两个明显的发展时代: 串行计算时代 并行计算时代。 并行计算机是由一组处理单元组成的,这组处理单元通过相互之间的通信与协作,以更快的速度共同完成一项大规模的计算任务。 并行计算机个最主要的组成部分: 计算节点 节点间的通信与协作机制 Flynn根据指令流和数据流的不同组织方式,把计算机系统的结构分为以下四类: 单指令流单数据流(SISD) 单指令流多数据流(SIMD) 多指令流单数据流(MISD) 多指令流多数据流(MIMD) 指令流(instruction stream) 指机器执行的指令序列 数据流(data stream) 指指令流调用的数据序列,包括输入数据和中间结果。 SISD 计算机是传统的顺序执行的计算机 在同一时刻只能执行一条指令(即只有一个控制流)、处理一个数据(即只有一个数据流)。 缺点: 单个处理器的处理能力有限 没有并行计算能力 在MIMD计算机中没有统一的控制部件。 在SIMD机中,各处理单元执行的是同一个程序, 而在MIMD机上,各处理器可以独立执行不同的程序。 MIMD结构比SIMD结构更加灵活。 SIMD计算机用于对不同数据的相同运算(向量和矩阵运算) 而MIMD计算机可以适应更多的并行算法 从系统结构的角度来分类,一般有以下几种: 1)对称多处理器(SMP) 2)分布式共享存储多处理机(DSM) 3)大规模并行处理机(MPP) 4)并行向量处理机(PVP) 5)集群计算机。 多核编程与并行计算实验报告 姓名: 日期:2014年 4月20日 实验一 // exa1.cpp : Defines the entry point for the console application. // #include"stdafx.h" #include 实验二 // exa2.cpp : Defines the entry point for the console application. // #include"stdafx.h" #include Traditional Chinese Medicine 中医学, 2018, 7(5), 282-285 Published Online September 2018 in Hans. https://www.doczj.com/doc/1912364775.html,/journal/tcm https://https://www.doczj.com/doc/1912364775.html,/10.12677/tcm.2018.75047 On the Significance of the Method of Multi-Source Heterogeneous Data Fusion in TCM Hanqing Zhao, Zhiguo Wang* Institute of Basic Research in Clinical Medicine, China Academy of Chinese Medical Sciences, Beijing Received: Aug. 18th, 2018; accepted: Aug. 26th, 2018; published: Sep. 3rd, 2018 Abstract Multi-source isomerism is one of the basic features of large data. It is a hot issue in recent years to study traditional Chinese medicine diagnosis and treatment methods based on data. Building a generalization model is one of the methods to solve multisource heterogeneous data fusion and shares and extends the scope of traditional Chinese medicine data. However, the complexity of the large data of traditional Chinese medicine is high. Many problems, such as rich semantics, uneven distribution and poor objectivity, have greatly restricted the research and application of big data in Chinese medicine. In this paper, the importance of multi-source heterogeneous data fusion me-thod under the background of Internet+ large data is discussed, and the importance of mul-ti-source heterogeneous data fusion method based on the combination of disease and syndrome is discussed. It is the original cause of the important component of the large data of traditional Chi-nese medicine in the future, and the further study of the multi-source isomerism of traditional Chinese medicine. The method of large data fusion provides a theoretical reference. Keywords TCM Informatization, Diagnosis and Treatment Mode, Combination of Disease and Syndrome, Big Data, Multi-Source Heterogeneous Fusion 论中医药多源异构大数据融合方法研究的意义 赵汉青,王志国* 中国中医科学院中医临床基础医学研究所,北京 收稿日期:2018年8月18日;录用日期:2018年8月26日;发布日期:2018年9月3日 *通讯作者。 多核处理器的发展趋势 摘要:多核处理器以其高性能、低功耗优势正逐步取代传统的单处理器成为市场的主流。介绍了 Hydra、Cell、RAW 这 3 种典型的多核处理器结构,重点讨论了核心结构选择、存储结构设计、低功耗等 4个影响当前多核处理器发展的关键技术,最后得出多核处理器的未来将呈现众核、低功耗和异构结构 3 种发展趋势。 Abstract:Multi-core processor has replaced single processor as the mainstream in the market for its high performance and low power. Three typical structures of multi-core processor: Hydra, Cell, RAW is introduced, and then four key techniques is presented, such as core architecture, memory architecture design, low power and finally thedevelopmenttrends of multi-coreprocessor isdiscussed, whichare manycore, low power and heterogeneous. 多核处理器也称为片上多处理器 (chip multi-processor,CMP),或单芯片多处理器。自 1996 年美国斯坦福大学首次提出片上多处理器(CMP)思想和首个多核结构原型,到 2001 年IBM 推出第一个商用多核处理器 POWER4,再到 2005 年 Intel和AMD多核处理器的大规模应用,最后到现在多核成为市场主流,多核处理器经历了十几年的发展。在这个过程中,多核处理器的应用范围已覆盖了多媒体计算、嵌入式设备、个人计算机、商用服务器和高性能计算机等众多领域,多核技术及其相关研究也迅速发展,比如多核结构设计方法、片上互连技术、可重构技术、下一代众核技术等。然而,多核处理器的技术并未成熟,多核的潜力尚未完全挖掘,仍然存在许多待研究的问题。 多核处理器将多个完全功能的核心集成在同一个芯片内,整个芯片作为一个统一的结构对外提供服务,输出性能。多核处理器首先通过集成多个单线程处理核心或者集成多个同时多线程处理核心,使得整个处理器可同时执行的线程数或任务数是单处理器的数倍,这极大地提升了处理器的并行性能。其次,多个核集成在片内,极大地缩短了核间的互连线,核间通信延迟变低,提高了通信效率,数据传输带宽也得到提高。再者,多核结构有效共享资源,片上资源的利用率得到了提高,功耗也随着器件的减少得到了降低。最后,多核结构简单,易于优化设计,扩展性强。这些优势最终推动了多核的发展并逐渐取代单处理器成为主流。 在整体结构设计上多核处理器与传统的单处理器相比,多核内部结构没有固定的组织形式,可以有很多种实现方式。各个研究机构和厂商根据自己的应用目标设计出结构完全不同的多核结构。虽然如此,但在已有的多核处理器中仍存在几种比较典型的结构,它们分别代表了多核处理器结构中的某一类特点,而 Hydra、Cell 和 RAW 处理器就是 3 种典型的结构。 Hydra处理器是 1996 年美国斯坦福大学研制得一个集成了 4 个核心的处理器,这在当时是一种新型的处理器结构。Hydra在一个芯片上集成了 4 个核心,核心间通过总线结构共享片上二级缓存、存储器端口和 I/O 访问端口。4 个核心采用了通用的百万指令级(MIPS)处理器,每个独立的处理核心有私有的一级缓存,其中指令缓存和数据缓存相互分离。 4 个核心共享的二级缓存,采用 DRAM 存储。核心之间、核心到二级缓存、主存与片内以及I/O 设备与片内的通信都是由总线结构来实现的。Hydra 被认为是一种典型的多核结构,不仅在于它是第一个多核处理器设计原型,还因为它采用了共享二级缓存的同构对称设计和高速总线的核间通信方式。 2001 年 3 月,IBM 与 Sony、Toshiba 合作,着手开发一种全新的微处理器结构——Cell 处理器,旨在以高效率、低功耗来处理下一代宽带多媒体与图形应用。Cell 处理器主要包含 9 个核心、一个存储器控制器和一个 IO 控制器,片上的部件互联总线将它们连接在一起。核心间通信和访问外部端口均是通过内部总线进行,而且为了便于核间通信,整 环/球/I T | 计算机教育 2007.7 | 39 ★英特尔多核课程园地★ 《多核程序设计》概述 浙江大学计算机学院 陈天洲 英特尔中国公司大学合作部 曹 捷 王靖淇/文 半导体技术的进步使单芯片多处理器成为现实并推动着多核计算技术的不断进步。浙江大学从2006年开设单独的多核课程,并联合国内五所重点高校设计编写了《多核程序设计》作为该课程的教材,对多核计算技术进行了全面深入的讲解,以期由此完善学生的知识结构。 1 多核计算技术的概述 随着新材料的应用和新技术的发展,VLSI 技术取得长足进步,在单个芯片上集成多个处理器核心构成多核处理器已经成为处理器技术的主流。按计算内核的对等与否,CMP 可分为同构多核和异构多核。计算内核相同,地位对等的称为同构多核。然而,一般认为处理器通用核的数目在超过16个后,再增加通用处理核的数目就难以带来更大的性能提升。于是出现了一些为特别任务专门定制的专用处理核,包括面向科学计算等的“领域专用核”、图形图像处理和数字信号处理(DSP)等“行业专用核”。这些专用核的体系结构利用特定应用的特征进行定制,从而达到定制应用的高性能和高效率。 从2005年出现的英特尔与AMD 的双核处理器、2006年推出的4核处理器到2007年2月英特尔公司展示的80核处理器,处理器中集成核的数目呈现迅速增多的趋势。除此之外,具有更多核和不同功能核的处理器也在研发,例如整合了1025个简单处理器的芯片Kilocore ,包括1024个8位处理器和1个Power PC 核。 伴随着多核处理器的发展尤其是处理器核数目的增加与处理器核功能的变化,在体系结构、软件、 功耗和安全性设计等方面,巨大的挑战也随之而来。处理器的发展使得原有面向单核或者多处理器的软件架构不适于在单芯片多处理器的硬件结构上充分利用多计算核心的能力,需要相应的软件层面的共同发展。为此,软件结构的变化尤其是针对多核硬件体系结构的程序设计成为有效发挥多核计算能力的重要方面。 为了适应技术的发展,为社会培养合格的计算机人才,在大学计算机教学中开设相应的多核计算课程势在必行。计算机方向课程的开设尤其是教材的设计,不仅要注意到满足完善学生知识结构,适应计算机技术迅速发展的情况,同时也需注意到社会对于多核计算技术方面人才的需求,通过合理的设计,满足知识更新与就业两方面的要求。 2 多核课程设计 多核计算技术的发展使得计算机教学发生了变化,这种变化主要来自于多核计算技术所带来的新的知识点。这些新的知识点主要包括:多核SOC 芯片技术;多核芯片与传统单核微处理器、SMP 的区别;多核下的各种硬件设计技术(Cache 与存储一致性、网络互连、IO 管理);并行体系与多核体系结构;典型多核芯片介绍;嵌入式多核芯片技术;多核平台结构与芯片组支持技术(包括固件技术);多核操作系统;多核系统软件对并行编程的支持;多线程编程对多核的支持;多核多线程编程技术(主要是关于Windows 与Linux 操作系统);OpenMP 对多核的支持;多核平台上的编译工具与编译优化技术;多核API 优化函数库;多核多线程程序的性能评测工具与方法。 选择题:20% 1.下列不是多核处理器的是B A.INTEL酷睿2 E4500 B.AMD闪龙3000+ C.cell处理器 2.若对于一个给定的应用,用串行算法执行的时间为24秒,用并行算法执行的时间为32秒,则加速比为:A A.0.75 B.1.33 C.1 3.OpenMP是哪种并行编程环境的代表? C A.消息传递 B.数据并行 C.共享存储 4.针对“降低处理器二分之一的频率,会增加二分之一的功率消耗”的说法,下面的选项中哪个是正确的:B A、这个说法是正确的 B、这个说法是错误的 C、对于台式机和服务器,这个说法是正确的,但对于笔记本电脑,这个说法是错误的 5.下面是线程创建函数,其中线程函数定义参数是: A HANDLE CreateThread( LPSECURITY_ATTRIBUTES lpThreadAttributes, SIZE_T dwStackSize, LPTHREAD_START_ROUTINE lpStartAddress, LPVOID IpParameter, DWORD dwCreationFlags, LPDWORD IpThreadId, ); A.lpParamenter B.lpStartSddress C.lpThreadAttributes 填空题:20% 1并行计算机的两个最主要的组成部分是计算节点和节点间的通信与协作机制 2.按计算内核的对等与否,CMP可分为同构多核和异构多核 3.目前比较主流的片上高效通信机制有两种,一种是基于总线共享的cache结构,一种是基于片上的互联结构. 4.进程具有两个明显的特征,一个是资源特征,另一个是执行特征. 5.线程有4个基本状态:就绪,运行,阻塞,终止 判断题10% 1.根据Amdahl定理,程序的加速比决定于串行部分的性能. . T 2.K-路组关联映射策略很容易产生cache颠簸. F 3.在忙等待条件下发生的饥饿,称为"死锁" F 4.在任何一个线程中调用exit将会结束整个进程. . T 5.墙上时间包括:计算CPU时间,通信CPU时间,同步开销时间和进程空闲时间. T 简答题:30% 1.简述什么是cache映射策略及当前的三种cache映射策略. Cache映射策略指的是内存块和cache线之间如何建立相互映射的关系. 异构多核SoC可编程图形系统硬件设计 异构多核SoC可编程图形系统硬件设计 摘要:采用开源LEON3(basic version)处理器,运行Linux操作系统,并驱动西安邮电大学自主设计研发的基于传统GPU架构的可编程图形处理器,实现了包含可编程图形系统的SoC平台。将系统集成到Dini Group最新的DNV6_F2PCIE开发板上,采取OpenGL 编程,通过鼠标、键盘、显示器运行2D、3D程序,进行图形的绘制,从而比较充分地验证了图形系统硬件设计。关键词:图形处理器;LEON3处理器;异构多核;Linux操作系 统为打破国外垄断,研发拥有自主知识产权的图形处理器GPU(Graphics Processing Unit)对国民经济以及增强国防力量具有极其重要的意义。西安邮电大学GPU项目组2009年研发了GPU及其配套软件OpenGL。为了验证设计的GPU,并为GPU应用开发建立平台,本文 研发了一个异构多核片上系统SoC(System on Chip)平台。本文在分析了嵌入式开源LEON3处理器[1]、Linux操作系统和西安邮电大学自主研发的可编程图形处理器的基础上,提出异构多核SoC图形系统[2]的设计,最后在DNV6_F2PCIE FPGA开发板进行系统验证。1系 统论证1.1研究路线首先构建一个C++的GPU算法仿真平台,并在其上进行图像渲染算法的研究;其次设计搭建System Verilog[3]建立验证平台,并开始Verilog语言设计硬件和OpenGL相关软件的开发,为了加快硬件设计速度,采用了第三方IP;由于此系统电路规模较大,选择Xilinx公司的XC6VLX550T[4]进行原型开发,并运行大量裸机OpenGL应用程序;最后加上嵌入式LEON3处理器、Linux操作系统,通过软件驱动和硬件接口完成CPU与GPU 的数据交互,实现了一个完整的移动异构多核SoC图形处理系统,通过外部可编程的方式在FPGA上验证整个SoC系统,进而验证硬件设计的正确性。1.2关键技术与可行性分析本系统采取软硬件协同设计技术、IP设计和复用技术、超深亚微米设计技术。涉及的关键技术 包括系统描述、高层次的算法分析与设计、软硬件的划分、语言和编译器设计、微处理器设计、Linux操作系统在LEON3处理器上的运行、驱动软件和硬件接口设计、图形处理器的软硬件协同设计、异构系统的协同仿真验证以及图形界面的生成。针对上述涉及的关键技术提出了理论分 析与仿真、验证和原型测试相结合的研究方法,制订了从系统的算法级到电路的RTL级,再到 原型系统实现,逐级细化、逐级验证的技术路线。采用Top-to-Down方法[5]设计SoC 芯片,充分考虑了异构多核SoC可编程图形处理器设计过程中所面临的挑战,保证了芯片功能和性能技术指标达到设计要求,有利于缩短开发周期,降低开发成本及产品的单片价格,符合SoC研究设计的客观规律。2系统的硬件设计系统的硬件设计主要包括作为系统主机的嵌入式开源LEON3处理器设计和作为从机的可编程图形处理器设计。系统的整体硬件结构。系统主要数据流向:(1)2D程序:上位机将镜像文件通过JTAG传到CPU-DDR中,CPU从中取出相应2D数据进行运算,将运算结果通过AHB/APB Bridge传到VGA,再将VGA 的数据发送到GPU中的显控,最终传到显示器上显示。(2)3D程序:CPU从CPU-DDR 中取出相应的3D命令数据环,将数据环通过AHB Bridge传到GPU;GPU经过各级渲染,将渲染结果存储到GPU-DDR中;显控通过存储管理器从中取出数据,传到显示器上显示。2.1嵌入式LEON3处理器的设计LEON3(basic version)作为整个系统的主机,是一款由欧洲航天总局旗下的Gaisler Research公司开发研制的32bit、符合SPARC V8[6]架构的、可配置、可综合适用于SoC设计中的开源处理器IP核[7],遵循GNU LGPL协议。LEON3内部包含7级整数流水线,具有可配置的TLB的内存管理MMU(Memory Management Unit)单元,支持硬件乘/除法器以及分立的指令与数据缓存,并将其设计为4核。它的源代码由可综合的VHDL代码构成,同时LEON系列处理器的性能也比较理想,可以达到大约0.85MIPS/MHz。更大的好处是LEON处理器是一个公开源代码,遵循GNU。通过高速的AMBA AHB[8]总线链接内存控制器及高速外部接口,低速的AMBA APB总线实现片上外设的接口,如定时器、串口、VGA等。 《多核程序设计》概述 陈天洲1 曹捷 王靖淇 (浙江大学计算机学院, 杭州 310027) 摘 要: 随着半导体技术的进步,多核芯片已经成为处理器技术的主流。浙江大学根据多核计算技术的发展趋势,以经典体系理论为基础,以培养动手实践能力为目标,开设了多核课程,并以此进行了教材设计,联合清华大学等高校编写了适合于《多核程序设计》,作为多核计算课程教学设计的一种探索。 关键词: 多核计算;课程设计;教材设计;实践 半导体技术的进步使单芯片多处理器成为现实并推动着多核计算技术的不断进步。浙江大学从2006年开设单独的多核课程,并联合国内五所重点高校设计编写了《多核程序设计》作为该课程的教材,对多核计算技术进行了全面深入的讲解,以期由此完善学生的知识结构。 1 多核计算技术的概述 随着新材料的应用和新技术的发展,VLSI技术取得长足进步,在单个芯片上集成多个处理器核心构成多核处理器[1][2][3]已经成为处理器技术的主流。按计算内核的对等与否,CMP可分为同构多核和异构多核。计算内核相同,地位对等的称为同构多核。然而,一般认为处理器通用核的数目在超过16个后,再增加通用处理核的数目就难以带来更大的性能提升。于是出现了一些为特别任务专门定制的专用处理核,包括面向科学计算等的“领域专用核”、图形图像处理和数字信号处理(DSP)等“行业专用核”[5, 6]。这些专用核的体系结构利用特定应用的特征进行定制,从而达到定制应用的高性能和高效率。 从2005年出现的英特尔与AMD的双核处理器[4]、2006年推出的4核处理器到2007年2月英特尔公司展示的80核处理器,处理器中集成核的数目呈现迅速增多的趋势。除此之外,具有更多核和不同功能核的处理器也在研发,例如整合了1025个简单处理器的芯片Kilocore [7],包括1024个8位处理器和1个Power PC核。 伴随着多核处理器的发展尤其是处理器核数目的增加与处理器核功能的变化,在体系结构、软件、功耗和安全性设计等方面,巨大的挑战也随之而来。处理器的发展使得原有面向单核或者多处理器的软件架构不适于在单芯片多处理器的硬件结构上充分利用多计算核心的能力,需要相应的软件层面的共同发展。为此,软件结构的变化尤其是针对多核硬件体系结构的程序设计成为有效发挥多核计算能力的重要方面。 为了适应技术的发展,为社会培养合格的计算机人才,在大学计算机教学中开设相应的多核计算课程势在必行。计算机方向课程的开设尤其是教材的设计,不仅要注意到满足完善学生知识结构,适应计算机技术迅速发展的情况,同时也需要到社会对于多核计算技术方面人才的需求,通过合理的设计,满足知识更新与就业两方面的要求。 2 多核课程设计 1收稿日期: 2007-05-16 作者简介: 陈天洲(1970-),男,浙江,博士,教授,主要研究方向:计算机系统结构、嵌入式系统。 曹捷,男,英特尔中国大学合作部 王靖淇,女,英特尔中国大学合作部 多核编程并不是最近才兴起的新鲜事物。早在intel发布双核cpu之前,多核编程已经在业内存在了,只不过那时候是多处理器编程而已。为了实现多核编程,人们开发实现了几种多核编程的标准。open-mp就是其中的一种。对于open-mp还不太熟悉的朋友,可以参照维基百科的相关解释。 open-mp的格式非常简单,原理也不难。它的基本原理就是创建多个线程,操作系统把这几个线程分到几个核上面同时执行,从而可以达到快速执行代码的目的。比如说,我们可以编写一个简单的例子。 在编写open-mp程序之前,朋友们应该注意下面三点, (1) 使用vs2005或者以上的版本编写open-mp程序; (2) 编写程序的时候,选择【Property Pages】->【Configuration Properties】->【c/c++】->【language】->【OpenMp Support】,打开开关; (3) 添加#include 《多核架构及编程技术》设计报告 基于OpenMP的二维方阵相乘及 基于IPP的函数DFT及反变换 学院:电子信息学院 专业:通信工程 学号: 2011301200237 姓名:叶子童 指导老师:谢银波 时间: 2013年6月 基于OpenMP的二维方阵相乘 姓名:叶子童专业:通信工程学号:2011301200237 指导教师:谢银波 [设计原理] 声明3个800阶的矩阵,用srand函数对A,B矩阵随机赋值,在主程序中用3个for循环来进行计算,用OpenMP实现循环并行化,用clock()函数统计运算时间并输出时间及C矩阵。 [主要功能] 计算2个随机生成的800阶二维矩阵相乘的结果,统计运算时间并输出结果矩阵。 [设计的主要内容] 实验代码为: #include"stdafx.h" #include int main() { int i, j, t, k; double duration; clock_t start, finish; for (int i=0;i<800;i++) for (int j=0;j<800;j++) a[i][j]=rand()%100; //随机产生-100的随机整数 for (int i=0;i<800;i++) for (int j=0;j<800;j++) b[i][j]=rand()%100; start=clock(); #pragma omp parallel shared(a,b,c) private(i,j,k) #pragma omp for schedule(dynamic) //循环动态分割成大小为chunk的块,动态分割给线程for(i=0;i<800;i++) { for(j=0;j<800;j++) { c[i][j]=0; for(k=0;k<800;k++) { c[i][j]+=a[i][k]*b[k][j]; } } } printf( "Time to do the calculate is "); finish = clock(); duration = (double)(finish - start) / CLOCKS_PER_SEC; printf( "%2.6f seconds\n", duration ); Sleep(2000); for(i = 0;i < 800;i++) { for(j = 0;j < 800;j++) { printf("%d ",c[i][j]); } printf("\n"); } return 0; } 输出的运算时间为3.483s。异构多核处理器的任务调度算法

多核编程与并行计算实验报告 (1)

012032异构多核处理器的编程模型和编译技术

什么是异构多处理系统,为什么需要异构多处理系统

【大数据】多源异构通用大数据处理服务平台

多核程序设计

多核编程与并行计算实验报告 (1)

论中医药多源异构大数据融合方法研究的意义

多核处理器的发展趋势

多核程序设计概述

多核程序设计考题(样本)

异构多核SoC可编程图形系统硬件设计

《多核程序设计》概述

02多线程的那点儿事(之多核编程)

多核架构及编程技术