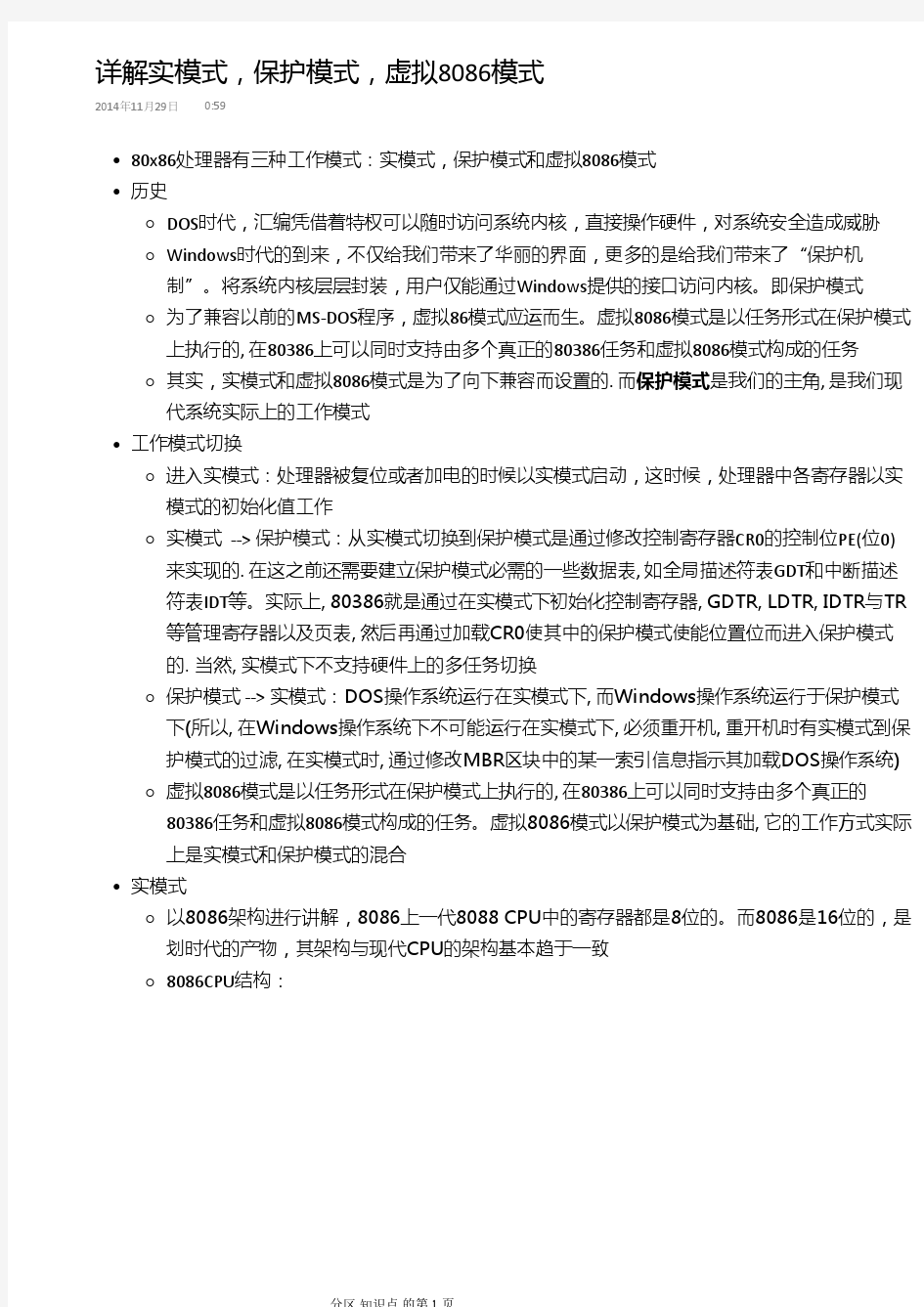

1.什么是“程序可见”的寄存器? 程序可见寄存器是指在用户程序中用到的寄存器,它们由指令来指定。 2. 80x86微处理器的基本结构寄存器组包括那些寄存器?各有何用途? 基本结构寄存器组按用途分为通用寄存器、专用寄存器和段寄存器3类。 通用寄存器存放操作数或用作地址指针;专用寄存器有EIP和EFLAGS,分别存放将要执行的下一条指令的偏移地址和条件码标志、控制标志和系统标志;段寄存器存放段基址或段选择子。 3.80x86微处理器标志寄存器中各标志位有什么意义? 常用的7位: CF进位标志: 在进行算术运算时,如最高位(对字操作是第15位,对字节操作是第7位)产生进位或借位时,则CF置1;否则置0。在移位类指令中,CF用来存放移出的代码(0或1)。 PF奇偶标志: 为机器中传送信息时可能产生的代码出错情况提供检验条件。 当操作结果的最低位字节中1的个数为偶数时置1,否则置0。 AF辅助进位标志: 在进行算术运算时,如低字节中低4位(第3位向第4位)产生进位或借位时,则AF置1;否则AF置0。 ZF零标志:如指令执行结果各位全为0时,则ZF置1;否则ZF置0。 SF符号标志:其值等于运算结果的最高位。 如果把指令执行结果看作带符号数,就是结果为负,SF置1;结果为正,SF置0。 OF溢出标志: 将参加算术运算的数看作带符号数,如运算结果超出补码表示数的范围N,即溢出时,则OF置1;否则OF置0。 DF方向标志: 用于串处理指令中控制处理信息的方向。 当DF位为1时,每次操作后使变址寄存器SI和DI减小;当DF位为0时,则使SI和DI增大,使串处理从低地址向高地址方向处理。 4.画出示意图,简述实模式下存储器寻址的过程。 20位物理地址如下计算(CPU中自动完成):10H×段基址+偏移地址=物理地址 5. 画出示意图,简述保护模式下(无分页机制)存储器寻址的过程。 采用对用户程序透明的机制由选择子从描述子表中选择相应的描述子,得到欲访问段的段基址、段限等有关信息,再根据偏移地址访问目标存储单元。

什么是实模式、保护模式和虚拟8086方式 1:实模式:寻址采用和8086相同的16位段和偏移量,最大寻址空间1MB,最大分段64KB。可以使用32位指令。32位的x86 CPU用做高速的8086。 2:保护模式:寻址采用32位段和偏移量,最大寻址空间4GB,最大分段4GB (Pentium Pre及以后为64GB)。在保护模式下CPU可以进入虚拟8086方式,这是在保护模式下的实模式程序运行环境。 第一:实模式下程序的运行回顾. 程序运行的实质是什么?其实很简单,就是指令的执行,显然CPU 是指令得以执行的硬件保障,那么CPU如何知道指令在什么地方呢? 对了,80x86系列是使用CS寄存器配合IP寄存器来通知CPU指令在内存 中的位置. 程序指令在执行过程中一般还需要有各种数据,80x86系列有DS、 ES、FS、GS、SS等用于指示不同用途的数据段在内存中的位置。 程序可能需要调用系统的服务子程序,80x86系列使用中断机制 来实现系统服务。 总的来说,这些就是实模式下一个程序运行所需的主要内容 (其它如跳转、返回、端口操作等相对来说比较次要。) 第二:保护模式---从程序运行说起 无论实模式还是保护模式,根本的问题还是程序如何在其中运行。 因此我们在学习保护模式时应该时刻围绕这个问题来思考。 和实模式下一样,保护模式下程序运行的实质仍是“CPU执行指令, 操作相关数据”,因此实模式下的各种代码段、数据段、堆栈段、中 断服务程序仍然存在,且功能、作用不变。 那么保护模式下最大的变化是什么呢?答案可能因人而异,我的 答案是“地址转换方式”变化最大。 第三:地址转换方式比较 先看一下实模式下的地址转换方式,假设我们在ES中存入0x1000, DI中存入0xFFFF,那么ES:DI=0x1000*0x10+0xFFFF=0x1FFFF,这就是众 所周知的“左移4位加偏移”。 那么如果在保护模式下呢?假设上面的数据不变ES=0x1000, DI=0xFFFF,现在ES:DI等于什么呢? 公式如下:(注:0x1000=1000000000000b= 10 0000 0000 0 00) ES:DI=全局描述符表中第0x200项描述符给出的段基址+0xFFFF 现在比较一下,好象是不一样。再仔细看看,又好象没什么区别! 为什么说没什么区别,因为我的想法是,既然ES中的内容都不是 真正的段地址,凭什么实模式下称ES为“段寄存器”,而到了保护模式 就说是“选择子”? 其实它们都是一种映射,只是映射规则不同而已:在实模式下这

实模式和保护模式的区别 实模式和保护模式的区别 2009-08-31 20:19 551人阅读评论(1) 收藏举报 从80386开始,cpu有三种工作方式:实模式,保护模式和虚拟8086模式。只有在刚刚启动的时候是real-mode,等到linux操作系统运行起来以后就运行在保护模式(所以存在一个启动时的模式转换问题)。 实模式只能访问地址在1M以下的内存称为常规内存,我们把地址在1M 以上的内存称为扩展内存。 在保护模式下,全部32条地址线有效,可寻址高达4G字节的物理地址空间; 扩充的存储器分段管理机制和可选的存储器分页管理机制,不仅为存储器共享和保护提供了硬件支持,而且为实现虚拟存储器提供了硬件支持; 支持多任务,能够快速地进行任务切换和保护任务环境; 4个特权级和完善的特权检查机制,既能实现资源共享又能保证代码和数据的安全和保密及任务的隔离; 支持虚拟8086方式,便于执行8086程序。 1.虚拟8086模式是运行在保护模式中的实模式,为了在32位保护模式下执行纯16位程序。它不是一个真正的CPU模式,还属于保护模式。 2.保护模式同实模式的根本区别是进程内存受保护与否。可寻址空间的区别只是这一原因的果。 实模式将整个物理内存看成分段的区域,程序代码和数据位于不同区域,系统程序和用户程序没有区别对待,而且每一个指针都是指向"实在"的物理地址。这样一来,用户程序的一个指针如果指向了系统程序区域或其他用户程序区域,并改变了值,那么对于这个被修改的系统程序或用户程序,其后果就很可能是灾难性的。为了克服这种低劣的内存管理方式,处理器厂商开发出保护模式。这样,物理内存地址不能直接被程序访问,程序内部的地址(虚拟地址)要由操作系统转化为物理地址去访问,程序对此一无所知。至此,进程(这时我们可以称程序为进程了)有了严格的边界,任何其他进程根本没有办法访问不属于自己的物理内存区域,甚至在自己的虚拟地址范围内也不是可以任意访问的,因为有一些虚拟区域已经被放进一些公共系统运行库。这些区域也不能随便修改,若修改就会有: SIGSEGV (linux 段错误);非法内存访问对话框(windows 对话框)。 CPU启动环境为16位实模式,之后可以切换到保护模式。但从保护模式无法切换回实模式

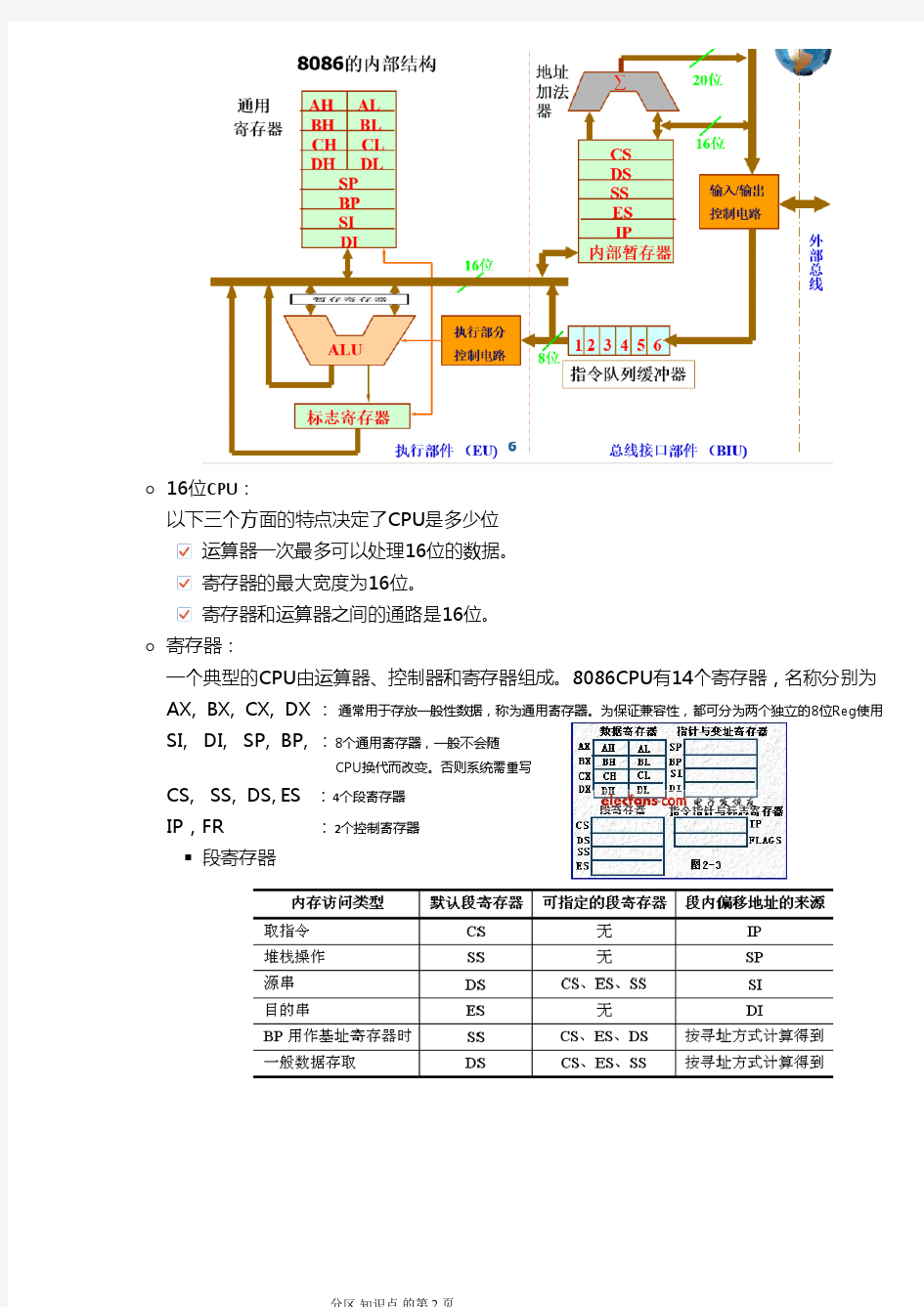

保护模式下寻址(易懂) 保护模式下寻址(易懂):网上看到的一强帖,不转不行了,牛人啊,把这段代码拿捏的相当到位括号中是我的加注段机制轻松体验[内存寻址]实模式下的内存寻址:让我们首先来回顾实模式下的寻址方式段首地址×16+偏 移量=物理地址为什么要×16?因为在8086CPU中,地址线是20位,但寄存器是16位的,最高寻址64KB,它无法寻址到1M内存。于是,Intel设计了这种寻址方式,先缩小4位成16位放入到段寄存器,用到时候,再将其扩大到20位,这也造成了段的首地址必须是16的倍数的限制。保护模式下分段机制的内存寻址:保护模式下分段机制是利用一个称作段选择符的偏移量,从而到描述符表找到需要的段描述符,而这个段描述符中就存放着真正的段的物理首地址,再加上偏移量一段话,出现了三个新名词:1、段选择子2、描述符表3、段描述符我们现在可以这样来理解这段话:有一个结构体类型,它有三个成员变量:段物理首地址段界限段属性内存中,维护一个该结构体类型的是一个数组。而分段机制就是利用一个索引,找到该数组对应的结构体,从而得到段的物理首地址,然后加上偏移量,得到真正的物理地址。公式:xxxx:yyyyyyyy其中,xxxx也就是索引,yyyyyyyy是偏移量(因为32位寄存器,所以8个

16进制)xxxx存放在段寄存器中。现在,我们来到过来分析一下那三个新名词。段描述符,一个结构体,它有三个成员变量:1、段物理首地址2、段界限3、段属性我们再来重温一遍描述符表,也就是一个数组,什么样的数组呢?是一个段描述符组成的数组。接下来看看段选择子:段选择子,也就是数组的索引,但这时候的索引不在是高级语言中数组的下标,而是我们将要找的那个段描述符相对于数组首地址(也就是全局描述表的首地址)偏移位置。就这么简单,如图:图中,通过Selector(段选择子)找到存储在Descriptor Table(描述符表)中某个Descriptor(段描述符),该段描述符中存放有该段的物理首地址,所以就可以找到内存中真正的物理段首地址SegmentOffset(偏移量):就是相对该段的偏移量物理首地址+偏移量就得到了物理地 址本图就是DATA但这时,心细的朋友就发现了一个GDTR这个家伙还没有提到!我们来看一下什么是GDTR ?Global Descriptor Table Register(全局描述符表寄存器)但是这个寄存器有什么用呢?大家想一下,段描述符表现在是存放在内存中,那CPU是如何知道它在哪里呢?所以,Intel 公司设计了一个全局描述符表寄存器,专门用来存放段描述符表的首地址,以便找到内存中段描述符表。这时,段描述符表地址被存到GDTR寄存器中了。好了,分析就到这,我们来看一下正式的定义:当x86 CPU 工作在保护模式时,可

西安外国语大学 硕士学位论文 多视角下的大遗址保护与开发模式研究 -----以汉长安城大遗址为例 作者姓名:学科专业:指导教师:魏元元 旅游管理 陈锋仪教授 西安2012

本论文由在其导师的指导下撰写而成,经论文答辩委员会评审、答辩,该论文达到专业硕士学位论文水平。 导师: 答辩主席: 日期:研究生部主任:

独创性声明 秉承学校严谨的学风与优良的科学道德,我声明所呈交的论文是我本人在导师指导下进行的研究工作所取得的成果。尽我所知,除了文中特别加以标注和致谢的地方外,论文中不包含其他人已经发表或撰写的研究成果,不包含本人或他人已申请学位或其他用途使用过的成果。他人对本研究所做的任何贡献均已在论文中作了明确的说明并表示了致谢。 申请学位论文与资料若有不实之处,本人承担一切相关责任。 作者签名: 日期:

知识产权声明 本人完全了解西安外国语大学有关知识产权的规定,即:研究生在校攻读硕士学位期间论文工作的知识产权单位属西安外国语大学。本人保证毕业离校后5年以内(自办理离校手续之日起),发表论文或使用论文工作成果时署名单位仍然为西安外国语大学。学校有权保留送交论文的复印件和磁盘文件,允许论文被查阅和借阅;学校可以公布论文的全部或部分内容,可以采用影印、缩印或其他复制手段保存论文。 作者签名: 日期:

摘要 随着申请世界遗产保护的热潮的到来,我国大遗址的保护也得到了社会各届的重视,尤其政府在大遗址的保护当中扮演着积极的角色。我国大遗址的分布范围比较分散,各种各样的大遗址给遗址保护工作带来了很大的难度。面对大遗址的保护工作,主要是从比较低层次和文物保护的角度去保护大遗址,往往给大遗址的保护带来不利的影响。大遗址的保护面临着来自“人为”和“自然为”两方面的破坏,针对大遗址保护面临着严峻的形势,我国大遗址保护应该从多角度的模式探讨,不仅要从社会科学的角度去探讨大遗址保护的方式方法,也应该从自然科学的角度,尤其是要采用当今发展迅猛的计算机技术去实现大遗址保护模式的创新去实践。 大遗址保护工作主要面临大遗址信息分散、信息多样、信息共享和交换比较难的特点,而面向服务的大遗址模式充分利用面向服务的架构SOA(service oriented architecture)技术体系针对大遗址保护的难点提出了完整的信息资源的整合模式,实现了大遗址保护的宏观与微观管理相结合;计算机三维可视化技术(OpenGL和Direct 3D)实现分散的大遗址周围地理数据库模型的建立,地理空间信息技术(GIS),WEB GIS信息技术及信息交换技术。 大遗址的保护与开发是大遗址保护模式面临的一对矛盾,面对这对矛盾,需要分析出陕西大遗址目前所面临的主要威胁,并分析其所属的类型、特点、利用因素分析法、均衡利益分析法、价值分析法、建立大遗址保护与开发评价体系价值体系,结合陕西省内大遗址目前所采用大遗址保护模式,综合对比提出基于均衡模式下陕西大遗址开发与保护模式。 多视角下的汉长安城大遗址保护与开发模式,是在综合对比国内外大遗址保护与开发模式的基础之下,结合当代计算机技术、经济学知识、管理学知识等分析总结出自己在每种视角下大遗址的保护与开发模式。针对汉长安城大遗址保护与开发模式研究,汉长安城大遗址主要采用建立“三区鼎立,综合管理”的大遗址开发保护模式,三区主要是在汉长安城大遗址上建立以汉长安城重点

整体解决方案系列 互联网安全保护技术措施 规定 (标准、完整、实用、可修改)

编号:FS-QG-49892互联网安全保护技术措施规定 Model Regulations for Internet Security Protection Measures 说明:为明确各负责人职责,充分调用工作积极性,使人员队伍与目标管理科学化、制度化、规范化,特此制定 第一条为加强和规范互联网安全技术防范工作,保障互联网网络安全和信息安全,促进互联网健康、有序发展,维护国家安全、社会秩序和公共利益,根据《计算机信息网络国际联网安全保护管理办法》,制定本规定。 第二条本规定所称互联网安全保护技术措施,是指保障互联网网络安全和信息安全、防范违法犯罪的技术设施和技术方法。 第三条互联网服务提供者、联网使用单位负责落实互联网安全保护技术措施,并保障互联网安全保护技术措施功能的正常发挥。 第四条互联网服务提供者、联网使用单位应当建立相应的管理制度。未经用户同意不得公开、泄露用户注册信息,但法律、法规另有规定的除外。互联网服务提供者、联网使

用单位应当依法使用互联网安全保护技术措施,不得利用互联网安全保护技术措施侵犯用户的通信自由和通信秘密。 第五条公安机关公共信息网络安全监察部门负责对互联网安全保护技术措施的落实情况依法实施监督管理。 第六条互联网安全保护技术措施应当符合国家标准。没有国家标准的,应当符合公共安全行业技术标准。 第七条互联网服务提供者和联网使用单位应当落实以下互联网安全保护技术措施: (一)防范计算机病毒、网络入侵和攻击破坏等危害网络安全事项或者行为的技术措施; (二)重要数据库和系统主要设备的冗灾备份措施; (三)记录并留存用户登录和退出时间、主叫号码、账号、互联网地址或域名、系统维护日志的技术措施; (四)法律、法规和规章规定应当落实的其他安全保护技术措施。 第八条提供互联网接入服务的单位除落实本规定第七条规定的互联网安全保护技术措施外,还应当落实具有以下功能的安全保护技术措施:(一)记录并留存用户注册信息;

Gate A20与保护模式 大家都知道,8088/8086只有20位地址线,按理它的寻址空间是2^20,应该是1024KB,但PC机的寻址结构是segment:offset,segment和offset都是16 位的寄存器,最大值是0ffffh,换算成物理地址的计算方法是把segment左移4位,再加上offset,所以segment:offset所能表达的寻址空间最大应为0ffff0h + 0ffffh = 10ffefh(前面的0ffffh是segment=0ffffh并向左移动4位的结果,后面的0ffffh是可能的最大offset),这个计算出的10ffefh是多大呢?大约是1088KB,就是说,segment:offset的地址表达能力,超过了20位地址线的物理寻址能力,你说这是不是有点麻烦。在早先,由于所有的机器都没有那么大的内存,加上地址线只有20位,所以当你用segment:offset的方式企图寻址100000h这个地址时,由于没有实际的第21位地址线,你实际寻址的内存是00000h的位置,如果你企图寻址100001h这个地址时,你实际得到的内容是地址00001h上的内容,所以这个事对实际使用几乎没有任何影响,但是后来就不行了,出现了80286,地址线达到了24位,使segment:offset寻址100000h--10ffefh这将近64K的存储器成为可能,为了保持向下兼容,于是出现了A20 Gate,这是后话,我们后面再细说。 我们可能经常听到一些只有在PC机上才有的一些关于存储器的专有名词,包括:常规内存(Conventional Memory)、上位内存区(Upper Memory Area)、高端内存区(High Memory Area)和扩展内存(Extended Memory),我尽量把这几个东东说明白,这需要下面这张著名的图。 这张图很清楚地说明了问题,大家都知道,DOS下的“常规内存”只有640K,这640K就是从0--A0000H这段地址空间;所谓“上位内存区”,指的就是20位地址线所能寻址到的1M地址空间的上面384K空间,就是从A0001H--100000H 这段地址空间,也就是我们说的用于ROM和系统设备的地址区域,这384K空间和常规内存的640K空间加起来就是20位地址线所能寻址的完整空间 1024KB;由于80286和80386的出现使PC机的地址线从20位变成24位又变成32位,寻址能力极大地增加,1M以上的内存寻址空间,我们统称为“扩展内存”;这里面绝大部分内存区域只能在保护模式下才能寻址到,但有一部分既可以在保护模式下,也可以在实模式下寻址,这就是我们前面提到过的地址100000h--10ffefh之间的这块内存,为了表明其特殊性,我们把这块有趣的内存区叫做“高端内存”。 前面我们提过由于IBM的愚蠢设计给PC机的内存结构埋下了麻烦的伏笔,现在我们来说说这个麻烦。我们都见过PC机上的内存条,但是由于上位内存区

第3章从8086到Pentium系列微处理器的技术发展 教材习题解答 1. 简述80286的特点和保护模式的保护功能。 【解】80286的特点: ①CPU内部分为四个处理部件:EU(执行部件)、AU(地址部件)、IU(指令部件)和BU(总线部件)。这四个处理部件可以并行的进行操作,提高了处理速度。 ②数据线和地址线完全分离。在一个总线周期中,当有效数据出现在数据总线上的时候,下一个总线周期的地址已经送到地址总线,形成总线周期的流水作业。 ③具有“实地址模式”(Real Address Mode,简称为“实模式”)和“保护虚地址模式”(Protected V irtual Address Mode,简称为“保护模式”)”两种工作模式。 ④能运行实时多任务操作系统,支持存储管理和保护功能。 ⑤实现了虚拟存储管理。 ⑥与80286 配合使用的数学协处理器是80287,它基本与8087相同,但适应80286 的两种工作模式。 保护模式体现了80286的特色,主要是对存储器管理、虚拟存储和对地址空间的保护。在保护模式下,可为每个任务提供多达1GB的虚拟存储空间和保护机制,有力地支持了多用户、多任务的操作。那些内存装不下的逻辑段,将以文件形式存在外存储器中,当处理器需要对它们进行存取操作时就会产生中断,通过中断服务程序把有关的程序或数据从外存储器调入到内存,从而满足程序运行的需要。 保护模式为不同程序设置了四个特权级别,可让不同程序在不同的特权级别上运行。依靠这一机制,可支持系统程序和用户程序的分离,并可进一步分离不同级别的系统程序,大大提高了系统运行的可靠性。 2. 简述80386 的特点、80386引脚与8086的区别。 【解】80386 的特点: 80386是全32位结构,它的外部数据总线和内部数据通道,包括寄存器、ALU和内部总线都是32位的。 80386 有3 种工作模式:实模式、虚拟86模式、386的保护模式。 80386的硬件结构可分成6个逻辑单元,它们以流水线方式工作,运行速度可达4MIPS。其硬件设计有支持段页式存储管理部件,易于实现虚拟存储系统。在保护模式下的分段寻址体系,与操作系统相配合可以组成虚拟存储器系统,一个任务的最大虚拟空间可达246=64 TB。 80386硬件支持多任务处理,用一条指令就可以实现任务切换。 80386设置了4级特权级,按优先顺序依次为0级、1级、2级、3级,前3级用于操作系统程序,后1级用于用户程序。 80386引脚与8086的区别见表3-1。 表3-1 80386引脚与8086的区别 8086CPU 80386CPU 共有40个引脚共有132个引脚 16条地址/数据复用线4条地址线34条地址线 32条数据线 在总线宽度控制信号16 BS的控制下,可实现16位或32位数据传送。字节控制信号0 BE~3 BE 协处理器接口信号 (1) PEREQ:协处理器向80386发出的请求信号,有效时表示协处理器请求与存储器之间传送数据。80386响应该请求后,将按照指令的要求控制对存储器的读写。 (2) BUSY:协处理器向80386发出的状态信号,有效时表示协处理器正在执行指令,处于忙状态,暂时不能接受新的指令。 (3)ERROR:协处理器向80386发出的状态信号,有效时表示协处理器出错。80386在检测到ERROR信号后,将转到错误处理子程序来处

第1章保护模式编程一 如果想更深、更亲近的了解电脑软件。那么学习cpu是你的必选!! 386是CPU史的一大转折点,那386做基础课是最好不过了。那么我们将开始进行学习之旅!!!大家跟我一块学习吧,呵呵!!! 1.1 准备工作 l1、NASM 编译环境(当然Masm 也可以但是用它来写COM程序比较 麻烦) l2、虚拟机 Virtual PC(Windows平台,执行比较快,即模拟又虚拟硬件)、 WMWarve(WIndows平台虚拟硬件,)、 Bochs(支持Windows平台、也支持在Linux平台上运行有RPM版本的) 我们这些生长在Windows这棵大树下的朋友们,还是用Virtual PC吧.。 l3、写虚拟启动镜像文件的程序 :不知道我观察的对不对?用Nasm 编译一个bin 然后将它转换为img 镜像文件的时候。只要文件大小符合软驱的标准就能启动。那么就代表a.bin 与a.img 文件的内容一模样就是文件大小不一样!我是不太了解镜像文件格式.我用的是Virtual PC。 1.2 开始接触引导程序 1.2.1 Com文件 Com文件是纯二进制的文件,也是直接与Cpu交换的顺序指令文件。Com文件的大小是有限制的,不能超过64KB.因为8086时代的CPU地址线是20位的,20位能表达的数值也就是fffffh(1MB )。而寄存器最高也只是16位,无法用5个F的形式来表达地址,所以用CS(段基地址)*16:IP(偏移地址)来寻址!80386后通用寄存器都得到了32位扩展! 而Cpu地址线也得到了32位的扩展。引导程序前期是需要进入实模式的,因为这是硬件上的限制是IA32的限

《微机原理与接口技术》李华贵主编 课后习题参考答案 第1章(1.6 习题) 1.简述名词的概念:微处理器、微型计算机、微型计算机系统。 答: (1)微处理器:微处理器(Microprocessor)简称μP或MP,或CPU。CPU是采用大规模和超大规模集成电路技术将算术逻辑部件ALU(Arithmetic Logic Unit)、控制部件CU (Control Unit)和寄存器组R(Registers)等三个基本部分以及内部总线集成在一块半导体芯片上构成的电子器件。 (2)微型计算机:微型计算机(Microcomputer)是指以微处理器为核心,配上由大规模集成电路制作的存储器、输入/输出接口电路及系统总线等所组成的计算机,简称微机。 (3)微型计算机系统:微型计算机系统由硬件与软件两大部分组成,分别称为硬件(Hardware)系统与软件(Software)系统。其中,硬件(Hardware)系统由CPU、内存储器、各类I/O接口、相应的I/O设备以及连接各部件的地址总线、数据总线、控制总线等组成。 软件(Software)系统:计算机软件(Software)是指为运行、维护、管理、应用计算机所编制的程序及程序运行所需要的数据文档资料的总和。一般把软件划分为系统软件和应用软件。其中系统软件为计算机使用提供最基本的功能,但是并不针对某一特定应用领域。而应用软件则恰好相反,不同的应用软件根据用户和所服务的领域提供不同的功能。 2.简述名词的概念:指令寄存器、地址寄存器、标志寄存器。 答: (1)指令寄存器:指令寄存器(Instruction Register,IR)用来保存计算机当前正在执行或即将执行的指令。当一条指令被执行时,首先,CPU从内存取出指令的操作码,并存入IR中,以便指令译码器进行译码分析。 (2)地址寄存器:地址寄存器(Address Register,AR)被动地接受IP传送给它的地址值(二进制地址),AR的作用是保持IP送来的地址,并且以并行方式连接输出到CPU的地址引脚上,以便CPU访问指定的内存单元。 (3)标志寄存器:标志寄存器(Flags,F)是CPU中不可缺少的程序状态寄存器,因此,也称程序状态字寄存器(PSW),所谓状态是指算术或逻辑运算后,结果的状态以二进制的0或1在标志寄存器中标识出来,例如,运算结果有进位,则进位标志位CF=1,否则为0。 3.何谓IA-32处理器?

保护模式下寻址 网上看到的一强帖,不转不行了,牛人啊,把这段代码拿捏的相当到位括号中是我的加注 段机制轻松体验 [内存寻址] 实模式下的内存寻址: 让我们首先来回顾实模式下的寻址方式 段首地址×16+偏移量=物理地址 为什么要×16?因为在8086CPU中,地址线是20位,但寄存器是16位的,最高寻址64KB,它无法寻址到1M 内存。于是,Intel设计了这种寻址方式,先缩小4位成16位放入到段寄存器,用到时候,再将其扩大到20位,这也造成了段的首地址必须是16的倍数的限制。 保护模式下分段机制的内存寻址: 保护模式下分段机制是利用一个称作段选择符的偏移量,从而到描述符表找到需要的段描述符,而这个段描述符中就存放着真正的段的物理首地址,再加上偏移量 一段话,出现了三个新名词: 1、段选择子 2、描述符表 3、段描述符 我们现在可以这样来理解这段话:有一个结构体类型,它有三个成员变量:段物理首地址段界限段属性内存中,维护一个该结构体类型的是一个数组。而分段机制就是利用一个索引,找到该数组对应的结构体,从而得到段的物理首地址,然后加上偏移量,得到真正的物理地址。 公式:xxxx:yyyyyyyy 其中,xxxx也就是索引,yyyyyyyy是偏移量(因为32位寄存器,所以8个16进制)xxxx存放在段寄存器中。 现在,我们来到过来分析一下那三个新名词。段描述符,一个结构体,它有三个成员变量:1、段物理首地址2、段界限3、段属性 我们再来重温一遍描述符表,也就是一个数组,什么样的数组呢?是一个段描述符组成的数组。 接下来看看段选择子:段选择子,也就是数组的索引,但这时候的索引不在是高级语言中数组的下标,而是我们将要找的那个段描述符相对于数组首地址(也就是全局描述表的首地址)偏移位置。 就这么简单,如图:

80386 和保护模式 ___William Liu Intel CPU 一般可以运行在两种模式之下,即实模式和保护模式。早期的 Intel CPU ( 8086 , 8088 )只能工作在实模式之下,系统中只能运行单个任务,而且只能使用实地址模式。对于 Intel 80386 以上的芯片则还可以运行在 32 位的保护模式之下。在保护模式之下的 CPU 可以支持多任务;支持 4GB 的物理内存;支持 64TB 的虚拟内存;支持内存的页式管理和段式管理以及支持特权级。 本文档将首先介绍 Intel 80386 CPU 的几个内部寄存器,然后再由浅入深的分别介绍保护模式下的段式管理,页式管理,虚拟内存,多任务以及特权级管理等几个方面。 Intel 80386 CPU 的内部寄存器 这一部分先大致介绍一下 386 的内部寄存器,具体细节在后面的几节中再详细说明。一般来说, CPU 设计用来系统编程的系统寄存器包括如下几类: ?标志寄存器 (EFLAGS) ?内存管理寄存器 (GDTR , LDTR , IDTR , TR) ?控制寄存器 (CR0 , CR1 , CR2 , CR3 , CR4) ?兼容 8086 通用寄存器( EAX , EBX , ECX , EDX ) ?兼容 8086 段寄存器( CS , DS , ES , SS , FS , GS ) ?兼容 8086 数据寄存器( ESI , EDI , EIP , ESP ) 下面分别加以介绍:

1) 标志寄存器 EFLAGS : 跟 8086/8088 的 FLAGS 大致差不多。只不过位宽由 16bit 变成了 32bit ,负责的状态标志也多了一些。见图一所示: 图一: EFLAGS 的结构 其中系统标志: VM -虚拟 8086 模式; RF -恢复标志; NT -任务嵌套标志;IOPL - I/O 特权级标志; IF -中断允许标志。 2) 内存管理寄存器: 一共有 4 个,用于分段内存管理,都是用于存放指针的,只是所指的再内存单元中的内容有所不同。 GDTR 全局描述符表寄存器( Global Descriptor Table Register ),存放的是一个指向内存单元列表的指针,用于指向全局段描述表( GDT ),如图二所示。共 48bit ,高 32bit 是 GDT 的基址,低 16bit 描述 GDT 的长度。由于每项 8Byte ,所以共可以有 2^(16)/8=2^13 项。 IDTR 中断描述符表寄存器( Interrupt Descriptor Table Register ),存放的是也一个指向内存单元列表的指针,用于指向全局中断描述符表( IDT ),如图二所示。跟 GDTR 一样,共 48bit 。

文章编号:1000-582X(2002)06-0067-04 X86体系中保护模式下的内存访问机制Ξ 湛辉来,曾 一 (重庆大学计算机学院,重庆400044) 摘 要:保护模式是X86体系结构的一种重要的工作方式,为在X86平台上实现的多任务、多进程操作系统提供了相应的硬件支持。在计算机的底层开发过程中,了解计算机体系结构中的主要部件-内存的工作方式是及其重要的。文章介绍了当前较流行的微机体系结构-X86系统中的内存的组织、管理、和访问机制,分析了X86在保护模式下分段机制、分页机制中的一些主要的数据结构和相应的硬件支持,并详细描述了分段机制中逻辑地址到线性地址的转换,分页机制中虚拟地址到物理地址的转换过程。通过分页和分段机制,可以实现多进程操作系统中的进程独立地址空间,以及对操作系统中内存的保护措施,从而及时而有效地防止了因内存的非法访问而导致的系统崩溃。 关键词:保护模式;描述符;描述符表;页表;页目录 中图分类号:TP31611文献标识码:A Intel的80X86CPU系列芯片可在2种模式下工作:实模式、保护模式[1]。实模式是MS-DOS的运行环境。当内存寻址模式为实模式时,采用80286的20位地址线的存储器分段线性管理技术,存储器容量最大为1M B,线性地址与物理地址一致,对物理内存单元读写直接、灵活。但因受限于640K基本内存,使大量的扩展内存的使用受到制约,同时,分段的64K范围限制影响了内存访问的连续性,从而使系统的内存资源难以得到充分利用。在保护模式下,系统采用分段机制和分页机制,提供了灵活的寻址方式,使得应用程序可以访问多达4G B的存储空间,并为操作系统和应用程序实现虚拟存储器提供了相应的硬件支持,从而打破了实模式下内存寻址所受到的制约,提高了内存资源的使用效率。 1 X86的分段机制 X86的分段机制就是将X86的线性地址空间分成若干空间段(Segment),利用这些段来存储(记录)代码和数据,通过对段的保护来提供一种对数据或代码的保护[2]。这种寻址模式允许CPU访问装在1M B以上的数据和程序代码,就象在实模式中访问1M B以内的内存一样。1.1 分段机制中的数据结构 在分段机制,X86使用了如下几种主要数据结构: 1)段描述符(Segment Descriptor):用来描述一个段的位置、长度以及访问权限。一个描述符由8个字节组成,具体的格式如下 : 其中:基地址描述了该段的开始位置共32位,使得该段可以从4G空间里的任意一个位置开始。段的长度是由20位的界限和一个标志位G决定。标志位G位于0字节的最高一个比特,它的含义如下: 0:段的长度=界限 范围为1B~1M B 1:段的长度=界限34K 范围为4K B-4G B 2)全局描述符表(G DT,G lobal Describe T able):存放系统用的段描述符和各项任务共用的段描述符; 3)局部描述符表(LDT,Local Describe T able):存放某个任务专用的各段的段描述符; 每个描述符表中最大可以放8,192个段描述符,因此,每个描述符表的最大长度为64K B。 1.2 分段机制的硬件支持 X86提供了如下几个用于支持分段机制的寄存器: 2002年6月重庆大学学报 (自然科学版)V ol.25 N o.6第25卷第6期Journal of Chongqing University(Natural Science Edition)Jun.2002 Ξ收稿日期:2002-01-21 作者简介:湛辉来(1972-),男,重庆人,重庆大学硕士研究生。主要研究方向:软件工程及计算机体系结构。

1:实模式:寻址采用和8086相同的16位段和偏移量,最大寻址空间1MB,最大分段64KB。可以使用32位指令。32位的x86 CPU用做高速的8086。 2:保护模式:寻址采用32位段和偏移量,最大寻址空间4GB,最大分段4GB (Pentium Pre及以后为64GB)。在保护模式下CPU可以进入虚拟8086方式,这是在保护模式下的实模式程序运行环境。 第一:实模式下程序的运行回顾. 程序运行的实质是什么?其实很简单,就是指令的执行,显然CPU 是指令得以执行的硬件保障,那么CPU如何知道指令在什么地方呢? 对了,80x86系列是使用CS寄存器配合IP寄存器来通知CPU指令在内存 中的位置. 程序指令在执行过程中一般还需要有各种数据,80x86系列有DS、 ES、FS、GS、SS等用于指示不同用途的数据段在内存中的位置。 程序可能需要调用系统的服务子程序,80x86系列使用中断机制 来实现系统服务。 总的来说,这些就是实模式下一个程序运行所需的主要内容 (其它如跳转、返回、端口操作等相对来说比较次要。) 第二:保护模式---从程序运行说起 无论实模式还是保护模式,根本的问题还是程序如何在其中运行。 因此我们在学习保护模式时应该时刻围绕这个问题来思考。 和实模式下一样,保护模式下程序运行的实质仍是“CPU执行指令, 操作相关数据”,因此实模式下的各种代码段、数据段、堆栈段、中 断服务程序仍然存在,且功能、作用不变。 那么保护模式下最大的变化是什么呢?答案可能因人而异,我的 答案是“地址转换方式”变化最大。 第三:地址转换方式比较 先看一下实模式下的地址转换方式,假设我们在ES中存入0x1000, DI中存入0xFFFF,那么ES:DI=0x1000*0x10+0xFFFF=0x1FFFF,这就是众 所周知的“左移4位加偏移”。 那么如果在保护模式下呢?假设上面的数据不变ES=0x1000, DI=0xFFFF,现在ES:DI等于什么呢? 公式如下:(注:0x1000=1000000000000b= 10 0000 0000 0 00) ES:DI=全局描述符表中第0x200项描述符给出的段基址+0xFFFF 现在比较一下,好象是不一样。再仔细看看,又好象没什么区别! 为什么说没什么区别,因为我的想法是,既然ES中的内容都不是 真正的段地址,凭什么实模式下称ES为“段寄存器”,而到了保护模式 就说是“选择子”? 其实它们都是一种映射,只是映射规则不同而已:在实模式下这 个“地址转换方式”是“左移4位”;在保护模式下是“查全局/局部描述表” 。前者是系统定义的映射方式,后者是用户自定义的转换方式。而它 影响的都是“shadow register” 从函数的观点来看,前者是表达式函数,后者是列举式函数: 实模式:F(es-->segment)={segment |segment=es*0x10}

第十二章模式转换——从实模式进入保护模式 12.1 NASM编译实践 12.1.1 实验20 ——NASM编译 ●情景描述 使用NASM编译一段程序,并可以在裸机上运行。 ●实现功能 在开机后显示"Hello, OS world!" ●流程 1)初始化寄存器 2)调用BIOS int 10h,显示字符串 3)进入死循环 ●代码及注释 %define _BOOT_DEBUG_ %ifdef _BOOT_DEBUG_ org 0100h %else org 07c00h %endif ;告诉编译器加载到0100处生成,这样方便生成com文件。 ;或者告诉编译器加载到7c00处生成,这样方便 mov ax,cs;将当前段地址放入ax,可以不要 mov ds,ax;将当前段地址放入数据寄存器,可以不要 mov es,ax;将当前段地址放入extra寄存器,可以不要 call DispStr;调用显示字符串程序 jmp $;无限循环(跳转到当前地址) DispStr: mov ax,BootMessage ;BootMessage的首地址送ax mov bp,ax; 段内地址送到bp,至此地址完成——CS:BP = 串地址 mov cx,16; CX = 串长度 mov ax,01301h; AH = 13,AL = 01h mov bx,000ch; BH = 0(页号为0),BL = 0ch(黑底红字高亮) mov dl,0 ; 0送dx寄存器的低字节 int 10h; 10h号中断(视频中断,对应的中断向量为40-43H) ret ; 从显示子程序中返回到主程序 BootMessage: db "Hello, OS world!" times 510-($-$$) db 0; 用“0”填充0面0磁道1扇区剩下的空间,使生成的二进制代码恰好为512字节; ;$是当前行的段内偏移地址,$$是本小节代码的第一行代码,在本程序中就是“org 07c00h”的段内偏移地址。 dw 0xaa55;结束标志.使得0面0磁道1扇区510字节存55,511字节存aa,0扇区从0-511号单元,共512个字节。(引导扇区的结束标志)

实模式、保护模式和虚拟8086模式 一直以来,都搞不清楚这几个概念。在网上搜了一下,把它晒上,不会再忘记!有其它的内容,请看到的朋友请补充。 实模式与保护模式 1. 实模式,又叫实地址模式,CPU完全按照8086的实际寻址方法访问从00000h--FFFFFh (1MB大小)的地址范围的内存,在这种模式下,CPU只能做单任务运行;寻址公式为:物理地址=左移4位的段地址+偏移地址,即:物理地址是由16位的段地址和16位的段内偏移地址组成的。 2.保护模式,又叫内存保护模式,寻址采用32位段和偏移量,最大寻址空间4GB,在这种模式下,系统运行于多任务,设计这种模式的原因和好处是:保护模式增加了寻址空间,增加了对多任务的支持,增加了段页式寻址机制的内存管理(分段机制使得段具有访问权限和特权级,各应用程序和操作系统的代码和核心是被保护的,这也是多任务支持的实现关键和保护这个名字的由来)。寻址过程为:物理地址=由段地址查询全局描述符表中给出的段基址+偏移地址,即:物理地址由影像寄存器中的基址加上16位或者32位的偏移组成。 1:实模式 是CPU启动的时候的模式 这时候就相当于一个速度超快的8086 不能使用多线程 不能实现权限分级 还不能访问20位以上地址线,也就是说只能访问1M内存(!!!) 2:保护模式 操作系统接管CPU后. 会使CPU进入保护模式. 这时候可以发挥80x86的所有威力.. 包括权限分级.内存分页.等等等等各种功能 从80386开始,cpu有三种工作方式:实模式,保护模式和虚拟8086模式。只有在刚刚启动的时候是real-mode,等到linux操作系统运行起来以后

段机制轻松体验(实模式和保护模式) [内存寻址] 实模式下的内存寻址: 让我们首先来回顾实模式下的寻址方式 段首地址×16+偏移量=物理地址 为什么要×16?因为在8086CPU中,地址线是20位,但寄存器是16位的,最高寻址64KB,它无法寻址到1M内存。于是,Intel设计了这种寻址方式,先缩小4位成16位放入到段寄存器,用到时候,再将其扩大到20位,这也造成了段的首地址必须是16的倍数的限制。 保护模式下分段机制的内存寻址: 保护模式下分段机制是利用一个称作段选择符的偏移量,从而到描述符表找到需要的段描述符,而这个段描述符中就存放着真正的段的物理首地址,再加上偏移量 一段话,出现了三个新名词: 1、段选择子 2、描述符表 3、段描述符 我们现在可以这样来理解这段话:有一个结构体类型,它有三个成员变量:段物理首地址段界限段属性 内存中,维护一个该结构体类型的是一个数组。而分段机制就是利用一个索引,找到该数组对应的结构体,从而得到段的物理首地址,然后加上偏移量,得到真正的物理地址。 公式:xxxx:yyyyyyyy 其中,xxxx也就是索引,yyyyyyyy是偏移量(因为32位寄存器,所以8个16进制)xxxx 存放在段寄存器中。 现在,我们来到过来分析一下那三个新名词。段描述符,一个结构体,它有三个成员变量:1、段物理首地址2、段界限3、段属性 我们再来重温一遍描述符表,也就是一个数组,什么样的数组呢?是一个段描述符组成的数组。 接下来看看段选择子:段选择子,也就是数组的索引,但这时候的索引不在是高级语言中数组的下标,而是我们将要找的那个段描述符相对于数组首地址(也就是全局描述表的首地址)偏移位置。

《计算机组成原理(含汇编)》 站点:专业年级:姓名:学号: 一、名词解释题(每空4分,共20分) 1.冯-诺依曼计算机 2.CISC和RISC 3.定点数和浮点数 4.微命令、微指令,微程序 5.指令流程 二、填空题(每空1分,共20分) 1、某定点小数字长16位,含一位符号位,补码表示,其能表示数的范围为,分辨率为。 2、CPU从主存取出一条指令并执行该指令的时间叫,它通常包含若干 个,而后者又包含若干个组成多级时序系统。 3、在组合逻辑(硬连逻辑)控制器中,是由组合逻辑电路产生的。电路固 定下来之后修改和扩展。 4、保护模式存储器寻址方式下,逻辑地址由段选择器和两部分组成。段选择 器存放在中,但它不能直接确定段基址,而由CPU通过一定的方法取得段基址,再和相加,从而求得所选存储单元的线性地址,线性地址再通过转换成物理地址。 5、已知BX=8830H,CF=1,执行指令:ADC BX,87CFH之后,BX=____________,标志 位的状态分别为CF=_______,ZF=_______,OF=________,SF=__________。 6、在80X86汇编语言程序中,逻辑地址可表示为: 7、伪指令语句是用来指示的语句,伪指令语句除 了其外,其他项均没有对应的目标代码 8、设字长8位,-128的补码是 三、问答题(共20分) 1、在实模式下如何实现存储器寻址?(5分)。

2、何谓组合逻辑控制器?何谓微程序控制器?试比较它们的优缺点。(6分) 3、简要说明80x86的三组基本结构寄存器组包含哪些寄存器?简要说明各寄存器组的用途。(9分) 四、计算题(共20 分) 1、分别写出下列各二进制数的原码、补码,设字长(含一位数符)为8位。(5分) (1)0;(2)0.1101;(3)- 0.1101;(4)1101; (5) –1101 2、用变形补码计算,并指出是否有溢出。(5分) (1) 补=11,110011 ; 补 = 00,10110,计算 补 - 补 = ?[X-Y]的真值=? (2) 补=00,101010; 补 = 11,111001,算 补 - 补 = ?[X+Y]的真值=? 3、设两个浮点数,X=×0.110111,Y=×(- 0.101001),其浮点格式为:阶码四位 位数8位,且均用双符号位。按浮点加减运算规则计算 补+ 补 = ?(10分) 五、阅读程序(共20分) 1、假设(BX)=12FFH,有以下程序段,阅读程序后在“;”后填上指令的功能及执行该指令后相应寄存器的内:(6分) MOV CL,8 ;功能(CL)= ROL BX,CL ;功能(BX)= AND BX,0FFH ;功能(BX)= CMP BX,0FFH ;功能 (BX)= ,ZF= ,CF= 2、在实模式下,已知堆栈寄存器SS的内容是0100H,堆栈指针SP的内容00FEH, 写出计算段基址(物理地址)的过程,并画出执行以下程序段后,堆栈区和SP的内容变化过程示意图(标出存储单元的物理地址)(6分) MOV AX,1234H MOV BX,5678H PUSH AX PUSH BX POP CX 3、程序如下: MOV CX, 9 MOV AL ,01H