浅析MOSFET 高速驱动器电路设计

赵

云

(船舶重工集团公司723所,扬州225 l )

摘要

通过对M O SFET 转换过程的分析,得出高速转换过程对驱动电路的要求。通过对转换过程

中功率损耗的计算和驱动电流计算的注意事项,得出了在设计高速驱动M O SFET 电路过程中的要点。这对用开关电源设计M O SFET 的高速驱动电路有参考价值。

关键词

M O SFET

驱动电路功率损耗

引

言

开关电源的发展趋势是工作频率越来越高。国外发达国家的实用频率已接近或超过l MH Z ,

我国目前实用频率为5 !l k H Z 。要提高工作频率,驱动电路的设计选型尤为重要,因此在MH Z 范围工作的高速MO SFET 的过渡过程就成为整个开关过程的重要部分。过渡过程太慢不仅影响工作频率的提高,而且对开关电源的效率、寿命等产生严重影响。本文就工程研制中高速驱动电路的设计考虑加以分析。

l

高速转换过程分析

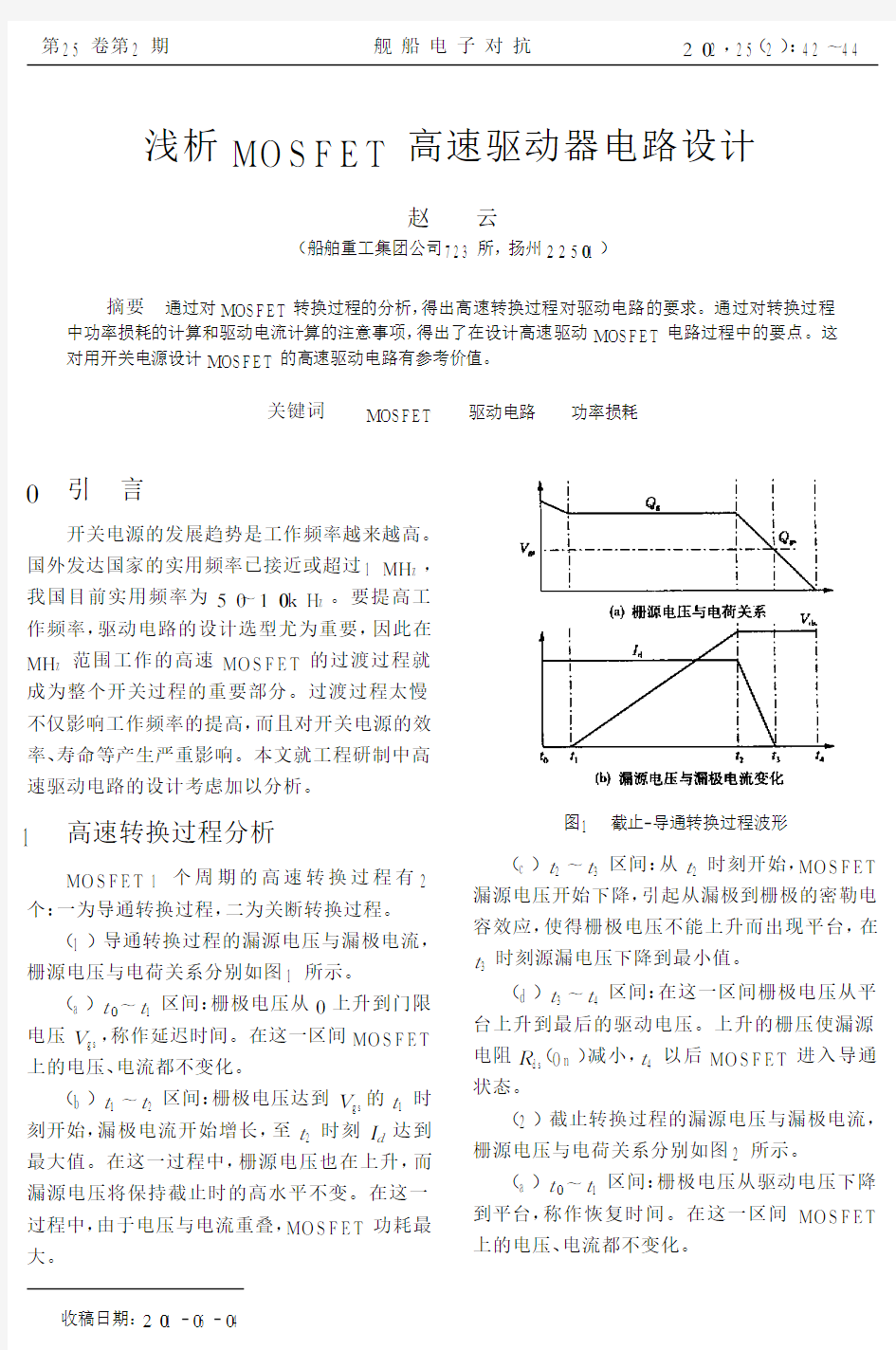

MO SFET l 个周期的高速转换过程有2个:一为导通转换过程,二为关断转换过程。(l )导通转换过程的漏源电压与漏极电流,栅源电压与电荷关系分别如图l 所示。(a )m !m l 区间:

栅极电压从 上升到门限电压V g s ,称作延迟时间。在这一区间MO SFET 上的电压、电流都不变化。

(b )m l !m 2区间:栅极电压达到V g s 的m l 时刻开始,漏极电流开始增长,至m 2时刻I d 达到最大值。在这一过程中,栅源电压也在上升,而漏源电压将保持截止时的高水平不变。在这一过程中,由于电压与电流重叠,MO SFET 功耗最大。

图l

截止导通转换过程波形

(c )m 2!m 3区间:从m 2时刻开始,

MO SFET 漏源电压开始下降,引起从漏极到栅极的密勒电容效应,使得栅极电压不能上升而出现平台,在

m 3时刻源漏电压下降到最小值。

(d )m 3!m 4区间:

在这一区间栅极电压从平台上升到最后的驱动电压。上升的栅压使漏源电阻R ds (On )减小,m 4以后MO

SFET 进入导通状态。

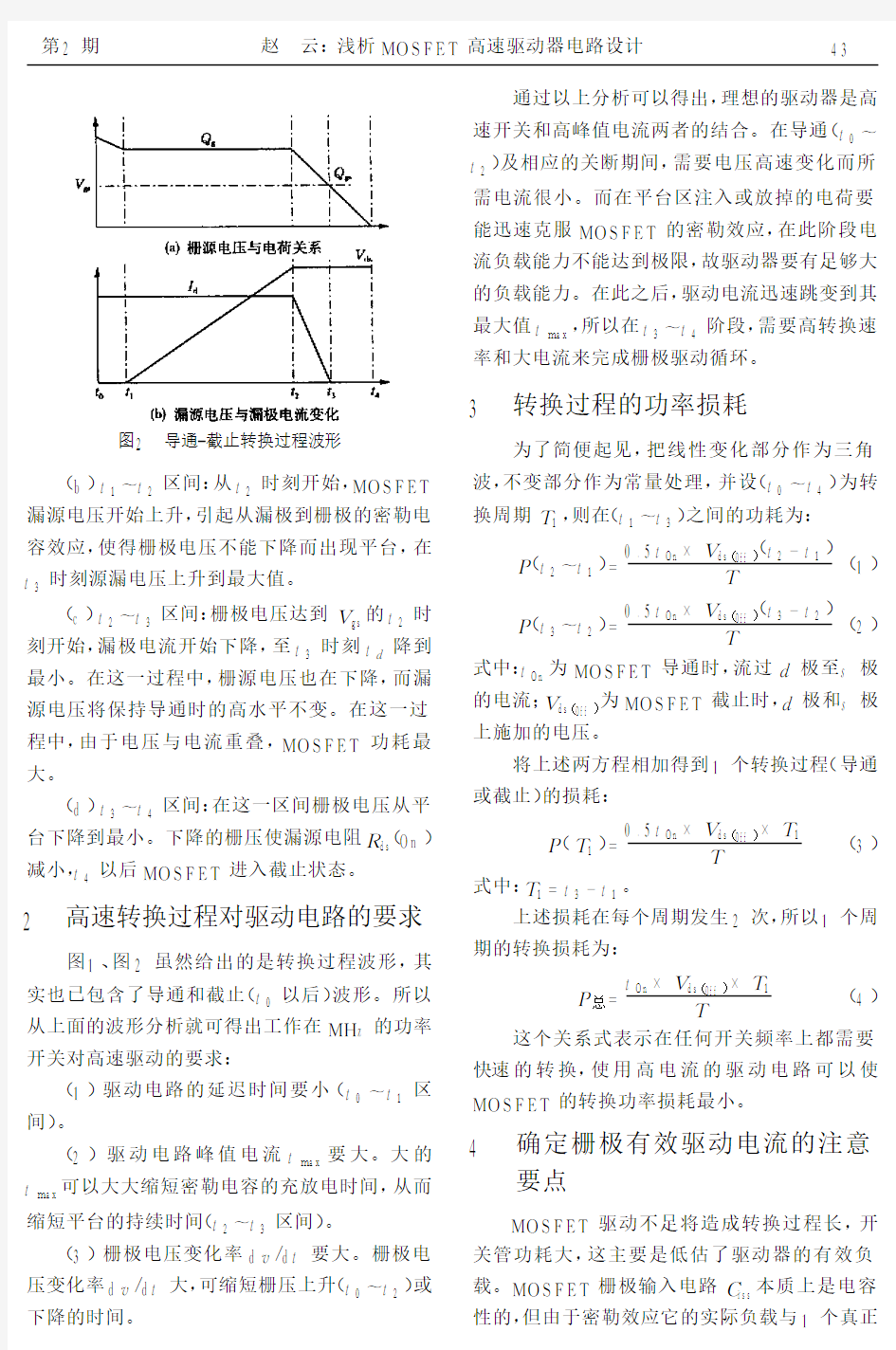

(2)截止转换过程的漏源电压与漏极电流,栅源电压与电荷关系分别如图2所示。(a )m !m l 区间:

栅极电压从驱动电压下降到平台,称作恢复时间。在这一区间MO SFET 上的电压、电流都不变化。

收稿日期:2 l 6 4

第25卷第2期

舰船电子对抗

2 2,25(2):42!

44

图2导通截止转换过程波形

(b)I

1

!I2区间:从I2时刻开始,MO SFET 漏源电压开始上升,引起从漏极到栅极的密勒电容效应,使得栅极电压不能下降而出现平台,在I3时刻源漏电压上升到最大值。

(c)I

2

!I3区间:栅极电压达到V g s的I2时

刻开始,漏极电流开始下降,至I

3时刻I

d

降到

最小。在这一过程中,栅源电压也在下降,而漏源电压将保持导通时的高水平不变。在这一过程中,由于电压与电流重叠,MO SFET功耗最大。

(d)I

3

!I4区间:在这一区间栅极电压从平

台下降到最小。下降的栅压使漏源电阻r

ds

(On)

减小,I

4

以后MO SFET进入截止状态。

2高速转换过程对驱动电路的要求图1、图2虽然给出的是转换过程波形,其

实也已包含了导通和截止(I

以后)波形。所以从上面的波形分析就可得出工作在MH Z的功率开关对高速驱动的要求:

(1)驱动电路的延迟时间要小(I

!I1区间)。

(2)驱动电路峰值电流I

m ax

要大。大的I m ax可以大大缩短密勒电容的充放电时间,从而

缩短平台的持续时间(I

2

!I3区间)。

(3)栅极电压变化率d U/d I要大。栅极电

压变化率d U/d I大,可缩短栅压上升(I

!I2)或

下降的时间。

通过以上分析可以得出,理想的驱动器是高

速开关和高峰值电流两者的结合。在导通(I

! I2)及相应的关断期间,需要电压高速变化而所需电流很小。而在平台区注入或放掉的电荷要能迅速克服MO SFET的密勒效应,在此阶段电流负载能力不能达到极限,故驱动器要有足够大的负载能力。在此之后,驱动电流迅速跳变到其

最大值I

m ax

,所以在I

3

!I4阶段,需要高转换速率和大电流来完成栅极驱动循环。

3转换过程的功率损耗

为了简便起见,把线性变化部分作为三角

波,不变部分作为常量处理,并设(I

!I4)为转

换周期T

1

,则在(I

1

!I3)之间的功耗为:

P(I2!I1)=

0.5I On X V ds(Off)(I2-I1)

T

(1)P(I3!I2)=

0.5I On X V ds(Off)(I3-I2)

T

(2)

式中:I

On

为MO SFET导通时,流过d极至S极

的电流;V

ds(Off)

为MO SFET截止时,d极和S极

上施加的电压。

将上述两方程相加得到1个转换过程(导通

或截止)的损耗:

P(T1)=

0.5I On X V ds(Off)X T1

T

(3)

式中:T

1

=I3-I1。

上述损耗在每个周期发生2次,所以1个周期的转换损耗为:

P总=

I On X V ds(

Off)

X T1

T

(4)这个关系式表示在任何开关频率上都需要快速的转换,使用高电流的驱动电路可以使MO SFET的转换功率损耗最小。

4确定栅极有效驱动电流的注意要点

MO SFET驱动不足将造成转换过程长,开关管功耗大,这主要是低估了驱动器的有效负

载。MO SFET栅极输入电路C

iss

本质上是电容

性的,但由于密勒效应它的实际负载与1个真正

34

第2期赵云:浅析MO SFET

高速驱动器电路设计

的容性负载有很大差别,更不能仅将MO SFET 的输入电容当作驱动器的实际负载来考虑。实际上1个MO SFET的有效输入电容!

ie

要比!iss高得多,所以驱动电路的设计选型不仅要知道最大有效负载,更重要的是要知道驱动器在1次给足的开关过程中的瞬时负载。以上参数从厂家提供的手册上可以查到。

5简易驱动电路

以前使用过的栅极驱动电路如图3所示。图3(a)所示射随器用在低频应用中,图3(b)所示电路用于高频。由于技术、成本等方面的考虑,这两种驱动电路目前仍在应用中。但上述两

图3简易驱动电路

种驱动器有不足之处。图3(a)由于用两种类型

MO S管,其阀值不同,当输入电压大于NMO S 的阀值电压而小于P MO S的阀值电压时也存在直通现象。在两漏极之间串入1个小阻值电阻可以减少浪涌电流,但会因此而限制驱动电路的峰值电流。

6结束语

我国目前普及的开关电源制作受技术、器件、成本等方面的影响,部分关键器件还依赖进口,以上两种驱动电路使用较多。但开关电源工作频率的提高是不容置疑的。开关电源频率的提高将使开关电源在技术特性、体积、可靠性等方面有很大的飞跃。随着集成电路技术的发展,现在已研制出第3代集成驱动器。它不仅克服了上述简易驱动电路的不足,而且d"/d#高,峰值电流大。有的还可以实现远程关闭控制,大大简化了高速MO SFET的工作应用设计。相信随着国内关键器件的不断出现和发展,国内开关电源的工作频率将越来越高,技术性能将越来越好,将使我国开关电源的制作水平迈上新的台阶。

(上接第39页)

测量中,水负载对微波的热转换效率及替代的不完全一致是测量不确定度的最大贡献因素,其次为电路的影响(主要是供电电压的不稳定)。

结合某型发射机的测量效果,得出:

(1)由于某些原因导致水质不纯,渐变管形变,水流波动等情况时诸参数之间的相对改变使相对于被测功率而言的替代(校准)功率失去了准确替代的价值。

(2)针对具体实验测量,虽然一般性的失配所造成的影响是很常见的,而且对测量结果并无过多的牵制,但严重失配会导致过大的微波反射,容易造成对被测主体(如发射机组)的损坏,绝对不能忽视。

(3)功率计的电路部分最好能采取有针对

电压变动进行自动校准的数字显示,因为其精确度优势突出,从而可能成倍降低电因素的灵敏度系数。

5结束语

总之,在实验室条件下必须先行对生产厂家给定的水负载结构的一致性进行分析论证和优选,并在实验过程中保证水的纯净、稳定的电压供给与良好的匹配,从而尽可能提高发射机测量结果的准确性和可信度,完成对被测发射机的功率因素的定量处理。

参考文献

1汤世贤.微波测量.北京:国防工业出版社,1991

44舰船电子对抗第25

卷

浅析MOSFET高速驱动器电路设计

作者:赵云

作者单位:船舶重工集团公司723所,扬州,225001

刊名:

舰船电子对抗

英文刊名:SHIPBOARD ELECTRONIC WARFARE

年,卷(期):2002,25(2)

被引用次数:2次

引证文献(2条)

1.曹芳磊.孙奉娄IGBT强驱动电路的设计[期刊论文]-现代电子技术 2010(19)

2.纪圣儒.朱志明.周雪珍.王琳化MOSFET隔离型高速驱动电路[期刊论文]-电焊机 2007(5)本文链接:https://www.doczj.com/doc/187220378.html,/Periodical_jcdzdk20020201

3.aspx

[讨论]今天终于弄懂了PCB高速电路板设计的方法和技巧受益匪浅啊 电容, 最大功率, 技巧 高速电路设计技术阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,并且得到最大功率输出的一种工作状态。高速PCB布线时,为了防止信号的反射,要求线路的阻抗为50Ω。这是个大约的数字,一般规定同轴电缆基带50Ω,频带75Ω,对绞线则为100Ω,只是取整数而已,为了匹配方便。根据具体的电路分析采用并行AC端接,使用电阻和电容网络作为端接阻抗,端接电阻R要小于等于传输线阻抗Z0,电容C必须大于100pF,推荐使用0.1UF的多层陶瓷电容。电容有阻低频、通高频的作用,因此电阻R不是驱动源的直流负载,故这种端接方式无任何直流功耗。 串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生不期望的电压噪声干扰。耦合分为容性耦合和感性耦合,过大的串扰可能引起电路的误触发,导致系统无法正常工作。根据串扰的一些特性,可以归纳出几种减小串扰的方法: 1、加大线间距,减小平行长度,必要时采用jog 方式布线。 2、高速信号线在满足条件的情况下,加入端接匹配可以减小或消除反射,从而减小串扰。 3、对于微带传输线和带状传输线,将走线高度限制在高于地线平面范围要求以内,可以显著减小串扰。 4、在布线空间允许的条件下,在串扰较严重的两条线之间插入一条地线,可以起到隔离的作用,从而减小串扰。传统的PCB设计由于缺乏高速分析和仿真指导,信号的质量无法得到保证,而且大部分问题必须等到制版测试后才能发现。这大大降低了设计的效率,提高了成本,在激烈的市场竞争下显然是不利的。于是针对高速PCB设计,业界人士提出了一种新的设计思路,成为“自上而下”的设计方法,经过多方面的方针分析和优化,避免了绝大部分可能产生的问题,节省了大量的时间,确保满足工程预算,产生高质量的印制板,避免繁琐而高耗的测试检错等。利用差分线传输数字信号就是高速数字电路中控制破坏信号完整性因素的一项有效措施。在印制电路板(PCB抄板)上的差分线,等效于工作在准TEM模的差分的微波集成传输线对。其中,位于PCB顶层或底层的差分线等效于耦合微带线,位于多层PCB内层的差分线,等效于宽边耦合带状线。数字信号在差分线上传输时是奇模传输方式,即正负两路信号的相位差是180,而噪声以共模的方式在一对差分线上耦合出现,在接受器中正负两路的电压或电流相减,从而可以获得信号消除共模噪声。而差分线对的低压幅或电流驱动输出实现了高速集成低功耗的要求。

该文章版权归 smarteebit 所有。若有疑问,请联系 songmin2@https://www.doczj.com/doc/187220378.html,

高速数字设计的经典案例若干则

【摘要】 随着这些年半导体工艺突飞猛进的发展, “高速数字设计”对广大硬件工程师来说,已经不再是一 个陌生的词。从航空、雷达到汽车电子,从无线通信到有线接入,甚至在一些低端的嵌入式系统上,高 速数字电路都已经在大行其道。 目前行业内已经有不少关于高速数字电路理论的好文章, 笔者就不在这 上面掺和了。 本文着眼于理论和实际相结合, 所用的素材都来自笔者亲历过的案例, 相信活生生的事实, 比空洞的理论更有说服力,也希望能使入行不久的硬件工程师们得到他们想要的信息,今后少走弯路。 由于不会对理论作过多的阐述, 因此, 本文的阅读对象应该具有一点点高速数字设计的理论基础, 请知。 【关键词】 高速数字设计 高速数字电路 案例

1 信号完整性

什么词汇在高速数字设计中出现得最多?对了,SI(Signal Integrity),也就是信号完整性。信 号完整性问题的表现形式多种多样,主要有如下种类:

图 1 过冲(OVERSHOOT)

图 2 振铃(RING)

图 3 非单调性(NON MONOTONIC)

过冲: 当较快的信号沿驱动一段较长的走线, 而走线拓扑上又没有有效的匹配时, 往往会产生过冲。 过冲带来的问题主要是“1”电平高于接收端器件的输入最大电压值(VIHmax),或“0”电平低于接收端 器件的输入最小电压值(VILmin),这样可能给器件带来潜在的累积性伤害,缩短其工作寿命,从而影响 产品的长期稳定性。

Smarteebit

Page 1 of 17

集成电路设计 实验报告 时间:2011年12月

实验一原理图设计 一、实验目的 1.学会使用Unix操作系统 2.学会使用CADENCE的SCHEMA TIC COMPOSOR软件 二:实验内容 使用schematic软件,设计出D触发器,设置好参数。 二、实验步骤 1、在桌面上点击Xstart图标 2、在User name:一栏中填入用户名,在Host:中填入IP地址,在Password:一栏中填入 用户密码,在protocol:中选择telnet类型 3、点击菜单上的Run!,即可进入该用户unix界面 4、系统中用户名为“test9”,密码为test123456 5、在命令行中(提示符后,如:test22>)键入以下命令 icfb&↙(回车键),其中& 表示后台工作,调出Cadence软件。 出现的主窗口所示: 6、建立库(library):窗口分Library和Technology File两部分。Library部分有Name和Directory 两项,分别输入要建立的Library的名称和路径。如果只建立进行SPICE模拟的线路图,Technology部分选择Don’t need a techfile选项。如果在库中要创立掩模版或其它的物理数据(即要建立除了schematic外的一些view),则须选择Compile a new techfile(建立新的techfile)或Attach to an existing techfile(使用原有的techfile)。 7、建立单元文件(cell):在Library Name中选择存放新文件的库,在Cell Name中输 入名称,然后在Tool选项中选择Composer-Schematic工具(进行SPICE模拟),在View Name中就会自动填上相应的View Name—schematic。当然在Tool工具中还有很多别的

三一文库(https://www.doczj.com/doc/187220378.html,)/实习报告 印刷电路板设计实践报告 摘要 Protel是目前EDA行业中使用最方便,操作最快捷,人性化界面的辅助工具。在中国用得最多的EDA工具,电子专业的大学生在大学基本上都学过protel99se,所以学习资源也最广,公司在招聘新人的时候用Protel新人会很快上手。Altium声称中国有73%的工程师和80%的电子工程相关专业在校学生正在使用其所提供的解决方案,而目前正版率只有3%左右。利用自己画好的原理生成的PCB电路图用学校现有的资源设备把电路图转印到铜板上腐蚀生成可用的电路板。 第一章设计内容与设计要求 1.1设计内容 这次课程实践在与注重学生的实践动手能力,板子的功能自己定义,但是我们学过了单片机,于是我们就行制作一块与单片机有关的板子,以后或许会有用,也算是对学过的PCB和单片机知识的一次实际应用。 板子的功能介绍:在液晶显示屏上显示年月日,温度。当厨房着火事温度超过设定的额定值时,蜂鸣器会响起来(模拟报警

声),LED灯也会不停的闪烁(模拟应急灯),同时经单片机控制发送短信或打电话到不在家的主人的手机里,提醒主人家里着火了。当厨房的煤气泄漏时,MQ-2可燃气体传感器感应接收并反馈到单片机并启动接蜂鸣器和排风扇进行排风,并且也会打电话给不在家的主人告知家里的煤气泄漏了。主板由51单片机,GSM(全球移动通信系统)模块,1602液晶显示屏,时钟芯片但是DS1302,蜂鸣器,LED灯等组成,还有可燃气体MQ-2传感器。 1.2设计目的: (1)了解altiumdesigner绘图环境、各个功能模块、界面环境设置方法以及文件管理方法; (2)理解用altiumdesigner设计电子电路的基本思想; (3)掌握用altiumdesigner绘制电子电路原理图的基本方法; (4)掌握用altiumdesigner绘制电子电路PCB板的基本方。 (5)学会转印,腐蚀,钻孔,去油墨,完整的制作一块板子。 1.3设计要求: 要求学会并熟悉一款制图软件(我们选择的是AltiumDesigner),完成一份完整的原理图设计和PCB图,并且将其打印出来,然后转印并印刷制成一个成品板。 用altiumdesigner软件绘制一个简易厨房报警系统的电路图,自己设计原理图,有部分的元器件要是自己建库。先绘制出

目 录 34 1.10.3电容耦合和电感耦合的比值 (33) 1.10.2翻转磁耦合环 (30) 1.10.1共模电感和串扰的关系 (28) 1.10共模电感 (27) 1.9.2终端电阻之间的共模电容 (26) 1.9.1共模电容和串扰的关系 (25) 1.9共模电容 (25) 1.8.2图1.15的应用 (23) 1.8.1在响应曲线下测试覆盖面积 (23) 1.8估算衰减时间的一个更好的方法 (18) 1.7普通电感 (12) 1.6普通电容 (10) 1.5四种类型的电抗 (9) 1.4关于3-dB 和 频率均方根值 的注意点 (8) 1.3集中式系统和分布式系统 (7) 1.2时间和距离 (3) 1.1 频率和时间 (3) 第 1 章 基本原理 (1) 前言.............................................................................

前言 这本书是专门为电路设计工程师写的。它主要描述了模拟电路原理在高速数字电路设计中的分析应用。通过列举很多的实例,作者详细分析了一直困扰高速电路路设计工程师的铃流、串扰和辐射噪音等问题。 所有的这些原理都不是新发现的,这些东西在以前时间里大家都是口头相传,或者只是写成应用手册,这本书的作用就是把这些智慧收集起来,稍作整理。在我们大学的课程里面,这些内容都是没有相应课程的,因此,很多应用工程师在遇到这些问题的时候觉得很迷茫,不知该如何下手。我们这本书就叫做“黑宝书”,它告诉了大家在高速数字电路设计中遇到这些问题应该怎么去解决,他详细分析了这些问题产生的原因和过程。 对于低速数字电路设计,这本书没有什么用,因为低速电路中,'0'、'1' 都是很干净的。 但是在高速数字电路设计中,由于信号变化很快,这时候模拟电路中分析的那些影响会产生很大的作用,使得信号失真、变形,或者产生毛刺、串扰等,作为高速数字电路的设计者,必须知道这些原理。这本书就详细的解释了这些现象产生的原理以及他们在电路设计中的应用。 书本中的公式和例子对于那些没有受过专业模拟电路设计训练的读者也是有用的。在线性电路原理理论课程中只接受了第一年的培训的读者,也许能更好地掌握本书的内容。 第1章——第3章分别介绍了模拟电路术语、逻辑门高速特性和标准高速电路测量方法和技巧等内容。这三章内容构成了本书的核心,应该包括在任何高速逻辑设计的学习中。 其余章节,第4章——第12章,每一章都讲述了一个高速逻辑设计中的专门问题,我们可以按照自己的需要选择学习。 附录A收集了本书各部分的要点,列出了所提出的最重要的思想和概念。它可以作为我们进行系统设计时的一个检查要点(CHECKLIST),或者碰到问题时可作为本书内容的索引。 附录B详细给出了各种上升时间测量形式背后的数学假设。它有助于把本书的结论跟相关术语的标准及来源联系起来。 附录C是列举物理结构中的电阻、电容和电感计算的标准公式。这些公式已经在MathCad上实现并可以从作者处获得。

电子科技大学成都学院 (微电子技术系) 实验报告书 课程名称:电路原理图设计及Hspice 学号: 姓名: 教师: 年06月15日 实验一基本电路图的Hspice仿真 实验时间:同组人员: 一、实验目的 1.学习用Cadence软件画电路图。 2.用Cadence软件导出所需的电路仿真网表。 3.对反相器电路进行仿真,研究该反相器电路的特点。 二、实验仪器设备 Hspice软件、Cadence软件、服务器、电脑 三、实验原理和内容 激励源:直流源、交流小信号源。 瞬态源:正弦、脉冲、指数、分线段性和单频调频源等几种形式。 分析类型:分析类型语句由定义电路分析类型的描述语句和一些控制语句组成,如直流分析(.OP)、交流小信号分析(.AC)、瞬态分析(.TRAN)等分析语句,以及初始状态设置(.IC)、选择项设置(.OPTIONS)等控制语句。这类语句以一个“.”开头,故也称为点语句。其位置可以在标题语句之间的任何地方,习惯上写在电路描述语句之后。 基本原理:(1)当UI=UIL=0V时,UGS1=0,因此V1管截止,而此时|UGS2|> |UTP|,所以V2导通,且导通内阻很低,所以UO=UOH≈UDD,即输出电平. (2)当UI=UIH=UDD时,UGS1=UDD>UTN,V1导通,而UGS2=0<|UTP|,因此V2截止。此时UO=UOL≈0,即输出为低电平。可见,CMOS反相器实现了逻辑非的功能. 四、实验步骤

1.打开Cadence软件,画出CMOS反相器电路图,导出反相器的HSPICE网表文件。 2.修改网表,仿真出图。 3.修改网表,做电路的瞬态仿真,观察输出变化,观察波形,并做说明。 4.对5个首尾连接的反相器组成的振荡器进行波形仿真。 5.分析仿真结果,得出结论。 五、实验数据 输入输出仿真: 网表: * lab2c - simple inverter .options list node post .model pch pmos .model nch nmos *.tran 200p 20n .dc vin 0 5 1m sweep data=w .print v(1) v(2) .param wp=10u wn=10u .data w wp wn 10u 10u 20u 10u 40u 10u 40u 5u .enddata vcc vcc 0 5 vin in 0 2.5 *pulse .2 4.8 2n 1n 1n 5n 20n cload out 0 .75p m1 vcc in out vcc pch l=1u w=wp m2 out in 0 0 nch l=1u w=wn .alter vcc vcc 0 3 .end 图像: 瞬态仿真: 网表: * lab2c - simple inverter .options list node post .model pch pmos .model nch nmos .tran 200p 20n .print tran v(1) v(2) vcc vcc 0 5 vin in 0 2.5 pulse .2 4.8 2n 1n 1n 5n 20n cload out 0 .75p m1 vcc in out vcc pch l=1u w=20u

高速电路设计规则参考(初稿) 张工 2015/3/8 高速电路完整性分析: 信号完整性是指在电路设计中互连线引起的所有问题,它主要研究互连线的电气特性参数与数字信号的电压电流波形相互作用后,如何影响到产品性能的问题。主要表现在对时序的影响、信号振铃、信号反射、近端串扰、远端串扰、开关噪声、非单调性、地弹、电源反弹、衰减、容性负载、电磁辐射、电磁干扰等。(引用于博士对信号完整性的理解)同时,归根到底,信号失真源自于信号传输过程的阻抗变化,因此假如一个信号的传输途径处处阻抗匹配且均衡,这信号的质量可以很好保留,不过实际中不能完全做到,但可以通过注意这些问题从而是信号质量有所改善,另外在多次阻抗改变和跌落之后信号会出现信号振铃、信号反射、上冲以及下冲等现象,此时可以通过一些有效的方法避免。 以下将从信号完整性的层面出发,介绍以下一些高速电路的设计规则参考: 一、器件选型及布局 1电容选型 1.1不同容值电容搭配 通常情况下有经验的工程师都知道一般电源入口处都会搭配容量大小不一样的 电容进行去耦或储能,但经常一知半解,因为从理论计算,大小电容并联就是两 个电容的容值相加,没有什么作用。不过现实中由于制作工艺以及封装的不同, 不同容值的电容其ESL和ESR是不同的,其谐振频率也不同。 因此在信号频率小于其器件的谐振频率时电容表现出容性,当信号频率大于器件的 谐振频率时电容表现为感性,因此高速电路中大电容常常由于谐振频率较低,表现 出感性特性,此时电路中的电容将被大大削弱了去耦特性。因此通过搭配不同容值 的电容可以在较大范围内满足电路的需求。同时尽量选用小ESL的电容。

通常设计中可以通过搭配不同数量级的电容改善去耦效果。 1.2电容封装 同样容量的不同封装形式的电容其谐振频率也不同,通常小封装的电容等效串联电感更低,效串联电感基本相同电容有更低的等效串联电感。某型号陶瓷电容的ESL和ESR 测量值如下: 因此高速电路中尽量选用小封装的器件进行设计。 2电容的布局 2.1电容去耦半径和电容的摆放位置 有经验的工程师都会知道电容布局时小电容需要尽量靠近电源入口,大电容就可以放的远一点,这是因为电容对电源进行去耦时其存在一个去耦范围,即“去耦半径”。超过该电容的去耦半径时的其将起不到去耦半径。同时大容值的电容的去耦半径大,小电容的去耦半径小。例如某电路中0.001UF的陶瓷电容的去耦半径大概为2.4厘米。其去耦半径大小不仅与器件本身,同时还跟焊接的电路有关,不过起主导作用的是容值。 2.2降低EMI时电容的连线 随着工作频率升高,滤波器件的感抗和PCB线路感抗开始呈现,且频率越高感抗越大,对供电回路的纹波影响越明显,因此需要选用感抗小的小容量电容提供良好的去耦。同时还应缩短滤波电容两端到负载的电源与地的距离,尽可能将去耦电容和负载器件放置在同一层。为降低EMI,也应尽量减小电源线和地回路之间包围的面积。 以下图例都是说明如何设计良好的去耦电路拓扑结构和布线策略。

数字电路与系统设计实验报告 学院: 班级: 姓名:

实验一基本逻辑门电路实验 一、实验目的 1、掌握TTL与非门、与或非门和异或门输入与输出之间的逻辑关系。 2、熟悉TTL中、小规模集成电路的外型、管脚和使用方法。 二、实验设备 1、二输入四与非门74LS00 1片 2、二输入四或非门74LS02 1片 3、二输入四异或门74LS86 1片 三、实验内容 1、测试二输入四与非门74LS00一个与非门的输入和输出之间的逻辑关系。 2、测试二输入四或非门74LS02一个或非门的输入和输出之间的逻辑关系。 3、测试二输入四异或门74LS86一个异或门的输入和输出之间的逻辑关系。 四、实验方法 1、将器件的引脚7与实验台的“地(GND)”连接,将器件的引脚14与实验台的十5V连接。 2、用实验台的电平开关输出作为被测器件的输入。拨动开关,则改变器件的输入电平。 3、将被测器件的输出引脚与实验台上的电平指示灯(LED)连接。指示灯亮表示输出低电平(逻辑为0),指示灯灭表示输出高电平(逻辑为1)。 五、实验过程 1、测试74LS00逻辑关系 (1)接线图(图中K1、K2接电平开关输出端,LED0是电平指示灯) (2)真值表 2、测试74LS02逻辑关系

(1)接线图 (2)真值表 3、测试74LS86逻辑关系接线图 (1)接线图 (2)真值表 六、实验结论与体会 实验是要求实践能力的。在做实验的整个过程中,我们首先要学会独立思考,出现问题按照老师所给的步骤逐步检查,一般会检查处问题所在。实在检查不出来,可以请老师和同学帮忙。

实验二逻辑门控制电路实验 一、实验目的 1、掌握基本逻辑门的功能及验证方法。 2、掌握逻辑门多余输入端的处理方法。 3、学习分析基本的逻辑门电路的工作原理。 二、实验设备 1、基于CPLD的数字电路实验系统。 2、计算机。 三、实验内容 1、用与非门和异或门安装给定的电路。 2、检验它的真值表,说明其功能。 四、实验方法 按电路图在Quartus II上搭建电路,编译,下载到实验板上进行验证。 五、实验过程 1、用3个三输入端与非门IC芯片74LS10安装如图所示的电路。 从实验台上的时钟脉冲输出端口选择两个不同频率(约7khz和14khz)的脉冲信号分别加到X0和X1端。对应B和S端数字信号的所有可能组合,观察并画出输出端的波形,并由此得出S和B(及/B)的功能。 2、实验得真值表

电子技术课程设计 题目: 班级: 姓名: 合作者:

数字电子钟计时系统 一、设计要求 用中、小规模集成电路设计一台能显示时、分、秒的数字电子钟,基本要求如下: 1、采用LED显示累计时间“时”、“分”、“秒”。 2、具有校时功能。 二、设计方案 数字电子钟主要由振荡器、分频器、计数器、译码器、显示器等几部分组成,其整体框图为 其中,秒信号发生器为:

由石英晶体发出32768Hz的振荡信号经过分频器,即CD4060——14级串行二进制计数器/分频器和振荡器,输出2Hz 的振荡信号传入D触发器,经过2分频变为秒信号输出。 校时电路为: 当K1开启时,与非门一端为秒信号另一端为高电位,输出即为秒信号秒计数器正常工作,当K1闭合,秒信号输出总为0,实现秒暂停。 当K2/K3开启时,分信号/时信号输入由秒计数器输出信号及高电平决定,所以输出信号即为分信号/时信号,当K2/K3闭合时,秒信号决定分信号/时信号输出,分信号/时信号输出与秒信号频率一致, 以实现分信号/时信号的加速校时。 秒、分计数器——60进制

首先,调节CD4029的使能端,使其为十进制加法计数器。将输入信号脉冲输入第一个 计数器(个位计数器)计十个数之后将,进位输出输给下一个计数器(十位计数器)的进位 输入实现十秒计数。当计数器的Q1,Q2输出均为1时经过与门电路,输出高电平,作为分 脉冲或时脉冲并同时使两计数器置零。 时计数器——24进制 时脉冲 首先,调节CD4029的使能端,使其为十进制加法计数器。将输入信号脉冲输入第一个 计数器(个位计数器)计十个数之后将,进位输出输给下一个计数器(十位计数器)的进位 输入实现十秒计数。当十位计数器Q1和个位计数器Q2输出均为1时经过与门电路,输出 高电平使两计数器置零。 译码显示电路

关于高速电路设计的几个热门(困惑)观点这一期和大家聊一聊高速电路设计中常见的几个设计观点,当然,对于这一部分可能会有一些工程师有不一样的观点,毕竟每一个人的理解都也不太一样,这也是就本人做过的或者了解到一些其他比较优秀公司的经验和设计习惯做这次分享。主要是总结高速线布线的一些情况。 1、关于松耦合还是紧耦合。只要了解高速电路的工程师都知道,差分线有紧耦合和松耦合之分,很多工程师在此都会纠结。一般SI工程师都会说这要看情况,我也会这么讲。但是从很多产品经验来看,对于差分走线,尽可能使用紧耦合会比较好。但是也有例外的情况,如果整个链路的布线有比较长一段距离无法达到紧耦合的话,这时就最好使用松耦合。图1显示了一对高速差分走线,采用了松耦合。由于最小间隔距离要求(受到SMA连接器的结构限制),在器件下无法采用紧耦合。如果内层采用紧耦合,信号会从紧耦合瞬变成松耦合,这会引起阻抗不连续。 图1. 松耦合和地参考实例 2、关于使用微带线还是带状线。通常,PCB布线分为微带线和带状线。很多资料都在讨论高速信号到底是使用微带线还是带状线,个人认为,布线在哪一层都是可以的,根据需要,如果布线长度较长,那么建议布线在内层(带状线)比较好(损耗和串扰都非常有优势),当然,内层会使信号换层,增加via。带状线还有将信号与其他噪声源相屏蔽的优势。

3、关于布线为圆弧角。现在设计工程师经常流传说高速信号线在设计时,都要使用圆角布线,其实不一定,我们之前做过很多实验,对于不超过10Gbps的信号设计,45°角布线完全可以满足设计要求(SI/EMC),当然,建议不要使用90°拐角,这会带来阻抗不连续性。当然,要是你还是不相信,那么你就去绕圆弧线吧。 4、关于跨分割。大家在学习高速电路设计的时候,不要让高速信号跨过平面分割层。当然,谁又不想有一个完整的平面,但是,当你遇到HDI板的时候,就会遇到不得不跨分割的情况,那么,请大胆的跨吧。记得让布线尽快的跨过gap区域(如图2),切忌在gap上绕线(如图3);如果可以,请就近加一颗合适的电容(猜一猜为什么要一个电容?)。(记住,这是在逼不得已的情况再跨,切记不要胡乱的来回跨,毕竟跨分割会增加返回通路,导致布线电感增加,阻抗变化,进而影响信号完整性) 图2 跨分割平面

电工电子综合试验——数字计时器实验报告 学号: 姓名: 学院: 专业:通信工程

目录 一,实验目的及要求 二,设计容简介 四,电路工作原理简述 三,设计电路总体原理框图五,各单元电路原理及逻辑设计 1. 脉冲发生电路 2. 计时电路和显示电路 3. 报时电路 4. 较分电路 六引脚图及真值表

七收获体会及建议 八设计参考资料 一,实验目的及要求 1,掌握常见集成电路实现单元电路的设计过程。 2,了解各单元再次组合新单元的方法。 3,应用所学知识设计可以实现00’00”—59’59”的可整点报时的数字计时器 二,设计容简介: 1,设计实现信号源的单元电路。( KHz F Hz F Hz F Hz F1 4 , 500 3 , 2 2 , 1 1≈ ≈ ≈ ≈ ) 2,设计实现00’00”—59’59”计时器单元电路。 3,设计实现快速校分单元电路。含防抖动电路(开关k1,频率F2,校分时秒计时器停止)。4,加入任意时刻复位单元电路(开关K2)。 5,设计实现整点报时单元电路(产生59’53”,59’55”,59’57”,三低音频率F3,59’59”一高音频率F4)。 三,设计电路总体原理框图 设计框图: 四,电路工作原理简述 电路由振荡器电路、分频器、计数器、译码器、显示器、校时电路和报时电路组成。振荡器产生的脉冲信号经过十二级分频器作为秒脉冲,秒脉冲送入计数器,计数器通过“时”、“分”、“秒”译码器显示时间,将分秒计时器分开,加入快速校分电路与防抖动电路,并控制秒计

时器停止工作。较分电路实现对“分”上数值的控制,而不受秒十位是否进位的影响,在60进制控制上加入任意时刻复位电路。报时电路通过1kHz或2kHz的信号和要报时的时间信号进行“与”的运算来实现的顶点报时的,通过两个不同频率的脉冲信号使得在不同的时间发出不同的声响。 五,各单元电路原理及逻辑设计 (1)脉冲发生电路 脉冲信号发生电路是危机时期提供技术脉冲,此次实验要求产生1HZ的脉冲信号。用NE555集成电路和CD4040构成。555定时器用来构成多谐振荡器,CD4040产生几种频率为后面电路使用。 实验电路如下(自激多谐振荡电路,周期矩形波发生电路) 震荡周期T=0.695(R1+2*R2)C,其中R1=1KΩ,R2=3KΩ,C=0.047uf,计算T=228.67*10-6 s ,f=4373.4Hz产生的脉冲频率为4KHz,脉冲信号发生电路 和CD4040连接成如图所示的电路,则从Q12输出端可以得到212分频信号F1,即1Hz的信号,Q11可以得到F2即2Hz的信号提供给D触发器CP和校分信号,Q3输出分频信号500Hz,Q2输出1KHz提供给报时电路 二,秒计时电路 应用CD4518及74LS00可以设计该电路,CD4518是异步清零,所以在进行分和秒十位计数的时候,需要进行清零,而在个位计数的时候不需要清零。所以Cr2=2QcQb,Cr4=4Qc4QB。当秒个位为1001时,秒十位要实现进位,此时需要EN2=1Qd,同理分的个位时钟EN3=2Qc,分十位时钟端EN4=3Qd。因此,六十进制计数器逻辑电路如下图所示

集成电路版图设计实习报告 学院:电气与控制工程学院 专业班级:微电子科学与工程1101班 姓名:孙召洋 学号:1106080113

一、实验要求: 1. 熟悉Cadence的工作环境。 2. 能够熟练使用Cadence工具设计反相器,与非门等基本电路。 3. 熟记Cadence中的快捷操作。比如说“W”是连线的快捷键。 4. 能够看懂其他人所画的原理图以及仿真结果,并进行分析等。 二、实验步骤: 1、使用用户名和密码登陆入服务器,右击桌面,在弹出菜单中单击open Terminal;在弹出的终端中键入Unix命令icfb&然后按回车启动Cadence。Cadence启动完成后,关闭提示信息。设计项目的建立 2、点击Tools-Library Manager启动设计库管理软件。点击File-New-Library 新建设计库文件。在弹出的菜单项中输入你的设计库的名称,比如My Design,点击OK。选择关联的工艺库文件,点击OK。在弹出的菜单中的Technology Library下拉菜单中选择需要的工艺库,然后单击OK。 3、设计的项目库文件建立完成,然后我们在这个项目库的基础上建立其子项目。点击选择My Design,然后点击File-New-Cell View。输入子项目的名称及子项目的类型,这设计版图之前我们假定先设计原理图:所以我们选择Composer-Schematic,然后点击OK。 4、进入原理图编辑平台,原理图设计,输入器件:点击Instance按键或快捷键I插入器件。查找所需要的器件类型-点击Browse-tsmc35mm-pch5点击Close。更改器件参数,主要是宽和长。点击Hide,在编辑作业面上点击插入刚才设定的器件。如果想改参数器件,点击选择该器件,然后按Q,可以修改参数器件使用同样的方法输入Nmos,工艺库中叫nch5. 点击Wire(narrow)手动连线。完成连线后,输入电源标志和地标志:在analogLib库中选择VDD和GND,输入电源线标示符。接输入输出标示脚:按快捷键P,输入引脚名称in, Direction选择input,点击Hide,并且和输入线连接起来。同理设置输出引脚Out。 5、版图初步建立新的Cell,点击File-New-Cell View 还是建立名称为inv的版图编辑文件,Tool选择Virtuoso版图编辑软件,点击OK,关闭信息提示框。进入版图编辑环境根据之前仿真所得宽长比和反相器inv或与非门NAND的原理图画出反相器inv或与非门NAND的IC版图; 6、完成后使用版图验证系统进行DRC(设计规则检查)。 三、实验设计规则: 1、Linux常用的文件和目录命令: cd //用于切换子目录 pwd//用于显示当前工作子目录 ls//用于列出当前子目录下的所有内容清单 rm//用于删除文件 touch//用于建立文件或是更新文件的修改日期 mkdir//用于建立一个或者几个子目录

咼速数字电路设计技术探讨 宏碁计算机桌上型计算机研展处工程师■苏家弘 关于高速数字电路的电气特性,设计重点大略可分为三项:正时(Timing )、信号质量(Signal Quality )与电磁干扰(EMI )的控制。在正时方面,由于数字电路大多依据频率信号来做信号间的同步工作,因此频率本身的准确度与各信号间的时间差都需配合才能正确运作。在高速的世界 里,时间失之毫厘差以千里,严格的控制线长,基版材质等都成为重要的工作。在信号质量方面, 高速电路已不能用传统的电路学来解释。随着频率变高,信号线长已逐渐逼近电磁波长,此时诸 如传输线原理(Tra nsmission Line )的分布电路(Distribute circuit )的概念,需加以引进才能解释并改进信号量测时所看到的缺陷。在电磁干扰方面,则需防范电路板的电磁波过强而干扰到 其它的电器用品。本文将依序介绍这些设计上的重点。 正时(Timing) 如图1,来源(source )芯片(A)发岀一个频率长度(T)的信号a给目标(target)芯片B< 对A的内部机制而言,他发岀或收起信号a是在频率上升一段时间之后,这就是有效持续时间valid delay )。在最坏的情形下,a信号只能持续T-(Tmax-Tmin)的时间。而B芯片,必须在这段持续时间内读入a,那就必须在频率B上升之前,a已存在一段设置时间(setup time ),在上升之后,再持续一段保存时间( hold time )。 要考虑的有以下几点: 1. A与B所收到的频率信号CLK_A与CLK_B是否不同步?亦即是否有频率歪斜( clock skew ) 的现象。 2. 信号a从A传至B所用的传导时间(flight time )需要多少? 3. 频率本身的不稳度(clock jitter )有多少?我们所设计的设置时间与保存时间能否容忍这个误差?传输速度的计算就1、2两点,我们都必须计算信号在电路板上的传导速度才行,但这又和许多系数息息相关, 包括导体(通常为铜箔)的厚度与宽度,基板厚度与其材质的电介系数( permittivity )。尤其以 基板的电介系数的影响最大:一般而言,传导速度与基板电介系数的平方根成反比。 以常见的FR-4而言,其电介系数随着频率而改变,其公式如下: £ =4.97-0.257log 但须注意,此处的参数f不是频率的频率,而是信号在傅立叶转换后所占的频宽。 以Pentium n的频率信号为例,其上升或下降缘速率典型值约在2V/ns,对2.5V的频率信号而言, 从10%到90%的信号水平约需1ns的时间,依公式: BW=0.35/T 可知频宽为350MHz。代入公式可知电介系数大约是 4.57。 如果传导的是两片无穷大的导体所组成的完美传输线,那么传输的速度应为亦即 1.38xm/sec, 或者5.43 in ch/ns。

中山大学数字电路与逻辑设计实验报告 院系信息科学与技术学院学号 专业计算机科学类实验人 3、实验题目:AU(Arithmetic Unit,算术单元)设计。 实验内容: 设计一个半加半减器,输入为 S、A、B,其中S为功能选择口。当S=0时,输出A+B及进位;当S=1时,输出A-B及借位。 S 输入1 输入2 输出Y 进/借位Cn 0 A B A+B 进位 1 A B A-B 借位 利用三种方法实现。 (1)利用卡诺图简化后只使用门电路实现。 (2)使用74LS138实现。 (3)使用74LS151实现,可分两次单独记录和/差结果、进位借位结果或使用两块74LS151实现。 实验分析: 真值表 S A B Y Cn 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 0 0 1 0 1 1 1 1 1 0 1 0 1 1 1 0 0 卡诺图: S AB 0 1 通过卡诺图可得:Y=A B+A B 00 01 11 100 0 1 1 0 0 1 1

S AB 0 1 00 Cn=AB S +A BS 01 =(A S +A S)B 11 10 实验设计: (1)利用门电路实现。 ①利用74LS197的八进制输出端Q1、Q2、Q3作为B 、A 、S 的输入。 ②用异或门74LS86实现输出Y. ③用74LS86实现A ⊕B ,再用74LS08与B 实现与门。 (2)利用74LS138实现 ①将74LS197的Q3、Q2、Q1作为74LS138的S2、S1、S0输入,G2A 、G2B 接低电平,G1接高电平。 ②将74LS138的Y1、Y5、Y2、Y6利用74LS20实现与非门作为输出Y 。 ③ 将74LS138的Y3、Y5利用74LS00实现与非门作为输出Cn 。 0 0 0 1 1 0 0 0

组合逻辑电路设计实验报告 1.实验题目 组合电路逻辑设计一: ①用卡诺图设计8421码转换为格雷码的转换电路。 ②用74LS197产生连续的8421码,并接入转换电路。 ③记录输入输出所有信号的波形。 组合电路逻辑设计二: ①用卡诺图设计BCD码转换为显示七段码的转换电路。 ②用74LS197产生连续的8421码,并接入转换电路。 ③把转换后的七段码送入共阴极数码管,记录显示的效果。 2.实验目的 (1)学习熟练运用卡诺图由真值表化简得出表达式 (2)熟悉了解74LS197元件的性质及其使用 3.程序设计 格雷码转化: 真值表如下:

卡诺图: 1 010100D D D D D D G ⊕=+= 2 121211D D D D D D G ⊕=+=

3232322D D D D D D G ⊕=+= 33D G = 电路原理图如下: 七段码显示: 真值表如下: 卡诺图:

2031020231a D D D D D D D D D D S ⊕++=+++= 10210102b D D D D D D D D S ⊕+=++= 201c D D D S ++= 2020101213d D D D D D D D D D D S ++++= 2001e D D D D S +=

2021013f D D D D D D D S +++= 2101213g D D D D D D D S +++= 01213g D D D D D S +⊕+= 电路原理图如下:

4.程序运行与测试 格雷码转化: 逻辑分析仪显示波形:

《高速电路板设计与仿真》课程教学大纲 课程代码:030442003 课程英文名称:High Speed Printed Circuit Board Design and Emulation 课程类别:专业基础课 课程性质:选修 适用专业:电子科学与技术 课程总学时:40 讲课:40 实验:0 上机:0 大纲编写(修订)时间:2011.7 一、大纲使用说明 (一)课程的地位及教学目标 本课程是电子科学与技术专业的专业任选课, 属于专业技术基础课,是一门重要的实践课程。通过本课程的学习,学生能够利用先进的高端软件设计高速电路板,绘制出具有实际意义的原理图和印刷电路板图,具有对设计中的信号完整性、电磁兼容性、电源完整性等问题的分析能力,熟悉一定的电子工艺和印刷电路板的布局布线知识,为今后从事高端设计工作打下一定的基础。 (二)知识、能力及技能方面的基本要求 在知识方面,要求学生具有初步的半导体工艺、印制电路、芯片封装等方面的知识,还要了解信号完整性、电磁兼容性、电源完整性等方面的基本概念,如此才能设计出高质量的高速PCB。在能力方面,要求学生具备一些计算机方面的操作技能。 (三)实施说明 1.教学内容:包括原理图设计、PCB设计、高速信号仿真三部分,其中PCB设计为重点内容。应突出高速和高质量PCB的讲解,以适应高端设计要求。讲课要理论联系实际,设计具有实际意义的原理图和印刷电路板图,而不只是空讲理论知识。 2.教学方法:采用启发式教学,提高学生分析问题和解决问题的能力。鼓励学生通过实践和自学获取知识,培养学生的自学能力,调动学生自行设计的学习积极性和创新能力。 3.教学手段:本课程属于技术基础课,在教学中可采用电子教案、CAI课件及多媒体教学系统等先进教学手段,以确保在有限的学时内,全面、高质量地完成课程教学任务。 4.大纲实施时应贯彻学院工程训练与工程教育相结合的特点,注重学生的能力培养和专业素质的提高,尤其是培养学生的实际动手设计和操作的能力。 (四)对先修课的要求 本课程的先修课为电路、模拟电子电路、数字电子电路、计算机基础知识。 (五)对习题课、实践环节的要求 每次课后留有一定量的操作练习,要求学生课后在自己的电脑上学习操作。本课程无实验。 (六)课程考核方式 1.考核方式:考查 2.考核目标:考核学生是否掌握了软件的基本操作方法,重点考核学生的原理图绘制和印刷电路板的设计能力,所设计的项目是否具有实际意义。 3.成绩构成:本课程的总成绩由两部分组成:平时成绩(包括平时自行练习、出勤等)占20%,期末验收成绩(以综合作业完成情况给出成绩)占80%。按优、良、中、及格、不及格五级给出最后成绩。 (七)参考书目 《Cadence SPB 15.7工程实例入门》于争著,电子工业出版社, 2010.5.

电子电路设计实验报告 电子线路专题实验Ⅱ 一、实验要求: 1. 认真阅读学习系统线路及相关资料 2. 将键盘阵列定义为0. 1. 2------ E. F,编程实现将键盘输入内容显示在LCD显示器上。 3. 编程实现将日历、时钟显示在LED显示屏上(注意仔细阅读PCF8563资料),日历、时钟轮回显示。 4. 利用D/A转换通道(下行通道)实现锯齿波发生器;输出(1~5V)固定电压转换成(4~20mA)电流。 5. 利用A/D转换通道(上行通道)实现数据采集,将采集信号显示在LED屏上。程序要求分别具有平均值滤波、中值滤波和滑动滤波功能。 6. 将按键阵列定义成与16个语音段对应,编写程序,实现按键播放不同的语音段。 二、实验设计思路: 本次实验用c语言实现,主要包括LCD,LED,AD,DA,日历芯片,测温传感芯片。受到嵌入式系统实验的启发,将LCD,LED,I2C总线协议,键盘扫描模块接口写成一个文件库(放在library文件夹下),尽量做到调用时与底层硬件无关。通过调用库文件中的函数,实现代码的重用性。键盘,LCD的代码由于与嵌入式实验具有相通之处,因此可将高层的函数(与底层硬件无关的函数)方便地移植过来。 三、实验设计: 1.矩阵键盘扫描模块 4×4的矩阵键盘,通过扫描可得到按下键的行列值,将行列值转换为相应的对应数字0~F。函数GetKey()实现获得按键的键值。对于键盘模块对于对按键的键值识别主要是通过两次扫描而取得。对于第一次扫描,给四行键全部赋予1,然后读回键盘值,对于第二次扫描,逐行为键盘送1,每次送1后再读回键盘值,若非零,说明此行有键按下,最终确定键值。 通过调用GetKey函数构造GetChar()函数,实现获取键盘字符(’0’~’F’)的功能。

OrCAD/PSpice电路分析 实 习 报 告 学院:电气信息工程学院 专业:电子信息工程 班级: 姓名: 学号: 指导老师:

目录 一、实习目的 二、实习的基本要求 三、实习方式 四、 OrCAD简介 五、 OrCAD软件系统的功能及特点 六、实习内容 1. 电路图绘制实例 2. 电路图的绘制 3. 电路特性分析 4. 实例特性分析 七、实习心得

一、实习目的 《OrCAD/PSpice电路分析》是一门实践性很强的课程。ORCAD是由ORCAD公司于八十年代末推出的EDA 软件,它是世界上使用最广的EDA软件,每天都有上百万的电子工程师在使用它,相对于其它EDA软件而言,它的功能也是最强大的。通过实训,使学生能够熟练掌握该软件的基本功能(绘制电路图、创建元器件、创建封装图、合理布局布线、设置障碍物、PCB后续处理等),能使用该软件设计出具有一定专业水平的PCB板。 1.学会安装OrCAD软件,了解并熟悉使用OrCAD PSpice软件系统。 2.学会在Capture中创建电路并运行出指定分析类型及仿真类型。 3.掌握运行仿真结果的方法,并学会分析数据及图形。 4.了解电路一些基本原件的使用方法。 5此次实习的目的不仅让大家如何使用Capture的绘图页编辑程序同时也增强大家的动手能力和实践能力。

二、实习的基本要求 1、这是对本期所学ORCAD知识进行的一次全面的演练,本次实习训需要用到ORCAD的许多基础知识和操作技能。 2、熟悉OrCAD软件的正确应用,绘制相应阴的原理图。 3、爱护公物,不准乱动实习场所的设备,护计算机房的清洁卫生,遵守机房规章制度。 4、实习期间,严格按学校的作习时间进行实习,不准迟到早退。 5、实习训结束后,每位同学除上交本次实训成果以外,还要写出一份实训报告。 三、实习方式 1、听取专业人员的讲解。 2、查阅相关资料。 3、上机操作。 四、OrCAD简介 OrCAD Capture (以下以Capture代称)是一款基于?操作环境下的电路设计工具。利用Capture,能够实现绘制电路原理图以