ARM920T的CP15协处理器

ARM920T的MMU和Cache都集成在CP15协处理器中,MMU和Cache的联系非常密切,本节首先从总体上介绍MMU、Cache和CPU核是如何协同工作的,后面两节分别讲解MMU和Cache的细节。三星公司的S3C2410是一种很常见的采用ARM920T的芯片,涉及到具体的芯片时我们以S3C2410为例。

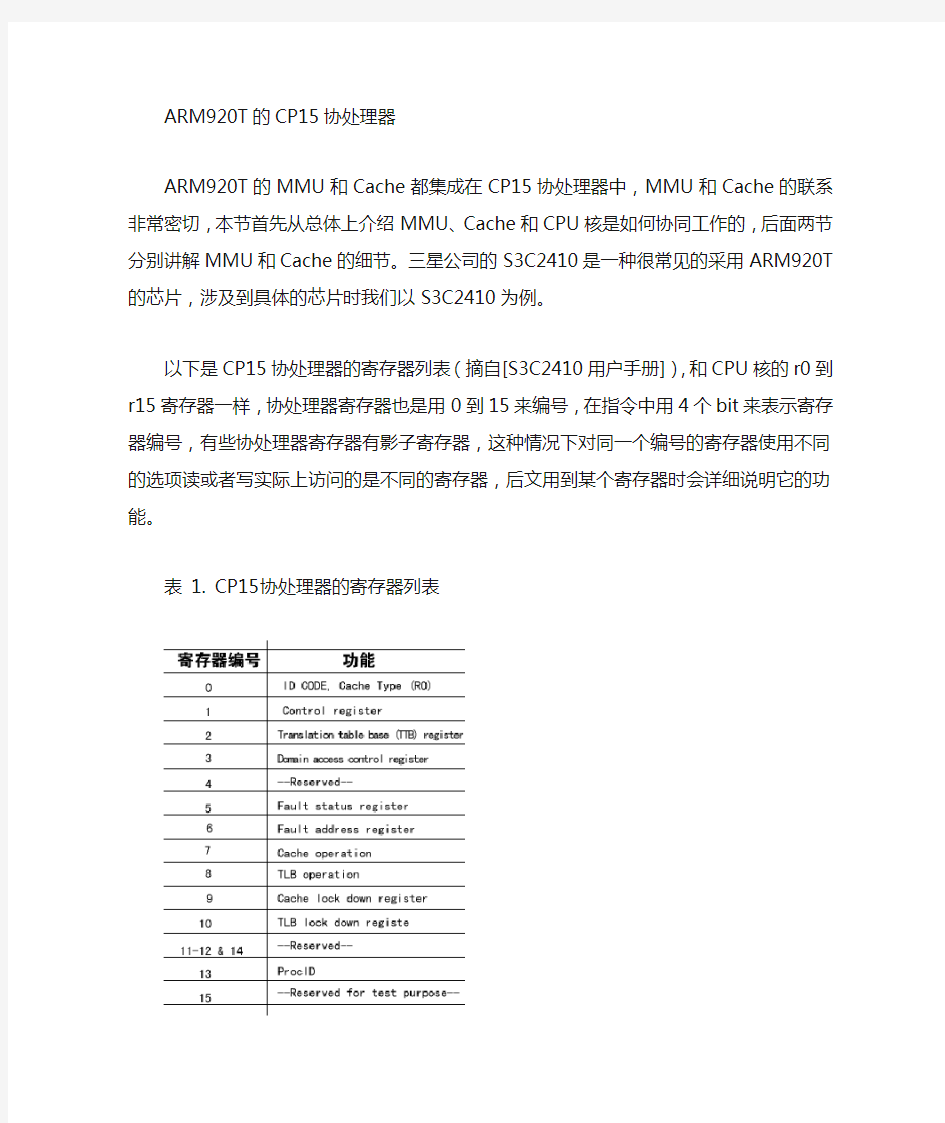

以下是CP15协处理器的寄存器列表(摘自[S3C2410用户手册]),和CPU核的r0到r15寄存器一样,协处理器寄存器也是用0到15来编号,在指令中用4个bit来表示寄存器编号,有些协处理器寄存器有影子寄存器,这种情况下对同一个编号的寄存器使用不同的选项读或者写实际上访问的是不同的寄存器,后文用到某个寄存器时会详细说明它的功能。

表1. CP15协处理器的寄存器列表

对CP15协处理器的操作使用mcr和mrc两条协处理器指令,这两条指令的记法是从后往前看:mcr是把r(CPU核寄存器)中的数据传送到c(协处理器寄存器)中,mrc则是把c(协处理器寄存器)中的数据传送到r(CPU核寄存器)中。对CP15协处理器的所有操作都是通过CPU核寄存器和CP15寄存器之间交换数据来完成的。下图是协处理器的指令格式(摘自[S3C2410用户手册])。

图8. 协处理器指令格式

和其它ARM指令一样,Cond是条件码,bit 20是L位,表示该指令是读还是写,如果L=1就表示Load,从外面读到CPU核中,也就是mrc指令,如果L=0就表示Store,也就是mcr指令。[11:8]这四个位是协处理器编号,CP15的编号是15,因此是4个1。CRn是CP15寄存器编号,Rd是CPU核寄存器编号,各占4个位。对于CP15协处理器,规定opcode1应该为0,opcode2和CRm是指令的选项,具体含义取决于不同的寄存器。

虽然这里介绍了协处理器的寄存器编号和相关指令,但读者只需了解对协处理器是这样进行操作的就可以了,我们的重点是讲解MMU和Cache的基本概念,具体各种操作的指令该怎么写可以参考[S3C2410用户手册]。

MMU是如何把VA映射成PA的呢?从图4 “进程地址空间是独立的”来看,好像是有一张VA转PA的表,给一个VA查表就可以查到PA,实际上并不是这么简单,通常要有一个多级的查表过程,对于ARM体系结构是两级查表,对于一些64位体系结构则需要更多级。看下面的图示。

图9. Translation Table Walk

首先将32位的VA[3]分成三段,前两段[31:20]和[19:12]作为两次查表的索引,第三段[11:0]作为页内的偏移。查表的步骤如下:

1 CP15协处理器的TTB寄存器(看看表1 “CP15协处理器的寄存器列表”中这是第几个寄存器?)中保存着第一级页表(Translation Table)的基地址,这个基地址指的是PA,也就是说页表是直接按这个地址存在物理内存中的。

2 以TTB中的内容为基地址,以VA[31:20]为索引在表中查出一项(想一下这个表中一共有多少项?),这个表项中保存着第二级页表(Coarse Page Table)的基地址,同样是物理地址,也就是说第二级页表也是直接按这个地址存在物理内存中的。

3 以VA[19:12]为索引在第二级页表中查出一项(想一下这个表中一共有多少项?),这个表项中就保存着物理页面的基地址,先前我们说虚拟内存管理是以页为单位的,一个虚拟内存的页映射到一个物理内存的页框,从这里就可以得到印证,因为查表是以页为单位来查的。

4 有了物理页面的基地址之后,加上VA[11:0]这个偏移量就可以取出相应地址上的数据(想一下一个页是多少字节?)。

这个过程称为Translation Table Walk,Walk这个词用得非常形象。从TTB走到一级页表,又走到二级页表,又走到物理页面,一次寻址其实是三次访问物理内存。注意这个“走”的过程完全是硬件做的,每次CPU寻址时MMU就自动完成以上四步,不需要编写指令指示MMU去做,前提是操作系统要维护页表项的正确性,每次分配内存时填写相应的页表项,每次释放内存时清除相应的页表项,在必要的时候分配或释放整个页表。

有了以上基本概念,我们来看CPU访问内存时的硬件操作顺序(摘自[ARM参考手册])。

图10. CPU访问内存时的硬件操作顺序

我们以CPU读内存为例解释一下图中的步骤,各步骤在图中有对应的标号。

1 CPU核(图中的“ARM”框)发出VA请求读数据,TLB(Translation Lookaside Buffer)接收到该地址。TLB是MMU中的一块高速缓存(也是一种Cache),它缓存最近查找过的VA 对应的页表项,如果TLB里缓存了当前VA的页表项就不必做Translation Table Walk了,否则去物理内存中读出页表项保存在TLB中,TLB缓存可以减少访问物理内存的次数。

2 页表项中不仅保存着物理页面的基地址,还保存着权限位和是否允许Cache的标志。MMU首先检查权限位,如果没有访问权限,就引发一个异常给CPU核。然后检查是否允许Cache,如果允许Cache就启用Cache和CPU核互操作,图中的“C, B bits”可以理解为选通线,后面再详细解释这两个位的作用。

3 如果不允许Cache,则直接发出PA从物理内存中读取数据到CPU核。

4 如果允许Cache,则以VA为索引到Cache中查找是否缓存了要读取的数据,如果Cache 中已经缓存了该数据(称为Cache Hit)则直接返回给CPU核,如果Cache中没有缓存该数据(称为Cache Miss),则发出PA从物理内存中读取数据并缓存到Cache中,同时返回给CPU核。然而Cache并不是只取CPU核所要的数据,而是把相邻的数据都取上来缓存,这称为一个Cache Line。ARM920T的Cache Line是32字节,例如CPU核要读取地址0x134-0x137的4字节数据,Cache会把地址0x120-0x13f(对齐到32字节地址边界)的32字节都取上来缓存。

ARM926EJ-S/ARM920T 协处理器CP14, CP15详解

ARM 微处理器可支持多达16 个协处理器,用于各种协处理操作,在程序执行的过程中,每个协处理器只执行针对自身的协处理指令,忽略ARM 处理器和其他协处理器的指令。ARM 的协处理器指令主要用于ARM 处理器初始化ARM 协处理器的数据处理操作,以及在ARM 处理器的寄存器和协处理器的寄存器之间传送数据,和在ARM 协处理器的寄存器和存储器之间传送数据。ARM 协处理器指令包括以下 5 条:

—CDP 协处理器数操作指令

—LDC 协处理器数据加载指令

—STC 协处理器数据存储指令

—MCR ARM 处理器寄存器到协处理器寄存器的数据传送指令

—MRC 协处理器寄存器到ARM 处理器寄存器的数据传送指令

1、CDP 指令

CDP 指令的格式为:

CDP{条件} 协处理器编码,协处理器操作码1,目的寄存器,源寄存器1,源寄存器2,协处理器操作码2。CDP 指令用于ARM 处理器通知ARM 协处理器执行特定的操作,若协处理器不能成功完成特定的操作,则产生未定义指令异常。其中协处理器操作码 1 和协处理器操作码2 为协处理器将要执行的操作,目的寄存器和源寄存器均为协处理器的寄存器,指令不涉及ARM 处理器的寄存器和存储器。

指令示例:

CDP P3 ,2 ,C12 ,C10 ,C3 ,4 ;该指令完成协处理器P3 的初始化

2、LDC 指令

LDC 指令的格式为:

LDC{条件}{L} 协处理器编码,目的寄存器,[源寄存器]

LDC 指令用于将源寄存器所指向的存储器中的字数据传送到目的寄存器中,若协处理器不能成功完成传送操作,则产生未定义指令异常。其中,{L}选项表示指令为长读取操作,如用于双精度数据的传输。

指令示例:

LDC P3 ,C4 ,[R0] ;将ARM 处理器的寄存器R0 所指向的存储器中的字数据传送到协处理器P3 的寄存器C4 中。

3、STC 指令

STC 指令的格式为:

STC{条件}{L} 协处理器编码,源寄存器,[目的寄存器]

STC 指令用于将源寄存器中的字数据传送到目的寄存器所指向的存储器中,若协处理器不能成功完成传送操作,则产生未定义指令异常。其中,{L}选项表示指令为长读取操作,如用于双精度数据的传输。

指令示例:

STC P3 ,C4 ,[R0] ;将协处理器P3 的寄存器C4 中的字数据传送到ARM 处理器的寄存器R0 所指向的存储器中。

4、MCR 指令

MCR 指令的格式为:

MCR{条件} 协处理器编码,协处理器操作码1,源寄存器,目的寄存器1,目的寄存器2,协处理器操作码2。

MCR 指令用于将ARM 处理器寄存器中的数据传送到协处理器寄存器中,若协处理器不能成功完成操作,则产生未定义指令异常。其中协处理器操作码1 和协处理器操作码2 为协处理器将要执行的操作,源寄存器为ARM 处理器的寄存器,目的寄存器1 和目的寄存器2 均为协处理器的寄存器。

指令示例:

MCR P3,3,R0,C4,C5,6;该指令将ARM 处理器寄存器R0 中的数据传送到协处理器P3 的寄存器C4 和C5 中。

5、MRC 指令

MRC 指令的格式为:

MRC{条件} 协处理器编码,协处理器操作码1,目的寄存器,源寄存器1,源寄存器2,协处理器操作码2。

MRC 指令用于将协处理器寄存器中的数据传送到ARM 处理器寄存器中,若协处理器不能成功完成操作,则产生未定义指令异常。其中协处理器操作码1 和协处理器操作码2 为协处理器将要执行的操作,目的寄存器为ARM 处理器的寄存器,源寄存器1 和源寄存器2 均为协处理器的寄存器。

指令示例:

MRC P3,3,R0,C4,C5,6;该指令将协处理器P3 的寄存器中的数据传送到ARM 处理器寄存器中.

The ARM920T 有两个具体协处理器

CP14调试通信通道协处理器

调试通信通道协处理器DCC(the Debug Communications Channel)提供了两个32bits寄存器用于传送数据,还提供了6bits通信数据控制寄存器控制寄存器中的两个位提供目标和主机调试器之间的同步握手。

通信数据控制寄存器

以下指令在Rd 中返回控制寄存器的值:

MRC p14, 0, Rd, c0, c0

此控制寄存器中的两个位提供目标和主机调试器之间的同步握手:

位1(W 位)从目标的角度表示通信数据写入寄存器是否空闲:

W = 0 目标应用程序可以写入新数据。

W = 1 主机调试器可以从写入寄存器中扫描出新数据。

位0(R 位)从目标的角度表示通信数据读取寄存器中是否有新数据:

R = 1 有新数据,目标应用程序可以读取。

R = 0 主机调试器可以将新数据扫描到读取寄存器中。

注意

调试器不能利用协处理器14 直接访问调试通信通道,因为这对调试器无意义。但调试器可使用扫描链读写DCC 寄存器。DCC 数据和控制寄存器可映射到EmbeddedICE 逻辑单元中的地址。若要查看EmbeddedICE 逻辑寄存器,请参阅您的调试器和调试目标的相关文档。

通信数据读取寄存器

用于接收来自调试器的数据的32 位宽寄存器。以下指令在Rd 中返

回读取寄存器的值:

MRC p14, 0, Rd, c1, c0

通信数据写入寄存器

用于向调试器发送数据的32 位宽寄存器。以下指令将Rn 中的值写

到写入寄存器中:

MCR p14, 0, Rn, c1, c0

注意

有关访问ARM10 和ARM11 内核DCC 寄存器的信息,请参阅相应的技术参考手册。ARM9 之后的各处理器中,所用指令、状态位位置以及对状态位的解释都有所不同。

目标到调试器的通信

这是运行于ARM 内核上的应用程序与运行于主机上的调试器之间的通信事件

顺序:

1. 目标应用程序检查DCC 写入寄存器是否空闲可用。为此,目标应用程序使

用MRC 指令读取调试通信通道控制寄存器,以检查W 位是否已清除。

2. 如果W 位已清除,则通信数据写入寄存器已清空,应用程序对协处理器14

使用MCR 指令将字写入通信数据写入寄存器。写入寄存器操作会自动设置

W 位。如果W 位已设置,则表明调试器尚未清空通信数据写入寄存器。此

时,如果应用程序需要发送另一个字,它必须轮询W 位,直到它已清除。

3. 调试器通过扫描链2 轮询通信数据控制寄存器。如果调试器发现W 位已设

置,则它可以读DCC 数据寄存器,以读取应用程序发送的信息。读取数据

的进程会自动清除通信数据控制寄存器中的W 位。

以下代码显示了这一过程

AREA OutChannel, CODE, READONLY

ENTRY

MOV r1,#3 ; Number of words to send

ADR r2, outdata ; Address of data to send

pollout

MRC p14,0,r0,c0,c0 ; Read control register

TST r0, #2

BNE pollout ; if W set, register still full

write

LDR r3,[r2],#4 ; Read word from outdata

; into r3 and update the pointer

MCR p14,0,r3,c1,c0 ; Write word from r3

SUBS r1,r1,#1 ; Update counter

BNE pollout ; Loop if more words to be written

MOV r0, #0x18 ; Angel_SWIreason_ReportException

LDR r1, =0x20026 ; ADP_Stopped_ApplicationExit

SVC 0x123456 ; ARM semihosting (formerly SWI)

outdata

DCB "Hello there!"

END

调试器到目标的通信

这是运行于主机上的调试器向运行于内核上的应用程序传输消息的事件顺序:1. 调试器轮询通信数据控制寄存器的R 位。如果R 位已清除,则通信数据读取寄存器已清空,可将数据写入此寄存器,以供目标应用程序读取。

2. 调试器通过扫描链2 将数据扫描到通信数据读取寄存器中。此操作会自动设置通信数据控制寄存器中的R 位。

3. 目标应用程序轮询通信数据控制寄存器中的R 位。如果该位已经设置,则通信数据读取寄存器中已经有数据,应用程序可使用MRC 指令从协处理器

14 读取该数据。同时,读取指令还会清除R 位。

以下显示的目标应用程序代码演示了这一过程

AREA InChannel, CODE, READONLY

ENTRY

MOV r1,#3 ; Number of words to read

LDR r2, =indata ; Address to store data read

pollin

MRC p14,0,r0,c0,c0 ; Read control register

TST r0, #1

BEQ pollin ; If R bit clear then loop

read

MRC p14,0,r3,c1,c0 ; read word into r3

STR r3,[r2],#4 ; Store to memory and

; update pointer

SUBS r1,r1,#1 ; Update counter

BNE pollin ; Loop if more words to read

MOV r0, #0x18 ; Angel_SWIreason_ReportException

LDR r1, =0x20026 ; ADP_Stopped_ApplicationExit

SVC 0x123456 ; ARM semihosting (formerly SWI)

AREA Storage, DATA, READWRITE

indata

DCB "Duffmessage#"

END

CP15系统控制协处理器

CP15 —系统控制协处理器(the system control coprocessor)他通过协处理器指令MCR和MRC提供具体的寄存器来配置和控制caches、MMU、保护系统、配置时钟模式(在bootloader 时钟初始化用到)

CP15的寄存器只能被MRC和MCR(Move to Coprocessor from ARM Register )指令访问

MCR{cond} p15,

MRC{cond} p15,

其中L位用来区分MCR(L=1)和MRC(L=0)操作. CP15包括15个具体的寄存器如下

-R0:ID号寄存器

-R0:缓存类型寄存器

-R1:控制寄存器

-R2:转换表基址寄存器(Translation Table Base --TTB)-R3:域访问控制寄存器(Domain access control )

-R4:保留

-R5:异常状态寄存器(fault status -FSR)

-R6:异常地址寄存器(fault address -FAR)

-R7:缓存操作寄存器

-R8:TLB操作寄存器

-R9:缓存锁定寄存器

-R10:TLB 锁定寄存器

-R11-12&14:保留

-R13:处理器ID

-R15:测试配置寄存器2-24

要注意有2个R0,根据MCR操作数的不同传送不同的值,这也一个只读寄存器

-R0:ID号寄存器这是一个只读寄存器,返回一个32位的设备ID号,具体功能参考ARM 各个系列型号的的CP15 Register 0说明.

MRC p15, 0,

以下为ID Code详细描叙(ARM926EJ-S); ARM920T Part Number为0x920,Architecture (ARMv4T) 为0x2具体可参照ARM各型号.

-R0:缓存类型寄存器(CACHE TYPE REGISTER),包含了caches的信息。读这个寄存器的方式是通过设置协处理操作码为1.

MRC p15, 0,

以下为CP15的一些应用示例

U32 ARM_CP15_DeviceIDRead(void)

{

U32 id;

__asm { MRC P15, 0, id, c0, c0; }

return id;

}

void ARM_CP15_SetPageTableBase(P_U32 TableAddress)

{

__asm { MCR P15, 0, TableAddress, c2, c0, 0; }

}

void ARM_CP15_SetDomainAccessControl(U32 flags)

{

__asm { MCR P15, 0, flags, c3, c0, 0; }

}

void ARM_CP15_ICacheFlush()

{

unsigned long dummy;

__asm { MCR p15, 0, dummy, c7, c5, 0; }

}

void ARM_CP15_DCacheFlush()

{

unsigned long dummy;

__asm { MCR p15, 0, dummy, c7, c6, 0; }

}

void ARM_CP15_CacheFlush()

{

unsigned long dummy;

__asm { MCR p15, 0, dummy, c7, c7, 0; }

}

void ARM_CP15_TLBFlush(void)

{

unsigned long dummy;

__asm { MCR P15, 0, dummy, c8, c7, 0; }

}

void ARM_CP15_ControlRegisterWrite(U32 flags) {

__asm { MCR P15, 0, flags, c1, c0; }

}

void ARM_CP15_ControlRegisterOR(U32 flag) {

mrc p15,0,r0,c1,c0,0

mov r2,flag

orr r0,r2,r0

mcr p15,0,r0,c1,c0,0

}

}

void ARM_CP15_ControlRegisterAND(U32 flag)

{

__asm {

mrc p15,0,r0,c1,c0,0

mov r2,flag

and r0,r2,r0

mcr p15,0,r0,c1,c0,0

}

}

void ARM_MMU_Init(P_U32 TableAddress)

{

ARM_CP15_TLBFlush();

ARM_CP15_CacheFlush();

ARM_CP15_SetDomainAccessControl(0xFFFFFFFF);

ARM_CP15_SetPageTableBase(TableAddress);

}

void Enable_MMU (void)

{

__asm {

mrc p15,0,r0,c1,c0,0

mov r2, #0x00000001

orr r0,r2,r0

mcr p15,0,r0,c1,c0,0

printf("MMU enabled\n");

}

void Disable_MMU (void) {

__asm {

mrc p15,0,r0,c1,c0,0

mov r2, #0xFFFFFFFE

and r0,r2,r0

mcr p15,0,r0,c1,c0,0

}

printf("MMU disabled\n"); }

ARM处理器中CP15协处理器的寄存器 注意: You can only access CP15 registers with MRC and MCR instructions in a privileged mode (只能在特权模式下,对cp15进行MRC,MCR操作)。 1.访问CP15寄存器的指令 访问CP15寄存器指令的编码格式及语法说明如下: 31 28 27 24 23 21 20 19 16 15 12 11 8 7 5 4 3 0 cond 1 1 1 0 opcode_1 L Cr n Rd 1 1 1 1 opcode_2 1 Cr m 说明: Opcode_1 :协处理器行为操作码,对于CP15来说,永远为0b000,否则结果未知。 Rd:处理器核心的寄存器名称,不能是r15/pc,否则,结果未知。 Crn:作为目标寄存器的协处理器寄存器名称,编号为C0~C15。 Crm:协处理器中附加的目标寄存器或源操作数寄存器,如果不需要设置附加信息,将Crm设置为c0,否则结果未知。 Opcode_2 :提供附加信息,比如寄存器的版本号或者访问类型,用于区分同一个编号的不同物理寄存器,可以省略或者将其设置为0,否则结果未知。 指令语法格式说明: mcr :将ARM处理器的寄存器中的数据写到CP15中的寄存器中 mcr{

2.9如果GDT寄存器值为0013000000FFH,装人LDTR的选择符为0040H,试问装人描述符高速缓存的LDT描述符的起始地址是多少? 解:GDT寄存器的高32位和低16位分别为GDT的基址和段限,所以:GDT的基址=00130000H LDTR选择符的高13位D15~D3=000000001000B是该LDT描述符在GDT中的序号,所以: LDT描述符的起始地址= GDT的基址 十LDT描述符相对于GDT基址的偏移值 =00130000H+8×8=00130040H 2.10假定80486工作在实模式下,(DS)=1000H, (SS)=2000H, ( SI ) = El07FH, ( BX )=0040H, (BP) = 0016H,变量TABLE的偏移地址为0100H。请间下列指令的源操作数字段是什么寻址方式?它的有效地址(EA)和物理地址(PA)分别是多少? (1)MOV AX,[1234H ] (2) MOV AX, TABLE (3) MOV AX,[BX+100H] (4) MOV AX,TABLE[BPI[SI] 解:(1)直接寻址,EA=1234H , PA =(DS)×16+EA=11234H。 (2)直接寻址,EA= O100H,PA= (DS)×16+EA=10100H。 (3)基址寻址,EA=( EBX)+100H =0140H,PA= (DS) × 16+EA=10140H。 (4)带位移的荃址加变址寻址。(EA)= (BP)+[SI]十TABLE的偏移地址=0195H PA=(SS)×16+EA=20195H} 2.11下列指令的源操作数字段是什么寻址方式? (1)MOV EAX , EBX (2)MOV EAX,[ ECX] [EBX ] (3) MOV EAX,[ESI][EDX * 2] (4)MOV EAx,[ ESI*8] 解:(1)寄存器寻址。 (2)基址加变址寻址。 (3)基址加比例变址寻址。 (4)比例变址寻址。 2.12分别指出下列指令中源操作和目的操作数的寻址方式。 式表示出EA和PA。 (1)MOV SI,2100H (2)MOV CX, DISP[BX] (3) MOV [SI] ,AX (4)ADC AX,[BX][SI] (5)AND AX,DX (6) MOV AX,[BX+10H] (7) MOV AX,ES:[BX] (8) MOV Ax, [BX+SI+20H] (9) MOV [BP ].CX (10) PUSH DS 解:(1) 源操作数是立即数寻址;目的操作数是寄存器寻址。 (2)源操作数是基址寻址,EA=(BX)+DISP,PA=(DS)×16+(BX)+DISP 目的操作数是寄存器寻址。 (3)源操作数是寄存器寻址; 目的操作数是寄存器间接寻址,EA=(SI).PA=(DS) × 16十(SI)。 (4)操作数是基址加变址寻址,EA= (BX)+(SI).PA= (DS) × 16十(BX)+(SI) 目的操作数是寄存器寻址。 (5)源操作数和目的操作数均为寄存器寻址。 (6)源操作数是基址寻址,EA=(BX)+10H.PA= (DS) × 16十(BX)+10H 目的操作数是寄存器寻址。 (7)源操作数是寄存器间接寻.EA= (Bx).PA= (ES) × 16+(BX)

在基于ARM的嵌入式应用系统中,存储系统通常是通过系统控制协处理器CP15完成的。CP15包含16个32位的寄存器,其编号为0~15。 访问CP15寄存器的指令 MCR ARM寄存器到协处理器寄存器的数据传送 MRC 协处理器寄存器到ARM寄存器的数据传送 MCR指令和MRC指令只能在处理器模式为系统模式时执行,在用户模式下执行MCR 指令和MRC指令将会触发未定义指令的异常中断。 MCR指令 MCR指令将ARM处理器的寄存器中的数据传送到协处理器寄存器中。如果协处理器不能成功地执行该操作,将产生未定义的指令异常中断。 指令语法格式 MCR{

ARM920T的CP15协处理器 ARM920T的MMU和Cache都集成在CP15协处理器中,MMU和Cache的联系非常密切,本节首先从总体上介绍MMU、Cache和CPU核是如何协同工作的,后面两节分别讲解MMU和Cache的细节。三星公司的S3C2410是一种很常见的采用ARM920T的芯片,涉及到具体的芯片时我们以S3C2410为例。 以下是CP15协处理器的寄存器列表(摘自[S3C2410用户手册]),和CPU核的r0到r15寄存器一样,协处理器寄存器也是用0到15来编号,在指令中用4个bit来表示寄存器编号,有些协处理器寄存器有影子寄存器,这种情况下对同一个编号的寄存器使用不同的选项读或者写实际上访问的是不同的寄存器,后文用到某个寄存器时会详细说明它的功能。 表1. CP15协处理器的寄存器列表 对CP15协处理器的操作使用mcr和mrc两条协处理器指令,这两条指令的记法是从后往前看:mcr是把r(CPU核寄存器)中的数据传送到c(协处理器寄存器)中,mrc则是把c(协处理器寄存器)中的数据传送到r(CPU核寄存器)中。对CP15协处理器的所有操作都是通过CPU核寄存器和CP15寄存器之间交换数据来完成的。下图是协处理器的指令格式(摘自[S3C2410用户手册])。

图8. 协处理器指令格式 和其它ARM指令一样,Cond是条件码,bit 20是L位,表示该指令是读还是写,如果L=1就表示Load,从外面读到CPU核中,也就是mrc指令,如果L=0就表示Store,也就是mcr指令。[11:8]这四个位是协处理器编号,CP15的编号是15,因此是4个1。CRn是CP15寄存器编号,Rd是CPU核寄存器编号,各占4个位。对于CP15协处理器,规定opcode1应该为0,opcode2和CRm是指令的选项,具体含义取决于不同的寄存器。 虽然这里介绍了协处理器的寄存器编号和相关指令,但读者只需了解对协处理器是这样进行操作的就可以了,我们的重点是讲解MMU和Cache的基本概念,具体各种操作的指令该怎么写可以参考[S3C2410用户手册]。 MMU是如何把VA映射成PA的呢?从图4 “进程地址空间是独立的”来看,好像是有一张VA转PA的表,给一个VA查表就可以查到PA,实际上并不是这么简单,通常要有一个多级的查表过程,对于ARM体系结构是两级查表,对于一些64位体系结构则需要更多级。看下面的图示。 图9. Translation Table Walk 首先将32位的VA[3]分成三段,前两段[31:20]和[19:12]作为两次查表的索引,第三段[11:0]作为页内的偏移。查表的步骤如下: 1 CP15协处理器的TTB寄存器(看看表1 “CP15协处理器的寄存器列表”中这是第几个寄存器?)中保存着第一级页表(Translation Table)的基地址,这个基地址指的是PA,也就是说页表是直接按这个地址存在物理内存中的。 2 以TTB中的内容为基地址,以VA[31:20]为索引在表中查出一项(想一下这个表中一共有多少项?),这个表项中保存着第二级页表(Coarse Page Table)的基地址,同样是物理地址,也就是说第二级页表也是直接按这个地址存在物理内存中的。

1-3、ARM开发步步深入之MMU初窥 实验目的:启用MMU,映射SDRAM的地址空间,操作虚拟地址实现“点灯大法”,借此掌握MMU的使用。 实验环境及说明:恒颐S3C2410开发板H2410。H2410核心板扩展有64MB的K4S561632 SDRAM(4M*16bit*4BANK),地址范围是0x30000000~0x33FFFFFF。GPIO端口的地址范围是 0x56000000~0X560000B0。 实验思路:开发板上电启动后,自动将NandFlash开始的4K数据复制到SRAM中,然后跳转到0地址开始执行,然后初始化存储控制器SDRAM,把2K后的代码从SRAM中复制到SDRAM中(存放在0x30004000,前16KB用来存放页表)、设置页表、启动MMU 实现虚拟地址映射GPIO寄存器和SDRAM,最后跳转到SDRAM中(地址0xB0004000)运行。重新设置栈指针,跳到点灯代码的入口点实现点灯操作。 知识掌握:MMU地址转换、内存访问权限检查、TLB及Cache的使用 一、MMU地址转换: 1.首先弄清除为什么要使用MMU纳?MMU即内存管理单元,直白一点的讲,就像食堂的餐具,所有的学生一起吃饭时不够用,但食堂又不想再出资购买新的餐具(原因很明显:一方面要成本,另一方面

又占地方。这就像增加内存一样),那么有没有解决办法?根据以往经验得知不可能全学校的学习一起都到食堂吃饭,于是食堂就找几个人负责餐具的管理(相当于MMU),他们一方面发放餐具,保证来的同学有餐具可用,另一方面又回收用完的餐具(这就相当于虚拟地址到物理地址之间建立了一个映射一样,内存还是那么多,但从任意单个程序角度都好像用不完一样)。当然如果有同学一个人拿好几套餐具肯定不允许的(这就相当于内存的权限检查)。MMU在地址转换过程中涉及到三种地址:(VA---Virtual Address,虚拟地址)---这个就相当于餐具存放的地方(大家都可以领到餐具)。CPU核心看到和用到的只是虚拟地址VA,至于VA如果去对应物理地址PA,CPU 核心不理会,大家也不会去关心总共有多少餐具吧; (MVA---Modified Virtual Address,变换后的虚拟地址)---这个相当于放假的时候,人很少,只发餐具好了,用过的就不先回收了,节省人员了。Caches和MMU看不到VA,他们利用MVA转换得到PA,放假了回收餐具的人也不需要一直寻找用完的餐具; (PA---Physical Address,物理地址)---实际的餐具量,就那些。实际设备看不到VA、MVA,读写它们使用的是物理地址PA,同学们就餐一般会领到餐具。 2.虚拟地址到物理地址的转换过程。ARM使用页表来进行转换, S3C2410最多会用到两级页表,以段(Section,1M)的方式进行转换时只用到一级页表,以页(Page)的方式进行转换时用到两级页表。页的大小有3种:大页(64KB)、小页(4KB)和极小页(1KB)。本文

微处理器和指令系统 一、选择题 1、微型计算机中的运算器,将运算结果的一些特征标志寄存在(FR)中。 2、微处理器内部的控制器是由(ALU与寄存器)组成。 3. 8086微处理器内部能够计算出访问内存储器的20位物理地址的附加机构是(加法器)。 4. 若有两个带有符号数ABH和FFH相加,其结果使FR中CF和OF 位为(1和0)。 5. 逻辑地址是(允许在程序中编排的)地址。 6.字符串操作时目标串逻辑地址只能由(ES、DI)提供。 5. 8086微处理器中的ES是(附加段)寄存器。 6.8086处理器最小工作方式和最大工作方式的主要差别是(单处理器和多处理器的不同)。 7.8086微处理器内部通用寄存器中的指针类寄存器是(AX)。8.8086/8088微处理器引脚中(B)信号线能够反映标志寄存器中断允许标志位下的当前值。A. 7S B.5S C. 4S D. 6S 9.若进行加法运算的两个操作数为ABH和8BH,其结果使得CF和OF 为(1和l)。 10.欲使RESET有效, 只要(接通电源或按RESET键)即可。11.8086微处理器内部具有自动增1功能的寄存器是(IP)。12.最大方式下8086系统送8288总线控制器的状态信号为( A )。

A. 2S 、1S 、0S B. R /DT C .0SS D. DEN 13.8086/8088微处理器状态信号共有( 5)条。 14.编程人员不能直接读写的寄存器是(IP )。 15. 16位带有符号数的补码数据范围为( +32767~-32768)。 16.8086/8088微处理器可访问内存储器地址为(00000H ~FFFFFH )。 17.当标志寄存器FR 中OF 位等于1时,表示带有符号的字运算超出数据(–32768~32767)范围。 18.8086/8088微处理器CLK 引脚输入时钟信号是由(8284)提供的。 19.8086微处理器引脚2S 1S 0S 处于(001)状态时,表明读I/O 端口。 20.8086/8088微处理器中的段寄存器中的CS 作为段基值,偏移量允许使用(IP )。 21.8086微处理器以BP 内容作为偏移量,则段基值是由(SS )寄存器提供。 22.8086/8088微处理器中的寄存器可以用做8 位或16位寄存器,如( D )。 A. SI B .SP C. IP D. CX 23.在最小方式下,原8l86微处理器最大方式下2S 、1S 、0S 引脚应改为( C )。 A. M/IO 、DEN 、DT/R B .DT/R 、M/IO 、DEN C. M/IO 、DT/R 、DEN D. DEN 、M/IO 、DT/R 24.访问I/O 端口可用地址线有(16)条. 25.最大方式下引脚25号和24号分别为0QS 和1QS ,若工作于最小

1. 确定processor type arch/arm/kernel/head.S中: 00075: mrc p15, 0, r9, c0, c0 @ get processor id 00076: bl __lookup_processor_type @ r5=procinfo r9=cpuid 00077: movs r10, r5 @ invalid processor (r5=0)? 00078: beq __error_p @ yes, error 'p' 75行: 通过cp15协处理器的c0寄存器来获得processor id的指令. 关于cp15 的详细内容可参考相关的arm手册 76行: 跳转到__lookup_processor_type.在__lookup_processor_type中,会把 processor type 存储在r5中 77,78行: 判断r5中的processor type是否是0,如果是0,说明是无效的 processor type,跳转到__error_p(出错) __lookup_processor_type 函数主要是根据从cpu中获得的processor id和系统中的proc_info进行匹配,将匹配到的proc_info_list的基地址存到r5中, 0表示没 有找到对应的processor type. 下面我们分析__lookup_processor_type函数 arch/arm/kernel/head-common.S中: 00145: .type __lookup_processor_type, %function 00146: __lookup_processor_type: 00147: adr r3, 3f 00148: ldmda r3, {r5 - r7} 00149: sub r3, r3, r7 @ get offset between virt&phys 00150: add r5, r5, r3 @ convert virt addresses to 00151: add r6, r6, r3 @ physical address space 00152: 1: ldmia r5, {r3, r4} @ value, mask 00153: and r4, r4, r9 @ mask wanted bits 00154: teq r3, r4 00155: beq 2f 00156: add r5, r5, #PROC_INFO_SZ @ sizeof(proc_info_list)

ARM协处理器指令 ARM 微处理器可支持多达 16 个协处理器,用于各种协处理操作,在程序执行的过程中,每个协处理器只执行针对自身的协处理指令,忽略 ARM 处理器和其他协处理器的指令。ARM 的协处理器指令主要用于 ARM 处理器初始化 ARM 协处理器的数据处理操作,以及在ARM 处理器的寄存器和协处理器的寄存器之间传送数据,和在ARM 协处理器的寄存器和存储器之间传送数据。 ARM 协处理器指令包括以下 5 条: — CDP 协处理器数操作指令 — LDC 协处理器数据加载指令 — STC 协处理器数据存储指令 — MCR ARM 处理器寄存器到协处理器寄存器的数据传送指令 — MRC 协处理器寄存器到ARM 处理器寄存器的数据传送指令 1、CDP 指令 CDP 指令的格式为: CDP{条件} 协处理器编码,协处理器操作码1,目的寄存器,源寄存器1,源寄存器2,协处理器操作码2。CDP 指令用于ARM 处理器通知ARM 协处理器执行特定的操作,若协处理器不能成功完成特定的操作,则产生未定义指令异常。其中协处理器操作码1 和协处理器操作码2 为协处理器将要执行的操作,目的寄存器和源寄存器均为协处理器的寄存器,指令不涉及ARM 处理器的寄存器和存储器。 指令示例: CDP P3 , 2 , C12 , C10 , C3 , 4 ;该指令完成协处理器 P3 的初始化 2、LDC 指令 LDC 指令的格式为: LDC{条件}{L} 协处理器编码,目的寄存器,[源寄存器] LDC 指令用于将源寄存器所指向的存储器中的字数据传送到目的寄存器中,若协处理器不能成功完成传送操作,则产生未定义指令异常。其中,{L}选项表示指令为长读取操作,如用于双精度数据的传输。 指令示例: LDC P3 , C4 , [R0] ;将 ARM 处理器的寄存器 R0 所指向的存储器中的字数据传送到协处理器 P3 的寄存器 C4 中。 3、STC 指令 STC 指令的格式为: STC{条件}{L} 协处理器编码,源寄存器,[目的寄存器]

访问CP15寄存器指令的编码格式及语法说明如下: 说明:

?CP15的寄存器C0 CP15中寄存器C0对应两个标识符寄存器,由访问CP15中的寄存器指令中的

第三章8086微处理器指令系统习题答案 一、单项选择题 1.B 2.C 3.B 4.D 5.A 6.C 7.B 8.C 9.C10. D 11.D12.C13.C14.A15.C16.B17.C18.B19.D20. D 21.B22.D23.A24.D25.A26.A27.A28.D29.C30. A 31.D32.C33.B34.D35.D36.D37.A38.B39.B40. B 41.B42.A43.D44.D45.A46.C47.D48. C 二、多项选择题 1.ABC 2.ABCD 3.ABF 4.BF 5.BCD 6.CD 7.ABCDE 8.BD 三、填空题 1.操作码,操作数 2段地址,10H,偏移地址,02051H 3.AA92AH 4.立即,基址变址 5.5425H 6.D36AH 7.源操作数为8位,目的操作数为16位,不匹配;源操作数和目的操作数不能同时为存储器;INC指令操作数不能为立即数;目的操作数的的地址大于字节。 8.6310H 9.0132H,0112H 10.0000H,1,1,0,0 11.1202H,1200H,2000H 12.除4 13.7230H 14.12AAH,0BBCCH 15.6804H 16.3,0 17.4154H,6F30H 18.0,00FFH,0 四、判断题 ×V ××V ××V ×V ××××V ×V ××× 五、读程序,指出结果 1.11H 2.5678H,1234H 3.80H,0 4.1,1 5. 1 6.0132H,0112H 7.01H,00H,08H 8.0,0 9.79H,6H,7FH 10.60H,35H

详解ARM处理器中的37个寄存器 作者:雪狼发布时间:March 22, 2010 分类:程序编程 ARM处理器共有37个寄存器。其中包括: 31个通用寄存器,包括程序计数器(PC)在内。这些寄存器都是32位寄存器。 6个状态寄存器。这些寄存器都是32位寄存器。 ARM处理器共有7种不同的处理器模式,每一种模式中都有一组相应的寄存器组。在任何时刻,可见的寄存器包括15个通用寄存器(R0-R14),一个或两个状态寄存器及程序计数器(PC)。在所有的寄存器中,有些是各模式公用一个物理寄存器,有一些寄存器各模式拥有自己独立的物理寄存器。 通用寄存器: 通用寄存器分为以下三类:备份寄存器、未备份寄存器、程序计数器PC 未备份寄存器: 未备份寄存器包括R0-R7。对于每一个未备份寄存器来说,所有处理器模式下都是使用同一个物理寄存器。未备份寄存器没有被系统用于特别的用途,任何可采用通用寄存器的场合都可以使用未备份寄存器。 备份寄存器: 对于R8-R12备份寄存器来说,每个寄存器对应两个不同的物理寄存器。系统为将备份寄存器用于任何的特殊用途,但是当中断处理非常简单,仅仅使用R8-R14寄存器时,FIQ处理程序可以不必执行保存和恢复中断现场的指令,从而可以使中断处理非常迅速。 对于R13,R14备份寄存器来说,每个寄存器对应六个不同的物理寄存器,其中的一个是系统模式和用户模式共用的;另外的五个对应于其他的五种处理器模式。采用下面的记号来区分各个物理寄存器: R13_ 其中MODE可以是下面几种模式之一:usr,svc,abt,und,irq,fiq

程序计数器PC 可以作为一般的通用寄存器使用,但有一些指令在使用R15时有一些限制。由于ARM采用了流水线处理器机制,当正确读取了PC的值时,该值为当前指令地址值加上8个字节。也就是说,对于ARM指令集来说,PC指向当前指令的下两条指令的地址。由于ARM指令是字对齐的,PC值的第0位和第一位总为0。 需要注意的是,当使用str/stm保存R15时,保存的可能是当前指令地址值加8个字节,也可能保存的是当前指令地址值加12个字节。到底哪种方式取决于芯片的具体设计。对于用户来说,尽量避免使用STR/STM指令来保存R15的值。 当成功的向R15写入一个数值时,程序将跳转到该地址执行。由于ARM指令是字对齐的,写入R15的值应满足bits[1:0]为0b00,具体要求arm个版本有所不同: **对于arm3以及更低的版本,写入R15的地址值bits[1:0]被忽略,即写入r15的地址值将与0xFFFF FFFC做与操作。 **对于ARM4以及更高的版本,程序必须保证写入R15的地址值bits[1:0]为0b00,否则将产生不可预知的后果。对于Thumb指令集来说,指令是班子对齐的,处理器将忽略bit[0]。 程序状态寄存器 CPSR(当前程序状态寄存器)在任何处理器模式下被访问。它包含了条件标志位、中断禁止位、当前处理器模式标志以及其他的一些控制和状态位。每一种处理器模式下都有一个专用的物理状态寄存器,称为SPSR(备份程序状态寄存器)。当特定的异常中断发生时,这个寄存器用于存放当前程序状态寄存器的内容。在异常中断退出时,可以用SPSR来恢复CPSR。由于用户模式和系统模式不是异常中断模式,所以他没有SPSR。当用户在用户模式或系统模式访问SPSR,将产生不可预知的后果。 CPSR格式如下所示。SPSR和CPSR格式相同。 31 30 29 28 27 26 7 6 5 4 3 2 1 0 N Z C V Q DNM(RAZ) I F T M4 M3 M2 M1 M0 ***条件标志位*** N——本位设置成当前指令运算结果的bit[31]的值。当两个表示的有符号整数运算时,n=1表示运算结果为负数,n=0表示结果为正书或零。 z——z=1表示运算的结果为零;z=0表示运算的结果不为零。对于CMP指令,Z=1表示进行比较的两个数大小相

4.1.1 访问CP15寄存器的指令 访问CP15寄存器指令的编码格式及语法说明如下: 3 1 2 8 2 7 2 4 2 3 2 1 2 1 9 1 6 1 5 1 2 1 1 8 7 5 43 c o n d 1 1 1 o p c o d e _ 1 L c r n r d 1 1 1 1 o p c o d e _ 2 1c r m 说明: :协处理器行为操作码,对于CP15来说,永远为0b000,否则结果未知。 :不能是r15/pc,否则,结果未知。 :作为目标寄存器的协处理器寄存器,编号为C0~C15。 :附加的目标寄存器或源操作数寄存器,如果不需要设置附加信息,将crm设置为 c0,否则结果未知。 :提供附加信息比如寄存器的版本号或者访问类型,用于区分同一个编号的不同物理寄存器,可以省略或者将其设置为0,否则结果未知。 指 ??令 说 ??明 语法格式

mcr 将ARM处理器的寄存器中的 数据写到CP15中的寄存器中 mcr{ } p15, , , , , { } mrc 将CP15中的寄存器中的数据 读到ARM处理器的寄存器中 mcr{ } p15, , , , , { } 4.1.2 CP15寄存器介绍 CP15的寄存器列表如表4-1所示。 表4-1 ARM处理器中CP15协处理器的寄存器 寄存器编号 基本 作用 在MMU 中的作 用 在PU中的作 用 0 ID编码(只 读) ID编码和 cache类型 1 控制位(可 读写) 各种控制位 2 存储保护和 控制 地址转换表基 地址 Cachability的控制 位 3 存储保护和 控制 域访问控制位 Bufferablity控制位

ARM体系结构与接口技术(一)

ARM920TDMA处理器是哈佛结构,包括取指、译码、执行、存储、写入的五级流水线。包括cp14和cp15两个协处理器。16k数据缓存和16k指令缓存。虚拟地址64路相关缓存。每线8字。 ARM的基本数据类型: ARM采用的是32位架构,基本上数据类型有以下三种: Byte :字节,8位 Halfword:半字,16bit(半字必须与2字节边界对齐 Word:字,32bit(必须与4字节边界对齐 所有的数据类型指令的操作数都是字类型。 ARM指令编译后是4字节(与字边界对齐,Thumb指令编译后是2字节(与半字对齐 存储器大/小端 Arm支持大端模式和小端模式。在大端模式下,一个字的高地址放的是数据的地位,在小端模式下,数据的低地址放的是数据的低位。 ARM920T,有7中工作模式: 用户模式(User,正常程序执行模式。 快速中断模式(FIQ,当一个高优先级中断产生时将会进入该模式,一般用于高速数据传输和通道处理。 外部中断模式(IRQ,当一个低优先级中断产生时将会进入该模式,一般用于通常的中断处理

特权模式(Supervise,当复位或软中断指令执行时进入该模式,是一种供操作系统使用的保护模式。 数据访问中止模式(abort,当存取异常时将会进入该模式,用于虚拟存储或存储保护未定义指令中止模式(undef,当执行未定义指令时进入该模式,有时用于通过软件仿真协处理器硬件的工作方式 系统模式(system使用和user模式相同的寄存器集模式,用于运行特权级操作系统任务 除了用户模式,其他六中均为特权模式。在特权模式下,程序可以访问所有的系统资源,也可以任意的进行处理器模式切换。 流水线的概念与原理 处理器按照一系列的步骤来执行每一条指令,典型的步骤如下: 1、从存储器读取指令(fetch 2、译码以鉴别它是属于哪一条指令(decode 3、从指令中提取指令的操作数(这些操作数往往存在于寄存器中(reg 4、将操作数进行组合以得到结果或存储器地址(ALU 5、如果需要,则访问存储器以存储数据(mem 6、将结果写回到寄存器堆(res 流水线的分类: 1、3级流水线ARM组织 取指令—>译码—>执行

ARM 协处理器及访问CP15协处理器 4.1.1 访问CP15寄存器的指令 访问CP15寄存器指令的编码格式及语法说明如下:31 28 27 24 23 21 2019 16 15 12 11 8 7 5 4 3 0 cond 1 1 1 0 opcode _1 L cr n rd 1 1 1 1 opcode _2 说明:

:协处理器行为操作码,对于CP15来说,永远为0b000,否则结果未知。:不能是r15/pc,否则,结果未知。 :作为目标寄存器的协处理器寄存器,编号为C0~C15。 :附加的目标寄存器或源操作数寄存器,如果不需要设置附加信息,将crm 设置为c0,否则结果未知。(很重要 如(来自UBOOT PROJECT: / * disable MMU stuff and caches */ mrc p15, 0, r0, c1, c0, 0 bic r0, r0, #0x00002300 @ clear bits 13, 9:8 (--V- --RS bic r0, r0, #0x00000087 @ clear bits 7, 2:0 (B--- -CAM orr r0, r0, #0x00000002 @ set bit 2 (A Align orr r0, r0, #0x00001000 @ set bit 12 (I I-Cache mcr p15, 0, r0, c1, c0, 0 :提供附加信息比如寄存器的版本号或者访问类型,用于区分同一个编号的不同物理寄存器,可以省略或者将其设置为0,否则结果未知。 指令说明 语法格式 mcr 将ARM 处理器的寄存器中的数据写 到CP15中的寄存器中 mcr{} p15, , , , , {} mrc 将CP15中的寄存器中的数据读到 ARM 处理器的寄存器中 mcr{}

ARM920T的MMU与Cache 目录 虚拟地址和物理地址的概念 虚拟内存管理 ARM920T的CP15协处理器 MMU Cache 操作MMU和Cache的内核启动代码 参考资料索引 虚拟地址和物理地址的概念 CPU通过地址来访问内存中的单元,地址有虚拟地址和物理地址之分,如果CPU没有MMU (Memory Management Unit,内存管理单元),或者有MMU但没有启用,CPU核在取指令或访问内存时发出的地址将直接传到CPU芯片的外部地址引脚上,直接被内存芯片(以下称为物理内存,以便与虚拟内存区分)接收,这称为物理地址(Physical Address,以下简称PA),如下图所示。 图 1. 物理地址示意图 如果CPU启用了MMU,CPU核发出的地址将被MMU截获,从CPU到MMU的地址称为虚拟地址(Virtual Address,以下简称VA),而MMU将这个地址翻译成另一个地址发到CPU芯片的外部地址引脚上,也就是将虚拟地址映射成物理地址,如下图所示[1]。

图 2. 虚拟地址示意图 MMU将虚拟地址映射到物理地址是以页(Page)为单位的,对于32位CPU 通常一页为4K。例如,虚拟地址0xb700 1000~0xb700 1fff是一个页,可能被MMU映射到物理地址0x2000~0x2fff,物理内存中的一个物理页面也称为一个页框(Page Frame)。 虚拟内存管理 现代操作系统充分利用MMU提供的VA到PA的映射机制来做内存管理,以下称为虚拟内存管理(Virtual Memory Management)。首先看下面的例子: 例 1. 进程的地址空间 这是bash进程的虚拟地址空间,32位CPU的虚拟地址空间是4GB,也就是 0x0000 0000-0xffff ffff,该进程占用的地址范围近似为0x0000 0000-0xbfff ffff,地址范围0xc000 0000-0xffff ffff由内核占用,用户进程不允许访问。在这个bash进程的地址空间中,从0x0804 8000开始的668K的权限为r-x--,

汇编知识点的要求: 1、能看的懂 2、可以做修改 3、不需要用汇编直接编写程序 汇编代码的应用场合: 1、ARM的启动代码必须要汇编,如:uboot最开始初始化硬件的代码 2、内核在最开始初始化的位置。。。。 一、ARM汇编指令的编码格式 1、编码格式 ARM汇编指令编译成机器码以后,机器码的长度是32bits,这32bits的编码有一个固定的格式。不同ARM 汇编指令,编码格式不同。 2、举例 C: if(a==10) a++; else a--;

汇编1: CMP R0, #10; ADDEQ R0,R0,#1 SUBNE R0,R0,#1 汇编2 SUBS R1, R0, #10; //S ---运算的结果会影响条件码标志位:CPSR:NZCV ADDEQ R0,R0,#1 SUBNE R0,R0,#1 提示: 空指令NOP,实际上是占用CPU的时间,但是执行后,没有什么意义。 NOP ---- MOV R0,R0 3、条件码标识 10 -10 Z = 1 C = 0 N = 0 V = 0 ================================================================================= 二、ARM的寻址方式 1、立即数寻址 操作数,有立即数。 ADD R0,R0,#1

MOV R1,#10 ORR R1,R1,#0xf @ R1=R1 | 0xf BIC R1,R1,#0xf @R1 = R1&(~(0xf)) 错误: ADD R1,#1,#2 注意:立即数合法的条件 在ARM汇编指令中,并不是所有的立即数,立即数是有一定的限制的。 什么样的立即数是合法的??? 1、如果一个立即数是小于256的(即该立即数是8bits以内的,0~255),该立即数是合法的。 2、如果一个立即数是大于等于256,该立即数经过循环左移偶数位,可以得到一个小于256的数,则该立即数合法。 256 = 0x100 ------→左移20位0x10000000----→左移4 0x1 合法 0x111 非法 0x102 非法 0x104 合法 0xfff 0xff00 0x12000 0x450000 0xab 原因: 在数据处理指令编码的时候,立即数用12bits来表示: 高4bits:循环左移左移偶数位除以2 低8bits:循环左移后的结果。 重要问题: ADD R1,R0,#0xffff 非法 解决: LDR R2,=0xffff // R2=0xffff,将立即数0xffff的值传送给R2 ADD R1, R0, R2 2、寄存器寻址 所有的操作数都是寄存器,没有立即数 ADD R0,R0,R1 MOV R1,R0 ORR R1,R1,R0 @ R1=R1 | 0xf BIC R1,R1,R0 @R1 = R1&(~(0xf))

MCR指令将ARM处理器的寄存器中的数据传送到协处理器的寄存器中。如果协处理器不能成功地执行该操作,将产生未定义的指令异常中断。 指令的语法格式: MCR{