Exhibition Services

展覽服務

Hong Kong Houseware Fair

香港家庭用品展

Hong Kong Gifts & Premium Fair 香港禮品及贈品展

We Deliver Premium Choices

Who can better fulfill your exhibition needs than a

creative and customer oriented partner? At Exhibition

Services Department of the Hong Kong Trade Development Council (HKTDC), our motto is “We deliver”. Since 1989, we have been building on this solid

culture, from simply a stand fitter to an integrated and

total solution provider today. From design concept to

final execution, we offer one-stop hassle free solutions.

We also see to the details that your every requirement is answered and timely executed. In our aim to be your

best exhibition partner, we relentlessly build our competencies in design and quality managemant, and advocate the established international standard in our operations. This is reflected in the full spectra of ISO certification we achieved in 2003, second to none in

Hong Kong’s exhibition contracting industry, including:

? ISO 9001 (Quality Management)

? ISO 14001 (Environmental Protection)

? OHSAS 18001 (Occupational Health and Safety)

? ISO 9001 (品質管理)

? ISO 14001 (環境保護)

? OHSAS 18001 (職業安全及健康)

特級選擇 盡在掌握

要全面滿足您展出的需要,自當要有一個創意無限及以客為先的合作伙伴。香港貿易發展局展覽服務部,向以「我們做得到」作為座右銘。自1989起,我們便一直朝著這目標進發,從初期作為裝配攤位的承建商,發展至今日提供全方位解決方案的服務供應商。由設計概念至落實執行,我們會為您提供一站式服務,確保您的要求全面及準時達到。作為您最佳的展覽合作伙伴,我們積極提升設計及服務質素,並按國際標準規範作業流程。於2003年,我們更率先成為本港業界獲得以下ISO 證書的服務供應商:

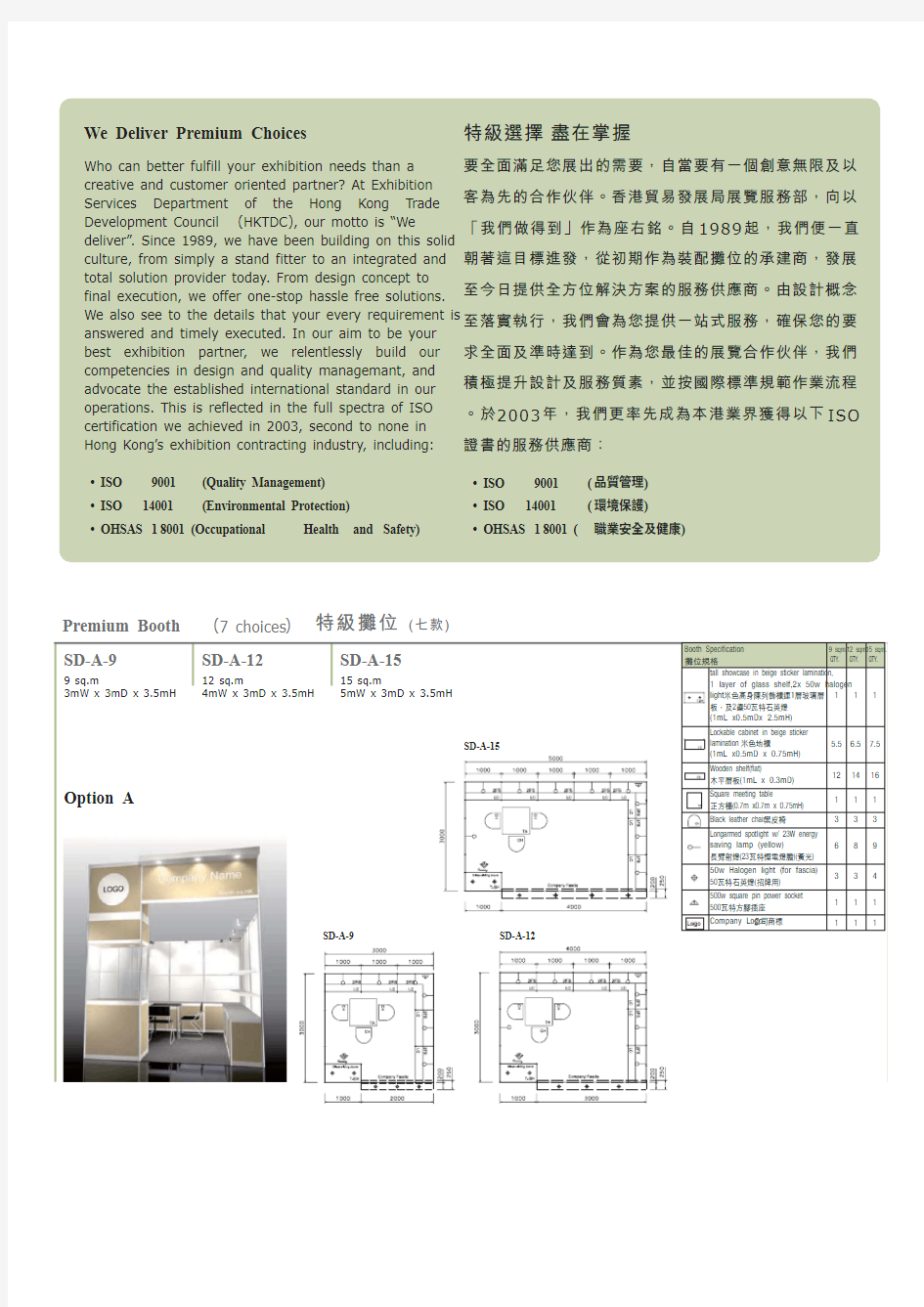

Premium Booth(7 choices) 特級攤位 (七款)

Premium Booth Enquiries 特級攤位查詢

For booth facilities Ms. Stephanie Voon Tel: (852) 2240 5485

Fax: (852) 2169 9551 / 2519 8223

E-mail: stephanie.nl.voon@https://www.doczj.com/doc/0f4849385.html, Ms. Tweety Yu

Tel: (852) 2240 5435

Fax: (852) 2169 9520 / 2519 8223E-mail: tweety.cy.yu@https://www.doczj.com/doc/0f4849385.html, Hong Kong Houseware Fair Mr. Jeffrey Tang Tel: (852) 2240 4215

Fax: (852) 2169 9567 / 2824 0026E-mail: jeffrey.kc.tang@https://www.doczj.com/doc/0f4849385.html, Hong Kong Gifts & Premium Fair Mr. Chan Chi Kin Tel: (852) 2240 4380

Fax: (852) 2169 9149 / 2824 0026E-mail: ck.chan@https://www.doczj.com/doc/0f4849385.html,

Raw Space Design Enquiries 空地攤位設計查詢

Ms. Joan Wong

Tel: (852) 2240 5470Fax: (852) 2519 8223

E-mail: joan.wong@https://www.doczj.com/doc/0f4849385.html,

Remarks:

* Sticker cut-out company name, rubbish bin and carpet are all included in premium booth

* The carpet colour shown in the drawing is for reference only. Only official carpet will be provided * Socket included in the booth is not used for lighting

註:

* 所有攤位包括公司名牌,廢紙簍及地氈

* 圖中地氈顏色只供參考,攤位只提供大會地氈* 攤位內提供之插座不可用於照明裝置

Hong Kong Trade Development Council - Exhibitions Department Unit 13, Expo Galleria, Hong Kong Convention & Exhibition Centre, 1 Expo Drive, Wanchai, Hong Kong

Tel: (852) 1830 668 Fax: (852) 2824 0026 E-mail: exhibitions@https://www.doczj.com/doc/0f4849385.html,.hk

初中物理家庭电路作图 题 TYYGROUP system office room 【TYYUA16H-TYY-TYYYUA8Q8-

家庭电路作图题训练 姓名:_____________班级:_____________ 1、把带有开关的电灯,三孔插座正确地连入如图的家庭电路中. 2、一间教室要安装2盏“220V 40W”的电灯和一个插座,要求开关S控制两盏灯,且每盏灯都能正常发光,请按以上要求将图中元件用笔画线代替导线连接起来. 3、请同学们将图连成符合安全用电原则的照明电路。 4、(2015洪湖市一模)请用笔画线代替导线,将如图中的电灯、开关和插座(插座准备接大功率用电器)接入家庭电路中. 5、将如图所示电水壶的3条接线按照安全用电的原则对应连接到插头上. 6、请将带开关的螺丝口灯泡和带熔丝的三孔插座,正确接入图中所示的电路中。 7、声控开关在静音时处于断开状态,在接收到一定响度的声音时会自动闭合一段时间;某地下通道两端的入口处各装有一个声控开关来控制同一盏电灯,为确保行人不管从那端进入,电灯都能接通电源发光;请用笔画线代替导线,在答题卡上按题意要求将图中的电路连接完整。 8、下图是家庭电路的示意图。请把该图连接完整(4分) 9、小宝想在卧室安装一盏照明电灯,请在图中帮他把灯和开关接入电路。 10、如图所示,甲为一个“一开三孔”开关(即一个开关和一个三孔插座连在一起)的实物图,乙为背面接线示意图,“A”“B”是从开关接线柱接出的两根导线,请你将图乙中的电路连接完整,使开关控制电灯,又不影响插座供其他电器使用。 11、请在图中的虚线框内设计一电路图:连接导线,使护士看见L1灯亮知道1号病房有人呼叫,看见L2灯亮知道2号病房有人呼叫。(虚线框内导线不许交叉) 12、为节约电能,地下通道电动扶梯只需在白天且有人时才开启,利用红外线自动开关S1(现场有人,S1闭合;现场无人,S1断开)以及可见光自动开关S2(白天,S2闭合;夜间,S2断开)控制电路,可达到目的.请完成电路连接.

排序算法 一、插入排序(Insertion Sort) 1. 基本思想: 每次将一个待排序的数据元素,插入到前面已经排好序的数列中的适当位置,使数列依然有序;直到待排序数据元素全部插入完为止。 2. 排序过程: 【示例】: [初始关键字] [49] 38 65 97 76 13 27 49 J=2(38) [38 49] 65 97 76 13 27 49 J=3(65) [38 49 65] 97 76 13 27 49 J=4(97) [38 49 65 97] 76 13 27 49 J=5(76) [38 49 65 76 97] 13 27 49 J=6(13) [13 38 49 65 76 97] 27 49 J=7(27) [13 27 38 49 65 76 97] 49 J=8(49) [13 27 38 49 49 65 76 97] Procedure InsertSort(Var R : FileType); //对R[1..N]按递增序进行插入排序, R[0]是监视哨// Begin for I := 2 To N Do //依次插入R[2],...,R[n]// begin R[0] := R[I]; J := I - 1; While R[0] < R[J] Do //查找R[I]的插入位置// begin R[J+1] := R[J]; //将大于R[I]的元素后移// J := J - 1 end R[J + 1] := R[0] ; //插入R[I] // end End; //InsertSort // 二、选择排序 1. 基本思想: 每一趟从待排序的数据元素中选出最小(或最大)的一个元素,顺序放在已排好序的数列的最后,直到全部待排序的数据元素排完。 2. 排序过程: 【示例】: 初始关键字[49 38 65 97 76 13 27 49] 第一趟排序后13 [38 65 97 76 49 27 49] 第二趟排序后13 27 [65 97 76 49 38 49] 第三趟排序后13 27 38 [97 76 49 65 49] 第四趟排序后13 27 38 49 [49 97 65 76] 第五趟排序后13 27 38 49 49 [97 97 76]

. 课程设计

. 教学院计算机学院 课程名称计算机组成原理题目4位乘法整列设计专业计算机科学与技术班级2014级计本非师班姓名唐健峰 同组人员黄亚军 指导教师 2016 年10 月 5 日

1 课程设计概述 1.1 课设目的 计算机组成原理是计算机专业的核心专业基础课。课程设计属于设计型实验,不仅锻炼学生简单计算机系统的设计能力,而且通过进行设计及实现,进一步提高分析和解决问题的能力。 同时也巩固了我们对课本知识的掌握,加深了对知识的理解。在设计中我们发现问题,分析问题,到最终的解决问题。凝聚了我们对问题的思考,充分的锻炼了我们的动手能力、团队合作能力、分析解决问题的能力。 1.2 设计任务 设计一个4位的二进制乘法器: 输入信号:4位被乘数A(A1,A2,A3,A4), 4位乘数B(B1,B2,B3,B4), 输出信号:8位乘积q(q1,q2,q3,q4,q5,q6,q7,q8). 1.3 设计要求 根据理论课程所学的至少设计出简单计算机系统的总体方案,结合各单元实验积累和课堂上所学知识,选择适当芯片,设计简单的计算机系统。 (1)制定设计方案: 我们小组做的是4位阵列乘法器,4位阵列乘法器主要由求补器和阵列全加器组成。 (2)客观要求 要掌握电子逻辑学的基本内容能在设计时运用到本课程中,其次是要思维灵活遇到问题能找到合理的解决方案。小组成员要积极配合共同达到目的。

2 实验原理与环境 2.1 1.实验原理 计算机组成原理,数字逻辑,maxplus2是现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。 用乘数的每一位去乘被乘数,然后将每一位权值直接去乘被乘数得到部分积,并按位列为一行每一行部分积末位与对应的乘数数位对齐,体现对应数位的权值,将各次部分积求和得到最终的对应数位的权值。 2.2 2.实验环境 2.2.1双击maxplu2II软件图标,启动软件 (1).新建工程,flie->new project ....,出现存储路径的选项框,指定项目保存路径并且为工程命名,第三行设置实体名,保持与工程名一致。点击OK

各种排序算法的总结和比较 1 快速排序(QuickSort) 快速排序是一个就地排序,分而治之,大规模递归的算法。从本质上来说,它是归并排序的就地版本。快速排序可以由下面四步组成。 (1)如果不多于1个数据,直接返回。 (2)一般选择序列最左边的值作为支点数据。(3)将序列分成2部分,一部分都大于支点数据,另外一部分都小于支点数据。 (4)对两边利用递归排序数列。 快速排序比大部分排序算法都要快。尽管我们可以在某些特殊的情况下写出比快速排序快的算法,但是就通常情况而言,没有比它更快的了。快速排序是递归的,对于内存非常有限的机器来说,它不是一个好的选择。 2 归并排序(MergeSort)

归并排序先分解要排序的序列,从1分成2,2分成4,依次分解,当分解到只有1个一组的时候,就可以排序这些分组,然后依次合并回原来的序列中,这样就可以排序所有数据。合并排序比堆排序稍微快一点,但是需要比堆排序多一倍的内存空间,因为它需要一个额外的数组。 3 堆排序(HeapSort) 堆排序适合于数据量非常大的场合(百万数据)。 堆排序不需要大量的递归或者多维的暂存数组。这对于数据量非常巨大的序列是合适的。比如超过数百万条记录,因为快速排序,归并排序都使用递归来设计算法,在数据量非常大的时候,可能会发生堆栈溢出错误。 堆排序会将所有的数据建成一个堆,最大的数据在堆顶,然后将堆顶数据和序列的最后一个数据交换。接下来再次重建堆,交换数据,依次下去,就可以排序所有的数据。

Shell排序通过将数据分成不同的组,先对每一组进行排序,然后再对所有的元素进行一次插入排序,以减少数据交换和移动的次数。平均效率是O(nlogn)。其中分组的合理性会对算法产生重要的影响。现在多用D.E.Knuth的分组方法。 Shell排序比冒泡排序快5倍,比插入排序大致快2倍。Shell排序比起QuickSort,MergeSort,HeapSort慢很多。但是它相对比较简单,它适合于数据量在5000以下并且速度并不是特别重要的场合。它对于数据量较小的数列重复排序是非常好的。 5 插入排序(InsertSort) 插入排序通过把序列中的值插入一个已经排序好的序列中,直到该序列的结束。插入排序是对冒泡排序的改进。它比冒泡排序快2倍。一般不用在数据大于1000的场合下使用插入排序,或者重复排序超过200数据项的序列。

摘要:基于VHDL的数字系统设计具有设计技术齐全、方法灵活、支持广泛等优点,同时也是EDA技术的重要组成部分.文章用VHDL语言设计了左移法和进位节省法实现的两种组合乘法器,通过功能仿真,对两种乘法器的性能进行了比较,从而得知后者的传输延迟时间小,即速度较快.通过设计实例,介绍了利用VHDL语言进行数字系统设计的方法. 关键词:VHDL语言左移法进位节省法 Abstract:Digital system design based on VHDL has complete design techniques, methods, the advantages of flexible and wide support, at the same time also is the important component of the EDA technology. The article using VHDL language to design the left shift method and carry save method to realize the combination of two kinds of multiplier, through the function simulation, compares the performance of the two kinds of multiplier, which the latter's small transmission delay time, namely fast. Through the design example, introduced the method of using VHDL language to design digital system. Keywords:VHDL language ,left shift method ,carry save method

课程设计报告 课程设计题目:各种排序算法性能比较 学生姓名: 学号: 专业:信息管理与信息系统 班级: 指导教师: 2012年06 月23 日

目录 CONT E NT S 一、课程设计目的 (2) 二、课程设计题目概述 (2) 三、数据定义 (2) 四、各种排序的基本原理及时间复杂度分析 (3) 五、程序流程图 (6) 六、程序源代码 (6) 七、程序运行与测试 (15) 八、实验体会………………………………………………………… 九、参考文献…………………………………………………………

一、课程设计目的 课程设计为学生提供了一个既动手又动脑,独立实践的机会,将课本上的理论知识和实际有机的结合起来,锻炼学生的分析解决实际问题的能力。提高学生适应实际,实践编程的能力。 二、课程设计题目概述 排序的方法很多,但是就其全面性能而言,很难提出一种被认为是最好的方法,每一种方法都有各自的优缺点,适合在不同的环境下使用。如果排序中依据的不同原则对内部排序方法进行分类,则大致可分为直接插入排序、直接选择排序、起泡排序、Shell排序、快速排序、堆排序等六类排序算法。 本实验是对直接插入排序、直接选择排序、起泡排序、Shell排序、快速排序、堆排序这几种内部排序算法进行比较,用不同的测试数据做测试比较。比较的指标为关键字的比较次数和关键字的移动次数。最后用图表数据汇总,以便对这些内部排序算法进行性能分析。 三、数据定义 输入数据: 由于大多数排序算法的时间开销主要是关键字之间的比较和记录的移动,算法的执行时间不仅依赖于问题的规模,还取决于输入实例中数据的状态。所以对于输入数据,我们采用由用户输入记录的个数(以关键字的数目分别为20,100,500为例),测试数据由随机数产生器生成。 输出数据: 产生的随机数分别用直接插入排序;直接选择排序;起泡排序;Shell排序;快速排序;堆排序这些排序方法进行排序,输出关键字的比较次数和移动次数。

EDA课程设计报告 实验名称:八位乘法器

目录 一.引言 1.1 EDA技术的概念?? 1.2 EDA技术的特点?? 1.3 EDA设计流程?? 1.4 VHDL介绍?? 二.八位乘法器的设计要求与设计思路??2.1 设计目的?? 2.2 设计要求?? 三.八位乘法器的综合设计?? 3.1 八位乘法器功能?? 3.2 八位乘法器设计方案?? 3.3 八位乘法器实体设计?? 3.4 八位乘法器VHDL设计?? 3. 5八位乘法器仿真图形?? 心得体会?? 参考文献??

一、引言 1.1 EDA技术的概念 EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪90年代初从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言HDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。 1.2 EDA技术的特点 利用EDA技术进行电子系统的设计,具有以下几个特点:①用软件的方式设计硬件;②用软件方式设计的系统到硬件系统的转换是由有关的开发软件自动完成的;③设计过程中可用有关软件进行各种仿真;④系统可现场编程,在线升级;⑤整个系统可集成在一个芯片上,体积小、功耗低、可靠性高。因此,EDA技术是现代电子设计的发展趋势。 1.3 EDA设计流程 典型的EDA设计流程如下: 1、文本/原理图编辑与修改。首先利用EDA工具的文本或图形编辑器将设计者的设计意图用文本或图形方式表达出来。 2、编译。完成设计描述后即可通过编译器进行排错编译,变成特定的文本格式,为下一步的综合做准备。 3、综合。将软件设计与硬件的可实现性挂钩,是将软件转化为硬件电路的关键步骤。 4、行为仿真和功能仿真。利用产生的网表文件进行功能仿真,以便了解设计描述与设计意图的一致性。 5、适配。利用FPGA/CPLD布局布线适配器将综合后的网表文件针对某一具体的目标器件进行逻辑映射操作,其中包括底层器件配臵、逻辑分割、逻辑优化、布局布线。适配报告指明了芯片内资源的分配与利用、引脚锁定、设计的布尔方程描述情况。

五种排序算法的分析与比较 广东医学院医学信息专业郭慧玲 摘要:排序算法是计算机程序设计广泛使用的解决问题的方法,研究排序算法具有重要的理论意义和广泛的应用价值。文章通过描述冒泡、选择、插入、归并和快速5种排序算法,总结了它们的时间复杂度、空间复杂度和稳定性。通过实验验证了5种排序算法在随机、正序和逆序3种情况下的性能,指出排序算法的适用原则,以供在不同条件下选择适合的排序算法借鉴。 关键词:冒泡排序;选择排序;插入排序;归并排序;快速排序。 排序是计算机科学中基本的研究课题之一,其目的是方便记录的查找、插入和删除。随着计算机的发展与应用领域的越来越广,基于计算机硬件的速度和存储空间的有限性,如何提高计算机速度并节省存储空间一直成为软件设计人员的努力方向。其中,排序算法已成为程序设计人员考虑的因素之一[1],排序算法选择得当与否直接影响程序的执行效率和内外存储空间的占用量,甚至影响整个软件的综合性能。排序操作[2,3],就是将一组数据记录的任意序列,重新排列成一个按关键字有序的序列。而所谓排序的稳定性[4]是指如果在排序的序列中,存在前后相同的两个元素,排序前和排序后他们的相对位臵不发生变化。 1 算法与特性 1.1冒泡排序 1.1.1冒泡排序的基本思想

冒泡排序的基本思想是[5,6]:首先将第1个记录的关键字和第2个记录的关键字进行比较,若为逆序,则将2个记录交换,然后比较第2个和第3个记录的关键字,依次类推,直至n-1个记录和第n个记录的关键字进行过比较为止。然后再按照上述过程进行下一次排序,直至整个序列有序为止。 1.1.2冒泡排序的特性 容易判断冒泡排序是稳定的。可以分析出它的效率,在最好情况下,只需通过n-1次比较,不需要移动关键字,即时间复杂度为O(n)(即正序);在最坏情况下是初始序列为逆序,则需要进行n-1次排序,需进行n(n-1)/2次比较,因此在最坏情况下时间复杂度为O(n2),附加存储空间为O(1)。 1.2选择排序 1.2.1选择排序的基本思想 选择排序的基本思想是[5,6]:每一次从待排序的记录中选出关键字最小的记录,顺序放在已排好序的文件的最后,直到全部记录排序完毕.常用的选择排序方法有直接选择排序和堆排序,考虑到简单和易理解,这里讨论直接选择排序。直接选择排序的基本思想是n个记录的文件的直接排序可经过n-1次直接选择排序得到有序结果。 1.2.2选择排序的特性 容易得出选择排序是不稳定的。在直接选择排序过程中所需进行记录移动的操作次数最少为0,最大值为3(n-1)。然而,无论记录的初始排序如何,所需进行的关键字间的比较次数相同,均为n(n-1)/2,时间

沈阳航空航天大学 课程设计报告 课程设计名称:计算机组成原理课程设计课程设计题目:阵列乘法器的设计与实现 院(系):计算机学院 专业:计算机科学与技术 班级: 学号: 姓名: 指导教师: 完成日期:2014年1月10日

目录 第1章总体设计方案 0 1.1设计原理 0 1.2设计思路 (1) 1.3设计环境 (2) 第2章详细设计方案 (2) 2.1总体方案的设计与实现 (2) 2.1.1总体方案的逻辑图 (3) 2.1.2器件的选择与引脚锁定 (3) 2.1.3编译、综合、适配 (4) 2.2功能模块的设计与实现 (4) 2.2.1 一位全加器的设计与实现 (4) 2.2.2 4位输入端加法器的设计与实现 (6) 2.2.3 阵列乘法器的设计与实现 (8) 第3章硬件测试 (11) 3.1编程下载 (11) 3.2 硬件测试及结果分析 (11) 参考文献 (13) 附录(电路原理图) (15)

第1章总体设计方案 1.1 设计原理 阵列乘法器采用类似人工计算的方法进行乘法运算。人工计算方法是用乘数的每一位去乘被乘数,然后将每一位权值对应相加得出每一位的最终结果。如图1.1所示,用乘数的每一位直接去乘被乘数得到部分积并按位列为一行,每一行部分积末位与对应的乘数数位对齐,体现对应数位的权值。将各次部分积求和,即将各次部分积的对应数位求和即得到最终乘积的对应数位的权值。 为了进一步提高乘法的运算速度,可采用大规模的阵列乘法器来实现,阵列乘法器的乘数与被乘数都是二进制数。可以通过乘数从最后一位起一个一个和被乘数相与,自第二位起要依次向左移一位,形成一个阵列的形式。这就可将其看成一个全加的过程,将乘数某位与被乘数某位与完的结果加上乘数某位的下一位与被乘数某位的下一位与完的结果再加上前一列的进位进而得出每一位的结果,假设被乘数与乘数的位数均为4位二进制数,即m=n=4,A×B可用如下竖式算出,如图1.1所示。 X4 X3 X2 X1 =A ×Y4 Y3 Y2 Y1=B X4Y1X3Y1X2Y1 X1Y1 X4Y2X3Y2X2Y2X1Y2 X4Y3X3Y3X2Y3X1Y3 (进位)X4Y4 X3Y4X2Y4X1Y4 Z8Z7Z6Z5Z4Z3Z2Z1 图1.1 A×B计算竖式 X4 ,X3 ,X2 ,X1 ,Y4 ,Y3 ,Y2 ,Y1为阵列乘法器的输入端,Z1-Z8为阵列乘法器的输出端,该逻辑框图所要完成的功能是实现两个四位二进制既A(X)*B(Y)的乘法运算,其计算结果为C(Z) (其中A(X)=X4X3X2X1 ,B(Y)=Y4Y3Y2Y1,C(Z)=Z8Z7Z6Z5Z4Z3Z2Z1而且输入和输出结果均用二进制表示)。阵列乘法器的总原理如图1.2所示。

各种排序法的比较 按平均时间将排序分为四类: (1)平方阶(O(n2))排序 一般称为简单排序,例如直接插入、直接选择和冒泡排序; (2)线性对数阶(O(nlgn))排序 如快速、堆和归并排序; (3)O(n1+£)阶排序 £是介于0和1之间的常数,即0<£<1,如希尔排序; (4)线性阶(O(n))排序 如桶、箱和基数排序。 各种排序方法比较: 简单排序中直接插入最好,快速排序最快,当文件为正序时,直接插入和冒泡均最佳。 影响排序效果的因素: 因为不同的排序方法适应不同的应用环境和要求,所以选择合适的排序方法 应综合考虑下列因素: ①待排序的记录数目n; ②记录的大小(规模); ③关键字的结构及其初始状态; ④对稳定性的要求; ⑤语言工具的条件; ⑥存储结构; ⑦时间和辅助空间复杂度等。 不同条件下,排序方法的选择 (1)若n较小(如n≤50),可采用直接插入或直接选择排序。 当记录规模较小时,直接插入排序较好;否则因为直接选择移动的记录数少于直接插人,应选直接选择排序为宜。 (2)若文件初始状态基本有序(指正序),则应选用直接插人、冒泡或随机的快速排序为宜; (3)若n较大,则应采用时间复杂度为O(nlgn)的排序方法:快速排序、堆排序或归并排序。 快速排序是目前基于比较的内部排序中被认为是最好的方法,当待排序的关键字是随机分布时,快速排序的平均时间最短; 堆排序所需的辅助空间少于快速排序,并且不会出现快速排序可能出现的最坏情况。这两种排序都是不稳定的。 若要求排序稳定,则可选用归并排序。从单个记录起进行两两归并,排序算法并不值得提倡,通常可以将它和直接插入排序结合在一起使用。先利用直接插入排序求得较长的有序子文件,然后再两两归并之。因为直接插入排序是稳定的,所以改进后的归并排序仍是稳定的。

00000000000000000000000 0000000000000000000000000 毕业论文 各种排序算法性能比较 系 专业姓名 班级学号 指导教师职称 设计时间 目录

摘要 (1) 第二章排序基本算法 (3) 第三章系统设计 (11) 第四章运行与测试 (24) 第五章总结 (26) 摘要 排序算法是数据结构这门课程核心内容之一。它是计算机程序设计、数据库、操作系统、编译原理及人工智能等的重要基础,广泛应用于信息学、系统工程等各种领域。学习排序算法是为了将实际问题中涉及的对象在计算机中进行处理。本毕业论文对直接插入排序、直接选择排序、起泡排序、Shell排序、快速排序以及堆排序算法进行比较。 我们设置待排序表的元素为整数,用不同的测试数据做测试比较,长度取固定的三种,对象由随机数生成,无需人工干预来选择或者输入数据。比较的指标为关键字的比较次数和关键字的移动次数。 经过比较可以看到,当规模不断增加时,各种算法之间的差别是很大的。这六种算法中,快速排序比较和移动的次数是最少的。也是最快的一种排序方法。堆排序和快速排序差不多,属于同一个数量级。直接选择排序虽然交换次数很少,但比较次数较多。 关键字:直接插入排序;直接选择排序;起泡排序;Shell排序;快速排序;堆排序;

1.3 本文主要内容 排序的方法很多,但是就其全面性能而言,很难提出一种被认为是最好的方法,每一种方法都有各自的优缺点,适合在不同的环境下使用。如果排序中依据的不同原则对内部排序方法进行分类,则大致可分为直接插入排序、直接选择排序、起泡排序、Shell排序、快速排序、堆排序六类。 本文编写一个程序对直接插入排序、直接选择排序、起泡排序、Shell排序、快速排序及堆排序这几种内部排序算法进行比较,用不同的测试数据做测试比较。比较的指标为关键字的比较次数和关键字的移动次数。最后用图表数据汇总,以便对这些内部排序算法进行性能分析。

物理与电子工程学院集成电路设计课程论文题目:乘法器的研究 学生姓名:XXX 指导教师:XXX 201X年XX月XX日

乘法器 摘要:乘法器,其基础就是加法器结构,它已经是现代计算机中必不可少的一部分。 乘法器的模型就是基于“移位和相加”的算法。本文讨论基本的阵列乘法器,以及产生部分 积和最终求和。 关键词:全加器,半加器,阵列。 引言: 乘法运算非常耗费硬件面积并且速度很慢,许多计算问题解决的快慢受乘法器电 路工作速度的约束,因此在现代高级的数字信号处理器和微处理器中都集成了硬件乘法单 元。并且乘法器在当今数字信号处理以及其他诸多应用领域中起着十分重要的作用。随着科 学技术的发展,许多研究人员已经开始试图设计一类拥有更高速率和低功耗,布局规律占用 面积小,集成度高的乘法器。这样,就能让它们更加适用于高速率,低功耗的大规模集成电 路的应用当中。通常的乘法计算方法是添加和位移的算法。在并行乘法器当中,相加的部分乘积的数量是主要的参数。它决定了乘法器的性能。为了减少相加的部分乘积的数量,修正 的Booth 算法是最常用的一类算法。但是,随着并行化的增多,大量的部分乘积和中间求和 的增加,会导致运行速度的下降。不规则的结构会增加硅板的面积,并且由于路由复杂而导 致中间连接过程的增多继而导致功耗的增大。另一方面串并行乘法器牺牲了运行速度来获得 更好的性能和功耗。因此,选择一款并行或串行乘法器实际上取决于它的应用性质。 主体 1.1.1二进制乘法定义 考虑两个无符号二进制数X 和Y ,X 为M 位宽,Y 为N 位宽,将它们用下列二进制数形 式表达 i 1 -M 0i i 2X X ∑== (1.1) j 1 -N 0j j 2Y Y ∑== (1.2) 其中i X 和j Y 为0或者1,那么X 和Y 的乘法运算定义如下 Z=X ×Y= k 1 -N M 0k k 2Z ∑+= =(i M i i X 210∑-=)(j 1-N 0j j 2Y ∑=)=∑∑=-=+???? ??1-M 0i 10j 2N j i j i Y X (1.3) 我们先来看一下手工是如何进行二进制乘法运算的。如图1-1所示,被乘数与乘数的第一个 位相乘(实际为“与”操作)产生积,并且根据乘数相应位的位置对部分积进行左移(例如, 被乘数与乘数的第0位相乘,则不移位;与第一位相乘,部分积左移1位,以此类推),最 终将所有的部分积相加得到乘法运算的结果。M 位被乘数与N 位乘数相乘得到的乘积是 M+N 位的。 1.1.2部分积生成

基于模拟乘法器MC1496的混频器设计

摘要 集成模拟乘法器是完成两个模拟量(电压或电流)相乘的电子器件。在高频电子线路中,振幅调制、同步检波、混频、倍频、鉴频等调制与解调的过程均可视为两个信号相乘的过程,而集成模拟乘法器正是实现两个模拟量,电压或电流相乘的电子器件。采用集成模拟乘法器实现上述功能比用分立器件要简单得多,而且性能优越,因此集成模拟乘法器在无线通信、广播电视等方面应用较为广泛。 混频器在通信工程和无线电技术中,应用非常广泛,在调制系统中,输入的基带信号都要经过频率的转换变成高频已调信号。在解调过程中,接收的已调高频信号也要经过频率的转换,变成对应的中频信号。特别是在超外差式接收机中,混频器应用较为广泛,混频电路是应用电子技术和无线电专业必须掌握的关键电路。 Matlab是一种电子技术界应用广泛的优秀科学计算软件,大量应用于算法开发、数据可视化、数据分析以及数值计算的高级技术计算语言和交互式环境。主要内容是基于MC1946的混频器应用设计与仿真,阐述混频器基本原理,并在Matlab中实现各信号波形的仿真。 关键词:MC1496模拟乘法器,混频器,Matlab

DESING OF MIXER BASED ON THE ANALOG MULTIPLIER MC1496 Abstract Integrated analog multiplier is to complete two analog multiplication electronics (voltage or current) In high frequency electronic circuit, amplitude modulation, synchronous detection, mixing, times frequency, frequency modulation and demodulation process can be regarded as the multiplication of two signals process, and integrated analog multiplier is the realization of two analog, voltage or current multiplication of electronic devices. The function is realized by using integrated analog multiplier is much simpler than with a discrete device, and superior performance, therefore integrated analog multiplier in wireless communication, radio and television are more widely application. Mixer in communication engineering and electronic technology, are widely applied in modulation system, the input of the baseband signal through frequency conversion into high frequency modulated signals. In the process of demodulation, receive the high frequency signal is modulated by frequency conversion, into the corresponding intermediate frequency signals. Especially in a superheterodyne receiver, which has been widely applied mixer, mixing circuit is a professional application of electronic technology, and radio must master the key circuit. Matlab is an electronic technology widely used mathematical software, a large number of used in algorithm development, data visualization, data analysis and numerical calculation of senior technical computing language and interactive environment. Main content is based on the MC1946 mixer application design and simulation, the basic principle of mixer, and realize the signal waveform in the Matlab simulation. Key Words: MC1496 analog multiplier, mixer, Matlab

本科生毕业论文(设计) 8位乘法器的设计 姓名:吴小东 指导教师:华婷婷 院系:信息工程学院 专业:计算机科学与技术 提交日期: 2010/4/30

目录 中文摘要 (2) 外文摘要 (3) 1.绪论 (4) 1.1概述 (4) 1.2 VHDL和MAX+PIUS简介 (5) 1.3 实验平台 (6) 2.乘法器初步设计 (7) 2.1 设计思想 (7) 2.2乘法器原理 (7) 2.3乘法器设计流程 (8) 3. 乘法器具体设计 (9) 3.1右移寄存器的设计 (9) 3.2 加法器模块的设计 (10) 3.2.1 4位加法器的设计 (10) 3.2.2 8位加法器的设计 (11) 3.3 乘1模块设计 (13) 3.4锁存器模块设计 (14) 4. 乘法器仿真 (17) 4.1 8位加法器仿真 (17) 4.2 乘1模块仿真 (17) 4.3 锁存器模块仿真 (18) 4.4 8位乘法器仿真 (18) 结束语 (19) 参考文献 (20) 致谢 (21)

8位乘法器的设计 吴小东 指导老师:华婷婷 (黄山学院信息工程学院,黄山,安徽 245041) 摘要:在微处理器芯片中,乘法器是进行数字信号处理的核心,同时也是微处理器中进行数据处理的关键部件,它已经是现代计算机必不可少的一部分。本文主要是在于如何运用标准硬件描述语言(VHDL)完成八位乘法器,以及如何做二进制位相乘的运算过程。该乘法器是由八位加法器构成的以时序方式设计八位乘法器,通过逐项移位相加来实现乘法功能,并以MAX+Plus II 软件工具进行模拟,仿真并予以显示。 关键字:乘法器;标准硬件描述语言(VHDL);移位相加;MAX+Plu s II

一、冒泡排序 已知一组无序数据a[1]、a[2]、……a[n],需将其按升序排列。首先比较a[1]与 a[2]的值,若a[1]大于a[2]则交换两者的值,否则不变。再比较a[2]与a[3]的值,若a[2]大于a[3]则交换两者的值,否则不变。再比较a[3]与a[4],以此类推,最后比较a[n-1]与a[n]的值。这样处理一轮后,a[n]的值一定是这组数据中最大的。再对a[1]~a[n- 1]以相同方法处理一轮,则a[n-1]的值一定是a[1]~a[n-1]中最大的。再对a[1]~a[n-2]以相同方法处理一轮,以此类推。共处理 n-1轮后a[1]、a[2]、……a[n]就以升序排列了。 优点:稳定; 缺点:慢,每次只能移动相邻两个数据。 二、选择排序 每一趟从待排序的数据元素中选出最小(或最大)的一个元素,顺序放在已排好序的数列的最后,直到全部待排序的数据元素排完。 选择排序是不稳定的排序方法。 n个记录的文件的直接选择排序可经过n-1趟直接选择排序得到有序结果: ①初始状态:无序区为R[1..n],有序区为空。 ②第1趟排序 在无序区R[1..n]中选出关键字最小的记录R[k],将它与无序区的第1个记录R[1]交换,使R[1..1]和R[2..n]分别变为记录个数增加1个的新有序区和记录个数减少1个的新无序区。 …… ③第i趟排序 第i趟排序开始时,当前有序区和无序区分别为R[1..i-1]和R(1≤i≤n-1)。该趟排序从当前无序区中选出关键字最小的记录 R[k],将它与无序区的第1个记录R交换,使R[1..i]和R分别变为记录个数增加1个的新有序区和记录个数减少1个的新无序区。 这样,n个记录的文件的直接选择排序可经过n-1趟直接选择排序得到有序结果。 优点:移动数据的次数已知(n-1次); 缺点:比较次数多。 三、插入排序 已知一组升序排列数据a[1]、a[2]、……a[n],一组无序数据b[1]、 b[2]、……b[m],需将二者合并成一个升序数列。首先比较b[1]与a[1]的值,若b[1]大于a[1],则跳过,比较b[1]与a[2]的值,若b[1]仍然大于a[2],则继续跳过,直到b[1]小于a数组中某一数据a[x],则将a[x]~a[n]分别向后移动一位,将b[1]插入到原来 a[x]的位置这就完成了b[1] 的插入。b[2]~b[m]用相同方法插入。(若无数组a,可将b[1]当作n=1的数组a) 优点:稳定,快; 缺点:比较次数不一定,比较次数越少,插入点后的数据移动越多,特别是当数据总量庞大的时候,但用链表可以解决这个问题。 四、缩小增量排序 由希尔在1959年提出,又称希尔排序(shell排序)。 已知一组无序数据a[1]、a[2]、……a[n],需将其按升序排列。发现当n不大时,插入排序的效果很好。首先取一增量d(d

数字电路课程设计 题目乘法器设计 班级实验二班 学号 姓名 时间第十三、十四周 地点科A-304 指导陈学英唐青

【摘要】:用FPGA设计完成基于半加器、全加器和保留进位思想设计的4BIT四级流水乘法器,用modelsim仿真其结果。 【目录】: 第一章、实验任务及原理 第二章、设计思路方法及方案 第三章、FPGA模块程序设计与仿真 第四章、结束语

【正文】 【第一章】:实验任务及原理 本实验只要求编写乘法器的硬件代码,并用Modelsim进行仿真测 试。设计乘法器,两个输入都是4BIT,对所有输入相乘都得到正 确结果,乘法器采用四级流水设计,以增加处理速度。用modelsim 仿真时,要求用时钟上升沿方式遍历所有输入,检查输出结果是否 正确。原理用到流水,进位保留思想。 【第二章】:设计思路及方案 算法结构(无符号) 由上图可见,乘法的运算最终是加法的运算,两个4BIT输入,输出为7BIT。模块一、半加器:单比特输入相加, 模块二、全加器:由两个半加器组成,有一个进位输入, 模块三、进位保留加法器:

最终程序结构图 流水设计的原理:在前向割集上加入四级流水 图一 图二 如上图所示方框代表触发器,五边形代表组合逻辑块,假设图一中逻辑块输入输出延时为Ta,图二将逻辑块切割成两块,延时分别为T1,T2,且Ta=T1+T2,

并在两逻辑块之间加触发器,两个逻辑块工作频率都可以达到clk频率,故工作速度增加一倍,虽然时延增加了,但资源优化了许多。 【第三章】:FPGA程序模块及仿真 半加器的程序模块: entity half_adder is port(a,b:in std_logic; s,cout:out std_logic); end half_adder; architecture Behavioral of half_adder is begin s<=a xor b; cout<=a and b; end Behavioral; 全加器的程序模块:调用半加器,采用顶层设计 entity full_adder is port(a,b,cin:in std_logic; s,cout:out std_logic); end full_adder; architecture Behavioral of full_adder is component half_adder port(a,b:in std_logic; cout,s:out std_logic); end component; signal h1s,h1cout,h2cout:std_logic; begin u1:half_adder port map(a,b,h1cout,h1s); u2:half_adder port map(cin,h1s,h2cout,s); cout<=h1cout or h2cout; end Behavioral; 乘法器的程序模块: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; ----Uncomment the following library declaration if instantiating ----any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all;

家庭电路作图题 1、把带有开关的电灯,三孔插座正确地连入如图的家庭电路中. 2、一间教室要安装2盏 “220V 40W”的电灯和一个 插座,要求开关S控制两盏灯, 且每盏灯都能正常发光,请按 以上要求将图中元件用笔画 线代替导线连接起来. 3、请同学们将图连 成符合安全用电原 4、将如图所示电水壶的3 条接线按照安全用电的原则 对应连接到插头上. 5、下图是家庭电路的示意 图。请把该图连接完整 6、请在图中连接家庭电路的 电路图.要求:L1灯、L2灯 并联,开关S控制两盏灯. 7、如图所示,甲为一个“一开三孔”开关(即一个开关和一个三孔插座 连在一起)的实物图,乙为背面接线示意图,“A”“B”是从开关接线柱接 出的两根导线,请你将图乙中的电路连接完整,使开关控制电灯,又不影 响插座供其他电器使用。 8、图15(甲)是小明常用的一个插线板。他在使用中发现:插线板上 的指示灯在开关闭合时会发光,插孔正常通电;如果指示灯损坏,开 关闭合时插孔也能正常通电。根据上述现象,在图15(乙)中画出插 线板上开关、指示灯和插孔的连接方式,并与电源线接通。 9、请在图中的虚线框内 设计一电路图:连接导 线,使护士看见L1灯亮 知道1号病房有人呼叫, 看见L2灯亮知道2号病 房有人呼叫。(虚线框内 导线不许交叉) 10、为节约电能,地下通 道电动扶梯只需在白天且 有人时才开启,利用红外 线自动开关S1(现场有人, S1闭合;现场无人,S1断 开)以及可见光自动开关 S2(白天,S2闭合;夜间, S2断开)控制电路,可达到目的.请完成电路连接. 11、图甲是某宾馆床头柜上的开关示意图,图乙是其控制的电路,其 中S1为旋钮开关,单独控制台灯的通断和亮度;S2为单独控制电视 插座的开关.请在图乙中将电路图连接完整,要求符合安全用电原则. 12、请将图中的“光控开关”、“声控开关”、灯泡用笔画线代替导线正 确连入电路,设计 出只有在光线很暗且有声 音时灯才亮的楼道灯自动 控制电路,同时安装一个不受开 关控制的三孔插座。 13、请在下图中用导线连接一个三项插座和一盏带开关的电灯的照明 电路 14、将图3中的开关、螺丝口灯泡、插座接入家庭电路。要求开关控 制灯泡。